# E. Renesas Electronics America Inc - UPD78F0730MC-CAB-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 16MHz                                                                                |

| Connectivity               | 3-Wire SIO, UART/USART, USB                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 19                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 3K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                    |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 30-LSSOP (0.240", 6.10mm Width)                                                      |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0730mc-cab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

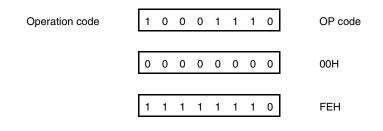

#### 3.4.3 Direct addressing

#### [Function]

The memory to be manipulated is directly addressed with immediate data in an instruction word becoming an operand address.

This addressing can be carried out for all of the memory spaces.

#### [Operand format]

| Identifier | Description                    |

|------------|--------------------------------|

| addr16     | Label or 16-bit immediate data |

#### [Description example]

MOV A, !0FE00H; when setting !addr16 to FE00H

#### [Illustration]

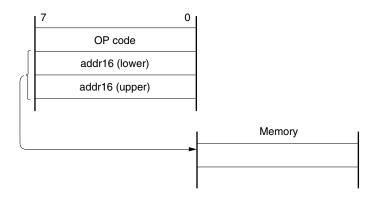

Figure 4-13. Block Diagram of P120

- P12: Port register 12

- PU12: Pull-up resistor option register 12

- PM12: Port mode register 12

- RD: Read signal

- WR××: Write signal

#### (9) USB clock control register (UCKC)

This register controls the USB clock (fuse) supplied to the USB function controller. UCKC can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 00H.

#### Figure 5-10. Format of USB Clock Control Register (UCKC)

| Address: FF | A7H After r | eset: 00H | R/W     |               |                  |               |           |   |

|-------------|-------------|-----------|---------|---------------|------------------|---------------|-----------|---|

| Symbol      | <7>         | 6         | 5       | 4             | 3                | 2             | 1         | 0 |

| UCKC        | UCKCNT      | 0         | 0       | 0             | 0                | 0             | 0         | 0 |

|             |             |           |         |               |                  |               |           |   |

|             |             |           | Control | of LICD alask | our paired to LU | CD function o | ontrollor |   |

| UCKCNT | Control of USB clock supplied to USB function controller |  |  |  |

|--------|----------------------------------------------------------|--|--|--|

| 0      | tops USB clock supply.                                   |  |  |  |

| 1      | Supplies USB clock.                                      |  |  |  |

Caution Before shifting to the STOP mode, stop the clock supply to the USB function controller. After the STOP mode is released, count the PLL oscillation stabilization time (800  $\mu$ s) using software, and supply the clock to the USB function controller after the oscillation stabilization wait time has elapsed.

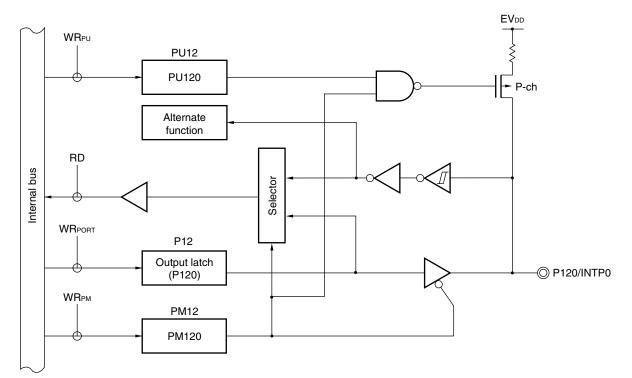

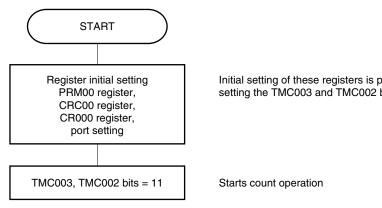

#### Figure 6-21. Example of Software Processing in External Event Counter Mode

<1> Count operation start flow

<2> Count operation stop flow

Initial setting of these registers is performed before setting the TMC003 and TMC002 bits to 11.

The counter is initialized and counting is stopped by clearing the TMC003 and TMC002 bits to 00.

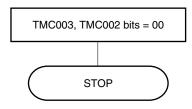

Figure 6-37. Timing Example of Free-Running Timer Mode (CR000: Capture Register, CR010: Capture Register) (2/2)

(b) TOC00 = 13H, PRM00 = C0H, CRC00 = 05H, TMC00 = 04H

This is an application example where both the edges of the TI010 pin are detected and the count value is captured to CR000 in the free-running timer mode.

When both CR000 and CR010 are used as capture registers and when the valid edge of only the TI010 pin is to be detected, the count value cannot be captured to CR010.

#### (1) 8-bit timer counter 5n (TM5n)

TM5n is an 8-bit register that counts the count pulses and is read-only. The counter is incremented in synchronization with the rising edge of the count clock.

|                    | Figure 7-3. Format of 8-Bit Timer Counter 5n (TM5n) |            |          |           |          |   |   |   |

|--------------------|-----------------------------------------------------|------------|----------|-----------|----------|---|---|---|

| Address: Fl        | F16H (TM5                                           | 50), FF1FH | I (TM51) | After res | set: 00H | R |   |   |

| Symbol             | 7                                                   | 6          | 5        | 4         | 3        | 2 | 1 | 0 |

| TM5n<br>(n = 0, 1) |                                                     |            |          |           |          |   |   |   |

In the following situations, the count value is cleared to 00H.

- <1> Reset signal generation

- <2> When TCE5n is cleared

<3> When TM5n and CR5n match in the mode in which clear & start occurs upon a match of the TM5n and CR5n.

#### (2) 8-bit timer compare register 5n (CR5n)

CR5n can be read and written by an 8-bit memory manipulation instruction.

Except in PWM mode, the value set in CR5n is constantly compared with the 8-bit timer counter 5n (TM5n) count value, and an interrupt request (INTTM5n) is generated if they match.

In the PWM mode, the TO5n pin becomes inactive when the values of TM5n and CR5n match, but no interrupt is generated.

The value of CR5n can be set within 00H to FFH.

Reset signal generation sets CR5n to 00H.

#### Figure 7-4. Format of 8-Bit Timer Compare Register 5n (CR5n)

| Address:           | FF17H (CR | 50), FF41H | I (CR51) | After res | set: 00H | R/W |   |   |

|--------------------|-----------|------------|----------|-----------|----------|-----|---|---|

| Symbol             | 7         | 6          | 5        | 4         | 3        | 2   | 1 | 0 |

| CR5n<br>(n = 0, 1) |           |            |          |           |          |     |   |   |

| (n = 0, 1)         |           |            |          |           |          |     |   |   |

- Cautions 1. In the mode in which clear & start occurs on a match of TM5n and CR5n (TMC5n6 = 0), do not write other values to CR5n during operation.

- 2. In PWM mode, make the CR5n rewrite period 3 count clocks of the count clock (clock selected by TCL5n) or more.

**Remark** n = 0, 1

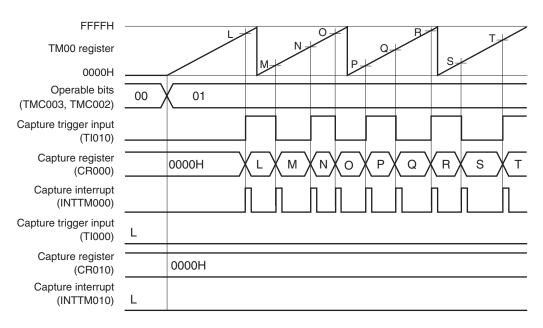

#### Figure 8-4. Format of 8-Bit Timer H Mode Register 1 (TMHMD1)

Address: FF6CH After reset: 00H R/W

TMHMD1

| _ | <7>   | 6     | 5     | 4     | 3      | 2      | <1>    | <0>   |

|---|-------|-------|-------|-------|--------|--------|--------|-------|

|   | TMHE1 | CKS12 | CKS11 | CKS10 | TMMD11 | TMMD10 | TOLEV1 | TOEN1 |

| TMHE1 | Timer operation enable                                                     |  |  |  |  |

|-------|----------------------------------------------------------------------------|--|--|--|--|

| 0     | Stops timer count operation (counter is cleared to 0)                      |  |  |  |  |

| 1     | Enables timer count operation (count operation started by inputting clock) |  |  |  |  |

| CKS12 | CKS11 | CKS10 | Count clock selection |                 |               |  |

|-------|-------|-------|-----------------------|-----------------|---------------|--|

|       |       |       |                       | fprs = 12 MHz   | fprs = 16 MHz |  |

| 0     | 0     | 0     | fprs                  | 12 MHz          | 16 MHz        |  |

| 0     | 0     | 1     | fprs/2 <sup>2</sup>   | 3 MHz           | 4 MHz         |  |

| 0     | 1     | 0     | fprs/24               | 750 kHz         | 1 MHz         |  |

| 0     | 1     | 1     | fprs/2 <sup>6</sup>   | 187.5 kHz       | 250 kHz       |  |

| 1     | 0     | 0     | fprs/212              | 2.93 kHz        | 3.91 kHz      |  |

| 1     | 0     | 1     | frl/27                | 1.88 kHz (TYP.) |               |  |

| 1     | 1     | 0     | frl/29                | 0.47 kHz (TYP.) |               |  |

| 1     | 1     | 1     | frL                   | 240 kHz (TYP.)  |               |  |

| TMMD11 | TMMD10 | Timer operation mode   |

|--------|--------|------------------------|

| 0      | 0      | Interval timer mode    |

| 0      | 1      | Carrier generator mode |

| 1      | 0      | PWM output mode        |

| 1      | 1      | Setting prohibited     |

| TOLEV1 | Timer output level control (in default mode) |

|--------|----------------------------------------------|

| 0      | Low level                                    |

| 1      | High level                                   |

| TOEN1 | Timer output control |

|-------|----------------------|

| 0     | Disables output      |

| 1     | Enables output       |

#### Cautions 1. When TMHE1 = 1, setting the other bits of TMHMD1 is prohibited.

- In the PWM output mode and carrier generator mode, be sure to set 8-bit timer H compare register 11 (CMP11) when starting the timer count operation (TMHE1 = 1) after the timer count operation was stopped (TMHE1 = 0) (be sure to set again even if setting the same value to CMP11).

- 3. When the carrier generator mode is used, set so that the count clock frequency of TMH1 becomes more than 6 times the count clock frequency of TM51.

#### Remarks 1. fprs: Peripheral hardware clock frequency

2. frL: Internal low-speed oscillation clock frequency

## Setting

<1> Set each register.

#### Figure 8-12. Register Setting in Carrier Generator Mode

#### (i) Setting 8-bit timer H mode register 1 (TMHMD1)

#### (ii) CMP01 register setting

• Compare value

#### (iii) CMP11 register setting

• Compare value

#### (iv) TMCYC1 register setting

- RMC1 = 1 ... Remote control output enable bit

- NRZB1 = 0/1 ... carrier output enable bit

### (v) TCL51 and TMC51 register setting

### • See 7.3 Registers Controlling 8-Bit Timer/Event Counters 50 and 51.

- <2> When TMHE1 = 1, 8-bit timer H1 starts counting.

- <3> When TCE51 of 8-bit timer mode control register 51 (TMC51) is set to 1, 8-bit timer/event counter 51 starts counting.

- <4> After the count operation is enabled, the first compare register to be compared is the CMP01 register. When the count value of 8-bit timer counter H1 and the CMP01 register value match, the INTTMH1 signal is generated, 8-bit timer counter H1 is cleared. At the same time, the compare register to be compared with 8-bit timer counter H1 is switched from the CMP01 register to the CMP11 register.

- <5> When the count value of 8-bit timer counter H1 and the CMP11 register value match, the INTTMH1 signal is generated, 8-bit timer counter H1 is cleared. At the same time, the compare register to be compared with 8-bit timer counter H1 is switched from the CMP11 register to the CMP01 register.

- <6> By performing procedures <4> and <5> repeatedly, a carrier clock is generated.

- <7> The INTTM51 signal is synchronized with count clock of the 8-bit timer H1 and output as the INTTM5H1 signal. The INTTM5H1 signal becomes the data transfer signal for the NRZB1 bit, and the NRZB1 bit value is transferred to the NRZ1 bit.

- <8> Write the next value to the NRZB1 bit in the interrupt servicing program that has been started by the INTTM5H1 interrupt or after timing has been checked by polling the interrupt request flag. Write data to count the next time to the CR51 register.

- <9> When the NRZ1 bit is high level, a carrier clock is output from the TOH1 pin.

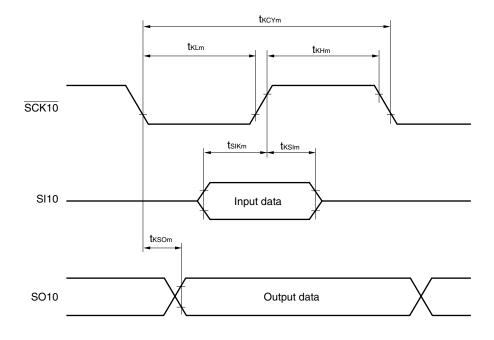

#### 11.4.2 3-wire serial I/O mode

The 3-wire serial I/O mode is used for connecting peripheral ICs and display controllers with a clocked serial interface. In this mode, communication is executed by using three lines: the serial clock (SCK10), serial output (SO10), and serial input (SI10) lines.

#### (1) Registers used

- Serial operation mode register 10 (CSIM10)

- Serial clock selection register 10 (CSIC10)

- Port mode register 1 (PM1)

- Port register 1 (P1)

The basic procedure of setting an operation in the 3-wire serial I/O mode is as follows.

- <1> Set the CSIC10 register (see Figure 11-3).

- <2> Set bits 0, 4 and 6 (CSOT10, DIR10, and TRMD10) of the CSIM10 register (see Figure 11-2).

- <3> Set bit 7 (CSIE10) of the CSIM10 register to 1.  $\rightarrow$  Transmission/reception is enabled.

- <4> Write data to transmit buffer register 10 (SOTB10). → Data transmission/reception is started. Read data from serial I/O shift register 10 (SIO10). → Data reception is started.

- Caution Take relationship with the other party of communication when setting the port mode register and port register.

## 12.2 Configuration

USB function controller USBF includes the following hardware.

| Item              | Configuration                                       |  |

|-------------------|-----------------------------------------------------|--|

| USB port pins     | USBP (+), USBM (-)                                  |  |

| Control registers | UF0 EP0NAK register (UF0E0N)                        |  |

|                   | UF0 EP0NAKALL register (UF0E0NA)                    |  |

|                   | UF0 EPNAK register (UF0EN)                          |  |

|                   | UF0 EPNAK mask register (UF0ENM)                    |  |

|                   | UF0 SNDSIE register (UF0SDS)                        |  |

|                   | UF0 CLR request register (UF0CLR)                   |  |

|                   | UF0 SET request register (UF0SET)                   |  |

|                   | UF0 EP status 0 register (UF0EPS0)                  |  |

|                   | UF0 EP status 1 register (UF0EPS1)                  |  |

|                   | UF0 EP status 2 register (UF0EPS2)                  |  |

|                   | UF0 INT status 0 register (UF0IS0)                  |  |

|                   | UF0 INT status 1 register (UF0IS1)                  |  |

|                   | UF0 INT status 2 register (UF0IS2)                  |  |

|                   | UF0 INT status 3 register (UF0IS3)                  |  |

|                   | UF0 INT status 4 register (UF0IS4)                  |  |

|                   | UF0 INT mask 0 register (UF0IM0)                    |  |

|                   | UF0 INT mask 1 register (UF0IM1)                    |  |

|                   | UF0 INT mask 2 register (UF0IM2)                    |  |

|                   | UF0 INT mask 3 register (UF0IM3)                    |  |

|                   | UF0 INT mask 4 register (UF0IM4)                    |  |

|                   | UF0 INT clear 0 register (UF0IC0)                   |  |

|                   | UF0 INT clear 1 register (UF0IC1)                   |  |

|                   | UF0 INT clear 2 register (UF0IC2)                   |  |

|                   | UF0 INT clear 3 register (UF0IC3)                   |  |

|                   | UF0 INT clear 4 register (UF0IC4)                   |  |

|                   | UF0 FIFO clear 0 register (UF0FIC0)                 |  |

|                   | UF0 FIFO clear 1 register (UF0FIC1)                 |  |

|                   | UF0 data end register (UF0DEND)                     |  |

|                   | UF0 GPR register (UF0GPR)                           |  |

|                   | UF0 mode control register (UF0MODC)                 |  |

|                   | UF0 mode status register (UF0MODS)                  |  |

|                   | UF0 active interface number register (UF0AIFN)      |  |

|                   | UF0 active alternative setting register (UF0AAS)    |  |

|                   | UF0 alternative setting status register (UF0ASS)    |  |

|                   | UF0 endpoint 1 interface mapping register (UF0E1IM) |  |

|                   | UF0 endpoint 2 interface mapping register (UF0E2IM) |  |

## Table 12-1. Configuration of USB Function Controller USBF (1/2)

#### 12.4 Register Configuration

#### 12.4.1 Control registers

#### (1) UF0 EP0NAK register (UF0E0N)

This register controls NAK of Endpoint0 (except an automatically executed request).

This register can be read or written in 8-bit units (however, bit 0 can only be read).

It takes five USB clocks to reflect the status on this register after the UF0FIC0 and UF0FIC1 registers have been set. If it is necessary to read the status correctly, therefore, separate a write signal that accesses the UF0FIC0 and UF0FIC1 registers from a read signal that accesses the UF0EPS0, UF0EPS1, UF0EPS2, UF0E0N, and UF0EN registers by at least four USB clocks.

While NAK is being transmitted to Endpoint0 Read and Endpoint2, a write access to the EP0NKR bit is ignored.

|              | 7  | 6                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                                | 3                                                                                                                                                          | 2                                                                                                                                                                | 1                                                                                                                                             | 0                                                                                                                                              | Address                                                                                              | After reset |

|--------------|----|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------|

| UF0E0N       | 0  | 0                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                | 0                                                                                                                                                          | 0                                                                                                                                                                | EP0NKR                                                                                                                                        | EP0NKW                                                                                                                                         | FF60H                                                                                                | 00H         |

| Bit position |    | Bit name                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                  |                                                                                                                                                            |                                                                                                                                                                  | Function                                                                                                                                      |                                                                                                                                                |                                                                                                      |             |

| 1            | EF | PONKR                                                                                                               | <ul> <li>This bit controls NAK to the OUT token to Endpoint0 (except an automatically executed request). It is automatically set to 1 by hardware when Endpoint0 has correctly received data. It is also cleared to 0 by hardware when the data of the UF0E0R register has been read by FW (counter value = 0).</li> <li>1: Transmit NAK.</li> <li>0: Do not transmit NAK (default value).</li> <li>Set this bit to 1 by FW when data should not be received from the USB bus for some reason even when USBF is ready for receiving data. In this case, USBF continues transmitting NAK until this bit is cleared to 0 by FW. This bit is also cleared to 0 as soon as the UF0E0R register has been cleared.</li> </ul> |                                                                                                                                                                  |                                                                                                                                                            |                                                                                                                                                                  |                                                                                                                                               |                                                                                                                                                | for some                                                                                             |             |

| 0 EPONKW     |    | automa<br>the da<br>The da<br>necess<br>the hos<br>EODEL<br>FIFO is<br>EPONH<br>1: D<br>0: T<br>If contu<br>data st | atically exe<br>ta of Endp<br>ata of the L<br>sary to rev<br>st could no<br>D bit of the<br>s full. As s<br>KW bit is a<br>two not tran<br>transmit NA<br>rol transfer<br>age, this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ecuted requ<br>oint0 is trai<br>JF0E0W re<br>vrite this bit<br>ot receive d<br>UF0DENE<br>soon as the<br>utomaticall<br>smit NAK.<br>AK (default<br>r enters the | uest). This<br>namitted a<br>gister is re-<br>even in th<br>lata correc<br>D register t<br>EODED b<br>y set to 1 a<br>value).<br>status sta<br>d to 0 as s | bit is autom<br>nd the host of<br>etained until<br>e case of a n<br>tly. To send<br>o 1. This bit<br>it of the UF0<br>at the same<br>ge while AC<br>oon as the U | correctly rece<br>this bit is clea<br>retransmissio<br>a short packe<br>is automatica<br>DEND regist<br>time.<br>K cannot be<br>JF0E0W regist | ed to 0 by ha<br>ives the trans<br>ared. Therefor<br>in request that<br>et, be sure to<br>ally set to 1 w<br>er is set to 1,<br>correctly rece | rdware when<br>smitted data.<br>ore, it is not<br>at is made if<br>set the<br>when the<br>the<br>the |             |

#### (33) UF0 active alternative setting register (UF0AAS)

This register specifies a link between the Interface number and Alternative Setting.

This register can be read or written in 8-bit units.

USBF of the  $\mu$ PD78F0730 can set a five-series Alternative Setting (Alternate Setting 0, 1, 2, 3, and 4 can be defined) and a two-series Alternative Setting (Alternative Setting 0 and 1 can be defined) for one Interface.

| <u></u> .                                                                                                 | 7    | 6                                                                                         | 5                              | 4                                                                                                                                                    | 3             | 2             | 1              | 0                      | Address         | After reset |  |  |

|-----------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|----------------|------------------------|-----------------|-------------|--|--|

| UF0AAS                                                                                                    | ALT2 | IFAL21                                                                                    | IFAL20                         | ALT2EN                                                                                                                                               | ALT5          | IFAL51        | IFAL50         | ALT5EN                 | FF71H           | 00H         |  |  |

|                                                                                                           |      |                                                                                           |                                |                                                                                                                                                      |               |               |                |                        |                 |             |  |  |

| Bit position                                                                                              | on   | Bit name                                                                                  |                                |                                                                                                                                                      |               |               | Function       |                        |                 |             |  |  |

| 7, 3                                                                                                      | A    | LTn                                                                                       |                                | • •                                                                                                                                                  |               |               |                | 0                      | ked with Inter  |             |  |  |

|                                                                                                           |      |                                                                                           |                                |                                                                                                                                                      |               |               | •              |                        | Ln0 bits is inv | alid.       |  |  |

|                                                                                                           |      |                                                                                           |                                |                                                                                                                                                      |               | ive Setting w |                | e 0.<br>nterface 0 (de | afault value)   |             |  |  |

|                                                                                                           |      |                                                                                           |                                |                                                                                                                                                      |               |               | 0              | •                      | ,               |             |  |  |

| 6, 5,<br>2, 1                                                                                             |      | ALn1,<br>ALn0                                                                             |                                | • •                                                                                                                                                  |               |               |                |                        | series Alterna  | 0           |  |  |

| 2, 1                                                                                                      | 11   | ALIIU                                                                                     |                                | If the linked Interface number is outside the range specified by the UF0AIFN register, the n-series Alternative Setting is invalid (ALTnEN bit = 0). |               |               |                |                        |                 |             |  |  |

|                                                                                                           |      |                                                                                           | IFA                            | Ln1 IF                                                                                                                                               | ALn0          |               | Interfac       | e number to            | be linked       |             |  |  |

|                                                                                                           |      |                                                                                           |                                | 1                                                                                                                                                    | 1             | Links Interfa | ace 4.         |                        |                 |             |  |  |

|                                                                                                           |      |                                                                                           |                                | 1                                                                                                                                                    | 0             | Links Interfa | ace 3.         |                        |                 |             |  |  |

|                                                                                                           |      | (                                                                                         | D                              | 1                                                                                                                                                    | Links Interfa | ace 2.        |                |                        |                 |             |  |  |

|                                                                                                           |      |                                                                                           | (                              | D                                                                                                                                                    | 0             | Links Interfa | ace 1.         |                        |                 |             |  |  |

| 4, 0 ALTnEN                                                                                               |      |                                                                                           | i link a five-<br>Interface nu |                                                                                                                                                      | ernative Set  | ting and a t  | two-series Alt | ternative Sett         | ing with the    |             |  |  |

|                                                                                                           |      | These bits validate the n-series Alternative Setting. Unless these bits are set to 1, the |                                |                                                                                                                                                      |               |               |                |                        | t to 1, the     |             |  |  |

| setting of the ALTn, IFALn1, and IFALn0 bits is invalid.<br>1: Validate the n-series Alternative Setting. |      |                                                                                           |                                |                                                                                                                                                      |               |               |                |                        |                 |             |  |  |

|                                                                                                           |      |                                                                                           |                                | 0: Do not validate the n-series Alternative Setting (default value).                                                                                 |               |               |                |                        |                 |             |  |  |

|                                                                                                           |      |                                                                                           |                                |                                                                                                                                                      |               |               |                | 0 (*******             | /               |             |  |  |

For example, when the UF0AIFN register is set to 82H and the UF0AAS register is set to 15H, Interfaces 0, 1, 2, and 3 are valid. Interfaces 0 and 2 support only Alternative Setting 0. Interface 1 supports Alternative Setting 0 and 1, and Interface 3 supports Alternative Setting 0, 1, 2, 3, and 4. With this setting, requests GET\_INTERFACE wIndex = 0/1/2/3, SET\_INTERFACE wValue = 0 & wIndex = 0/2, SET\_INTERFACE wValue = 0/1 & wIndex = 1, and SET\_INTERFACE wValue = 0/1/2/3/4 & wIndex = 3 are automatically responded to, and a STALL response is made to the other GET/SET\_INTERFACE requests.

| Register Name                   | After CPU Reset (RESET)     | After Bus Reset |

|---------------------------------|-----------------------------|-----------------|

| UF0E0R register                 | Undefined <sup>Note 1</sup> | Value is held.  |

| UF0E0L register                 | 00Н                         | Value is held.  |

| UF0E0ST register                | 00H                         | 00H             |

| UF0E0W register                 | Undefined <sup>Note 1</sup> | Value is held.  |

| UF0BO1 register                 | Undefined <sup>Note 1</sup> | Value is held.  |

| UF0BO1L register                | 00H                         | Value is held.  |

| UF0BI1 register                 | Undefined <sup>Note 1</sup> | Value is held.  |

| UF0DSTL register                | 00H                         | 00H             |

| UF0E0SL register                | 00H                         | 00H             |

| UF0E1SL register                | 00H                         | 00H             |

| UF0E2SL register                | 00H                         | 00H             |

| UF0ADRS register                | 00H                         | 00H             |

| UF0CNF register                 | 00H                         | 00H             |

| UF0IF0 register                 | 00H                         | 00H             |

| UF0IF1 register                 | 00H                         | 00H             |

| UF0IF2 register                 | 00H                         | 00H             |

| UF0IF3 register                 | 00H                         | 00H             |

| UF0IF4 register                 | 00H                         | 00H             |

| UF0DSCL register                | 00H                         | Value is held.  |

| UF0DDn register (n = 0 to 17)   | Note 2                      | Note 2          |

| UF0CIEn register (n = 0 to 255) | Note 2                      | Note 2          |

| Table 12-8. | . Register Values in Specific Status (2 | 2/2) |

|-------------|-----------------------------------------|------|

|-------------|-----------------------------------------|------|

- **Notes 1.** This register can be cleared to 0 by the RESET signal because its write pointer, counter, and read pointer are cleared to 0 when the RESET signal becomes active, in the same manner as clearing by the UF0FICn register, as the register is controlled by FIFO.

- This register cannot be cleared to 0. Because data can be written to it by FW, however, any value can be written to the register (before doing so, however, be sure to set the EP0NKA bit of the UF0E0NA register to 1).

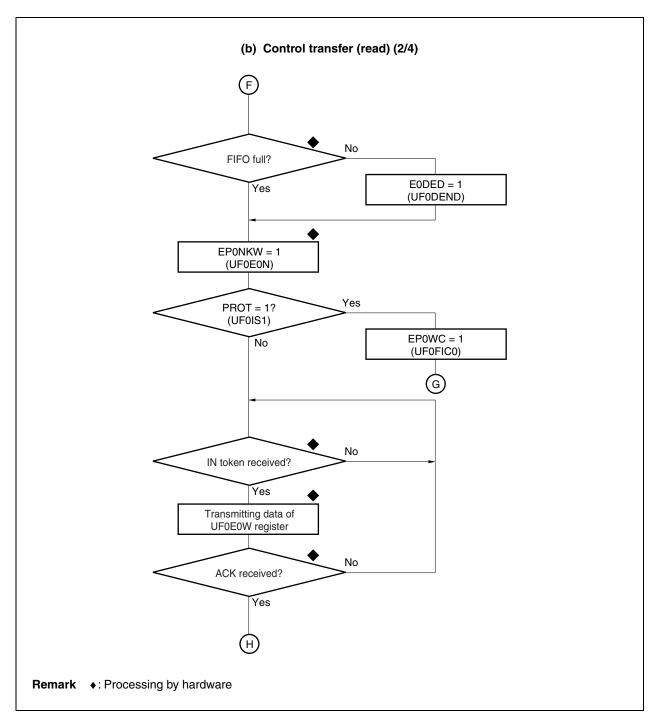

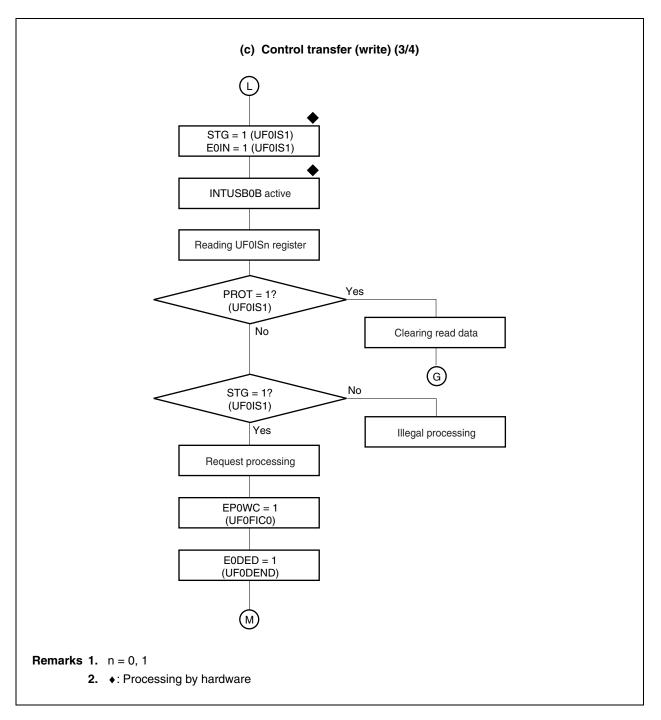

Figure 12-19. CPUDEC Request for Control Transfer (4/12)

Figure 12-19. CPUDEC Request for Control Transfer (9/12)

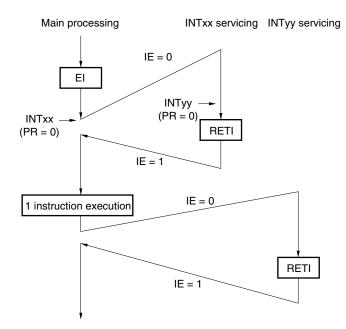

#### Figure 13-10. Examples of Multiple Interrupt Servicing (2/2)

#### Example 3. Multiple interrupt servicing does not occur because interrupts are not enabled

Interrupts are not enabled during servicing of interrupt INTxx (El instruction is not issued), therefore, interrupt request INTyy is not acknowledged and multiple interrupt servicing does not take place. The INTyy interrupt request is held pending, and is acknowledged following execution of one main processing instruction.

- PR = 0: Higher priority level

- IE = 0: Interrupt request acknowledgement disabled

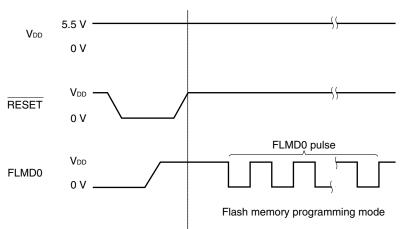

#### 19.7.2 Flash memory programming mode

To rewrite the contents of the flash memory by using the dedicated flash memory programmer, set the  $\mu$ PD78F0730 in the flash memory programming mode. To set the mode, set the FLMD0 pin to V<sub>DD</sub> and clear the reset signal.

Change the mode by using a jumper when writing the flash memory on-board.

#### Figure 19-13. Flash Memory Programming Mode

| FLMD0 | Operation Mode                |

|-------|-------------------------------|

| 0     | Normal operation mode         |

| VDD   | Flash memory programming mode |

# DC Characteristics (1/3)

| Parameter                              | Symbol | Conditions                                                         |                                       | MIN. | TYP. | MAX.  | Unit |

|----------------------------------------|--------|--------------------------------------------------------------------|---------------------------------------|------|------|-------|------|

| Output current, high <sup>Note 1</sup> | Іон1   | Per pin for P00, P01, P10 to P17,<br>P30 to P33, P120              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -3.0  | mA   |

|                                        |        | Total of P00, P01, P10 to P17,<br>P30, P33, P120 <sup>Note 3</sup> | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -20.0 | mA   |

|                                        |        | Total of P31 and P32 <sup>Note 3</sup>                             | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -6.0  | mA   |

|                                        |        | Total <sup>Note 3</sup> of all pins                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -26.0 | mA   |

|                                        | Іон2   | Per pin for P121, P122                                             | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -100  | μA   |

| Output current, low <sup>Note 2</sup>  | Iol1   | Per pin for P00, P01, P10 to P17,<br>P30 to P33, P120              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 8.5   | mA   |

|                                        |        | Per pin for P60, P61                                               | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 15.0  | mA   |

|                                        |        | Total of P00, P01, P10 to P17,<br>P30, P33, P120 <sup>Note 3</sup> | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 20.0  | mA   |

|                                        |        | Total of P31, P32, P60, P61 <sup>Note 3</sup>                      | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 45.0  | mA   |

|                                        |        | Total of all pins <sup>Note 3</sup>                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 65.0  | mA   |

|                                        | IOL2   | Per pin for P121, P122                                             | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 400   | μA   |

Notes 1. Value of current at which the device operation is guaranteed even if the current flows from  $V_{DD}$  to an output pin.

- 2. Value of current at which the device operation is guaranteed even if the current flows from an output pin to GND.

- **3.** Specification under conditions where the duty factor is 70% (time for which current is output is  $0.7 \times t$  and time for which current is not output is  $0.3 \times t$ , where t is a specific time). The total output current of the pins at a duty factor of other than 70% can be calculated by the following expression.

- Where the duty factor of IoH is n%: Total output current of pins = (IoH  $\times$  0.7)/(n  $\times$  0.01)

- <Example> Where the duty factor is 50%, IoH = 20.0 mA

Total output current of pins =  $(20.0 \times 0.7)/(50 \times 0.01) = 28.0 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

## Serial Transfer Timing

## CSI10:

**Remark** m = 1, 2

# C.2 Register Index (In Alphabetical Order with Respect to Register Symbol)

# [A]

| ASIF6: Asynchronous serial interface transmission status register 6    |     |

|------------------------------------------------------------------------|-----|

| ASIM6: Asynchronous serial interface operation mode register 6         | 228 |

| ASIS6: Asynchronous serial interface reception error status register 6 | 230 |

|                                                                        |     |

|                                                                        |     |

# [B]

| RGC6: Baud rate generator control register 6 233 |

|--------------------------------------------------|

|--------------------------------------------------|

## [C]

| • •                                              |       |

|--------------------------------------------------|-------|

| CKSR6: Clock selection register 6                | . 232 |

| CMP01: 8-bit timer H compare register 01         | . 198 |

| CMP11: 8-bit timer H compare register 11         | . 198 |

| CR000: 16-bit timer capture/compare register 000 | . 116 |

| CR010: 16-bit timer capture/compare register 010 | . 116 |

| CR50: 8-bit timer compare register 50            | . 181 |

| CR51: 8-bit timer compare register 51            | . 181 |

| CRC00: Capture/compare control register 00       | . 121 |

| CSIC10: Serial clock selection register 10       | . 259 |

| CSIM10: Serial operation mode register 10        | . 258 |

|                                                  |       |

## [E]

| EGN: External interrupt falling edge enable register | 403 |

|------------------------------------------------------|-----|

| EGP: External interrupt rising edge enable register  | 403 |

## [I]

| F0H: Interrupt request flag register 0H            | 399 |

|----------------------------------------------------|-----|

| F0L: Interrupt request flag register 0L            | 399 |

| F1H: Interrupt request flag register 1H            | 399 |

| F1L: Interrupt request flag register 1L            |     |

| MS: Internal memory size switching register        | 454 |

| XS: Internal expansion RAM size switching register | 455 |

## [L]

| LVIM: Low-voltage detection register                 | 40 |

|------------------------------------------------------|----|

| LVIS: Low-voltage detection level selection register | 41 |

## [M]

| MCM: Main clock mode register         |     |

|---------------------------------------|-----|

| MK0H: Interrupt mask flag register 0H |     |

| MK0L: Interrupt mask flag register 0L | 401 |

| MK1H: Interrupt mask flag register 1H | 401 |

| MK1L: Interrupt mask flag register 1L | 401 |

| MOC: Main OSC control register        |     |

# [0]

| OSTS: Oscillation stabilization time select register         | 92, 414 |

|--------------------------------------------------------------|---------|

| -                                                            |         |

| OSTC: Oscillation stabilization time counter status register | 91. 413 |

| OSCCTL: Clock operation mode select register                 |         |

|                                                              |         |