Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Obsolete                                                                                                            |

| Core Processor                     | ARM® Cortex®-A8                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, DDR2, DDR3                                                                                                  |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100Mbps (1)                                                                                                      |

| SATA                               | SATA 1.5Gbps (1)                                                                                                    |

| USB                                | USB 2.0 (2), USB 2.0 + PHY (2)                                                                                      |

| Voltage - I/O                      | 1.3V, 1.8V, 2.775V, 3.3V                                                                                            |

| Operating Temperature              | -40°C ~ 85°C (TA)                                                                                                   |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 529-FBGA                                                                                                            |

| Supplier Device Package            | 529-FBGA (19x19)                                                                                                    |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx537cvv8b                                               |

### Introduction

- Multilevel memory system—The multilevel memory system of the i.MX53 is based on the L1 instruction and data caches, L2 cache, internal and external memory. The i.MX53 supports many types of external memory devices, including DDR2, low voltage DDR2, LPDDR2, DDR3, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>TM</sup>, and managed NAND including eMMC up to rev 4.4.

- Smart speed technology—The i.MX53 device has power management throughout the IC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product requiring levels of power far lower than industry expectations.

- Multimedia powerhouse—The multimedia performance of the i.MX53 processor ARM core is boosted by a multilevel cache system, Neon (including advanced SIMD, 32-bit single-precision floating point support) and vector floating point coprocessors. The system is further enhanced by a multi-standard hardware video codec, autonomous image processing unit (IPU), and a programmable smart DMA (SDMA) controller.

- Powerful graphics acceleration— The i.MX53 processors provide two independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator (33 Mtri/s, 200 Mpix/s, and 800 Mpix/s z-plane performance) and an OpenVG<sup>TM</sup> 1.1 2D graphics accelerator (200 Mpix/s).

- Interface flexibility—The i.MX53 processor supports connection to a variety of interfaces, including LCD controller for two displays and CMOS sensor interface, high-speed USB on-the-go with PHY, plus three high-speed USB hosts, multiple expansion card ports (high-speed MMC/SDIO host and others), 10/100 Ethernet controller, and a variety of other popular interfaces (PATA, UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, among others).

- Advanced security—The i.MX53 processors deliver hardware-enabled security features that enable secure e-commerce, digital rights management (DRM), information encryption, secure boot, and secure software downloads. For detailed information about the i.MX53 security features contact a Freescale representative.

The i.MX53 application processor is a follow-on to the i.MX51, with improved performance, power efficiency, and multimedia capabilities.

## 1.1 Functional Part Differences and Ordering Information

shows the functional differences between the different parts in the i.MX53 family.

Table 1 provides ordering information.

**Table 1. Ordering Information**

| Part Number   | Mask Set | CPU Frequency | Notes | Package <sup>1</sup>                          |

|---------------|----------|---------------|-------|-----------------------------------------------|

| MCIMX537CVV8C | N78C     | 800 MHz       | _     | 19 x 19 mm, 0.8 mm pitch BGA<br>Case TEPBGA-2 |

Case TEPBGA-2 is RoHS compliant, lead-free MSL (moisture sensitivity level) 3.

3

### 1.2 Features

The i.MX53 multimedia applications processor (AP) is based on the ARM Platform, which has the following features:

- MMU, L1 instruction and L1 data cache

- Unified L2 cache

- Maximum frequency of the core (including Neon, VFPv3 and L1 cache): 800 MHz

- Neon coprocessor (SIMD media processing architecture) and vector floating point (VFP-Lite) coprocessor supporting VFPv3

- TrustZone

The memory system consists of the following components:

- Level 1 cache:

- Instruction (32 Kbyte)

- Data (32 Kbyte)

- Level 2 cache:

- Unified instruction and data (256 Kbyte)

- Level 2 (internal) memory:

- Boot ROM, including HAB (64 Kbyte)

- Internal multimedia/shared, fast access RAM (128 Kbyte)

- Secure/non-secure RAM (16 Kbyte)

- External memory interfaces:

- 16/32-bit DDR2-800, LV-DDR2-800 or DDR3-800 up to 2 Gbyte

- 32-bit LPDDR2

- 8/16-bit NAND SLC/MLC Flash, up to 66 MHz, 4/8/14/16-bit ECC

- 8/16-bit NOR Flash, PSRAM, and cellular RAM.

- 32-bit multiplexed mode NOR Flash, PSRAM & cellular RAM.

- 8-bit Asynchronous (DTACK mode) EIM interface.

- All EIM pins are muxed on other interfaces (data with NFC pins). I/O muxing logic selects EIM port, as primary muxing at system boot.

- Samsung OneNAND<sup>TM</sup> and managed NAND including eMMC up to rev 4.4 (in muxed I/O mode)

The i.MX53 system is built around the following system on chip interfaces:

- 64-bit AMBA AXI v1.0 bus—used by ARM platform, multimedia accelerators (such as VPU, IPU, GPU3D, GPU2D) and the external memory controller (EXTMC) operating at 200 MHz.

- 32-bit AMBA AHB 2.0 bus—used by the rest of the bus master peripherals operating at 133 MHz.

- 32-bit IP bus—peripheral bus used for control (and slow data traffic) of the most system peripheral devices operating at 66 MHz.

## 3 Modules List

The i.MX53 processor contains a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

Table 2. i.MX53 Digital and Analog Blocks

| Block<br>Mnemonic          | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM                        | ARM Platform                                                                        | ARM                                     | The ARM Cortex <sup>TM</sup> A8 platform consists of the ARM processor version r2p5 (with TrustZone) and its essential sub-blocks. It contains the 32 Kbyte L1 instruction cache, 32 Kbyte L1 data cache, Level 2 cache controller and a 256 Kbyte L2 cache. The platform also contains an event monitor and debug modules. It also has a NEON coprocessor with SIMD media processing architecture, a register file with 32/64-bit general-purpose registers, an integer execute pipeline (ALU, Shift, MAC), dual single-precision floating point execute pipelines (FADD, FMUL), a load/store and permute pipeline and a non-pipelined vector floating point (VFP Lite) coprocessor supporting VFPv3. |

| ASRC                       | Asynchronous<br>Sample Rate<br>Converter                                            | Multimedia<br>Peripherals               | The asynchronous sample rate converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120 dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                                                                                                                                                                |

| AUDMUX                     | Digital Audio<br>Multiplexer                                                        | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and synchronous data routing between host serial interfaces (for example, SSI1, SSI2, and SSI3) and peripheral serial interfaces (audio and voice codecs). The AUDMUX has seven ports (three internal and four external) with identical functionality and programming models. A desired connectivity is achieved by configuring two or more AUDMUX ports.                                                                                                                                                                                                                                                                                  |

| CAMP-1<br>CAMP-2           | Clock Amplifier                                                                     | Clocks,<br>Resets, and<br>Power Control | Clock amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CCM<br>GPC<br>SRC          | Clock Control<br>Module<br>Global Power<br>Controller<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, as well as for system power management. The system includes four PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CSPI<br>ECSPI-1<br>ECSPI-2 | Configurable<br>SPI, Enhanced<br>CSPI                                               | Connectivity<br>Peripherals             | Full-duplex enhanced synchronous serial interface, with data rates 16-60 Mbit/s. It is configurable to support master/slave modes. In Master mode it supports four slave selects for multiple peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CSU                        | Central Security<br>Unit                                                            | Security                                | The central security unit (CSU) is responsible for setting comprehensive security policy within the i.MX53 platform, and for sharing security information between the various security modules. The security control registers (SCR) of the CSU are set during boot time by the high assurance boot (HAB) code and are locked to prevent further writing.                                                                                                                                                                                                                                                                                                                                              |

### **Modules List**

Table 2. i.MX53 Digital and Analog Blocks (continued)

| Block<br>Mnemonic                                                  | Block Name                        | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------|-----------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7 | General Purpose<br>I/O Modules    | System<br>Control<br>Peripherals | These modules are used for general purpose input/output to external ICs. Each GPIO module supports up to 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPT                                                                | General Purpose<br>Timer          | Timer<br>Peripherals             | Each GPT is a 32-bit "free-running" or "set and forget" mode timer with a programmable prescaler and compare and capture register. A timer counter value can be captured using an external event, and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in "set and forget" mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPU3D                                                              | Graphics<br>Processing Unit       | Multimedia<br>Peripherals        | The GPU, version 3, provides hardware acceleration for 2D and 3D graphics algorithms with sufficient processor power to run desk-top quality interactive graphics applications on displays up to HD1080 resolution. It supports color representation up to 32 bits per pixel. GPU enables high-performance mobile 3D and 2D vector graphics at rates up to 33 Mtriangles/s, 200 Mpix/s, 800 Mpix/s (z).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPU2D                                                              | Graphics<br>Processing<br>Unit-2D | Multimedia<br>Peripherals        | The GPU2D version 1, provides hardware acceleration for 2D graphic algorithms with sufficient processor power to run desk-top quality interactive graphics applications on displays up to HD1080 resolution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12C-1<br>12C-2<br>12C-3                                            | I <sup>2</sup> C Controller       | Connectivity<br>Peripherals      | I <sup>2</sup> C provides serial interface for controlling peripheral devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IIM                                                                | IC Identification<br>Module       | Security                         | The IC identification module (IIM) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically programmable poly fuses (e-Fuses). The IIM also provides a set of volatile software-accessible signals that can be used for software control of hardware elements not requiring non-volatility. The IIM provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals requiring permanent non-volatility. The IIM also provides up to 28 volatile control signals. The IIM consists of a master controller, a software fuse value shadow cache, and a set of registers to hold the values of signals visible outside the module.  IIM interfaces to the electrical fuse array (split to banks). Enabled to set up boot modes, security levels, security keys and many other system parameters.  i.MX53A consists of 4 x 256-bit + 1 x 128-bit fuse-banks (total 1152 bits) through IIM interface. |

Table 2. i.MX53 Digital and Analog Blocks (continued)

| Block<br>Mnemonic       | Block Name                          | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|-------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECRAM                  | Secure /<br>Non-secure RAM          | Internal<br>Memory               | Secure / non-secure Internal RAM, controlled by SCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SJC                     | Secure JTAG<br>Interface            | System<br>Control<br>Peripherals | JTAG manipulation is a known hacker's method of executing unauthorized program code, getting control over secure applications, and running code in privileged modes. The JTAG port provides a debug access to several hardware blocks including the ARM processor and the system bus. The JTAG port must be accessible during platform initial laboratory bring-up, manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. However, in order to properly secure the system, unauthorized JTAG usage should be strictly forbidden. In order to prevent JTAG manipulation while allowing access for manufacturing tests and software debugging, the i.MX53 processor incorporates a mechanism for regulating JTAG access. SJC provides four different JTAG security modes that can be selected through an e-fuse configuration. |

| SPBA                    | Shared<br>Peripheral Bus<br>Arbiter | System<br>Control<br>Peripherals | SPBA (shared peripheral bus arbiter) is a two-to-one IP bus interface (IP bus) arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SPDIF                   | Sony Philips<br>Digital Interface   | Multimedia<br>Peripherals        | A standard digital audio transmission protocol developed jointly by the Sony and Philips corporations. Both transmitter and receiver functionalists are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SRTC                    | Secure Real<br>Time Clock           | Security                         | The SRTC incorporates a special system state retention register (SSRR) that stores system parameters during system shutdown modes. This register and all SRTC counters are powered by dedicated supply rail NVCC_SRTC_POW. The NVCC_SRTC_POW can be energized separately even if all other supply rails are shut down. This register is helpful for storing warm boot parameters. The SSRR also stores the system security state. In case of a security violation, the SSRR mark the event (security violation indication).                                                                                                                                                                                                                                                                                                                                               |

| SSI-1<br>SSI-2<br>SSI-3 | I2S/SSI/AC97<br>Interface           | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface used on the i.MX53A processor to provide connectivity with off-chip audio peripherals. The SSI interfaces connect internally to the AUDMUX for mapping to external ports. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock/frame sync options.  Each SSI has two pairs of 8 x 24 FIFOs and hardware support for an external DMA controller in order to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream, which reduces CPU overhead in use cases where two time slots are being used simultaneously.                                                                                                                                                      |

### **Modules List**

Table 2. i.MX53 Digital and Analog Blocks (continued)

| Block<br>Mnemonic                              | Block Name                                 | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------|--------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPTP                                           | IEEE1588<br>Precision Time<br>Protocol     | Connectivity<br>Peripherals      | The IEEE 1588-2002 (version 1) standard defines a precision time protocol (PTP) - which is a time-transfer protocol that enables synchronization of networks (for example, Ethernet), to a high degree of accuracy and precision.  The IEEE1588 hardware assist is composed of the two blocks: time stamp unit and real time clock, which provide the timestamping protocol's functionality, generating and reading the needed timestamps.  The hardware-assisted implementation delivers more precise clock synchronization at significantly lower CPU load compared to purely software implementations. |

| Temperature<br>Monitor                         | (Part of SATA<br>Block)                    | System<br>Control<br>Peripherals | The temperature sensor is an internal module to the i.MX53 that monitors the die temperature. The monitor is capable in generating SW interrupt, or trigger the CCM, to reduce the core operating frequency.                                                                                                                                                                                                                                                                                                                                                                                              |

| TVE                                            | TV Encoder                                 | Multimedia                       | The TV encoder, version 2.1 is implemented in conjunction with the image processing unit (IPU) allowing handheld devices to display captured still images and video directly on a TV or LCD projector. It supports composite PAL/NTSC, VGA, S-video, and component up to HD1080p analog video outputs.                                                                                                                                                                                                                                                                                                    |

| TZIC                                           | TrustZone Aware<br>Interrupt<br>Controller | ARM/Control                      | The TrustZone interrupt controller (TZIC) collects interrupt requests from all i.MX53 sources and routes them to the ARM core. Each interrupt can be configured as a normal or a secure interrupt. Software Force Registers and software Priority Masking are also supported.                                                                                                                                                                                                                                                                                                                             |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                             | Connectivity<br>Peripherals      | <ul> <li>Each of the UART blocks supports the following serial data transmit/receive protocols and configurations:</li> <li>7 or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd, or none)</li> <li>Programmable bit-rates up to 4 Mbps. This is a higher max baud rate relative to the 1.875 Mbps, which is specified by the TIA/EIA-232-F standard.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                    |

| USB                                            | USB Controller                             | Connectivity<br>Peripherals      | USB supports USB2.0 480 MHz, and contains:  One high-speed OTG sub-block with integrated HS USB PHY  One high-speed host sub-block with integrated HS USB PHY  Two identical high-speed Host modules The high-speed OTG module, which is internally connected to the HS USB PHY, is equipped with transceiver-less logic to enable on-board USB connectivity without USB transceivers All the USB ports are equipped with standard digital interfaces (ULPI, HS IC-USB) and transceiver-less logic to enable onboard USB connectivity without USB transceivers.                                           |

### **Electrical Characteristics**

## 3.1 Special Signal Considerations

The package contact assignments can be found in Section 6, "Package Information and Contact Assignments." Signal descriptions are defined in the i.MX53 Reference Manual. Special signal considerations information is contained in Chapter 1 of *i.MX53 System Development User's Guide* (MX53UG).

## 4 Electrical Characteristics

This section provides the device and module-level electrical characteristics for the i.MX53 processor.

## 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 3 for a quick reference to the individual tables and sections.

For these characteristics, ...

Absolute Maximum Ratings

Table 4 on page 16

TEPBGA-2 Package Thermal Resistance Data

i.MX53 Operating Ranges

Table 6 on page 18

External Clock Sources

Table 7 on page 20

Maximal Supply Currents

Table 8 on page 20

USB Interface Current Consumption

Table 9 on page 23

Table 3. i.MX53 Chip-Level Conditions

## 4.1.1 Absolute Maximum Ratings

### **CAUTION**

Stresses beyond those listed under Table 4 may affect reliability or cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the Operating Ranges table is not implied.

| Parameter Description          | Symbol                         | Min  | Max  | Unit |

|--------------------------------|--------------------------------|------|------|------|

| Peripheral Core Supply Voltage | VCC                            | -0.3 | 1.35 | V    |

| ARM Core Supply Voltage        | VDDGP                          | -0.3 | 1.4  | V    |

| Supply Voltage UHVIO           | Supplies denoted as I/O Supply | -0.5 | 3.6  | V    |

| Supply Voltage for non UHVIO   | Supplies denoted as I/O Supply | -0.5 | 3.3  | V    |

| USB VBUS                       | VBUS                           | _    | 5.25 | V    |

**Table 4. Absolute Maximum Ratings**

i.MX53 Applications Processors for Industrial Products, Rev. 6

# 4.1.6 USB-OH-3 (OTG + 3 Host ports) Module and the Two USB PHY (OTG and H1) Current Consumption

Table 9 shows the USB interface current consumption.

**Table 9. USB Interface Current Consumption**

| Parameter                            | Condition    | Conditions |     | Max | Unit |

|--------------------------------------|--------------|------------|-----|-----|------|

|                                      | Full Speed   |            | 5.5 | 6   | mA   |

| Analog Supply 3.3 V<br>USB_H1_VDDA33 | Full Speed   | TX         | 7   | 8   |      |

| USB_OTG_VDDA33                       | High Speed   | RX         | 5   | 6   |      |

|                                      | Tilgii Speed | TX         | 5   | 6   |      |

|                                      | Full Cross d | RX         | 6.5 | 7   | mA   |

| Analog Supply 2.5 V<br>USB_H1_VDDA25 | Full Speed   | TX         | 6.5 | 7   |      |

| USB_OTG_VDDA25                       | High Chood   |            | 12  | 13  |      |

|                                      | High Speed   | TX         | 21  | 22  |      |

|                                      | Full Speed   | RX         | 8   | _   | mA   |

| Digital Supply                       | Full Speed   | TX         | 8   | _   |      |

| VCC (1.2 V)                          | High Speed   | RX         | 8   | _   |      |

|                                      | Tilgit Speed | TX         | 8   | _   |      |

## 4.2 Power Supply Requirements and Restrictions

The system design must comply with power-up sequence, power-down sequence and steady state guidelines as described in this section to guarantee the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the i.MX53 processor (worst-case scenario)

## 4.2.1 Power-Up Sequence

The following observations should be considered:

- The consequent steps in power up sequence should not start before the previous step supplies have been stabilized within 90-110% of their nominal voltage, unless stated otherwise.

- NVCC\_SRTC\_POW should remain powered ON continuously, to maintain internal real-time clock status. Otherwise, it has to be powered ON together with VCC, or preceding VCC.

- The VCC should be powered ON together, or any time after NVCC\_SRTC\_POW.

- NVCC\_CKIH should be powered ON after VCC is stable and before other I/O supplies (NVCC\_xxx) are powered ON.

### **NOTE**

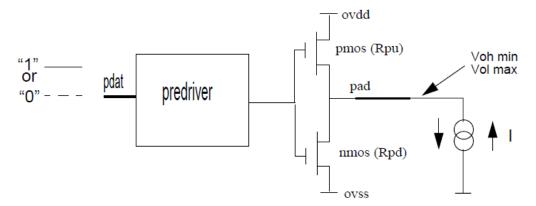

The term 'OVDD' in this section refers to the associated supply rail of an input or output. The association is shown in Table 111.

Figure 3. Circuit for Parameters Voh and Vol for I/O Cells

### 4.3.1 General Purpose I/O (GPIO) DC Parameters

The parameters in Table 10 are guaranteed per the operating ranges in Table 6, unless otherwise noted. Table 10 shows DC parameters for GPIO pads, operating at two supply ranges:

- 1.1 V to 1.3 V

- 1.65 V to 3.1 V

Table 10. GPIO I/O DC Electrical Characteristics

| Parameter                                   | Symbol | Test Conditions                  | Min         | Тур          | Max        | Unit |

|---------------------------------------------|--------|----------------------------------|-------------|--------------|------------|------|

| High-level output voltage <sup>1</sup>      | Voh    | lout = -0.8 mA                   | OVDD - 0.15 | _            | _          | ٧    |

| Low-level output voltage <sup>1</sup>       | Vol    | lout = 0.8 mA                    | _           | _            | 0.15       | ٧    |

| High-Level DC input voltage <sup>1, 2</sup> | VIH    | _                                | 0.7 × OVDD  | _            | OVDD       | ٧    |

| Low-Level DC input voltage <sup>1, 2</sup>  | VIL    | _                                | 0           | _            | 0.3 × OVDD | ٧    |

| Input Hysteresis                            | VHYS   | OVDD = 1.875 V<br>OVDD = 2.775 V | 0.25        | 0.34<br>0.45 | _          | V    |

| Schmitt trigger VT+ <sup>2, 3</sup>         | VT+    | _                                | 0.5 × OVDD  | _            | _          | ٧    |

| Schmitt trigger VT-2,3                      | VT-    | _                                | _           | _            | 0.5 × OVDD | ٧    |

| Input current (no pull-up/down)             | lin    | Vin = OVDD or 0                  | _           | _            | 10         | μΑ   |

| Input current (22 kΩ Pull-up)               | lin    | Vin = 0 V<br>Vin = OVDD          | _           | _            | 161<br>10  | μΑ   |

| Input current (47 kΩ Pull-up)               | lin    | Vin = 0 V<br>Vin = OVDD          | _           | _            | 76<br>10   | μΑ   |

| Input current (100 kΩ Pull-up)              | lin    | Vin = 0 V<br>Vin= OVDD           | _           | _            | 40<br>10   | μΑ   |

i.MX53 Applications Processors for Industrial Products, Rev. 6

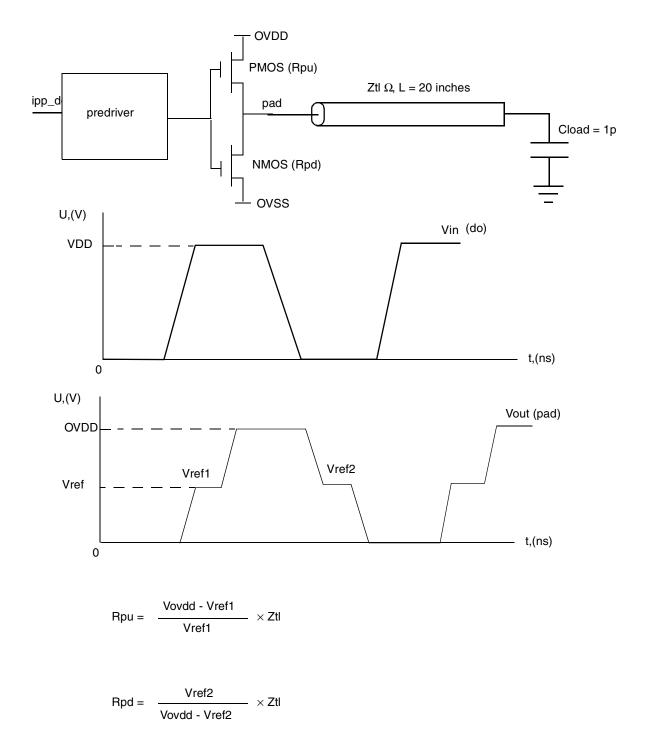

Figure 4. Impedance Matching Load for Measurement

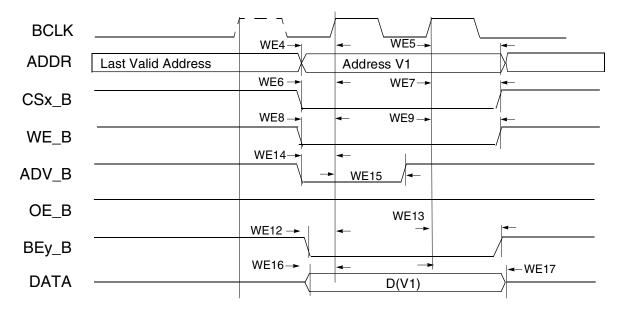

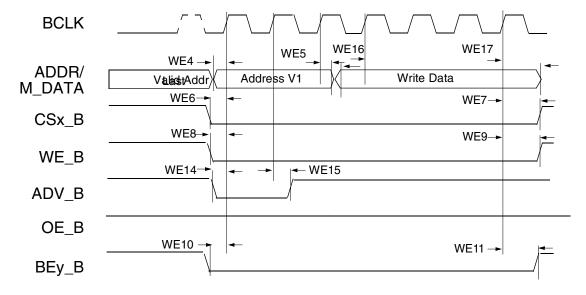

Figure 19. Synchronous Memory, Write Access, WSC=1, WBEA=0, and WADVN=0

Figure 20. Muxed Address/Data (A/D) Mode, Synchronous Write Access, WSC=6, ADVA=0, ADVN=1, and ADH=1

### NOTE

In 32-bit muxed address/data (A/D) mode the 16 MSBs are driven on the data bus.

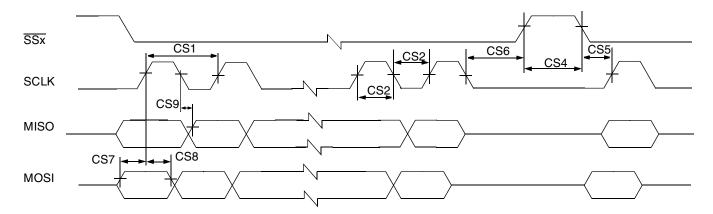

| ID   | Parameter                                          | Symbol                 | Min | Max | Unit |

|------|----------------------------------------------------|------------------------|-----|-----|------|

| CS1  | SCLK Cycle Time                                    | t <sub>clk</sub>       | 60  | _   | ns   |

| CS2  | SCLK High or Low Time                              | t <sub>SW</sub>        | 26  | _   | ns   |

| CS3  | SCLK Rise or Fall <sup>1</sup>                     | t <sub>RISE/FALL</sub> | _   | _   | ns   |

| CS4  | SSx pulse width                                    | t <sub>CSLH</sub>      | 26  | _   | ns   |

| CS5  | SSx Lead Time (Slave Select setup time)            | t <sub>SCS</sub>       | 26  | _   | ns   |

| CS6  | SSx Lag Time (SS hold time)                        | t <sub>HCS</sub>       | 26  | _   | ns   |

| CS7  | MOSI Propagation Delay (C <sub>LOAD</sub> = 20 pF) | t <sub>PDmosi</sub>    | -1  | 21  | ns   |

| CS8  | MISO Setup Time                                    | t <sub>Smiso</sub>     | 5   | _   | ns   |

| CS9  | MISO Hold Time                                     | t <sub>Hmiso</sub>     | 5   | _   | ns   |

| CS10 | RDY to SSx Time <sup>2</sup>                       | t <sub>SDRY</sub>      | 5   | _   | ns   |

<sup>1</sup> See specific I/O AC parameters Section 4.5, "I/O AC Parameters"

#### 4.7.2.2 **CSPI Slave Mode Timing**

Figure 33 depicts the timing of CSPI in slave mode. Timing characteristics were not available at the time of publication.

Figure 33. CSPI/ECSPI Slave Mode Timing Diagram

i.MX53 Applications Processors for Industrial Products, Rev. 6 66 Freescale Semiconductor

<sup>&</sup>lt;sup>2</sup> SPI\_RDY is sampled internally by ipg\_clk and is asynchronous to all other CSPI signals.

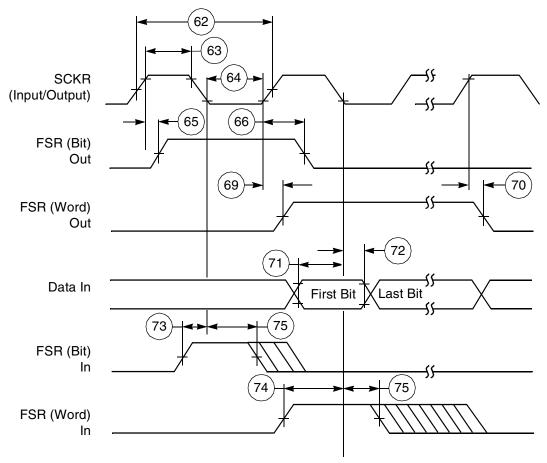

Figure 35. ESAI Receiver Timing

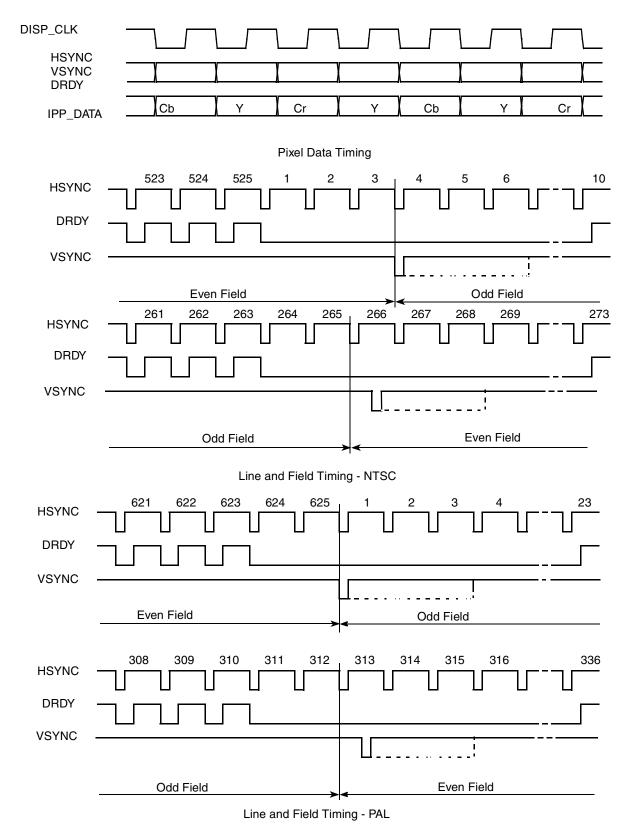

Figure 51. TV Encoder Interface Timing Diagram

i.MX53 Applications Processors for Industrial Products, Rev. 6

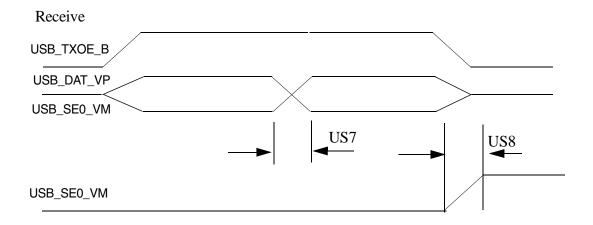

Figure 90. USB Receive Waveform in DAT\_SE0 Bidirectional Mode

Table 92. Definitions of USB Waveform in DAT\_SE0 Bi — Directional Mode

| No. | Parameter         | Signal Name | Direction | Min  | Max  | Unit | Conditions /<br>Reference Signal |

|-----|-------------------|-------------|-----------|------|------|------|----------------------------------|

| US1 | TX Rise/Fall Time | USB_DAT_VP  | Out       | _    | 5.0  | ns   | 50 pF                            |

| US2 | TX Rise/Fall Time | USB_SE0_VM  | Out       | _    | 5.0  | ns   | 50 pF                            |

| US3 | TX Rise/Fall Time | USB_TXOE_B  | Out       | _    | 5.0  | ns   | 50 pF                            |

| US4 | TX Duty Cycle     | USB_DAT_VP  | Out       | 49.0 | 51.0 | %    | _                                |

| US7 | RX Rise/Fall Time | USB_DAT_VP  | ln        | _    | 3.0  | ns   | 35 pF                            |

| US8 | RX Rise/Fall Time | USB_SE0_VM  | ln        | _    | 3.0  | ns   | 35 pF                            |

Table 111. 19 x 19 mm Signal Assignments, Power Rails, and I/O (continued)

|                      | 0                     |               | 1/0 D - #          | Out of Reset Condition <sup>1</sup> |                   |                                                                                                    |           |                  |  |  |  |  |  |

|----------------------|-----------------------|---------------|--------------------|-------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|-----------|------------------|--|--|--|--|--|

| Contact Name         | Contact<br>Assignment | Power Rail    | I/O Buffer<br>Type | Alt.<br>Mode                        | Block<br>Instance | Block I/O                                                                                          | Direction | Config.<br>Value |  |  |  |  |  |

| DRAM_A3              | N20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[3]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_A4              | K20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[4]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_A5              | N21                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[5]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_A6              | M22                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[6]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_A7              | N22                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[7]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_A8              | N23                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[8]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_A9              | M21                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_A[9]                                                                                      | Output    | Low              |  |  |  |  |  |

| DRAM_CALIBRA<br>TION | M23                   | NVCC_EMI_DRAM | special            | _                                   | ı                 | (used in DRAM<br>driver<br>calibration. See<br>Section 3.1,<br>"Special Signal<br>Considerations") | Input     | -                |  |  |  |  |  |

| DRAM_CAS             | L18                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_CA<br>S                                                                                   | Output    | High             |  |  |  |  |  |

| DRAM_CS0             | K18                   | NVCC_EMI_DRAM | DDR3               | ALTO EXTMC                          |                   | emi_DRAM_CS[<br>0]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_CS1             | P19                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_CS[<br>1]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D0              | H20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[0<br>]                                                                                  | Output    | High             |  |  |  |  |  |

| DRAM_D1              | G21                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>]                                                                                  | Output    | High             |  |  |  |  |  |

| DRAM_D10             | E22                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>0]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D11             | D20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>1]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D12             | E23                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>2]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D13             | C23                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>3]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D14             | F23                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>4]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D15             | C22                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>5]                                                                                 | Output    | High             |  |  |  |  |  |

| DRAM_D16             | U20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[1<br>6]                                                                                 | Output    | High             |  |  |  |  |  |

Table 111. 19 x 19 mm Signal Assignments, Power Rails, and I/O (continued)

|                    | 0                     |               | 1/0 D.#-           | Out of Reset Condition <sup>1</sup> |                   |                       |           |                  |  |  |  |  |  |

|--------------------|-----------------------|---------------|--------------------|-------------------------------------|-------------------|-----------------------|-----------|------------------|--|--|--|--|--|

| Contact Name       | Contact<br>Assignment | Power Rail    | I/O Buffer<br>Type | Alt.<br>Mode                        | Block<br>Instance | Block I/O             | Direction | Config.<br>Value |  |  |  |  |  |

| DRAM_D6            | J22                   | DDR3          | ALT0               | EXTMC                               | emi_DRAM_D[6      | Output                | High      |                  |  |  |  |  |  |

| DRAM_D7            | G22                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[7<br>]     | Output    | High             |  |  |  |  |  |

| DRAM_D8            | E21                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[8<br>]     | Output    | High             |  |  |  |  |  |

| DRAM_D9            | D21                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_D[9<br>]     | Output    | High             |  |  |  |  |  |

| DRAM_DQM0          | H21                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_DQ<br>M[0]   | Output    | Low              |  |  |  |  |  |

| DRAM_DQM1          | E20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_DQ<br>M[1]   | Output    | Low              |  |  |  |  |  |

| DRAM_DQM2          | T20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_DQ<br>M[2]   | Output    | Low              |  |  |  |  |  |

| DRAM_DQM3          | W20                   | NVCC_EMI_DRAM | DDR3               | ALTO EXTMC                          |                   | emi_DRAM_DQ<br>M[3]   | Output    | Low              |  |  |  |  |  |

| DRAM_RAS           | J19                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_RA<br>S      | Output    | High             |  |  |  |  |  |

| DRAM_RESET         | P18                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_RE<br>SET    | Output    | Low              |  |  |  |  |  |

| DRAM_SDBA0         | R19                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_SD<br>BA[0]  | Output    | Low              |  |  |  |  |  |

| DRAM_SDBA1         | P20                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_SD<br>BA[1]  | Output    | Low              |  |  |  |  |  |

| DRAM_SDBA2         | N19                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_SD<br>BA[2]  | Output    | Low              |  |  |  |  |  |

| DRAM_SDCKE0        | H19                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_SD<br>CKE[0] | Output    | Low              |  |  |  |  |  |

| DRAM_SDCKE1        | T19                   | NVCC_EMI_DRAM | DDR3               | ALT0                                | EXTMC             | emi_DRAM_SD<br>CKE[1] | Output    | Low              |  |  |  |  |  |

| DRAM_SDCLK_<br>0   | K23                   | NVCC_EMI_DRAM | DDR3CLK            | ALT0                                | EXTMC             | emi_DRAM_SD<br>CLK0   | Output    | Floating         |  |  |  |  |  |

| DRAM_SDCLK_<br>0_B | K22                   | NVCC_EMI_DRAM | DDR3CLK            | ALT0                                | EXTMC             | emi_DRAM_SD<br>CLK0_B | Output    | Floating         |  |  |  |  |  |

| DRAM_SDCLK_<br>1   | P22                   | NVCC_EMI_DRAM | DDR3CLK            | ALT0                                | EXTMC             | emi_DRAM_SD<br>CLK1   | Output    | Floating         |  |  |  |  |  |

| DRAM_SDCLK_<br>1_B | P23                   | NVCC_EMI_DRAM | DDR3CLK            | ALT0                                | EXTMC             | emi_DRAM_SD<br>CLK1_B | Output    | Floating         |  |  |  |  |  |

Table 111. 19 x 19 mm Signal Assignments, Power Rails, and I/O (continued)

|              | Comtact               |               | I/O Duffer         |              | O                 | tion <sup>1</sup>       | n <sup>1</sup>      |                    |  |  |

|--------------|-----------------------|---------------|--------------------|--------------|-------------------|-------------------------|---------------------|--------------------|--|--|

| Contact Name | Contact<br>Assignment | Power Rail    | I/O Buffer<br>Type | Alt.<br>Mode | Block<br>Instance | Block I/O               | Direction           | Config.<br>Value   |  |  |

| EIM_DA10     | AB7                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[10] | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA11     | AC6                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[11] | Input               | 100 KΩ<br>PU       |  |  |

| EIM_DA12     | V10                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[12] | Input               | 100 KΩ<br>PU       |  |  |

| EIM_DA13     | AC7                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[13] | Input               | 100 KΩ<br>PU       |  |  |

| EIM_DA14     | Y10                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[14] | Input               | 100 KΩ<br>PU       |  |  |

| EIM_DA15     | AA9                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[15] | Input               | 100 KΩ<br>PU       |  |  |

| EIM_DA2      | AA7                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[2]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA3      | W9                    | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[3]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA4      | AB6                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[4]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA5      | V9                    | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[5]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA6      | Y9                    | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[6]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA7      | AC5                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[7]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA8      | AA8                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[8]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_DA9      | W10                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_NAND_EIM<br>_DA[9]  | Input <sup>2</sup>  | 100 KΩ<br>PU       |  |  |

| EIM_EB0      | AC3                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_EIM_EB[0]           | Output <sup>2</sup> | _                  |  |  |

| EIM_EB1      | AB5                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_EIM_EB[1]           | Output <sup>2</sup> | _                  |  |  |

| EIM_EB2      | Y3                    | NVCC_EIM_MAIN | UHVIO              | ALT1         | GPIO-2            | gpio2_GPIO[30]          | Input               | 100 KΩ<br>PU       |  |  |

| EIM_EB3      | Y4                    | NVCC_EIM_MAIN | UHVIO              | ALT1         | GPIO-2            | gpio2_GPIO[31]          | Input               | Input 100 KΩ<br>PU |  |  |

| EIM_LBA      | AA6                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_EIM_LBA             | Output <sup>2</sup> | _                  |  |  |

| EIM_OE       | V8                    | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_EIM_OE              | Output              | _                  |  |  |

| EIM_RW       | AB4                   | NVCC_EIM_MAIN | UHVIO              | ALT0         | EXTMC             | emi_EIM_RW              | Output              | _                  |  |  |

Table 112. 19 x 19 mm, 0.8 mm Pitch Ball Map (continued)

|             |             |            |              |            |             |             | 1            |         | 1             |               |               | 1           | 1           | 1            |               | 1              | 1              |               |             | 1          | 1        |              | 1 .            | 1           |

|-------------|-------------|------------|--------------|------------|-------------|-------------|--------------|---------|---------------|---------------|---------------|-------------|-------------|--------------|---------------|----------------|----------------|---------------|-------------|------------|----------|--------------|----------------|-------------|

| Ь           | CSIO_PIXCLK | CSIO_MCLK  | CSIO_DATA_EN | CSIO_VSYNC | PATA_DATA15 | PATA_DATA14 | GND          | GNÐ     | NCC           | GND           | NCC           | GND         | VCC         | GND          | NCC           | GND            | NVCC_EMI_DRAM  | DRAM_RESET    | DRAM_CS1    | DRAM_SDBA1 | GND      | DRAM_SDCLK_1 | DRAM_SDCLK_1_B | ۵           |

| æ           | CSI0_DAT4   | CSI0_DAT5  | CSI0_DAT7    | CSI0_DAT9  | CSI0_DAT10  | CSI0_DAT6   | NVCC_CSI     | NCC     | GND           | NCC           | GND           | NCC         | GND         | NCC          | GND           | NCC            | GND            | DRAM_SDODT1   | DRAM_SDBA0  | GND        | DRAM_D19 | DRAM_D21     | DRAM_D23       | Я           |

| F           | CSI0_DAT8   | CSI0_DAT11 | CSI0_DAT12   | CSI0_DAT16 | CSI0_DAT17  | CSI0_DAT13  | VCC          | GND     | VCC           | GND           | VCC           | NVCC_NANDF  | VCC         | GND          | VCC           | GND            | VCC            | NVCC_EMI_DRAM | DRAM_SDCKE1 | DRAM_DQM2  | DRAM_D17 | DRAM_SDQS2   | DRAM_SDQS2_B   | _           |

| D           | CSI0_DAT14  | CSI0_DAT15 | CSI0_DAT18   | CSI0_DAT19 | EIM_D17     | EIM_D16     | NVCC_EIM_SEC | NCC     | NVCC_EIM_MAIN | NVCC_EIM_MAIN | NANDF_RB0     | VDDA        | NVCC_LVDS   | NVCC_LVDS_BG | GND           | TVDAC_DHVDD    | TVDAC_AHVDDRGB | VCC           | GND         | DRAM_D16   | DRAM_D18 | DRAM_D22     | DRAM_D20       | n           |

| >           | EIM_D18     | EIM_D19    | EIM_D21      | EIM_D27    | EIM_D26     | EIM_A23     | EIM_A17      | EIM_OE  | EIM_DA5       | EIM_DA12      | NVCC_SRTC_POW | NVCC_XTAL   | NANDF_CS1   | NANDF_CS2    | GND           | TVDAC_AHVDDRGB | GPIO_11        | GND           | GND         | GND        | GND      | GND          | DRAM_D29       | ^           |

| W           | EIM_D20     | EIM_D22    | EIM_D25      | EIM_D30    | EIM_D31     | EIM_A25     | EIM_A19      | EIM_CS0 | EIM_DA3       | EIM_DA9       | EIM_BCLK      | NANDF_CS0   | NANDF_CS3   | PMIC_ON_REQ  | PMIC_STBY_REQ | GPIO_10        | GPIO_12        | GPIO_14       | GND         | DRAM_DQM3  | DRAM_D25 | DRAM_D27     | DRAM_D31       | W           |

| <b>&gt;</b> | EIM_D23     | EIM_D24    | EIM_EB2      | EIM_EB3    | EIM_A24     | EIM_A20     | EIM_CS1      | EIM_DA0 | EIM_DA6       | EIM_DA14      | NANDF_ALE     | LVDS1_TX3_P | LVDS1_CLK_P | GND          | GND           | LVDS0_TX2_N    | LVDS0_TX0_N    | TVDAC_VREF    | GND         | DRAM_D24   | DRAM_D26 | DRAM_SDQS3   | DRAM_SDQS3_B   | <b>&gt;</b> |

# 7 Revision History

Table 113 provides a revision history for this data sheet.

Table 113. i.MX53 Data Sheet Document Revision History

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 6         | 03/2013 | In Table 1, "Ordering Information" removed MCIMX535DVV2C, as it no longer exists.  In Table 6, "i.MX53 Operating Ranges," updated minimum values of LVDS interface supply (NVCC_LVDS) and LVDS band gap supply (NVCC_LVDS_BG) to 2.375 volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Rev. 5         | 09/2012 | <ul> <li>In Table 1, "Ordering Information," on page 2," renamed "Features" column as "CPU Frequency."</li> <li>In Section 1.2, "Features:"  —Changed "SATA I" to "SATA II" under Hard disk drives bullet  —Added a new bullet item to mention support for tamper detection mechanism</li> <li>In Section 1.2, "Features," added a new bullet item to mention support for FlexCAN feature.</li> <li>Removed the note shown at the end of Section 1.2, "Features."</li> <li>In Table 2, "i.MX53 Digital and Analog Blocks," on page 7, removed details of MPEG2 encoder, as this is not supported on i.MX53.</li> <li>In Table 6, "i.MX53 Operating Ranges," on page 18:  —Changed VDDGP max voltage, for all frequency ranges and for STOP mode, to 1.15 V  —Updated footnote on TVDAC_DHVDD and TVDAC_AHVDDRGB</li> <li>In Table 8, "Maximal Supply Currents," on page 20:  —Corrected power line name, MVCC_XTAL, to NVCC_XTAL  —Added a footnote on NVCC_EMI_DRAM  —Updated max current value and added a footnote for power line, NVCC_SRTC_POW  —Removed duplicate entries for NVCC_EMI_DRAM and NVCC_XTAL</li> <li>In Section 4.2.3, "Power Supplies Usage," updated the fourth bullet item.</li> <li>In Figure 25, "Asynchronous A/D Muxed Write Access," on page 58, renamed "WE41" as "WE41A" and shifted its position to left.</li> <li>In Table 57, "Camera Input Signal Cross Reference, Format and Bits Per Cycle," on page 80, added a footnote on "YCbCr 8 bits 2 cycles" column header.</li> </ul>                                                          |

| Rev. 4         | 11/2011 | <ul> <li>In Section 1, "Introduction," changed 1 GHz to 1.2 GHz in the second paragraph and updated the bulleted list after the second paragraph.</li> <li>In Table 1, "Ordering Information," on page 2:         —Removed part numbers "PCIMX535DVV1C" and "MCIMX538DZK1C"         —Added a new part number "MCIMX535DVV2C"         —Updated package information for part number "PCIMX538DZK1C"         —Updated the second footnote</li> <li>In Section 1.2, "Features," changed "Target frequency" to "Maximum frequency" and 1 GHz to 1–1.2 GHz in the third bullet item of the first bulleted list.</li> <li>In Table 2, "i.MX53 Digital and Analog Blocks," on page 7, removed "Sorenson H.263 decode, 4CIF resolution, 8 Mbps bit rate" from VPU brief description.</li> <li>In Table 4, "Absolute Maximum Ratings," on page 16, changed the maximum voltage for VDDGP from 1.35V to 1.4V.</li> <li>In Table 6, "i.MX53 Operating Ranges," on page 18:         —Added a row and a footnote for "ARM core supply voltage f<sub>ARM</sub> ≤ 1200 MHz" parameter of VDDGP —Added a new footnote for "Peripheral supply voltage" parameter of VCC —Updated the footnote for "Junction temperature" parameter</li> <li>In Section 1.2, "Features," changed "Target frequency" to "Maximum frequency" in the third bullet item of the first bulleted list.</li> <li>In Table 2, "i.MX53 Digital and Analog Blocks," on page 7, removed "Sorenson H.263 decode, 4CIF resolution, 8 Mbps bit rate" from VPU brief description.</li> <li>(continued on next page)</li> </ul> |

i.MX53 Applications Processors for Industrial Products, Rev. 6