Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

## Details

·XF

| Details                 |                                                                                |

|-------------------------|--------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                       |

| Applications            | Intelligent LED Driver                                                         |

| Core Processor          | M8C                                                                            |

| Program Memory Type     | FLASH (16KB)                                                                   |

| Controller Series       | CY8CLED                                                                        |

| RAM Size                | 1K x 8                                                                         |

| Interface               | DALI, DMX512, I <sup>2</sup> C, IrDA, SPI, UART/USART                          |

| Number of I/O           | 14                                                                             |

| Voltage - Supply        | 4.75V ~ 5.25V                                                                  |

| Operating Temperature   | -40°C ~ 105°C                                                                  |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 56-VFQFN Exposed Pad                                                           |

| Supplier Device Package | 56-QFN (8x8)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8cled01d01-56ltxq |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2. Contents

| Logic Block Diagrams                                                                                                                                                                                                                                                                                                 | . 3                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

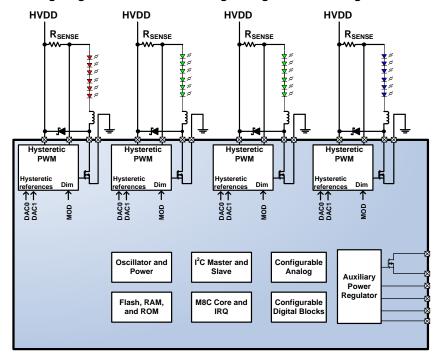

| PowerPSoC Functional Overview                                                                                                                                                                                                                                                                                        | . 9                        |

| Power Peripherals                                                                                                                                                                                                                                                                                                    | . 9                        |

| Hysteretic Controllers                                                                                                                                                                                                                                                                                               |                            |

| Low Side N-Channel FETs                                                                                                                                                                                                                                                                                              | 10                         |

| External Gate Drivers                                                                                                                                                                                                                                                                                                | 10                         |

| Dimming Modulation Schemes                                                                                                                                                                                                                                                                                           | 10                         |

| Current Sense Amplifier                                                                                                                                                                                                                                                                                              | 10                         |

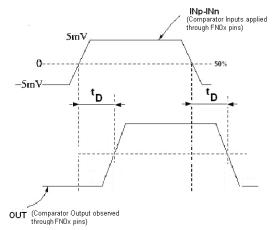

| Voltage Comparators                                                                                                                                                                                                                                                                                                  | 11                         |

| Reference DACs                                                                                                                                                                                                                                                                                                       | 11                         |

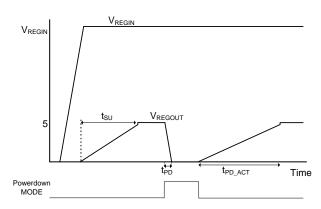

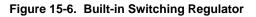

| Built-in Switching Regulator                                                                                                                                                                                                                                                                                         | 11<br>11                   |

| Analog Multiplexer<br>Digital Multiplexer                                                                                                                                                                                                                                                                            | 12                         |

| Function Pins (FN0[0:3])                                                                                                                                                                                                                                                                                             | 12                         |

|                                                                                                                                                                                                                                                                                                                      | . –                        |

| PSoC Core<br>Digital System                                                                                                                                                                                                                                                                                          | <b>13</b><br>13            |

| Analog System                                                                                                                                                                                                                                                                                                        | 13<br>13                   |

| Analog Multiplexer System                                                                                                                                                                                                                                                                                            | 13                         |

| Additional System Resources                                                                                                                                                                                                                                                                                          | 14                         |

| Applications                                                                                                                                                                                                                                                                                                         |                            |

| PowerPSoC Device Characteristics                                                                                                                                                                                                                                                                                     |                            |

|                                                                                                                                                                                                                                                                                                                      |                            |

|                                                                                                                                                                                                                                                                                                                      | 18                         |

| Application Notes                                                                                                                                                                                                                                                                                                    | 18                         |

| Development Kits<br>Training                                                                                                                                                                                                                                                                                         | 18<br>18                   |

| CYPros Consultants                                                                                                                                                                                                                                                                                                   | 10<br>18                   |

| Technical Support                                                                                                                                                                                                                                                                                                    | 18                         |

|                                                                                                                                                                                                                                                                                                                      | -                          |

|                                                                                                                                                                                                                                                                                                                      | 18                         |

| PSoC Designer Software Subsystems<br>In-Circuit Emulator                                                                                                                                                                                                                                                             | 18<br>19                   |

|                                                                                                                                                                                                                                                                                                                      |                            |

|                                                                                                                                                                                                                                                                                                                      | 19                         |

| Pin Information<br>CY8CLED04D0x 56-Pin Part Pinout (without OCD)<br>CY8CLED04G01 56-Pin Part Pinout (without OCD)<br>CY8CLED04DOCD1 56-Pin Part Pinout (with OCD)<br>CY8CLED03D0x 56-Pin Part Pinout (without OCD)<br>CY8CLED03G01 56-Pin Part Pinout (without OCD)<br>CY8CLED02D01 56-Pin Part Pinout (without OCD) | 20<br>21<br>22<br>23<br>24 |

| CY8CLED01D01 56-Pin Part Pinout (without OCD)                                                                                                                                                                                                                                                                        |                            |

| Register General Conventions<br>Abbreviations Used<br>Register Naming Conventions<br>Register Mapping Tables                                                                                                                                                                                                         | 27<br>27                   |

| Register Map Bank 0 Table                                                                |    |

|------------------------------------------------------------------------------------------|----|

| Register Map Bank 1 Table: User Space                                                    |    |

| Electrical Specifications                                                                |    |

| Operating Temperature                                                                    |    |

| Electrical Characteristics                                                               |    |

| System Level                                                                             |    |

| Chip Level                                                                               |    |

| Power Peripheral Low Side N-Channel FET                                                  |    |

| Power Peripheral External Power FET Driver                                               |    |

| Power Peripheral Hysteretic Controller                                                   |    |

| Power Peripheral Comparator                                                              |    |

| Power Peripheral Current Sense Amplifier<br>Power Peripheral PWM/PrISM/DMM Specification | 37 |

| Table                                                                                    | 38 |

| Power Peripheral Reference DAC Specification                                             | 39 |

| Power Peripheral Built-in Switching Regulator                                            | 39 |

| General Purpose I/O / Function Pin I/O                                                   |    |

| PSoC Core Operational Amplifier Specifications                                           |    |

| PSoC Core Low Power Comparator                                                           |    |

| PSoC Core Analog Output Buffer                                                           |    |

| PSoC Core Analog Reference                                                               |    |

| PSoC Core Analog Block                                                                   |    |

| PSoC Core POR and LVD<br>PSoC Core Programming Specifications                            |    |

| PSoC Core Digital Block Specifications                                                   |    |

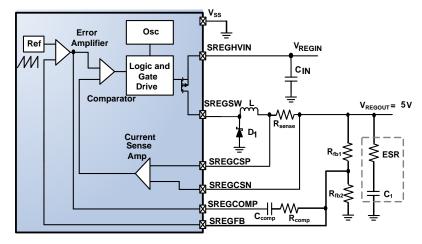

| PSoC Core I2C Specifications                                                             |    |

| Ordering Information                                                                     |    |

| Ordering Code Definitions                                                                |    |

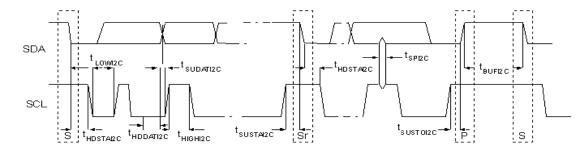

| Packaging Information                                                                    |    |

| Packaging Dimensions                                                                     |    |

| Thermal Impedance                                                                        |    |

| Solder Reflow Peak Temperature                                                           |    |

| Acronyms                                                                                 | 53 |

| Document Conventions                                                                     | 53 |

| Units of Measure                                                                         | 53 |

| Document History Page                                                                    | 55 |

| Sales, Solutions, and Legal Information                                                  |    |

| Worldwide Sales and Design Support                                                       |    |

| Products                                                                                 |    |

| PSoC® Solutions                                                                          |    |

| Cypress Developer Community<br>Technical Support                                         |    |

|                                                                                          | 00 |

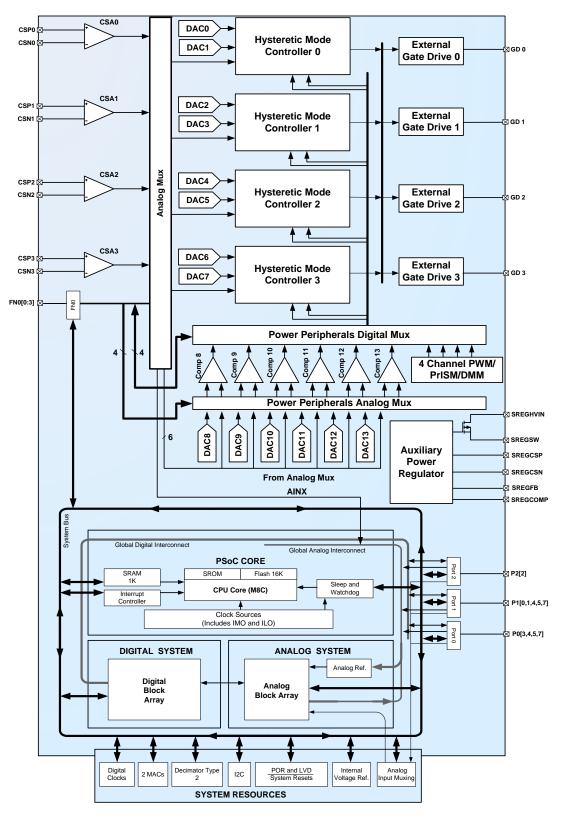

Figure 3-2. CY8CLED04G01 Logic Block Diagram

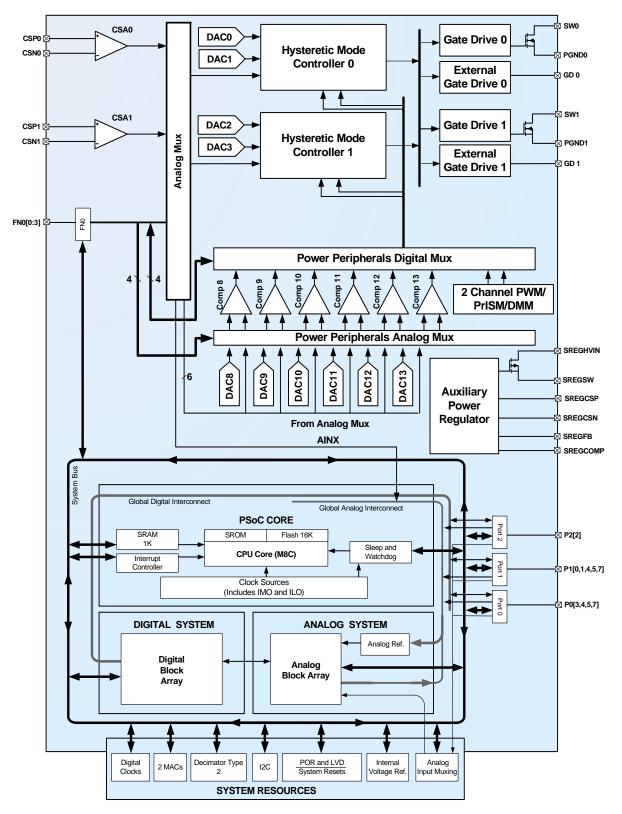

Figure 3-5. CY8CLED02D01 Logic Block Diagram

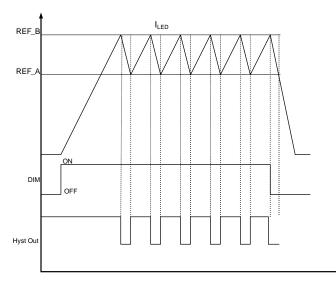

## Figure 5-2. Current Waveforms

The minimum on-time and off-time circuits in the PowerPSoC prevent oscillations at very high frequencies, which can be very destructive to output switches.

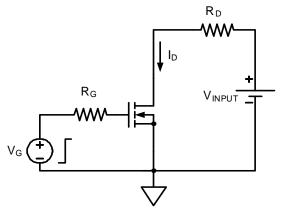

## 5.2 Low Side N-Channel FETs

The internal low side N-Channel FETs are designed to enhance system integration. The low side N-Channel FETs include the following key features:

- Drive capability up to 1 A

- Switching times of 20 ns (rise and fall times) to ensure high efficiency (more than 90%)

- Drain source voltage rating 32 V

- Low R<sub>DS(ON)</sub> to ensure high efficiency

- Switching frequency up to 2 MHz

## 5.3 External Gate Drivers

These gate drivers enable the use of external FETs with higher current capabilities or lower  $R_{DS(ON)}$ . The external gate drivers directly drive MOSFETs that are used in switching applications. The gate driver provides multiple programmable drive strength steps to enable improved EMI management. The external gate drivers include the following key features:

- Programmable drive strength options (25%, 50%, 75%, 100%) for EMI management

- Rise and fall times at 55 ns with 4 nF load

## 5.4 Dimming Modulation Schemes

There are three dimming modulation schemes available with the PowerPSoC. The configurable modulation schemes are:

- Precise intensity signal modulation (PrISM)

- Delta Sigma modulation mode (DMM)

- Pulse-width modulation (PWM)

#### 5.4.1 PrISM Mode Configuration

- High resolution operation up to 16 bits

- Dedicated PrISM module enables customers to use core PSoC digital blocks for other needs

- Clocking up to 48 MHz

- Selectable output signal density

- Reduced EMI

The PrISM mode compares the output of a pseudo-random counter with a signal density value. The comparator output asserts when the count value is less than or equal to the value in the signal density register.

#### 5.4.2 DMM Mode Configuration

- High resolution operation up to 16 bits

- Configurable output frequency and delta sigma modulator width to trade off repeat rates versus resolution

- Dedicated DMM module enables customers to use PSoC digital blocks for other uses

- Clocking up to 48 MHz

The DMM modulator consists of a 12-bit PWM block and a 4-bit delta sigma modulator (DSM) block. The width of the PWM, the width of the DMM, and the clock defines the output frequency. The duty cycle of the PWM output is dithered by using the DSM block which has a user-selectable resolution up to 4 bits.

#### 5.4.3 PWM Mode Configuration

- High resolution operation up to 16 bits

- User programmable period from 1 to 65535 clocks

- Dedicated PWM module enables customers to use core PSoC digital blocks for other use

- Interrupt on rising edge of the output or terminal count

- Precise PWM phase control to manage system current edges

- Phase synchronization among the four channels

- PWM output can be aligned to left, right, or center

The PWM features a down counter and a pulse width register. A comparator output is asserted when the count value is less than or equal to the value in the pulse width register.

## 5.5 Current Sense Amplifier

The high side current sense amplifiers provide a differential sense capability to sense the voltage across current sense resistors in lighting systems. The current sense amplifier includes the following key features:

- Operation with high common mode voltage to 32 V

- High common mode rejection ratio

- Programmable bandwidth to optimize system noise immunity

An off-chip resistor  $R_{sense}$  is used for high side current measurement as shown in Figure 5-3. on page 11. The output of the current sense amplifier goes to the power peripherals analog multiplexer where, you select the hysteretic controller to which

## 6. PSoC Core

The PSoC core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable general purpose I/O(GPIO).

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a four MIPS 8-bit Harvard architecture microprocessor. The CPU uses an interrupt controller with up to 20 vectors to simplify programming of real time embedded events. The program execution is timed and protected using the included sleep and watchdog timers (WDT) time and protect program execution.

Memory encompasses 16 K of flash for program storage, 1 K of SRAM for data storage, and up to 2 K of EEPROM emulated using the flash. Program flash uses four protection levels on blocks of 64 bytes, allowing customized software IP protection.

The PSoC device incorporates flexible internal clock generators, including a 24 MHz internal main oscillator (IMO) accurate to 4 percent over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for use by the digital system. A low power 32 kHz internal low-speed oscillator (ILO) is provided for the sleep timer and WDT. The clocks, together with programmable clock dividers (as a system resource), provide the flexibility to integrate almost any timing requirement into the PowerPSoC device.

PowerPSoC GPIOs provide connection to the CPU, digital, and analog resources of the device. Each pin's drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

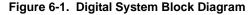

## 6.1 Digital System

The digital system contains eight digital PSoC blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to form 8, 16, 24, and 32-bit peripherals, which are called user module references.

Digital peripheral configurations include:

- DMX512

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

- UART 8-bit with selectable parity

- SPI master and slave

- I<sup>2</sup>C master, slave, and multi-master

- Cyclical redundancy checker/generator (8 to 32 bit)

- IrDA

- Pseudo random sequence generators (8 to 32 bit)

**Note** The DALI interface is supported through the use of a combination of the above mentioned user modules. For more details on the exact configuration and an example project, refer to the application note, PowerPSoC Firmware Design Guidelines, Lighting Control Interfaces - AN51012.

The digital blocks can be connected to any GPIO through a series of global buses that route any signal to any pin. The buses

also allow signal multiplexing and performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

There are four digital blocks in each row. This allows optimum choice of system resources for your application.

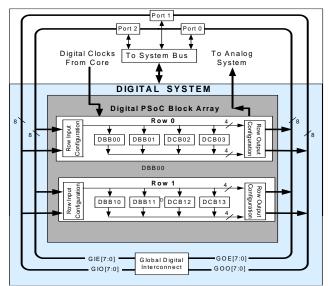

## 6.2 Analog System

The analog system contains six configurable blocks, each comprised of an opamp circuit allowing the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PowerPSoC analog functions (most available as user modules) are:

- Analog-to-digital converters (up to 2, with 6 to 12-bit resolution, selectable as incremental, Delta Sigma, and SAR)

- Filters (2 and 4 pole band-pass, low-pass, and notch)

- Amplifiers (up to 2, with selectable gain to 48x)

- Instrumentation amplifiers (1 with selectable gain to 93x)

- Comparators (up to 2, with 16 selectable thresholds)

- DACs (up to 2, with 6 to 9-bit resolution)

- Multiplying DACs (up to 2, with 6 to 9-bit resolution)

- High current output drivers (two with 30 mA drive as a PSoC core resource)

- 1.3 V reference (as a system resource)

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are arranged in two columns of three blocks each, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in Figure 6-2. on page 14.

Microcontroller Interface (Address Bus, Data Bus, Etc.)

## 6.3 Analog Multiplexer System

The Analog Mux Bus connects to every GPIO pin in ports 0 to 2. Pins can be connected to the bus individually or in any combination. The bus also connects to the analog system for analysis with comparators and analog-to-digital converters. It can be split into two sections for simultaneous dual-channel processing. An additional analog input multiplexer provides a second path to bring Port 0 pins to the analog array.

Switch control logic enables selected pins to precharge continuously under hardware control. This enables capacitive

measurement for applications such as touch sensing. Other multiplexer applications include:

- Track pad, finger sensing

- Crosspoint connection between any I/O pin combinations

Like other PSoC devices, PowerPSoC has specific pins allocated to the reference capacitor (Ref Cap) and modulation resistor (Mod resistor). These are indicated in the device pinouts (Section 13). For more details on capacitive sensing, see the design guide, Getting Started With CapSense. Apart from these, there are a number of application notes on Capacitive Sensing on the Cypress webbiest. The PowerPSoC Technical Reference Manual provides details on the analog system configuration that enables all I/Os in the device to be CapSense inputs.

#### 6.4 Additional System Resources

System resources provide additional capability useful in complete systems. Additional resources include a multiplier, decimator, low voltage detection, and power on reset. Brief statements describing the merits of each resource follow.

- Two multiply accumulates (MACs) provide fast 8-bit multipliers with 32-bit accumulate, to assist in both general math and digital filters.

- A decimator provides a custom hardware filter for digital signal processing applications including creation of delta sigma ADCs.

- Low-voltage detection (LVD) interrupts signal the application of falling voltage levels, while the advanced POR (power on reset) circuit eliminates the need for a system supervisor.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. The designer can generate additional clocks using digital PSoC blocks as clock dividers.

- The I<sup>2</sup>C module provides 100 and 400 kHz communication over two wires. Slave, master, and multi-master applications are supported.

- An internal 1.3 V reference provides an absolute reference for the analog system, including ADCs and DACs.

- Versatile analog multiplexer system.

## 7. Applications

The PowerPSoC family of devices can be used to add hysteretic current control capability to power applications. The devices can be used to control current in devices such as LEDs, heating elements, and solenoids. For LED applications, all high-brightness LEDs (HBLEDs) can be controlled using the PowerPSoC. The following figures show examples of applications in which the PowerPSoC family of devices adds intelligent power control for power applications.

Figure 7-1. LED Lighting with RGGB Color Mixing Configured as Floating Load Buck Converter

## 12.2 CY8CLED04G01 56-Pin Part Pinout (without OCD)

The CY8CLED04G01 PowerPSoC device is available with the following pinout information. Every port pin (labeled with a "P" and "FN0") is capable of Digital I/O.

| Pin |                 | Туре              |                      |                      |                                                                                | Fig | ure 1           | 2-2. CY                              | 8CLED0                               | 4G01 5                | 6-Pin PowerPSoC Device                                  |

|-----|-----------------|-------------------|----------------------|----------------------|--------------------------------------------------------------------------------|-----|-----------------|--------------------------------------|--------------------------------------|-----------------------|---------------------------------------------------------|

| No. | Digital<br>Rows | Analog<br>Columns | Power<br>Peripherals | Name                 | Description                                                                    |     |                 |                                      |                                      |                       |                                                         |

| 1   | I/O             | I                 |                      | P1[0]                | GPIO/I <sup>2</sup> C SDA (Secondary)/<br>ISSP SDATA                           |     |                 |                                      |                                      |                       |                                                         |

| 2   | I/O             | I                 |                      | P2[2]                | GPIO/Direct Switch Cap connection                                              |     |                 |                                      | QF                                   | N Top                 | View                                                    |

| 3   | I/O             | I/O               |                      | P0[3]                | GPIO/Analog Input (Column 0)/<br>Analog Output (Column 0)                      |     |                 |                                      |                                      | -                     |                                                         |

| 4   | I/O             | I/O               |                      | P0[5]                | GPIO/Analog Input (Column 0)/<br>Analog Output (Column 1)/<br>Capsense Ref Cap |     |                 | _                                    | P1[4]<br>VSS<br>VDD<br>P0[4]<br>CSN1 |                       |                                                         |

| 5   | I/O             | I                 |                      | P0[7]                | GPIO/Analog Input (Column 0)/<br>Capsense Ref Cap                              |     |                 | P1[0] = 1                            | 56<br>55<br>54<br>53<br>53           | 511<br>50<br>49<br>48 | 42 PGND0                                                |

| 5   | I/O             | I                 |                      | P1[1]                | GPIO/I <sup>2</sup> C SCL (Secondary)/<br>ISSP SCLK                            |     |                 | P2[2] = 2<br>P0[3] = 3<br>P0[5] = 4  |                                      |                       | 41= GD0<br>40= DNC<br>39= PGND1                         |

| 7   | I/O             | I                 |                      | P1[5]                | GPIO/I <sup>2</sup> C SDA (Primary)                                            |     |                 | P0[7] 5                              |                                      | 111                   | 39 <b>=</b> PGND1<br>38 <b>=</b> GD1                    |

| 3   | I/O             | I                 |                      | P1[7]                | GPIO/I <sup>2</sup> C SCL (Primary)                                            |     |                 | P1[1] = 6                            | ( / ) f                              | Indea                 | 37 DNC                                                  |

| )   |                 |                   |                      | V <sub>SS</sub>      | Digital Ground                                                                 |     |                 | P1[5] <b>9</b> 7<br>P1[7] <b>9</b> 8 | 1/7                                  | 644                   | 36= DNC                                                 |

| 0   |                 |                   |                      | NC                   | No Connect                                                                     |     |                 | VSS 9                                | 111                                  |                       | 35 <b>=</b> GD2<br>34 <b>=</b> PGND2                    |

| 1   |                 |                   |                      | NC                   | No Connect                                                                     | 1   |                 | NC = 10                              |                                      | 111                   | 33= DNC                                                 |

| 2   |                 |                   |                      | NC                   | No Connect                                                                     |     |                 | NC = 11<br>NC = 12                   |                                      | 111                   | 32= GD3                                                 |

| 3   |                 |                   |                      | NC                   | No Connect                                                                     | 1   |                 |                                      |                                      | 111                   | 31 PGND3<br>30 GDVSS                                    |

| 4   |                 |                   |                      | XRES                 | External Reset                                                                 | 1   |                 | XRES 14                              | L .                                  | 0 - 0 -               | 29 GDVDD                                                |

| 5   |                 |                   |                      | V <sub>DD</sub>      | Digital Power Supply                                                           | 1   |                 |                                      |                                      |                       |                                                         |

| 6   |                 |                   |                      | V <sub>SS</sub>      | Digital Ground                                                                 |     |                 |                                      | VDD<br>VS S<br>VSS<br>VDD<br>SN 2    | P2<br>P3<br>N3        | SREGEB<br>SREGCSP<br>SREGCSP<br>SREGCSP<br>SREGLVIN     |

| 7   |                 |                   |                      | AV <sub>SS</sub>     | Analog Ground                                                                  |     |                 |                                      | CSI AC                               | CONCON                | BHA 2000                                                |

| 8   |                 |                   |                      | AV <sub>DD</sub>     | Analog Power Supply                                                            |     |                 |                                      |                                      | Ű.                    | SRE<br>SRE<br>SRE<br>SRE<br>SRE                         |

| 9   |                 |                   |                      | CSN2                 | Current Sense Negative Input 2                                                 |     |                 |                                      |                                      | RS                    | 0,0,0,0                                                 |

| 20  |                 |                   |                      | CSP2                 | Current Sense Positive Input and<br>Power Supply - CSA2                        |     |                 |                                      |                                      |                       |                                                         |

| 21  |                 |                   |                      | CSP3                 | Current Sense Positive Input and<br>Power Supply - CSA3                        |     |                 | * C                                  | Connect E                            | Exposed               | l Pad to PGNDx                                          |

| 22  |                 |                   | I                    | CSN3                 | Current Sense Negative Input 3                                                 |     |                 |                                      |                                      |                       |                                                         |

| 23  |                 |                   |                      | SREGCOMP             | Voltage Regulator Error Amp Comp                                               |     |                 |                                      |                                      |                       |                                                         |

| 24  |                 |                   | 1                    | SREGFB               | Regulator Voltage Mode Feedback<br>Node                                        |     |                 |                                      |                                      |                       |                                                         |

| 25  |                 |                   | I                    | SREGCSN              | Current Mode Feedback Negative                                                 |     |                 |                                      |                                      |                       |                                                         |

| 26  |                 |                   |                      | SREGCSP              | Current Mode Feedback Positive                                                 |     |                 |                                      |                                      |                       |                                                         |

| 27  |                 |                   | 0                    | SREGSW               | Switch Mode Regulator OUT                                                      |     |                 |                                      |                                      |                       |                                                         |

| 8   |                 |                   |                      | SREGHVIN             | Switch Mode Regulator IN                                                       |     |                 | -                                    |                                      |                       |                                                         |

| 29  |                 |                   |                      | GDV <sub>DD</sub>    | Gate Driver Power Supply                                                       | Pin | District        | Туре                                 |                                      | Name                  | Description                                             |

| 80  |                 |                   |                      | GDV <sub>SS</sub>    | Gate Driver Ground                                                             | No. | Digital<br>Rows | Analog<br>Columns                    | Power<br>Peripherals                 |                       | 2000101011                                              |

| 1   |                 |                   |                      | PGND3 <sup>[3]</sup> | Power FET Ground 3                                                             | 44  |                 |                                      |                                      | GDV <sub>DD</sub>     | Gate Driver Power Supply                                |

| 2   |                 |                   | 0                    | GD3                  | External Low Side Gate Driver 3                                                | 45  |                 |                                      | I/O                                  | FN0[0]                | Function I/O                                            |

| 3   |                 |                   |                      | DNC <sup>[2]</sup>   | Do Not Connect                                                                 | 46  |                 |                                      | I/O                                  | FN0[1]                | Function I/O                                            |

| 4   |                 |                   |                      | PGND2 <sup>[3]</sup> | Power FET Ground 2                                                             | 47  |                 |                                      | I/O                                  | FN0[2]                | Function I/O                                            |

| 5   |                 |                   | 0                    | GD2                  | External Low Side Gate Driver 2                                                | 48  |                 |                                      | I/O                                  | FN0[3]                | Function I/O                                            |

| 6   |                 |                   |                      | DNC <sup>[2]</sup>   | Do Not Connect                                                                 | 49  |                 |                                      | I                                    | CSN0                  | Current Sense Negative Input 0                          |

| 37  |                 |                   |                      | DNC <sup>[2]</sup>   | Do Not Connect                                                                 | 50  |                 |                                      |                                      | CSP0                  | Current Sense Positive Input and<br>Power Supply - CSA0 |

| 38  |                 |                   | 0                    | GD1                  | External Low Side Gate Driver 1                                                | 51  |                 |                                      |                                      | CSP1                  | Current Sense Positive Input and<br>Power Supply - CSA1 |

| 39  |                 |                   |                      | PGND1 <sup>[3]</sup> | Power FET Ground 1                                                             | 52  |                 |                                      | I                                    | CSN1                  | Current Sense Negative Input 1                          |

| 40  |                 |                   |                      | DNC <sup>[2]</sup>   | Do Not Connect                                                                 | 53  | I/O             | I                                    |                                      | P0[4]                 | GPIO/Analog Input (Column 1) /<br>Bandgap Output        |

| 1   |                 |                   | 0                    | GD0                  | External Low Side Gate Driver 0                                                | 54  |                 |                                      |                                      | V <sub>DD</sub>       | Digital Power Supply                                    |

| 2   |                 |                   |                      | PGND0 <sup>[3]</sup> | Power FET Ground 0                                                             | 55  |                 |                                      |                                      | V <sub>SS</sub>       | Digital Ground                                          |

| 3   |                 |                   |                      | GDV <sub>SS</sub>    | Gate Driver Ground                                                             | 56  | I/O             | I                                    |                                      | P1[4]                 | GPIO / External Clock Input                             |

### Table 12-2. CY8CLED04G01 56-Pin Part Pinout (QFN)

#### Notes

Do Not Connect (DNC) pins must be left unconnected, or floating. Connecting these pins to power or ground may cause improper operation or failure of the device.

All PGNDx pins must be connected to the ground plane on the PCB irrespective of whether the corresponding PowerPSoC channel is used or not.

# CY8CLED04D01/CY8CLED04D02/CY8CLED04G01 CY8CLED03D01/CY8CLED03D02/CY8CLED03G01 CY8CLED02D01/CY8CLED01D01

## 12.3 CY8CLED04DOCD1 56-Pin Part Pinout (with OCD)

The CY8CLED04DOCD1 PowerPSoC device is available with the following pinout information. Every port pin (labeled with a "P" and "FN0") is capable of Digital I/O.

|            |         | Type           |             |                      | , , , , , , , , , , , , , , , , , , ,                                           | Figure 12-3. CY8CLED04DOCD1 56-Pin PowerPSoC De                                                                  |                 |                                  |                            | 1 56 Din BowerBSoC Dovice |                                                                          |  |  |

|------------|---------|----------------|-------------|----------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|----------------------------|---------------------------|--------------------------------------------------------------------------|--|--|

| Pin<br>No. | Digital | Type<br>Analog | Power       | Name                 | Description                                                                     | Fig                                                                                                              | ure 14          | 2-3. 61                          | OCLEDU4                    | IDOCD                     | 1 56-PIN PowerPSoC Device                                                |  |  |

| <b>NO.</b> | Rows    |                | Peripherals | P1[0]                | GPIO/I <sup>2</sup> C SDA (Secondary)/                                          | QFN Top View                                                                                                     |                 |                                  |                            |                           |                                                                          |  |  |

|            |         | •              |             |                      | ISSP SDATA                                                                      |                                                                                                                  |                 |                                  |                            | •                         |                                                                          |  |  |

| 2          | I/O     |                |             | P2[2]                | GPIO/Direct Switch Cap connection                                               |                                                                                                                  |                 |                                  | <b>=</b> ~ ~ <del>=</del>  | 5283                      |                                                                          |  |  |

| 3          | I/O     | I/O            |             | P0[3]                | GPIO/Analog Input (Column 0)/<br>Analog Output (Column 0)                       | P 1[4]<br>V VDD<br>V VSS<br>V VSS<br>V VSS<br>V VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>V |                 |                                  |                            |                           |                                                                          |  |  |

| 4          | I/O     | I/O            |             | P0[5]                | GPIO/Analog Input (Column 0)/<br>Analog Output (Column 1) /<br>Capsense Ref Cap |                                                                                                                  |                 | P1[0]                            | 1                          | 53<br>51<br>50            | 42= PGND0<br>41= GD0                                                     |  |  |

| 5          | I/O     | I              |             | P0[7]                | GPIO/Analog Input (Column 0)/<br>Capsense Ref Cap                               |                                                                                                                  |                 | P0[3] <b>=</b><br>P0[5] <b>=</b> | 4                          |                           | 40= SW0<br>39= PGND1                                                     |  |  |

| 6          | I/O     | I              |             | P1[1]                | GPIO/I <sup>2</sup> C SCL (Secondary)/<br>ISSP SCLK                             |                                                                                                                  |                 | P0[7] =<br>P1[1] =               | 6 <b>1 1</b>               | Éxpos                     | 38= GD1<br>37= SW1                                                       |  |  |

| 7          | I/O     | 1              |             | P1[5]                | GPIO/I <sup>2</sup> C SDA (Primary)                                             |                                                                                                                  |                 | P1[5]                            |                            |                           | 36 SW2                                                                   |  |  |

| 8          | I/O     | 1              |             | P1[7]                | GPIO/I <sup>2</sup> C SCL (Primary)                                             |                                                                                                                  |                 | P1[7]                            |                            | / Fau                     | 35 <b>=</b> GD2<br>34 <b>=</b> PGND2                                     |  |  |

| 9          |         |                |             | V <sub>SS</sub>      | Digital Ground                                                                  |                                                                                                                  |                 | OCDE                             |                            | / / /                     | 33= SW3                                                                  |  |  |

| 10         | I/O     |                |             | OCDE                 | On Chip Debugger Port                                                           |                                                                                                                  |                 |                                  |                            | 111                       | 32 <b>=</b> GD3                                                          |  |  |

| 11         | I/O     |                |             | OCDO                 | On Chip Debugger Port                                                           |                                                                                                                  |                 |                                  |                            | ' <i>' ' ' '</i>          | 31 PGND3<br>30 GDVSS                                                     |  |  |

| 12         | I/O     |                |             | CCLK                 | On Chip Debugger Port                                                           |                                                                                                                  |                 | XRES                             |                            |                           | 001/00                                                                   |  |  |

| 13         | I/O     |                |             | HCLK                 | On Chip Debugger Port                                                           |                                                                                                                  |                 |                                  | 112                        | 5 2 2 2                   | © 7 9 9 10 8 29 GDVDD                                                    |  |  |

| 14         | 1       |                |             | XRES                 | External Reset                                                                  |                                                                                                                  |                 |                                  |                            | 9 0 0 g                   |                                                                          |  |  |

| 15         |         |                |             | V <sub>DD</sub>      | Digital Power Supply                                                            |                                                                                                                  |                 |                                  | VDD<br>VSS<br>AVSS<br>AVDD | CSF                       | SREGCOMP<br>SREGCER<br>SREGCSN<br>SREGCSN<br>SREGCSN<br>SREGSN<br>SREGSN |  |  |

| 16         |         |                |             | V <sub>SS</sub>      | Digital Ground                                                                  |                                                                                                                  |                 |                                  |                            |                           | S S S S S S S S S S S S S S S S S S S                                    |  |  |

| 17         |         |                |             | AV <sub>SS</sub>     | Analog Ground                                                                   |                                                                                                                  |                 |                                  |                            |                           | S S S S S S S S S S S S S S S S S S S                                    |  |  |

| 18         |         |                |             | AV <sub>DD</sub>     | Analog Power Supply                                                             |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 19         |         |                | I           | CSN2                 | Current Sense Negative Input 2                                                  |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 20         |         |                |             | CSP2                 | Current Sense Positive Input and<br>Power Supply - CSA2                         |                                                                                                                  |                 | * C                              | Connect E                  | xposed                    | d Pad to PGNDx                                                           |  |  |

| 21         |         |                |             | CSP3                 | Current Sense Positive Input and<br>Power Supply - CSA3                         |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 22         |         |                | I           | CSN3                 | Current Sense Negative Input 3                                                  |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 23         |         |                |             | SREGCOMP             | Voltage Regulator Error Amp Comp                                                |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 24         |         |                | I           | SREGFB               | Regulator Voltage Mode Feedback<br>Node                                         |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 25         |         |                | I           | SREGCSN              | Current Mode Feedback Negative                                                  |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 26         |         |                | I           | SREGCSP              | Current Mode Feedback Positive                                                  |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 27         |         |                | 0           | SREGSW               | Switch Mode Regulator OUT                                                       |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 28         |         |                |             | SREGHVIN             | Switch Mode Regulator IN                                                        |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

| 29         |         |                |             | GDV <sub>DD</sub>    | Gate Driver Power Supply                                                        | Pin                                                                                                              |                 | Туре                             | •                          |                           |                                                                          |  |  |

| 30         |         |                |             | GDV <sub>SS</sub>    | Gate Driver Ground                                                              | No.                                                                                                              | Digital<br>Rows | Analog<br>Columns                | Power<br>Peripherals       | Name                      | Description                                                              |  |  |

| 31         |         |                |             | PGND3 <sup>[4]</sup> | Power FET Ground 3                                                              | 44                                                                                                               |                 |                                  |                            | GDV <sub>DD</sub>         | Gate Driver Power Supply                                                 |  |  |

| 32         |         |                | 0           | GD3                  | External Low Side Gate Driver 3                                                 | 45                                                                                                               |                 |                                  | I/O                        | FN0[0]                    | Function I/O                                                             |  |  |

| 33         |         |                |             | SW3                  | Power Switch 3                                                                  | 46                                                                                                               |                 |                                  | I/O                        | FN0[1]                    | Function I/O                                                             |  |  |

| 34         |         |                |             | PGND2 <sup>[4]</sup> | Power FET Ground 2                                                              | 47                                                                                                               |                 |                                  | I/O                        | FN0[2]                    | Function I/O                                                             |  |  |

| 35         |         |                | 0           | GD2                  | External Low Side Gate Driver 2                                                 | 48                                                                                                               |                 |                                  | I/O                        | FN0[3]                    | Function I/O                                                             |  |  |

| 36         |         |                |             | SW2                  | Power Switch 2                                                                  | 49                                                                                                               |                 |                                  | I                          | CSN0                      | Current Sense Negative Input 0                                           |  |  |

| 37         |         |                |             | SW1                  | Power Switch 1                                                                  | 50                                                                                                               |                 |                                  |                            | CSP0                      | Current Sense Positive Input and<br>Power Supply - CSA0                  |  |  |

| 38         |         |                | 0           | GD1                  | External Low Side Gate Driver 1                                                 | 51                                                                                                               |                 |                                  |                            | CSP1                      | Current Sense Positive Input and<br>Power Supply - CSA1                  |  |  |

| 39         | 1       |                |             | PGND1 <sup>[4]</sup> | Power FET Ground 1                                                              | 52                                                                                                               |                 |                                  |                            | CSN1                      | Current Sense Negative Input 1                                           |  |  |

| 40         |         |                |             | SW0                  | Power Switch 0                                                                  | 53                                                                                                               | I/O             | I                                |                            | P0[4]                     | GPIO/Analog Input (Column 1) /<br>Bandgap Output                         |  |  |

| 41         | 1       |                | 0           | GD0                  | External Low Side Gate Driver 0                                                 | 54                                                                                                               |                 |                                  |                            | V <sub>DD</sub>           | Digital Power Supply                                                     |  |  |

| 42         | l       |                |             | PGND0 <sup>[4]</sup> | Power FET Ground 0                                                              | 55                                                                                                               |                 |                                  |                            | V <sub>SS</sub>           | Digital Ground                                                           |  |  |

| 43         | l       |                |             | GDV <sub>SS</sub>    | Gate Driver Ground                                                              | 56                                                                                                               | I/O             | I                                |                            | P1[4]                     | GPIO / External Clock Input                                              |  |  |

|            |         |                |             |                      | L                                                                               |                                                                                                                  |                 |                                  |                            |                           |                                                                          |  |  |

## Table 12-3. CY8CLED04DOCD1 56-Pin Part Pinout (QFN)

#### Note

4. All PGNDx pins must be connected to the ground plane on the PCB irrespective of whether the corresponding PowerPSoC channel is used or not.

## 14. Electrical Specifications

This section presents the DC and AC electrical specifications of the CY8CLED04D0X, CY8CLED04G01, CY8CLED03D0X, CY8CLED03G01, CY8CLED02D01, and CY8CLED01D01 of the PowerPSoC device family. For the most up to date electrical specifications, confirm that you have the most recent datasheet by going to the web at http://www.cypress.com/powerpsoc. Specifications for Industrial rated devices are valid for -40 °C  $\leq T_A \leq 85$  °C,  $T_J \leq 115$  °C and for Extended Temperature rated devices for -40 °C  $\leq T_A \leq 105$  °C,  $T_J \leq 125$  °C, except where noted.

## 14.1 Absolute Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the device. Not all user guidelines are production tested.

#### Table 14-1. Absolute Maximum Ratings

| Symbol                                                       | Description                                                                      | Min                  | Тур | Max                   | Units  | Notes                                                                                                                                                                               |

|--------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------|-----|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>                                             | Storage temperature                                                              | -55                  | _   | +115                  | °C     | Higher storage temperatures<br>reduces data retention time.<br>Recommended storage<br>temperature is 0 °C to 50 °C.                                                                 |

| T <sub>A</sub>                                               | Ambient temperature with power applied                                           | -40<br>-40           | -   | +85<br>+105           | °<br>C | $T_J \le 115 \text{ °C}$ (industrial rated)<br>$T_J \le 125 \text{ °C}$ (extended<br>temperature rated)                                                                             |

| V <sub>DD</sub> ,<br>AV <sub>DD</sub> ,<br>GDV <sub>DD</sub> | Supply voltage on $V_{DD},AV_{DD},and$ $GDV_{DD}$                                | -0.5                 | -   | +6.0                  | V      | Relative to $V_{SS}, AV_{SS},$ and $GDV_{SS}$ respectively                                                                                                                          |

| V <sub>IO</sub>                                              | DC input voltage                                                                 | V <sub>SS</sub> -0.5 | -   | V <sub>DD</sub> + 0.5 | V      | Applies only to GPIO and FN0 pins                                                                                                                                                   |

| V <sub>IO2</sub>                                             | DC voltage applied to tristate                                                   | $V_{SS} - 0.5$       | _   | V <sub>DD</sub> + 0.5 | V      |                                                                                                                                                                                     |

| V <sub>FET</sub>                                             | Maximum voltage from power Switch<br>(SWx) to Power FET Ground (PGNDx)           | -                    | _   | 36 <sup>[13]</sup>    | V      | PGNDx is connected to $\mathrm{GDV}_\mathrm{SS}$                                                                                                                                    |

| V <sub>REGIN</sub>                                           | Maximum voltage on SREGHVIN Pin relative to V <sub>SS</sub>                      | -                    | -   | 36 <sup>[13]</sup>    | V      |                                                                                                                                                                                     |

| V <sub>CSP</sub> ,V <sub>CSN</sub>                           | Maximum voltage applied to CSA pins relative to $V_{SS}$                         | -0.5                 | -   | 36 <sup>[13]</sup>    | V      |                                                                                                                                                                                     |

| V <sub>SENSE</sub>                                           | Maximum input differential voltage across<br>CSA input                           | -1.0                 | _   | 1.0                   | V      |                                                                                                                                                                                     |

| I <sub>MAIO</sub>                                            | Maximum current into any port pin<br>configured as analog driver                 | -50                  | -   | +50                   | mA     |                                                                                                                                                                                     |

| I <sub>MIO</sub>                                             | Maximum current into any port and function pin                                   | -25                  | -   | +50                   | mA     |                                                                                                                                                                                     |

| LU                                                           | Latch up current                                                                 | 200                  | _   | _                     | mA     | JESD78A Conformal                                                                                                                                                                   |

| ESD                                                          | Electrostatic discharge voltage                                                  | 2000                 | -   | -                     | V      | Human Body Model ESD.                                                                                                                                                               |

| SR <sub>REGIN</sub>                                          | Ramp rate for the SREGHVIN pin                                                   | -                    | _   | 32                    | V/µs   |                                                                                                                                                                                     |

| SR <sub>CSP</sub>                                            | Ramp rate for the CSPx pins                                                      | -                    | _   | 3.2                   | V/µs   |                                                                                                                                                                                     |

| SR <sub>H</sub> V <sub>DD-FLB</sub>                          | High voltage supply ramp rate for floating load buck configuration               | _                    | -   | 15                    | V/ms   | For other topologies, to enable<br>operation with faster ramp rates,<br>or if the LED string voltage is<br>< 6.5 V, see the <i>PowerPSoC</i><br><i>Technical Reference Manual</i> . |

| SRV <sub>DD-EXT</sub>                                        | External $V_{DD}$ supply ramp rate ( $V_{DD}$ , $AV_{DD}$ , and $GDV_{DD}$ pins) | -                    | -   | 0.2                   | V/μs   | Applies only when powered by a<br>source other than the Built-in<br>Switching Regulator                                                                                             |

Note