#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 66MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 38                                                                               |

| Program Memory Size        | 320KB (320K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-6                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2336b40f66laakxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16/32-Bit

Architecture

# XC2336B

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2000 Family / Value Line

Data Sheet V1.5 2014-06

# Microcontrollers

# XC2336B XC2000 Family / Value Line

#### **Summary of Features**

#### **General Device Information**

| Pin | Symbol            | Ctrl.  | Туре | Function                                          |

|-----|-------------------|--------|------|---------------------------------------------------|

| 7   | P6.0              | O0 / I | DA/A | Bit 0 of Port 6, General Purpose Input/Output     |

|     | EMUX0             | 01     | DA/A | External Analog MUX Control Output 0 (ADC0)       |

|     | BRKOUT            | O3     | DA/A | OCDS Break Signal Output                          |

|     | ADCx_REQG<br>TyG  | I      | DA/A | External Request Gate Input for ADC0/1            |

|     | U1C1_DX0E         | I      | DA/A | USIC1 Channel 1 Shift Data Input                  |

| 8   | P6.1              | O0 / I | DA/A | Bit 1 of Port 6, General Purpose Input/Output     |

|     | EMUX1             | 01     | DA/A | External Analog MUX Control Output 1 (ADC0)       |

|     | T3OUT             | 02     | DA/A | GPT12E Timer T3 Toggle Latch Output               |

|     | U1C1_DOUT         | O3     | DA/A | USIC1 Channel 1 Shift Data Output                 |

|     | ADCx_REQT<br>RyE  | I      | DA/A | External Request Trigger Input for ADC0/1         |

|     | ESR1_6            | I      | DA/A | ESR1 Trigger Input 6                              |

| 10  | P15.0             | I      | In/A | Bit 0 of Port 15, General Purpose Input           |

|     | ADC1_CH0          | I      | In/A | Analog Input Channel 0 for ADC1                   |

| 11  | P15.4             | I      | In/A | Bit 4 of Port 15, General Purpose Input           |

|     | ADC1_CH4          | I      | In/A | Analog Input Channel 4 for ADC1                   |

|     | T6INA             | I      | In/A | GPT12E Timer T6 Count/Gate Input                  |

| 12  | $V_{AREF}$        | -      | PS/A | Reference Voltage for A/D Converters ADC0/1       |

| 13  | V <sub>AGND</sub> | -      | PS/A | Reference Ground for A/D Converters ADC0/1        |

| 14  | P5.0              | I      | In/A | Bit 0 of Port 5, General Purpose Input            |

|     | ADC0_CH0          | I      | In/A | Analog Input Channel 0 for ADC0                   |

| 15  | P5.2              | I      | In/A | Bit 2 of Port 5, General Purpose Input            |

|     | ADC0_CH2          | I      | In/A | Analog Input Channel 2 for ADC0                   |

|     | TDI_A             | I      | In/A | JTAG Test Data Input                              |

| 19  | P5.4              | I      | In/A | Bit 4 of Port 5, General Purpose Input            |

|     | ADC0_CH4          | I      | In/A | Analog Input Channel 4 for ADC0                   |

|     | T3EUDA            | I      | In/A | GPT12E Timer T3 External Up/Down Control<br>Input |

|     | TMS_A             | 1      | In/A | JTAG Test Mode Selection Input                    |

#### **General Device Information**

| Table | e 6 Pin De        | efinitior | ns and | Functions (cont'd)                             |

|-------|-------------------|-----------|--------|------------------------------------------------|

| Pin   | Symbol            | Ctrl.     | Туре   | Function                                       |

| 38    | P10.0             | O0 / I    | St/B   | Bit 0 of Port 10, General Purpose Input/Output |

|       | U0C1_DOUT         | 01        | St/B   | USIC0 Channel 1 Shift Data Output              |

|       | CCU60_CC6<br>0    | O2        | St/B   | CCU60 Channel 0 Output                         |

|       | CCU60_CC6<br>0INA | I         | St/B   | CCU60 Channel 0 Input                          |

|       | ESR1_2            | I         | St/B   | ESR1 Trigger Input 2                           |

|       | U0C0_DX0A         | I         | St/B   | USIC0 Channel 0 Shift Data Input               |

|       | U0C1_DX0A         | I         | St/B   | USIC0 Channel 1 Shift Data Input               |

| 39    | P10.1             | O0 / I    | St/B   | Bit 1 of Port 10, General Purpose Input/Output |

|       | U0C0_DOUT         | O1        | St/B   | USIC0 Channel 0 Shift Data Output              |

|       | CCU60_CC6<br>1    | O2        | St/B   | CCU60 Channel 1 Output                         |

|       | CCU60_CC6<br>1INA | I         | St/B   | CCU60 Channel 1 Input                          |

|       | U0C0_DX1A         | I         | St/B   | USIC0 Channel 0 Shift Clock Input              |

|       | U0C0_DX0B         | I         | St/B   | USIC0 Channel 0 Shift Data Input               |

| 40    | P10.2             | O0 / I    | St/B   | Bit 2 of Port 10, General Purpose Input/Output |

|       | U0C0_SCLK<br>OUT  | 01        | St/B   | USIC0 Channel 0 Shift Clock Output             |

|       | CCU60_CC6<br>2    | 02        | St/B   | CCU60 Channel 2 Output                         |

|       | CCU60_CC6<br>2INA | I         | St/B   | CCU60 Channel 2 Input                          |

|       | U0C0_DX1B         | I         | St/B   | USIC0 Channel 0 Shift Clock Input              |

| 42    | P2.10             | O0 / I    | St/B   | Bit 10 of Port 2, General Purpose Input/Output |

|       | U0C1_DOUT         | O1        | St/B   | USIC0 Channel 1 Shift Data Output              |

|       | U0C0_SELO<br>3    | O2        | St/B   | USIC0 Channel 0 Select/Control 3 Output        |

|       | CC2_CC23          | O3 / I    | St/B   | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|       | U0C1_DX0E         | I         | St/B   | USIC0 Channel 1 Shift Data Input               |

|       | CAPINA            | I         | St/B   | GPT12E Register CAPREL Capture Input           |

# **General Device Information**

# 2.2 Identification Registers

The identification registers describe the current version of the XC2336B and of its modules.

| Table 7 | XC2336B Identification Registers |

|---------|----------------------------------|

|---------|----------------------------------|

| Short Name  | Value                  | Address              | Notes                   |

|-------------|------------------------|----------------------|-------------------------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |                         |

| SCU_IDCHIP  | 3001 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking EES-AA or ES-AA |

|             | 3002 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking AA, AB          |

| SCU_IDMEM   | 304F <sub>H</sub>      | 00'F07A <sub>H</sub> |                         |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |                         |

| JTAG_ID     | 0018'B083 <sub>H</sub> |                      | marking EES-AA or ES-AA |

|             | 1018'B083 <sub>H</sub> |                      | marking AA, AB          |

# 3 Functional Description

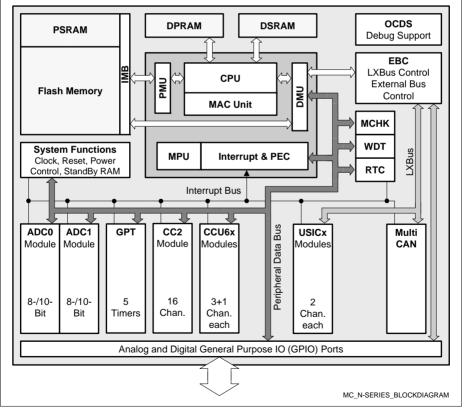

The architecture of the XC2336B combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC2336B.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC2336B.

Figure 4 Block Diagram

# 3.5 Interrupt System

The architecture of the XC2336B supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Using a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed. With the PEC just one cycle is 'stolen' from the current CPU activity to perform the PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC2336B has eight PEC channels, each with fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC2336B can react quickly to the occurrence of non-deterministic events.

# Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

# External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

# Trap Processing

The XC2336B provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

# 3.9 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

Note: Signals T2IN, T2EUD, T4EUD, and T6EUD are not connected to pins.

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

# **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

|              | Table 11 Instruction Set Summary (contra) |       |  |  |  |  |  |  |

|--------------|-------------------------------------------|-------|--|--|--|--|--|--|

| Mnemonic     | Description                               | Bytes |  |  |  |  |  |  |

| NOP          | Null operation                            | 2     |  |  |  |  |  |  |

| CoMUL/CoMAC  | Multiply (and accumulate)                 | 4     |  |  |  |  |  |  |

| CoADD/CoSUB  | Add/Subtract                              | 4     |  |  |  |  |  |  |

| Co(A)SHR     | (Arithmetic) Shift right                  | 4     |  |  |  |  |  |  |

| CoSHL        | Shift left                                | 4     |  |  |  |  |  |  |

| CoLOAD/STORE | Load accumulator/Store MAC register       | 4     |  |  |  |  |  |  |

| CoCMP        | Compare                                   | 4     |  |  |  |  |  |  |

| CoMAX/MIN    | Maximum/Minimum                           | 4     |  |  |  |  |  |  |

| CoABS/CoRND  | Absolute value/Round accumulator          | 4     |  |  |  |  |  |  |

| CoMOV        | Data move                                 | 4     |  |  |  |  |  |  |

| CoNEG/NOP    | Negate accumulator/Null operation         | 4     |  |  |  |  |  |  |

# Table 11 Instruction Set Summary (cont'd)

1) The Enter Power Down Mode instruction is not used in the XC2336B, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

# 4 Electrical Parameters

The operating range for the XC2336B is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

# 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

| Parameter                                                       | Symbol                  | Values |      |                        | Unit | Note /                             |

|-----------------------------------------------------------------|-------------------------|--------|------|------------------------|------|------------------------------------|

|                                                                 |                         | Min.   | Тур. | Max.                   |      | Test Condition                     |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR      | -30    | -    | -                      | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR      | -      | -    | 30                     | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$    | -10    | -    | 10                     | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -      | -    | 100                    | mA   | 1)                                 |

| Junction Temperature                                            | $T_{J}SR$               | -40    | -    | 150                    | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$     | -65    | -    | 150                    | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | -0.5   | -    | 6.0                    | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}~{\rm SR}$   | -0.5   | -    | V <sub>DDP</sub> + 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

Table 12

Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

Note: Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

# 4.3.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

**Table 17** is valid under the following conditions:  $V_{\rm DDP} \ge 3.0$  V;  $V_{\rm DDP}$ typ. 3.3 V;  $V_{\rm DDP} \le 4.5$  V

| Parameter                                                                                   | Symbol                   |                                     | Values | S                                 | Unit | Note /<br>Test Condition                                                                                                      |

|---------------------------------------------------------------------------------------------|--------------------------|-------------------------------------|--------|-----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min.                                | Тур.   | Max.                              |      |                                                                                                                               |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | C <sub>IO</sub> CC       | _                                   | -      | 10                                | pF   | not subject to production test                                                                                                |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | $0.07 	ext{ x}$<br>$V_{	ext{DDP}}$  | _      | -                                 | V    | R <sub>S</sub> = 0 Ohm                                                                                                        |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>OZ1</sub>  <br>CC | _                                   | 10     | 200                               | nA   | $V_{\rm IN}$ > $V_{\rm SS}$ ;<br>$V_{\rm IN}$ < $V_{\rm DDP}$                                                                 |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double           | I <sub>OZ2</sub>  <br>CC | _                                   | 0.2    | 2.5                               | μA   | $\begin{array}{l} T_{\rm J} \leq 110 ~^{\circ}{\rm C}; \\ V_{\rm IN} > V_{\rm SS} ~; \\ V_{\rm IN} < V_{\rm DDP} \end{array}$ |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                                   | 0.2    | 8                                 | μA   | $T_{ m J} \le 150 \ ^{\circ}{ m C}; \ V_{ m IN} > V_{ m SS}; \ V_{ m IN} < V_{ m DDP}$                                        |

| Pull Level Force Current <sup>5)</sup>                                                      | I <sub>PLF</sub>   SR    | 150                                 | _      | _                                 | μA   |                                                                                                                               |

| Pull Level Keep Current <sup>6)</sup>                                                       | I <sub>PLK</sub>  <br>SR | -                                   | _      | 10                                | μA   | $V_{\rm IN} \ge V_{\rm IHmin}(pull up);$<br>$V_{\rm IN} \le V_{\rm ILmax}(pull down)$                                         |

| Input high voltage (all<br>except XTAL1)                                                    | $V_{\rm IH}{ m SR}$      | $0.7 	ext{ x}$<br>$V_{	extsf{DDP}}$ | -      | V <sub>DDP</sub> + 0.3            | V    |                                                                                                                               |

| Input low voltage<br>(all except XTAL1)                                                     | $V_{\rm IL}{ m SR}$      | -0.3                                | -      | $0.3 	ext{ x}$<br>$V_{	ext{DDP}}$ | V    |                                                                                                                               |

# Table 17 DC Characteristics for Lower Voltage Range

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332<sub>µ</sub>)

- 5) TUE is tested at V<sub>AREF</sub> = V<sub>DDPA</sub> = 5.0 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

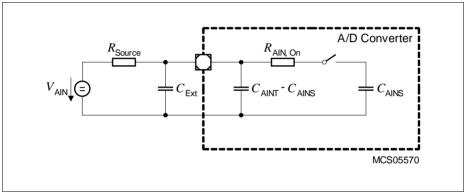

Figure 16 Equivalent Circuitry for Analog Inputs

- This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

- 3)  $f_{WU}$  in MHz

- 4) This value includes a hysteresis of approximately 50 mV for rising voltage.

- 5)  $V_{LV}$  = selected SWD voltage level

- 6) The limit  $V_{LV}$  0.10 V is valid for the OK1 level. The limit for the OK2 level is  $V_{LV}$  0.15 V.

# Conditions for t<sub>SPO</sub> Timing Measurement

The time required for the transition from **Power-on** to **Base** mode is called  $t_{SPO}$ . It is measured under the following conditions:

Precondition: The pad supply is valid, i.e.  $V_{\text{DDPB}}$  is above 3.0V and remains above 3.0V even though the XC2336B is starting up. No debugger is attached.

Start condition: Power-on reset is removed ( $\overline{PORST} = 1$ ).

End condition: External pin toggle caused by first user instruction executed from FLASH after startup.

# Conditions for t<sub>SSO</sub> Timing Measurement

The time required for the transition from **Stopover** to **Stopover Waked-Up** mode is called  $t_{SSO}$ . It is measured under the following conditions:

Precondition: The **Stopover** mode has been entered using the procedure defined in the Programmer's Guide.

Start condition: Pin toggle on ESR pin triggering the startup sequence.

End condition: External pin toggle caused by first user instruction executed from PSRAM after startup.

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and Figure 20).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$D_{\text{Tmax}}$  [ns] = ±(220 / (K2 ×  $f_{\text{SYS}}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS} / 1.2$ ) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$D_{T}$  [ns] =  $D_{Tmax} \times [(1 - 0.058 \times K2) \times (T - 1) / (0.83 \times f_{SYS} - 1) + 0.058 \times K2]$

$f_{SYS}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max}$  =  $\pm(220$  / (4  $\times$  33) + 4.3) = 5.97 ns (Not applicable directly in this case!)

$D_3 = 5.97 \times [(1 - 0.058 \times 4) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 4]$

= 5.97 × [0.768 × 2 / 26.39 + 0.232]

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max} = \pm (220 / (2 \times 33) + 4.3) = 7.63$  ns (Not applicable directly in this case!)

$\begin{array}{l} \mathsf{D}_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) \ / \ (0.83 \times 33 - 1) + 0.058 \times 2] \\ = 7.63 \times [0.884 \times 2 \ / \ 26.39 + 0.116] \end{array}$

# 4.7.4 Pad Properties

The output pad drivers of the XC2336B can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . Therefore the following tables list the pad parameters for the upper voltage range and the lower voltage range, respectively.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 28** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}}$  typ. 5 V;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

| Parameter                                                       | Symbol                  | Values |      |      | Unit | Note /                      |

|-----------------------------------------------------------------|-------------------------|--------|------|------|------|-----------------------------|

|                                                                 |                         | Min.   | Тур. | Max. |      | Test Condition              |

| Maximum output driver<br>current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 4.0  | mA   | Driver_Strength<br>= Medium |

|                                                                 |                         | _      | -    | 10   | mA   | Driver_Strength<br>= Strong |

|                                                                 |                         | _      | -    | 0.5  | mA   | Driver_Strength<br>= Weak   |

| Nominal output driver current (absolute value)                  | I <sub>Onom</sub><br>CC | -      | -    | 1.0  | mA   | Driver_Strength<br>= Medium |

|                                                                 |                         | _      | -    | 2.5  | mA   | Driver_Strength<br>= Strong |

|                                                                 |                         | _      | -    | 0.1  | mA   | Driver_Strength<br>= Weak   |

Table 28 Standard Pad Parameters for Upper Voltage Range

| Parameter                          | Symbol             |      | Values | ;                                         | Unit | Note /                                                                                                              |

|------------------------------------|--------------------|------|--------|-------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------|

|                                    |                    | Min. | Тур.   | Max.                                      |      | Test Condition                                                                                                      |

| Rise and Fall times (10% -<br>90%) | t <sub>RF</sub> CC | _    | _      | 23 +<br>0.6 x<br>C <sub>L</sub>           | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Medium                            |

|                                    |                    | _    | _      | 11.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Medium |

|                                    |                    | -    | _      | 4.2 +<br>0.14 x<br>C <sub>L</sub>         | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Sharp  |

|                                    |                    | -    | -      | 20.6 +<br>0.22 x<br>C <sub>L</sub>        | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Slow   |

|                                    |                    | -    | -      | 212 +<br>1.9 x<br><i>C</i> L              | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Weak                              |

Table 28 Standard Pad Parameters for Upper Voltage Range (cont'd)

An output current above |I<sub>OXnom</sub>| may be drawn from up to three pins at the same time. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

# 4.7.6 Debug Interface Timing

The debugger can communicate with the XC2336B either via the 2-pin DAP interface or via the standard JTAG interface.

# Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 34** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage\_range= upper

| Parameter                                         | Symbol                    | Values |      |      | Unit | Note /         |

|---------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                   |                           | Min.   | Тур. | Max. |      | Test Condition |

| DAP0 clock period <sup>1)</sup>                   | t <sub>11</sub> SR        | 25     | -    | _    | ns   |                |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8      | -    | _    | ns   |                |

| DAP0 low time <sup>1)</sup>                       | t <sub>13</sub> SR        | 8      | -    | _    | ns   |                |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -      | -    | 4    | ns   |                |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -      | -    | 4    | ns   |                |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6      | -    | -    | ns   |                |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6      | -    | -    | ns   |                |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 17     | 20   | -    | ns   |                |

Table 34

DAP Interface Timing for Upper Voltage Range

1) See the DAP chapter for clock rate restrictions in the Active::IDLE protocol state.

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

**Table 35** is valid under the following conditions:  $C_{L}$  = 20 pF; voltage\_range= lower

# Package and Reliability

# 5.2 Thermal Considerations

When operating the XC2336B in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} \cdot V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- · Reduce the number of output pins

- Reduce the load on active output drivers