#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 38                                                                               |

| Program Memory Size        | 320KB (320K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 110°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-6                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2336b40f80laahxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2014-06 Published by Infineon Technologies AG 81726 Munich, Germany © 2014 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

|          | B Data Sheet<br>n History: V1.5 2014-06                                  |

|----------|--------------------------------------------------------------------------|

| Previous | Versions:                                                                |

| V1.4, 20 | 13-02                                                                    |

| V1.3, 20 | 11-07                                                                    |

| V1.2, 20 | 10-04                                                                    |

| V1.1, 20 | 09-07                                                                    |

| V1.0, 20 | 09-03 Preliminary                                                        |

| Page     | Subjects (major changes since last revision)                             |

| 9        | Added XC2336B-40FxLR to Basic Device Types                               |

| 10       | Moved XC2336B-24FxL, XC2336B-40FxL from Basic to Special Device<br>Types |

| 103      | Added package type PG-LQFP-64-24                                         |

### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                                   | Summary of Features7Basic Device Types9Special Device Types10Definition of Feature Variants11                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                          | General Device Information13Pin Configuration and Definition14Identification Registers26                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18 | Functional Description27Memory Subsystem and Organization28Central Processing Unit (CPU)32Memory Protection Unit (MPU)34Memory Checker Module (MCHK)34Interrupt System35On-Chip Debug Support (OCDS)36Capture/Compare Unit (CC2)37Capture/Compare Units CCU6x40General Purpose Timer (GPT12E) Unit42Real Time Clock46A/D Converters48Universal Serial Interface Channel Modules (USIC)49MultiCAN Module51System Timer52Watchdog Timer52Clock Generation53Parallel Ports54Instruction Set Summary55 |

|                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4<br>4.5                                                                 | Electrical Parameters58General Parameters58Operating Conditions59Voltage Range definitions61Parameter Interpretation61DC Parameters62DC Parameters for Upper Voltage Area64DC Parameters for Lower Voltage Area66Power Consumption68Analog/Digital Converter Parameters72System Parameters76                                                                                                                                                                                                       |

| 4.6<br>4.7                                                                                                                                      | Flash Memory Parameters    79      AC Parameters    81                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |  |  |

| 43    | P10.3                                                  | O0 / I | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |  |  |

|       | CCU60_COU<br>T60                                       | O2     | St/B | CCU60 Channel 0 Output                         |  |  |  |

|       | U0C0_DX2A                                              | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |  |  |

|       | U0C1_DX2A                                              | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |  |  |

| 44    | P10.4                                                  | O0 / I | St/B | Bit 4 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C0_SELO<br>3                                         | O1     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |  |

|       | CCU60_COU<br>T61                                       | O2     | St/B | CCU60 Channel 1 Output                         |  |  |  |

|       | U0C0_DX2B                                              | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |  |  |

|       | U0C1_DX2B                                              | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |  |  |

|       | ESR1_9                                                 | I      | St/B | ESR1 Trigger Input 9                           |  |  |  |

| 45    | P10.5                                                  | O0 / I | St/B | Bit 5 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C1_SCLK<br>OUT                                       | O1     | St/B | USIC0 Channel 1 Shift Clock Output             |  |  |  |

|       | CCU60_COU<br>T62                                       | O2     | St/B | CCU60 Channel 2 Output                         |  |  |  |

|       | U0C1_DX1B                                              | I      | St/B | USIC0 Channel 1 Shift Clock Input              |  |  |  |

| 46    | P10.6                                                  | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C0_DOUT                                              | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |

|       | U1C0_SELO<br>0                                         | O3     | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |  |  |

|       | U0C0_DX0C                                              | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|       | U1C0_DX2D                                              | I      | St/B | USIC1 Channel 0 Shift Control Input            |  |  |  |

|       | CCU60_CTR<br>APA                                       | 1      | St/B | CCU60 Emergency Trap Input                     |  |  |  |

|     | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                               |  |  |  |

|-----|-----------------------------------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin | Symbol                                        | Ctrl.      | Туре | Function                                                                                                                                                                      |  |  |  |

| 53  | P10.10                                        | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |  |

|     | U0C0_SELO<br>0                                | O1         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                                       |  |  |  |

|     | CCU60_COU<br>T63                              | O2         | St/B | CCU60 Channel 3 Output                                                                                                                                                        |  |  |  |

|     | U0C0_DX2C                                     | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                           |  |  |  |

|     | U0C1_DX1A                                     | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                             |  |  |  |

|     | TDI_B                                         | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.                      |  |  |  |

| 54  | P10.11                                        | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |  |

|     | U1C0_SCLK<br>OUT                              | O1         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                            |  |  |  |

|     | BRKOUT                                        | 02         | St/B | OCDS Break Signal Output                                                                                                                                                      |  |  |  |

|     | U1C0_DX1D                                     | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                             |  |  |  |

|     | TMS_B                                         | IH         | St/B | <b>JTAG Test Mode Selection Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.     |  |  |  |

| 55  | P10.12                                        | O0 / I     | St/B | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |  |

|     | U1C0_DOUT                                     | 01         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                             |  |  |  |

|     | TDO_B                                         | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |  |

|     | U1C0_DX0C                                     | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                              |  |  |  |

| _   | U1C0_DX1E                                     | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                             |  |  |  |

| 56  | P10.13                                        | O0 / I     | St/B | Bit 13 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |  |

|     | U1C0_DOUT                                     | 01         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                             |  |  |  |

|     | U1C0_SELO<br>3                                | O3         | St/B | USIC1 Channel 0 Select/Control 3 Output                                                                                                                                       |  |  |  |

|     | U1C0_DX0D                                     | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                              |  |  |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------|--------------------------------------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                  |  |  |

| 58    | P10.14                                                 | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                                           |  |  |

|       | U1C0_SELO<br>1                                         | O1     | St/B | USIC1 Channel 0 Select/Control 1 Output                                                                                                                                                                                                                                                                                                   |  |  |

|       | U0C1_DOUT                                              | O2     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                                         |  |  |

|       | ESR2_2                                                 | I      | St/B | ESR2 Trigger Input 2                                                                                                                                                                                                                                                                                                                      |  |  |

|       | U0C1_DX0C                                              | Ι      | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                          |  |  |

| 59    | P10.15                                                 | O0 / I | St/B | Bit 15 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                                           |  |  |

|       | U1C0_SELO<br>2                                         | O1     | St/B | USIC1 Channel 0 Select/Control 2 Output                                                                                                                                                                                                                                                                                                   |  |  |

|       | U0C1_DOUT                                              | 02     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                                         |  |  |

|       | U1C0_DOUT                                              | O3     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                                         |  |  |

|       | U0C1_DX1C                                              | I      | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                                                                                         |  |  |

| 60    | XTAL2                                                  | 0      | Sp/M | Crystal Oscillator Amplifier Output                                                                                                                                                                                                                                                                                                       |  |  |

| 61    | XTAL1                                                  | I      | Sp/M | <b>Crystal Oscillator Amplifier Input</b><br>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected.<br>Voltages on XTAL1 must comply to the core supply voltage $V_{\text{DDIM}}$ .                                                                                                                   |  |  |

|       | ESR2_9                                                 | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                                      |  |  |

| 62    | PORST                                                  | 1      | In/B | Power On Reset Input<br>A low level at this pin resets the XC2336B<br>completely. A spike filter suppresses input pulses<br><10 ns. Input pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition<br>should be 120 ns.<br>An internal pull-up device will hold this pin high<br>when nothing is driving it. |  |  |

| 63    | ESR0                                                   | O0 / I | St/B | <b>External Service Request 0</b><br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                                                                                                                                                                              |  |  |

|       | U1C0_DX0E                                              | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                          |  |  |

|       | U1C0_DX2B                                              | 1      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                                                                       |  |  |

| Table                          | Table 6Pin Definitions and Functions (cont'd) |       |      |                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------|-----------------------------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                            | Symbol                                        | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                       |  |  |  |

| 6                              | V <sub>DDIM</sub>                             | -     | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                                                                                                                           |  |  |  |

| 24,<br>41,<br>57               | V <sub>DDI1</sub>                             | -     | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All V <sub>DDI1</sub> pins must be connected to each other.                                                                                                            |  |  |  |

| 9                              | V <sub>DDPA</sub>                             | -     | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.                                                                                                                      |  |  |  |

|                                |                                               |       |      | Note: The A/D_Converters and ports P5, P6 and P15 are fed from supply voltage $V_{DDPA}$ .                                                                                                                                                                                                     |  |  |  |

| 2,<br>16,<br>18,               | V <sub>DDPB</sub>                             | -     | PS/B | <b>Digital Pad Supply Voltage for Domain B</b><br>Connect decoupling capacitors to adjacent $V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.                                                                                                                         |  |  |  |

| 32,<br>34,<br>48,<br>50,<br>64 |                                               |       |      | Note: The on-chip voltage regulators and all ports except P5, P6 and P15 are fed from supply voltage $V_{\rm DDPB}$ .                                                                                                                                                                          |  |  |  |

| 1,<br>17,<br>33,               | V <sub>SS</sub>                               | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line or ground-plane.                                                                                                                                                                                               |  |  |  |

| 49                             |                                               |       |      | Note: Also the exposed pad is connected<br>internally to $V_{SS}$ . To improve the EMC<br>behavior, it is recommended to connect the<br>exposed pad to the board ground.<br>For thermal aspects, please refer to the<br>Data Sheet. Board layout examples are<br>given in an application note. |  |  |  |

### XC2336B XC2000 Family / Value Line

### **Functional Description**

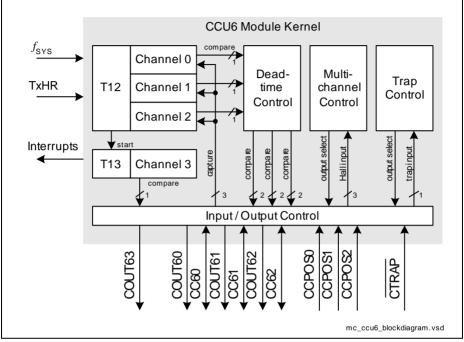

### Figure 7 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

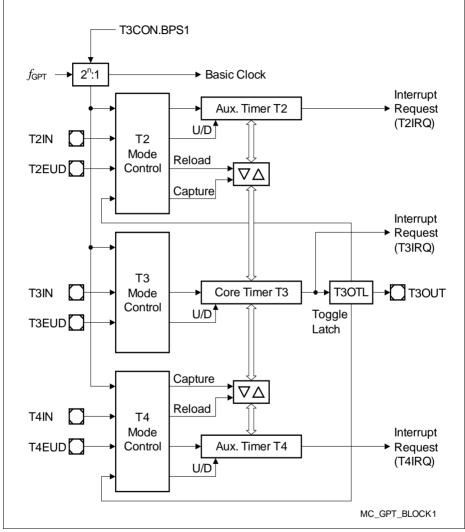

Figure 8 Block Diagram of GPT1

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

## 3.11 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 7 + 2 multiplexed input channels and a sample and hold circuit have been integrated onchip. 2 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XC2336B support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- · Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

### 3.14 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

### 3.15 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz).

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

| Parameter                         | Symbol             |                           | Values | 5    | Unit | Note /<br>Test Condition                 |

|-----------------------------------|--------------------|---------------------------|--------|------|------|------------------------------------------|

|                                   |                    | Min.                      | Тур.   | Max. |      |                                          |

| Output High voltage <sup>7)</sup> | V <sub>OH</sub> CC | V <sub>DDP</sub> -<br>1.0 | _      | -    | V    | $I_{\text{OH}} \ge I_{\text{OHmax}}$     |

|                                   |                    | V <sub>DDP</sub> - 0.4    | -      | -    | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{8}$ |

| Output Low Voltage <sup>7)</sup>  | $V_{\sf OL}\sf CC$ | -                         | -      | 0.4  | V    | $I_{\rm OL} \leq I_{\rm OLnom}^{8)}$     |

|                                   |                    | -                         | -      | 1.0  | V    | $I_{\rm OL} \leq I_{\rm OLmax}$          |

#### Table 16 DC Characteristics for Upper Voltage Range (cont'd)

1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ-)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- 5) Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device.

- 6) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level.

- 7) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- As a rule, with decreasing output current the output levels approach the respective supply level (V<sub>OL</sub>->V<sub>SS</sub>, V<sub>OH</sub>->V<sub>DDP</sub>). However, only the levels for nominal output currents are verified.

### 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XC2336B into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                |                                         | Values       | 5                                     | Unit | Note /                                   |

|-----------------------------------------------------------------------|-----------------------|-----------------------------------------|--------------|---------------------------------------|------|------------------------------------------|

|                                                                       |                       | Min. Typ.                               |              | Max.                                  |      | <b>Test Condition</b>                    |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC  | -1                                      | -            | 1                                     | %    | $\Delta T_{\rm J} \le 10^{\circ}{\rm C}$ |

| Internal clock source frequency                                       | $f_{\rm INT}{\rm CC}$ | 4.8                                     | 5.0          | 5.2                                   | MHz  |                                          |

| Wakeup clock source                                                   | $f_{\rm WU}$ CC       | 400                                     | -            | 700                                   | kHz  | FREQSEL= 00                              |

| frequency <sup>2)</sup>                                               |                       | 210                                     | -            | 390                                   | kHz  | FREQSEL= 01                              |

|                                                                       |                       | 140                                     | -            | 260                                   | kHz  | FREQSEL= 10                              |

|                                                                       |                       | 110                                     | -            | 200                                   | kHz  | FREQSEL= 11                              |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC   | 1.5                                     | 2.0          | 2.4                                   | ms   | <i>f</i> <sub>WU</sub> = 500 kHz         |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC   | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | -            | 12 /<br>f <sub>WU</sub> <sup>3)</sup> | μs   |                                          |

| Core voltage (PVC) supervision level                                  | $V_{\rm PVC}{ m CC}$  | V <sub>LV</sub> -<br>0.03               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.07 <sup>4)</sup>  | V    | 5)                                       |

| Supply watchdog (SWD) supervision level                               | <b>U</b> ( )          | V <sub>LV</sub> -<br>0.10 <sup>6)</sup> | $V_{\rm LV}$ | V <sub>LV</sub> +<br>0.15             | V    | voltage_range=<br>lower <sup>5)</sup>    |

|                                                                       |                       | V <sub>LV</sub> -<br>0.15               | $V_{\rm LV}$ | V <sub>LV</sub> +<br>0.15             | V    | voltage_range=<br>upper <sup>5)</sup>    |

|                                                                       |                       | V <sub>LV</sub> -<br>0.30               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.30                | V    | $V_{\rm LV}$ = 5.5 V <sup>5)</sup>       |

### Table 22 Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

### 4.6 Flash Memory Parameters

The XC2336B is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XC2336B's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                  | Symbol               |      | Values          | 5               | Unit   | Note /                                                                            |

|------------------------------------------------------------|----------------------|------|-----------------|-----------------|--------|-----------------------------------------------------------------------------------|

|                                                            |                      | Min. | Тур.            | Max.            |        | Test Condition                                                                    |

| Parallel Flash module                                      | $N_{\rm PP}~{ m SR}$ | -    | -               | 2 <sup>1)</sup> |        | $N_{\rm FL_RD} \leq 1$                                                            |

| program/erase limit<br>depending on Flash read<br>activity |                      | _    | -               | 1 <sup>2)</sup> |        | N <sub>FL_RD</sub> > 1                                                            |

| Flash erase endurance for security pages                   | $N_{\rm SEC}{ m SR}$ | 10   | -               | -               | cycles | $t_{\rm RET} \ge 20$ years                                                        |

| Flash wait states3)                                        | $N_{\rm WSFLAS}$     | 1    | -               | -               |        | f <sub>SYS</sub> ≤8 MHz                                                           |

|                                                            | <sub>н</sub> SR      | 2    | -               | _               |        | $f_{\rm SYS} \le 13 \ {\rm MHz}$                                                  |

|                                                            |                      | 3    | -               | -               |        | $f_{\rm SYS} \le 17 \; {\rm MHz}$                                                 |

|                                                            |                      | 4    | -               | _               |        | $f_{\rm SYS}$ > 17 MHz                                                            |

| Erase time per<br>sector/page                              | t <sub>ER</sub> CC   | _    | 7 <sup>4)</sup> | 8.0             | ms     |                                                                                   |

| Programming time per page                                  | t <sub>PR</sub> CC   | -    | 3 <sup>4)</sup> | 3.5             | ms     |                                                                                   |

| Data retention time                                        | t <sub>RET</sub> CC  | 20   | -               | _               | years  | $N_{\rm ER} \le 1,000 \; {\rm cycl}$ es                                           |

| Drain disturb limit                                        | $N_{\rm DD}{\rm SR}$ | 32   | -               | -               | cycles |                                                                                   |

| Number of erase cycles                                     | $N_{ER}SR$           | _    | -               | 15.000          | cycles | $t_{\text{RET}} \ge 5$ years;<br>Valid for Flash<br>module 1 (up to<br>64 kbytes) |

|                                                            |                      | -    | _               | 1.000           | cycles | $t_{\text{RET}} \ge 20 \text{ years}$                                             |

#### Table 25 Flash Parameters

The unused Flash module(s) can be erased/programmed while code is executed and/or data is read from only one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be erased/programmed.

## 4.7.2 Definition of Internal Timing

The internal operation of the XC2336B is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC2336B.

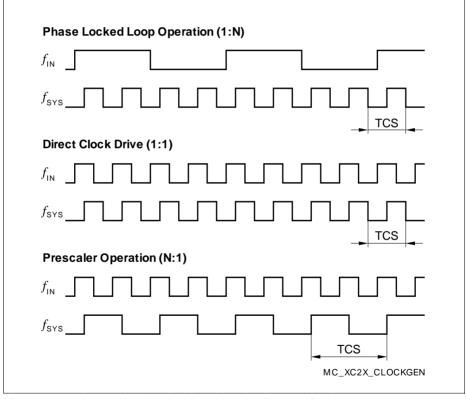

Figure 19 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 19** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

## 4.7.4 Pad Properties

The output pad drivers of the XC2336B can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . Therefore the following tables list the pad parameters for the upper voltage range and the lower voltage range, respectively.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 28** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}}$  typ. 5 V;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

| Parameter                                                    | Symbol                  | Values |      |      | Unit | Note /                      |

|--------------------------------------------------------------|-------------------------|--------|------|------|------|-----------------------------|

|                                                              |                         | Min.   | Тур. | Max. |      | Test Condition              |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 4.0  | mA   | Driver_Strength<br>= Medium |

|                                                              |                         | _      | -    | 10   | mA   | Driver_Strength<br>= Strong |

|                                                              |                         | _      | -    | 0.5  | mA   | Driver_Strength<br>= Weak   |

| Nominal output driver current (absolute value)               | I <sub>Onom</sub><br>CC | -      | -    | 1.0  | mA   | Driver_Strength<br>= Medium |

|                                                              |                         | -      | -    | 2.5  | mA   | Driver_Strength<br>= Strong |

|                                                              |                         | _      | -    | 0.1  | mA   | Driver_Strength<br>= Weak   |

Table 28 Standard Pad Parameters for Upper Voltage Range

### Table 31 USIC SSC Master Mode Timing for Lower Voltage Range

| Parameter                                                               | Symbol            |                                        | Values | 5    | Unit | Note /<br>Test Condition |

|-------------------------------------------------------------------------|-------------------|----------------------------------------|--------|------|------|--------------------------|

|                                                                         |                   | Min.                                   | Тур.   | Max. |      |                          |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | t <sub>SYS</sub> -<br>10 <sup>1)</sup> | -      | -    | ns   |                          |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | t <sub>SYS</sub> -<br>9 <sup>1)</sup>  | -      | -    | ns   |                          |

| Data output DOUT valid time                                             | t <sub>3</sub> CC | -7                                     | -      | 11   | ns   |                          |

| Receive data input setup time to SCLKOUT receive edge                   | t <sub>4</sub> SR | 40                                     | -      | -    | ns   |                          |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge                | t <sub>5</sub> SR | -5                                     | -      | _    | ns   |                          |

1)  $t_{SYS} = 1 / f_{SYS}$

**Table 32** is valid under the following conditions:  $C_L = 20 \text{ pF}$ ; *SSC*= slave ; voltage\_range= upper

### Table 32 USIC SSC Slave Mode Timing for Upper Voltage Range

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                   |                           | Min.   | Тур. | Max. |      | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

### Package and Reliability

## Package Outlines

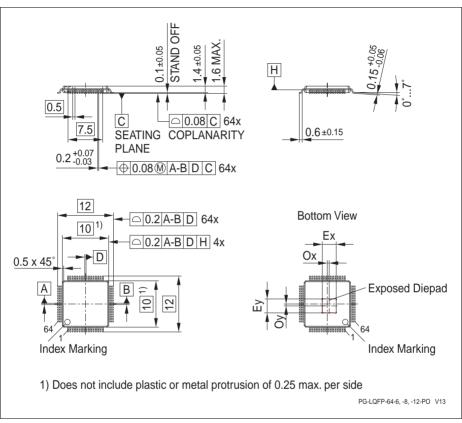

Figure 28 PG-LQFP-64-6/-24 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages

### Package and Reliability

## 5.2 Thermal Considerations

When operating the XC2336B in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} \cdot V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- · Reduce the number of output pins

- Reduce the load on active output drivers