Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | AM13L                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 10MHz                                                       |

| Connectivity               | I <sup>2</sup> C, UART/USART                                |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                |

| Number of I/O              | 69                                                          |

| Program Memory Size        | 64KB (64K × 8)                                              |

| Program Memory Type        | ReRAM                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                 |

| Data Converters            | A/D 8x12b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 80-TQFP                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/panasonic/mn101lr05dxw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Hardware Features

#### Features

In this document, the divided clock and the frequency of it are described as follows: Divided clock:Clock name/n (n: division ratio)

Frequency: f<sub>Clock name</sub>

- CPU Core

- AM13L core

- LOAD-STORE architecture (3- or 4-stage Pipeline)

- Machine Cycle and Operating Voltage

- High-Speed mode 100 ns / 10 MHz (Max) (V<sub>DD30</sub>: 1.8 V to 3.6 V) 1.0 μs / 1 MHz (Max) (V<sub>DD30</sub>: 1.3 V to 3.6 V)

Low-Speed Mode

25  $\mu s$  / 40 kHz (Max)  $(V_{DD30}:\,1.1$  V to 3.6 V)

- Operating Mode

- NORMAL mode (High-Speed mode)

- SLOW mode (Low-Speed mode)

- HALT mode (High-Speed/Low-Speed mode)

- STOP mode

- · Embedded Memory

- ROM (ReRAM): 64 KB (Programmable area and Data area vary depending on the ROM name. For details, see Table:1.1.1.)

- RAM: 4 KB

- ReRAM Specification

- Program voltage ( $V_{DD30}$ ): 1.8 V to 3.6 V

- Program cycles: 1000 times (Program area), 100000 times (Data area)

- Data is rewritable in bytes without data erase.

- Clock Oscillator (4 circuits)

- External Low-Speed Oscillation (SOSCCLK): 32.768 kHz (crystal or ceramic)

- External High-Speed Oscillation (HOSCCLK): up to 10 MHz (crystal or ceramic)

- Internal Low-Speed Oscillation (SRCCLK): 40 kHz  $\pm$  20 % (V<sub>DD30</sub>: 1.1 V to 3.6 V)

- Internal High-Speed Oscillation (HRCCLK): 10/8 MHz  $\pm 3$  % (V<sub>DD30</sub>: 1.8 V to 3.6 V)

- $1 \text{ MHz} \pm 10 \% (V_{DD30}: 1.3 \text{ V to } 3.6 \text{ V})$

\* MN101LR02D does not have external high-speed oscillation (HOSCCLK).

- Internal Operating Clock

- System Clock (SYSCLK): 10 MHz (Max)

- SYSCLK is generated by dividing HCLK or SCLK, and the division ratio is 1, 2, 4, 8, 16 or 32. HCLK: HOSCCLK or HRCCLK SCLK: SOSCCLK or SRCCLK

- \* MN101LR02D cannot be selected HOSCCLK.

| <ul> <li>Interrupt Circuit<br/>MN101LR05D/04D/0<br/>MN101LR02D:</li> </ul>                                                | <ul> <li>03D: 31 internal interrupts (except for NMI)</li> <li>8 external interrupts (IRQ interrupt: 7, KEY interrupt: 1)</li> <li>29 internal interrupts (except for NMI)</li> <li>3 external interrupts (IRQ interrupt: 2, KEY interrupt: 1)</li> </ul> |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>DMA (1 channel)</li> <li>Data transfer size:</li> <li>Maximum transfer c</li> <li>Activation trigger:</li> </ul> | 8 bits/16 bits<br>counts: 1023<br>external interrupts / internal interrupts / software (setting the DMA start bit)                                                                                                                                        |

|                                                                                                                           | OT)<br>atchdog time-out generates NMI, and 2nd consecutive time-out generates a LSI reset.<br>CCLK (SOSCCLK or SRCCLK)                                                                                                                                    |

| - General-purpose 16-                                                                                                     | bit timer (Timer 0/1/2/3/4/5): 6 units<br>-bit timer (Timer 7/8/9): 3 units<br>r 6) /Time-base timer: 1 unit each<br>r (RTC-TBT): 1 unit                                                                                                                  |

| simpl<br>- Clock Source: HCL                                                                                              | re wave output, additional pulse PWM output, event count,<br>le pulse width measurement<br>K, HCLK/4, HCLK/16, HCLK/32, HCLK/64, SCLK, SYSCLK/2, SYSCLK/4,<br>4010 input                                                                                  |

| - Clock Source: HCL                                                                                                       | re wave output, event count, 16-bit cascade connection (connected with Timer 0)<br>K, HCLK/4, HCLK/16, HCLK/64, HCLK/128, SCLK, SYSCLK/2, SYSCLK/8,<br>//1IO input                                                                                        |

| simpl<br>- Clock Source: HCL<br>or TM                                                                                     | re wave output, additional pulse PWM output, event count,<br>le pulse width measurement<br>K, HCLK/4, HCLK/16, HCLK/32, HCLK/64, SCLK, SYSCLK/2, SYSCLK/4,<br><i>I</i> /2IO input<br>not be used simple pulse width measurement.                          |

| - Clock Source: HCL                                                                                                       | re wave output, event count, 16-bit cascade connection (connected with Timer 2)<br>K, HCLK/4, HCLK/16, HCLK/64, HCLK/128, SCLK, SYSCLK/2, SYSCLK/8,<br>//3IO input                                                                                        |

| simpl<br>- Clock Source: HCL                                                                                              | re wave output, additional pulse PWM output, event count,<br>le pulse width measurement<br>K, HCLK/4, HCLK/16, HCLK/32, HCLK/64, SCLK, SYSCLK/2, SYSCLK/4,<br>/I4IO input                                                                                 |

| - Clock Source: HCL<br>or TM                                                                                              | re wave output, event count, 16-bit cascade connection (connected with Timer 4)<br>K, HCLK/4, HCLK/16, HCLK/64, HCLK/128, SCLK, SYSCLK/2, SYSCLK/8,<br><i>A</i> 5IO input<br>not be used square wave output, event count and TM5IO.                       |

```

<Timer 6>

```

- Function: One-minute timer can be generated in combination with a time base timer.

- Clock Source: HCLK, HCLK/2<sup>7</sup>, HCLK/2<sup>13</sup>, SYSCLK, SCLK, SCLK/2<sup>7</sup> or SCLK/2<sup>13</sup>

<Time Base Timer>

- Function: An interrupt can be generated at a given set time.

- Clock Source: HCLK or SCLK

- Interrupt generation cycle:  $2^{N}/f_{HCLK}$ ,  $2^{N}/f_{SCLK}$  (N = 7, 8, 9, 10, 12, 13, 14, 15)

- <Timer 7>

- Function: Square wave output, PWM output (duty/cycle are programmable), one-shot pulse output, IGBT output, event count, and input capture

- Clock Source: Generated clock by dividing HCLK, SYSCLK, SCLK, or TM7IO input by 1, 2, 4 or 16.

<Timer 8 >

- Function: Square wave output, PWM output (duty/cycle are programmable), event count, and input capture

- Clock Source: Generated clock by dividing HCLK, SYSCLK, SCLK, or TM8IO input by 1, 2, 4 or 16.

- <Timer 9 >

- Function: Square wave output, PWM output (duty/cycle are programmable), event count, and input capture

- Clock Source: Generated clock by dividing HCLK, SYSCLK, SCLK, or TM9IO input by 1, 2, 4 or 16. \* MN101LR03D and MN101LR02D

- cannot be used square wave output, PWM output, event count and TM9IO.

- <RTC time base timer (RTC-TBT)>

- Function: Clock generation for the Real Time Clock (RTC) Frequency correction (Correction Range: ±488 ppm to ±31220 ppm, Accuracy: approx. 0.48 ppm to 30.52 ppm)

- Clock Source: SOSCCLK or SRCCLK

- Function: Calendar calculation, adjustment of leap year

- Periodic interrupt (0.5 s, 1 s, 1 min or 1 hour)

Alarm0 interrupt (date/hour/minute), Alarm1 interrupt (month/day/hour/minute)

Buzzer Output/Inverted Buzzer Output

- Output frequency:  $f_{HCLK}/2^M$  (M = 9, 10, 11, 12, 13, 14),  $f_{SCLK}/2^N$  (N = 3, 4)

- \* MN101LR02D can be used inverted buzzer output only.

- Serial Interface: 4 units

<Serial Interface 0, 1> (Full duplex UART/Clock synchronous serial)

- Function:

Full duplex UART:

Parity check, Detection of overrun error/framing error, Selectable transfer bits of 7 or 8 Clock synchronous serial (SPI compatible):

2,3 or 4-wire communication, MSB/LSB first selectable, multiple bytes transmission is available.

- Clock Source: external clock, dedicated baud rate timer

<Serial Interface 2, 3> (Multi-master IIC/Clock synchronous serial)

- Function:

Multi-master IIC

Clock synchronous serial (SPI compatible):

2,3 or 4-wire communication, MSB/LSB first selectable, multiple bytes transmission is available.

- Clock Source: external clock, dedicated baud rate timer

<sup>&</sup>lt;Real Time Clock (RTC)>

• Package

MN101LR05D: TQFP080-P-1212(12 mm square, 0.5 mm pitch, halogen free)MN101LR04D: TQFP064-P-1010(10 mm square, 0.5 mm pitch, halogen free)MN101LR03D: TQFP048-P-0707(7 mm square, 0.5 mm pitch, halogen free)MN101LR02D: HQFN032-A-0505(5 mm square, 0.5 mm pitch, halogen free)

Panasonic "halogen free" semiconductor products refer to the products made of molding resin and interposer which conform to the following standards.

- Bromine: 900 ppm (Maximum Concentration Value)

- Chlorine: 900 ppm (Maximum Concentration Value)

- Bromine + Chlorine: 1500 ppm (Maximum Concentration Value)

The above-mentioned standards are based on the numerical value described in IEC61249-2-21. Antimony and its compounds are not added intentionally.

• Operating Ambient Temperature: Ta = -40 °C to 85 °C

# 1.3 Comparison of Product Specification

| Function              | Specification                            | MN101LR05D                              | MN101LR04D                              | MN101LR03D                             | MN101LR02D                          |

|-----------------------|------------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------|-------------------------------------|

| Port                  | I/O port                                 | 69 pins                                 | 53 pins                                 | 37 pins                                | 22 pins                             |

|                       | N-channel transistor drive strength      | 55 pins                                 | 41 pins                                 | 27 pins                                | 19 pins                             |

| Interrupt             | Internal interrupt                       | 31                                      | 31                                      | 31                                     | 29                                  |

|                       | External interrupt                       | 8<br>(7: IRQ0-6, 1: KEY0-7)             | 8<br>(7: IRQ0-6, 1: KEY1-7)             | 8<br>(7: IRQ0-6, 1: KEY1-5)            | 3<br>(2: IRQ4-5, 1: KEY1-7)         |

| Timer 5               | Timer I/O                                | TM5IO                                   | TM5IO                                   | TM5IO                                  | - (*1)                              |

| Timer 9               | Timer I/O                                | ТМ9Ю                                    | ТМ9Ю                                    | - (*1)                                 | - (*1)                              |

| Serial<br>interface 1 |                                          | $\checkmark$                            | $\checkmark$                            | $\checkmark$                           | -                                   |

| Serial<br>interface 3 | Serial communication pins                | SBO3/SDA3<br>SBT3/SCL3<br>SBI3<br>SBCS3 | SBO3/SDA3<br>SBT3/SCL3<br>SBI3<br>SBCS3 | SBO3/SDA3<br>SBT3/SCL3<br>-<br>-       | SBO3/SDA3<br>SBT3/SCL3<br>SBI3<br>- |

|                       | Clock synchronous                        | 2, 3 or 4-wire                          | 2, 3 or 4-wire                          | 2-wire                                 | 2 or 3-wire                         |

|                       | SPI compatible                           | $\checkmark$                            | $\checkmark$                            | - (*2)                                 | - (*2)                              |

| Buzzer                | Buzzer output<br>/Inverted buzzer output | BUZ<br>NBUZ                             | BUZ<br>NBUZ                             | BUZ<br>NBUZ                            | -<br>NBUZ                           |

| ADC                   | Analog input                             | 8 pins (AN0-7)                          | 6 pins (AN2-7)                          | 4 pins (AN2-5)                         | 3 pins (AN3-5)                      |

| LCD driver            | Segment output                           | 43 pins (SEG0-42)<br>/39 pins (SEG4-42) | 31 pins (SEG0-30)                       | 21 pins (SEG0-20)                      | -                                   |

|                       | Common output                            | 4 pins (COM0-3)<br>/8 pins (COM0-7)     | 4 pins (COM0-3)                         | 4 pins (COM0-3)                        | -                                   |

| Oscillation           |                                          | HOSCCLK<br>SOSCCLK<br>HRCCLK<br>SRCCLK  | HOSCCLK<br>SOSCCLK<br>HRCCLK<br>SRCCLK  | HOSCCLK<br>SOSCCLK<br>HRCCLK<br>SRCCLK | -<br>SOSCCLK<br>HRCCLK<br>SRCCLK    |

| Package               |                                          | 80-pin TQFP                             | 64-pin TQFP                             | 48-pin TQFP                            | 32-pin HQFN                         |

#### Table:1.3.1 Functions

\*1 Timer function is available.

\*2 Chip select pin is not assigned.

| I/O   |              |              | ΜN           | 1101         | LRC          | )5D          |              |              |              |              | M٢           | 1101         | LRC          | 4D           |              |              |              |              | ΜN           | 1101         | LRC          | )3D          |              |              |              |              | M٨           | 1101         | LR0          | 2D           |              |   |

|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---|

| Port  | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0 |

| Port0 | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            | $\checkmark$ |              | -            | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | - |

| Port1 | $\checkmark$ | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ |              |              | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | - |

| Port2 | $\checkmark$ | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            | -            | -            | $\checkmark$ | -            | -            | -            | -            | -            | -            | - |

| Port3 | $\checkmark$ |              | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | - |

| Port4 | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            |              |              |              | $\checkmark$ | $\checkmark$ | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |   |

| Port5 | $\checkmark$ | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            | - |

| Port6 | $\checkmark$ | -            | -            | -            | -            |              | $\checkmark$ | -            | -            | -            | - |

| Port7 | $\checkmark$ | -            | -            | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            |              |              | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            | -            | -            | -            | - |

| Port8 | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -            | -            | -            | -            | -            | -            | - |

| 2     |              |              | mon          | l . l        | 0            | a set        |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |              |   |

#### Table:1.3.2 Functions of I/O Port

$\sqrt{}$  : implemented I/O port

√ : implemented I/O port (selectable N-channel transistor drive strength)

- : not implemented

#### Table:1.3.3 Functions of LCD Control

| I/O   |           |           | I         | MN101     | LR05D                 | )                     |                       |                       |           |           | 1         | MN101     | LR04D     | )         |           |           | MN101LR03D |           |           |           |           |           |           |           |

|-------|-----------|-----------|-----------|-----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Port  | 7         | 6         | 5         | 4         | 3                     | 2                     | 1                     | 0                     | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         | 7          | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| Port2 | -         | SEG<br>36 | SEG<br>37 | SEG<br>38 | SEG<br>39             | SEG<br>40             | SEG<br>41             | SEG<br>42             | -         | SEG<br>28 | -         | -         | -         | -         | SEG<br>29 | SEG<br>30 | -          | SEG<br>20 | -         | -         | -         | -         | -         | -         |

| Port3 | SEG<br>28 | SEG<br>29 | SEG<br>30 | SEG<br>31 | SEG<br>32             | SEG<br>33             | SEG<br>34             | SEG<br>35             | SEG<br>20 | SEG<br>21 | SEG<br>22 | SEG<br>23 | SEG<br>24 | SEG<br>25 | SEG<br>26 | SEG<br>27 | SEG<br>12  | SEG<br>13 | SEG<br>14 | SEG<br>15 | SEG<br>16 | SEG<br>17 | SEG<br>18 | SEG<br>19 |

| Port4 | SEG<br>20 | SEG<br>21 | SEG<br>22 | SEG<br>23 | SEG<br>24             | SEG<br>25             | SEG<br>26             | SEG<br>27             | SEG<br>12 | SEG<br>13 | SEG<br>14 | SEG<br>15 | SEG<br>16 | SEG<br>17 | SEG<br>18 | SEG<br>19 | -          | -         | -         | SEG<br>7  | SEG<br>8  | SEG<br>9  | SEG<br>10 | SEG<br>11 |

| Port5 | SEG<br>12 | SEG<br>13 | SEG<br>14 | SEG<br>15 | SEG<br>16             | SEG<br>17             | SEG<br>18             | SEG<br>19             | SEG<br>8  | SEG<br>9  | SEG<br>10 | -         | -         | -         | -         | SEG<br>11 | SEG<br>4   | SEG<br>5  | SEG<br>6  | -         | -         | -         | -         | -         |

| Port6 | SEG<br>4  | SEG<br>5  | SEG<br>6  | SEG<br>7  | SEG<br>8              | SEG<br>9              | SEG<br>10             | SEG<br>11             | SEG<br>0  | SEG<br>1  | SEG<br>2  | SEG<br>3  | SEG<br>4  | SEG<br>5  | SEG<br>6  | SEG<br>7  | -          | -         | -         | -         | SEG<br>0  | SEG<br>1  | SEG<br>2  | SEG<br>3  |

| Port7 | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  | COM<br>4/<br>SEG<br>0 | COM<br>5/<br>SEG<br>1 | COM<br>6/<br>SEG<br>2 | COM<br>7/<br>SEG<br>3 | -         | -         | -         | -         | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  | -          | -         | -         | -         | COM<br>0  | COM<br>1  | COM<br>2  | COM<br>3  |

| Port8 | -         | -         | VLC<br>2  | VLC<br>3  | C2                    | C1                    | -                     | -                     | -         | -         | VLC<br>2  | VLC<br>3  | C2        | C1        | -         | -         | -          | -         | VLC<br>2  | VLC<br>3  | C2        | C1        | -         | -         |

| -     | VLC1      |           |           |           |                       | VLC1                  |                       |                       |           |           |           |           | VLC1      |           |           |           |            |           |           |           |           |           |           |           |

-: not implemented

LCD control function is not implemented in MN101LR02D.

Ē

Set "0" to the registers and bits corresponding to the functions which are not implemented.

|                | Pin            | No.            |                | Power supply                             | Port | External                    | Timer  | Serial      | Buzzer        | A/D |

|----------------|----------------|----------------|----------------|------------------------------------------|------|-----------------------------|--------|-------------|---------------|-----|

| MN101<br>LR05D | MN101<br>LR04D | MN101<br>LR03D | MN101<br>LR02D | /Oscillations<br>/Reset<br>/Mode control |      | interrupt<br>/KEY interrupt |        | interface   | /Clock output |     |

| 45             | 37             | 29             | 21             |                                          | P44  |                             |        | SBCS2A      |               |     |

| 46             | 38             |                |                |                                          | P45  |                             |        | SBI1B/RXD1B |               |     |

| 47             | 39             |                |                |                                          | P46  |                             |        | SBO1B/TXD1B |               |     |

| 48             | 40             |                |                |                                          | P47  |                             |        | SBT1B       |               |     |

| 49             | 41             |                |                |                                          | P50  |                             |        | SBCS1B      |               |     |

| 50             |                |                |                |                                          | P51  |                             |        | SBI3B       |               |     |

| 51             |                |                |                |                                          | P52  |                             |        | SBO3B/SDA3B |               |     |

| 52             |                |                |                |                                          | P53  |                             |        | SBT3B/SCL3B |               |     |

| 53             |                |                |                |                                          | P54  | KEY0B                       |        | SBCS3B      |               |     |

| 54             | 42             | 30             | 22             |                                          | P55  | KEY1B                       | TM1IOA |             |               |     |

| 55             | 43             | 31             | 23             |                                          | P56  | KEY2B                       | TM3IOA |             |               |     |

| 56             | 44             | 32             | 24             |                                          | P57  | KEY3B                       | TM8IOA |             | CLKOUTB       |     |

| 57             | 45             | 33             |                |                                          | P60  | IRQ0B                       |        |             |               |     |

| 58             | 46             | 34             |                |                                          | P61  | IRQ1B                       |        |             |               |     |

| 59             | 47             | 35             |                |                                          | P62  | IRQ2B                       |        |             |               |     |

| 60             | 48             | 36             |                |                                          | P63  | IRQ3B                       |        |             |               |     |

| 61             | 49             |                | 25             |                                          | P64  | KEY4B                       |        | SBI0A/RXD0A |               |     |

| 62             | 50             |                | 26             |                                          | P65  | KEY5B                       |        | SBO0A/TXD0A |               |     |

| 63             | 51             |                | 27             |                                          | P66  | KEY6B                       |        | SBT0A       |               |     |

| 64             | 52             |                | 28             |                                          | P67  | KEY7B                       |        | SBCS0A      |               |     |

| 65             | 53             | 37             |                |                                          | P70  | IRQ6B                       |        |             |               |     |

| 66             | 54             | 38             |                |                                          | P71  | IRQ5B                       |        |             |               |     |

| 67             | 55             | 39             |                |                                          | P72  | IRQ4B                       | TM3IOB |             |               |     |

| 68             | 56             | 40             |                |                                          | P73  |                             | TM5IOB |             |               |     |

| 69             |                |                |                |                                          | P74  |                             |        |             |               |     |

| 70             |                |                |                |                                          | P75  |                             |        |             |               |     |

| 71             |                |                |                |                                          | P76  |                             |        |             |               |     |

| 72             |                |                |                |                                          | P77  |                             |        |             |               |     |

| 73             | 57             | 41             |                | C1                                       | P82  |                             |        |             |               |     |

| 74             | 58             | 42             |                | C2                                       | P83  |                             |        |             |               |     |

| 75             | 59             | 43             |                | VLC3                                     | P84  |                             |        |             |               |     |

| 76             | 60             | 44             |                | VLC2                                     | P85  |                             |        |             |               |     |

| 77             | 61             | 45             |                | VLC1                                     |      |                             |        |             |               |     |

| 78             | 62             | 46             | 29             | VDD30                                    |      |                             |        |             |               |     |

| 79             | 63             | 47             | 30             | VDD18                                    |      |                             |        |             |               |     |

| 80             | 64             | 48             | 31             | VDD11                                    |      |                             |        |             |               |     |

\* See Table:1.3.3 for LCD control pins.

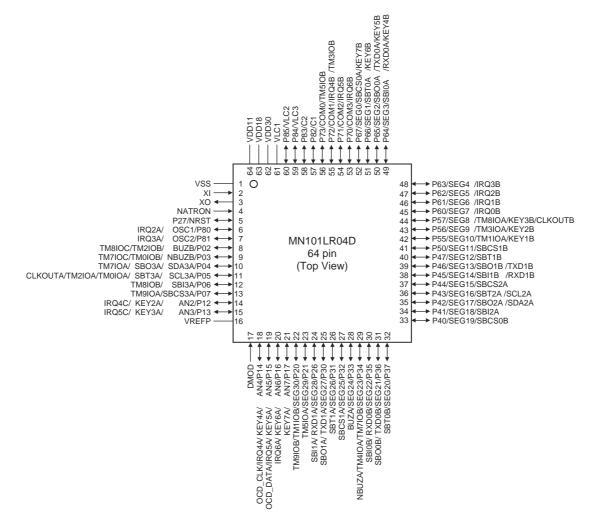

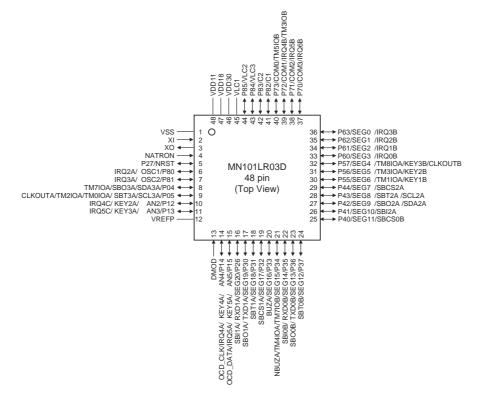

Figure:1.4.2 MN101LR04D Pin Configuration

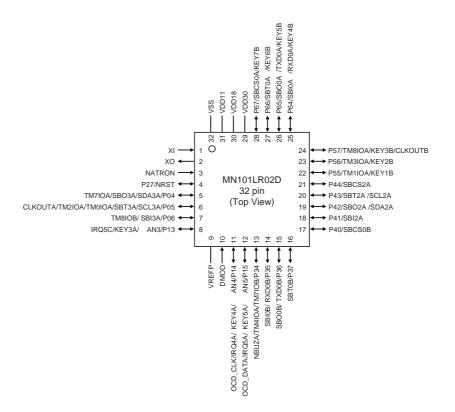

Figure:1.4.4 MN101LR02D Pin Configuration

|                | Pin r          | name           |                | lpput/           | Output                    |                                                                                                                           |  |  |  |  |

|----------------|----------------|----------------|----------------|------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MN101LR<br>05D | MN101LR<br>04D | MN101LR<br>03D | MN101LR<br>02D | Input/<br>Output | drive strength selectable | Description                                                                                                               |  |  |  |  |

| P00            | -              | -              | -              |                  | Yes                       | Port 0                                                                                                                    |  |  |  |  |

| P01            | -              | -              | -              |                  | Yes                       | <ul> <li>At each port, the I/O direction and the pull-up resistor con-<br/>nection is controlled individually.</li> </ul> |  |  |  |  |

| P02            | P02            | -              | -              |                  | Yes                       | -At LSI reset, each pin is set to input mode and the pull-up                                                              |  |  |  |  |

| P03            | P03            | -              | -              | Input/           | Yes                       | resistor is not connected.<br>-The drive strength of output Nch transistor can be changed.                                |  |  |  |  |

| P04            | P04            | P04            | P04            | Output           | Yes                       |                                                                                                                           |  |  |  |  |

| P05            | P05            | P05            | P05            |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P06            | P06            | -              | P06            |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P07            | P07            | -              | -              |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P10            | -              | -              | -              |                  | No                        | Port 1                                                                                                                    |  |  |  |  |

| P11            | -              | -              | -              |                  | No                        | <ul> <li>At each port, the I/O direction and the pull-up resistor con-<br/>nection is controlled individually.</li> </ul> |  |  |  |  |

| P12            | P12            | P12            | -              |                  | No                        | -At LSI reset, each pin is set to input mode and the pull-up resistor is not connected.                                   |  |  |  |  |

| P13            | P13            | P13            | P13            | Input/           | No                        |                                                                                                                           |  |  |  |  |

| P14            | P14            | P14            | P14            | Output           | No                        |                                                                                                                           |  |  |  |  |

| P15            | P15            | P15            | P15            |                  | No                        |                                                                                                                           |  |  |  |  |

| P16            | P16            | -              | -              |                  | No                        |                                                                                                                           |  |  |  |  |

| P17            | P17            | -              | -              |                  | No                        |                                                                                                                           |  |  |  |  |

| P20            | P20            | -              | -              |                  | Yes                       | Port 2                                                                                                                    |  |  |  |  |

| P21            | P21            | -              | -              |                  | Yes                       | <ul> <li>At each port, the I/O direction and the pull-up resistor con-<br/>nection is controlled individually.</li> </ul> |  |  |  |  |

| P22            | -              | -              | -              |                  | Yes                       | -At LSI reset, each pin is set to input mode and the pull-up resistor is not connected.                                   |  |  |  |  |

| P23            | -              | -              | -              | Input/<br>Output | Yes                       | -The drive strength of output Nch transistor can be changed.                                                              |  |  |  |  |

| P24            | -              | -              | -              |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P25            | -              | -              | -              |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P26            | P26            | P26            | -              |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P27            | P27            | P27            | P27            | Input/<br>Output | No                        | Port 2<br>-LSI is reset by setting P2OUT.P2OUT7 to "0".                                                                   |  |  |  |  |

| P30            | P30            | P30            | -              |                  | Yes                       | Port 3                                                                                                                    |  |  |  |  |

| P31            | P31            | P31            | -              |                  | Yes                       | -At each port, the I/O direction and the pull-up resistor con-<br>nection is controlled individually.                     |  |  |  |  |

| P32            | P32            | P32            | -              |                  | Yes                       | -At LSI reset, each pin is set to input mode and the pull-up resistor is not connected.                                   |  |  |  |  |

| P33            | P33            | P33            | -              | Input/           | Yes                       | -The drive strength of output Nch transistor can be changed.                                                              |  |  |  |  |

| P34            | P34            | P34            | P34            | Output           | Yes                       |                                                                                                                           |  |  |  |  |

| P35            | P35            | P35            | P35            |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P36            | P36            | P36            | P36            |                  | Yes                       |                                                                                                                           |  |  |  |  |

| P37            | P37            | P37            | P37            |                  | Yes                       |                                                                                                                           |  |  |  |  |

#### Table:1.4.2 General-purpose Port Function Pin

| INN101LR<br>05DMN101LR<br>04DMN101LR<br>03DInput<br>02DOutput<br>Outputdrive strength<br>selectableDescriptionP40P40P40P40P40P40P40P40P40P41P41P41P41P41P41P41P41P42P42P42P42P42P42P42P43P43P43Input/YesAt ESI reset, each port, the I/O direction and the pull-resistor is not connectedThe drive strength of output Nch transistor can be chanP44P44P44P44P44OutputYes-The drive strength of output Nch transistor can be chanP45P45YesYesP46P46YesP50P50YesP51YesP52P53P54OutputYesYesP55P56P56P56P56P56P57P57P57P57P57P57P61P61-P63P63P63P64P64P65P65P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P67P64 <td< th=""><th></th><th>Pin n</th><th>name</th><th></th><th></th><th>Output</th><th></th></td<>                                                                                                                                                                                                                                                                                                        |     | Pin n | name |     |        | Output         |                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|-----|--------|----------------|-------------------------------------------------------------------------------------------------------|

| P41P41P41P41P41P41P42P42P42P42P42Yes-At each port, the I/O direction and the pull-up resistor on nection is controlled individually.P43P43P43P43P43P43P43-At each port, the I/O direction and the pull-resistor is not connected.P44P44P44P44P44P44P44P44P44P45P45Yes-The drive strength of output Nch transistor can be chanP46P46Yes-The drive strength of output Nch transistor can be chanP47P47YesP50P50YesP51YesP52YesP53YesP54YesP55P55P55YesP56P56P56P56P57P57P57YesP60P60P61P61-P63P63P63-P64-P64P65P65-P66P66-P66P66P66-P66P66P66P66P66P66P66P66P67P68P64P64P65P66P66P66<                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |       |      |     |        | drive strength | Description                                                                                           |

| P41P41P41P41Yesnection is controlled individually.<br>-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.<br>-The drive strength of output Nch transistor can be chanP43P43P43P43P43Input/<br>VesYes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.<br>-The drive strength of output Nch transistor can be chanP44P44P44P44OutputYes-P45P45Yes-P46P46YesP47P47YesP50P50YesP51P52P53P54P55P55P55P55P56P56P56P57P57P57P60P60-P61P61-P62P62P62P63P63-P64P64P64P64P65P65P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66                                                                                                                                                                                                                                                                                                                                                                                                   | P40 | P40   | P40  | P40 |        | Yes            | Port 4                                                                                                |

| P42P42P42P42P42P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P43P44P44P44P44P44P44P44P44P44P44P44P44P44P44P44P44P44P45P45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P41 | P41   | P41  | P41 |        | Yes            | -At each port, the I/O direction and the pull-up resistor con-                                        |

| P43P43P43P43Input/<br>OutputYes-The drive strength of output Nch transistor can be chanP44P44P44P44VesYes-The drive strength of output Nch transistor can be chanP45P45Yes-P46P46Yes-P47P47Yes-P50P50YesP51Yes-P52P53YesP54OutputP55P55P55P56P56P56P56YesP57P57P57YesP60P60P61P61-P62P62-P63P63P63P64OutputYesP65P65-P66P66-P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P67P68P66 <td>P42</td> <td>P42</td> <td>P42</td> <td>P42</td> <td></td> <td>Yes</td> <td>-At LSI reset, each pin is set to input mode and the pull-up</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P42 | P42   | P42  | P42 |        | Yes            | -At LSI reset, each pin is set to input mode and the pull-up                                          |

| P44         P44         P44         Output         Yes           P45         P45         -         -         Yes           P46         P46         -         -         Yes           P47         P47         -         -         Yes           P50         P50         -         -         Yes           P51         -         -         -         Yes           P52         -         -         -         Yes           P53         -         -         -         -           P54         -         -         -         -           P53         -         -         -         -           P54         -         -         -         -           P55         P55         P55         P56         P56         P56           P56         P56         P57         P57         P57         P57         P57           P57         P57         P57         P57         P57         P57         P57           P61         P61         -         -         -         -         -           P62         P62         P63         -         P | P43 | P43   | P43  | P43 | Input/ | Yes            | -The drive strength of output Nch transistor can be changed.                                          |

| P46P46YesP47P47YesP50P50YesPort 5P51Yes-At each port, the I/O direction and the pull-up resistor or nection is controlled individually.P52YesP53Yes-At LSI reset, each pin is set to input mode and the pull-resistor is not connected.P53YesP54OutputYesP55P55P55P55YesP56P56P56YesP57P57P57YesP60P60P60-P61P61-YesP62P62P62-P63P63P63-P64P64-P65P65YesP66P66-P66P66P67P65Yes-P68P66P64YesP65P65P66P66P66P66P67P68P68P64P64P65P66P66P66P66P67P68P68P69P69P60P60P61P62P63P64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P44 | P44   | P44  | P44 |        | Yes            |                                                                                                       |

| P47P47YesP50P50YesP51P51P52P53P54P55P55P55P55Yes-P56P56P56P56Yes-P57P57P57P57YesP60P60-Yes-P61P61-YesP63P63P63-Input/<br>OutputP64P64-P64P66P66-P66P66P66-P66P66-P66P66-P67P62P62P63P63-P64YesP65P66P66YesP66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P66P67P68<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P45 | P45   | -    | -   |        | Yes            |                                                                                                       |

| P50P50YesPort 5<br>-At each port, the I/O direction and the pull-up resistor or<br>nection is controlled individually.P51Yes-At each port, the I/O direction and the pull-up resistor or<br>nection is controlled individually.P53Yes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.P53Yes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.P54OutputYes-P55P55P55P55YesP56P56P56P56YesP60P60P60-YesP61P61-YesYesP63P63P63-Input/Yes-P64P64-P64YesYes-P65P65-P66Yes-P66P66-P66Yes-                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P46 | P46   | -    | -   |        | Yes            |                                                                                                       |

| P51P52<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P47 | P47   | -    | -   |        | Yes            |                                                                                                       |

| P51Yesnection is controlled individually.<br>-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.P53Input/Yes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.P53OutputYes-The drive strength of output Nch transistor can be chanP54OutputYes-The drive strength of output Nch transistor can be chanP55P55P55P55P56Yes-P56P56P56P57Yes-P57P57P57P57YesP60P60-Yes-P61P61-Yes-P62P62P62-YesP63P63P63-Input/P64P64-P64YesP65P65-P65YesP66P66-P66YesYesP66P66-P66P66P66Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P50 | P50   | -    | -   |        | Yes            | Port 5                                                                                                |

| P52 <t< td=""><td>P51</td><td>-</td><td>-</td><td>-</td><td></td><td>Yes</td><td>-At each port, the I/O direction and the pull-up resistor con-</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P51 | -     | -    | -   |        | Yes            | -At each port, the I/O direction and the pull-up resistor con-                                        |

| P53Input/<br>OutputYes<br>Yes-The drive strength of output Nch transistor can be chan<br>YesP54OutputYesP55P55P55P55YesYesP56P56P56P56YesP57P57P57P57YesP60P60P60P61P61YesP62P62P62-YesP63P63P63-Input/<br>OutputYesP64P64-P65P65-P65P66-P66YesP66P66-P66YesP66P66-P66P66P66-P66P66-P66P66-P66P66-P66P66P66P66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P52 | -     | -    | -   |        | Yes            | -At LSI reset, each pin is set to input mode and the pull-up                                          |

| P54OutputYesP55P55P55P55P55YesP56P56P56P56YesP57P57P57P57YesP60P60YesP61P61-Yes-P62P62P62-YesP63P63P63-Input/P64P64-P64OutputP65P65-P65YesP66P66-P66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P53 | -     | -    | -   | Input/ | Yes            | resistor is not connected.<br>-The drive strength of output Nch transistor can be changed.            |

| P56P56P56P56YesP57P57P57P57YesP60P60P60-YesP61P61-YesPort 6P62P62P62-YesP63P63P63-Input/P64P64-P65P65P66P66-P66P66P66-P66P66P66-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P54 | -     | -    | -   |        | Yes            |                                                                                                       |

| P57P57P57YesP60P60-YesPort 6P61P61-Yes-At each port, the I/O direction and the pull-up resistor or<br>nection is controlled individually.P62P62P62-YesP63P63P63-Input/<br>OutputYesP64P64-P65P65-P66P66-P66Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P55 | P55   | P55  | P55 |        | Yes            |                                                                                                       |

| P60P60P60-YesPort 6P61P61-YesPort 6P62P62P62-YesAt each port, the I/O direction and the pull-up resistor or<br>nection is controlled individually.P63P63P63-Input/Yes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.P64P64-P64OutputYes-The drive strength of output Nch transistor can be chan<br>YesP65P65-P66YesYes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P56 | P56   | P56  | P56 |        | Yes            |                                                                                                       |

| P61P61P61-Yes-At each port, the I/O direction and the pull-up resistor of nection is controlled individually.<br>-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.<br>-The drive strength of output Nch transistor can be chan<br>P64P63P63P63-Input/<br>OutputYes-At each port, the I/O direction and the pull-up resistor of nection is controlled individually.<br>-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.<br>-The drive strength of output Nch transistor can be chan<br>P65P65P65-P65YesP66P66-P66Yes                                                                                                                                                                                                                                                                                                                                                                                                                                 | P57 | P57   | P57  | P57 |        | Yes            |                                                                                                       |

| P61P61P61-Yesnection is controlled individually.P62P62P62-Yes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.P63P63P63-Input/Yes-The drive strength of output Nch transistor can be chan<br>YesP64P64-P65P65YesYesP66P66-P66YesYes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P60 | P60   | P60  | -   |        | Yes            | Port 6                                                                                                |

| P62P62P62-Yes-At LSI reset, each pin is set to input mode and the pull-<br>resistor is not connected.<br>- The drive strength of output Nch transistor can be chan<br>YesP64P64-P64OutputYes-P65P65-P65YesYesYesP66P66-P66YesYes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P61 | P61   | P61  | -   |        | Yes            | -At each port, the I/O direction and the pull-up resistor con-                                        |

| P63P63P63-Input/Yes-The drive strength of output Nch transistor can be chanP64P64-P64OutputYesP65P65-P65YesP66P66-P66Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P62 | P62   | P62  | -   |        | Yes            | -At LSI reset, each pin is set to input mode and the pull-up                                          |

| P64P64P64OutputYesP65P65-P65YesP66P66-P66Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P63 | P63   | P63  | -   | Input/ | Yes            | resistor is not connected.<br>-The drive strength of output Nch transistor can be changed.            |

| P66 P66 - P66 Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P64 | P64   | -    | P64 |        | Yes            |                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P65 | P65   | -    | P65 |        | Yes            |                                                                                                       |

| P67 P67 - P67 Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P66 | P66   | -    | P66 |        | Yes            |                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P67 | P67   | -    | P67 |        | Yes            |                                                                                                       |

| P70 P70 P70 - Yes Port 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P70 | P70   | P70  | -   |        | Yes            | Port 7                                                                                                |

| P71 P71 P71 - Yes -At each port, the I/O direction and the pull-up resistor connection is controlled individually.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P71 | P71   | P71  | -   |        | Yes            | -At each port, the I/O direction and the pull-up resistor con-                                        |

| P72 P72 P72 - Yes -At LSI reset, each pin is set to input mode and the pull-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P72 | P72   | P72  | -   |        | Yes            | -At LSI reset, each pin is set to input mode and the pull-up                                          |

| P73 P73 P73 - Input/ Yes resistor is not connected.<br>-The drive strength of output Nch transistor can be chan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P73 | P73   | P73  | -   | Input/ | Yes            | -The drive strength of output Nch transistor can be changed.                                          |