Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 13x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f071c8u6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 87 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

# 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The

precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                                                    | Memory address            |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------|---------------------------|--|--|--|

| VREFINT_CAL            | Raw data acquired at a<br>temperature of 30 °C (± 5 °C),<br>V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |  |  |  |

Table 4. Internal voltage reference calibration values

# 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

# 3.11 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This digital Interface supports the following features:

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

Six DAC trigger inputs are used in the device. The DAC is triggered through the timer trigger outputs and the DAC interface is generating its own DMA requests.

# 3.12 Comparators (COMP)

The device embeds two fast rail-to-rail low-power comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output pins

- Internal reference voltage or submultiple (1/4, 1/2, 3/4). Refer to *Table 28: Embedded internal reference voltage* for the value and precision of the internal reference voltage.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- Periodic wakeup unit with programmable resolution and period.

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- Three anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s), Fast mode (up to 400 kbit/s) and Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive on most of the associated I/Os.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

| Table 8. Comparison of I <sup>2</sup> C analog and digital filters | Table 8. Comparison of I | <sup>2</sup> C analog and digital filters |

|--------------------------------------------------------------------|--------------------------|-------------------------------------------|

|--------------------------------------------------------------------|--------------------------|-------------------------------------------|

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts

#### Pinouts and pin descriptions

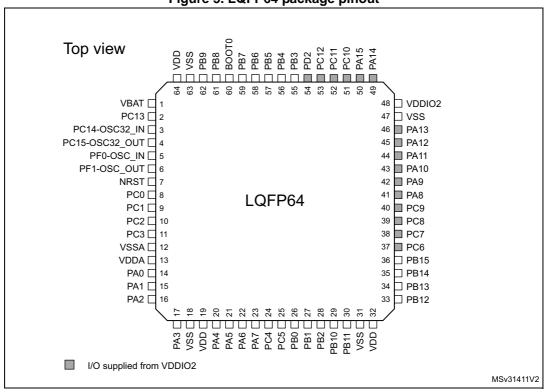

Figure 5. LQFP64 package pinout

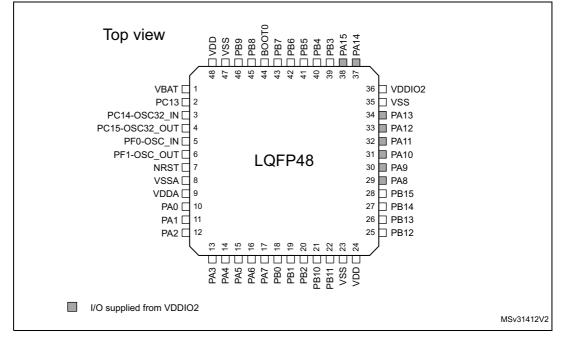

Figure 6. LQFP48 package pinout

DocID025451 Rev 6

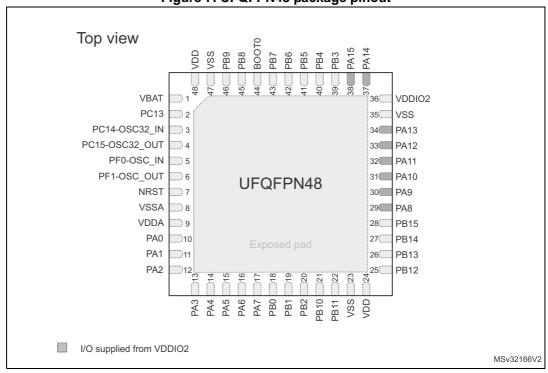

Figure 7. UFQFPN48 package pinout

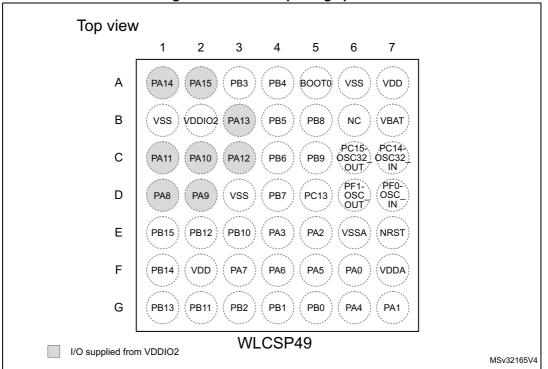

Figure 8. WLCSP49 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

#### Table 14. Alternate functions selected through GPIOA\_AFR registers for port A AF1 AF2 AF4 Pin name AF0 AF3 AF5 AF7 AF6 USART2 CTS TIM2 CH1 ETR TSC G1 IO1 USART4 TX PA0 COMP1 OUT \_ -EVENTOUT USART2\_RTS TIM2\_CH2 TSC\_G1\_IO2 USART4 RX PA1 TIM15 CH1N \_ TIM15\_CH1 TIM2\_CH3 PA2 USART2\_TX TSC\_G1\_IO3 COMP2\_OUT ---PA3 TIM15 CH2 USART2 RX TIM2\_CH4 TSC G1 IO4 ----SPI1\_NSS, I2S1\_WS USART2\_CK TSC\_G2\_IO1 TIM14\_CH1 PA4 \_ --\_ SPI1\_SCK, I2S1\_CK CEC TIM2\_CH1\_ETR TSC\_G2\_IO2 PA5 \_ \_ \_ USART3 CTS COMP1 OUT PA6 SPI1 MISO, I2S1 MCK TIM3 CH1 TIM1 BKIN TSC G2 103 TIM16 CH1 EVENTOUT SPI1\_MOSI, I2S1\_SD TIM3\_CH2 TIM1\_CH1N TSC\_G2\_IO4 TIM14\_CH1 TIM17\_CH1 COMP2\_OUT PA7 **EVENTOUT** PA8 МСО USART1 CK TIM1\_CH1 **EVENTOUT** CRS\_SYNC \_ \_ USART1 TX TIM15 BKIN TIM1 CH2 TSC G4 IO1 PA9 ----TIM17\_BKIN USART1 RX TIM1 CH3 TSC\_G4\_IO2 PA10 ----EVENTOUT PA11 USART1\_CTS TIM1 CH4 TSC\_G4\_IO3 COMP1 OUT -\_ -EVENTOUT USART1\_RTS TIM1 ETR TSC\_G4\_IO4 COMP2 OUT PA12 ---SWDIO IR\_OUT PA13 \_ --\_ SWCLK USART2\_TX PA14 -\_ -SPI1 NSS, I2S1 WS USART2 RX TIM2 CH1 ETR **EVENTOUT** USART4 RTS PA15 \_ --

DocID025451 Rev 6

39/122

| Bus  | Boundary address          | Size    | Peripheral             |

|------|---------------------------|---------|------------------------|

|      | 0x4800 1800 - 0x5FFF FFFF | ~384 MB | Reserved               |

|      | 0x4800 1400 - 0x4800 17FF | 1 KB    | GPIOF                  |

|      | 0x4800 1000 - 0x4800 13FF | 1 KB    | GPIOE                  |

| AHB2 | 0x4800 0C00 - 0x4800 0FFF | 1 KB    | GPIOD                  |

| ANDZ | 0x4800 0800 - 0x4800 0BFF | 1 KB    | GPIOC                  |

|      | 0x4800 0400 - 0x4800 07FF | 1 KB    | GPIOB                  |

|      | 0x4800 0000 - 0x4800 03FF | 1 KB    | GPIOA                  |

|      | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved               |

|      | 0x4002 4000 - 0x4002 43FF | 1 KB    | TSC                    |

|      | 0x4002 3400 - 0x4002 3FFF | 3 KB    | Reserved               |

|      | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC                    |

|      | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved               |

| AHB1 | 0x4002 2000 - 0x4002 23FF | 1 KB    | Flash memory interface |

|      | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved               |

|      | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC                    |

|      | 0x4002 0400 - 0x4002 0FFF | 3 KB    | Reserved               |

|      | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA                    |

|      | 0x4001 8000 - 0x4001 FFFF | 32 KB   | Reserved               |

|      | 0x4001 5C00 - 0x4001 7FFF | 9 KB    | Reserved               |

|      | 0x4001 5800 - 0x4001 5BFF | 1 KB    | DBGMCU                 |

|      | 0x4001 4C00 - 0x4001 57FF | 3 KB    | Reserved               |

|      | 0x4001 4800 - 0x4001 4BFF | 1 KB    | TIM17                  |

|      | 0x4001 4400 - 0x4001 47FF | 1 KB    | TIM16                  |

|      | 0x4001 4000 - 0x4001 43FF | 1 KB    | TIM15                  |

|      | 0x4001 3C00 - 0x4001 3FFF | 1 KB    | Reserved               |

|      | 0x4001 3800 - 0x4001 3BFF | 1 KB    | USART1                 |

|      | 0x4001 3400 - 0x4001 37FF | 1 KB    | Reserved               |

|      | 0x4001 3000 - 0x4001 33FF | 1 KB    | SPI1/I2S1              |

| APB  | 0x4001 2C00 - 0x4001 2FFF | 1 KB    | TIM1                   |

|      | 0x4001 2800 - 0x4001 2BFF | 1 KB    | Reserved               |

|      | 0x4001 2400 - 0x4001 27FF | 1 KB    | ADC                    |

|      | 0x4001 0800 - 0x4001 23FF | 7 KB    | Reserved               |

|      | 0x4001 0400 - 0x4001 07FF | 1 KB    | EXTI                   |

|      | 0x4001 0000 - 0x4001 03FF | 1 KB    | SYSCFG + COMP          |

|      | 0x4000 8000 - 0x4000 FFFF | 32 KB   | Reserved               |

# Table 20. STM32F071x8/xB peripheral register boundary addresses

DocID025451 Rev 6

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

# 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

# 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

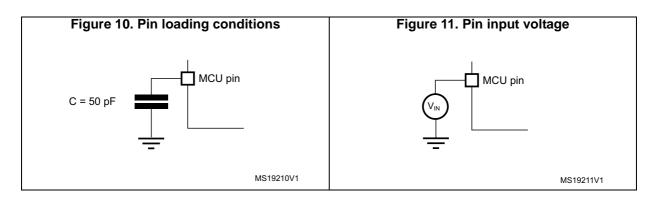

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

# 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

DocID025451 Rev 6

| Tabl                                | Table 21. Programmable voltage detector characteristics (continued) |              |      |      |                     |      |  |  |  |  |

|-------------------------------------|---------------------------------------------------------------------|--------------|------|------|---------------------|------|--|--|--|--|

| Symbol                              | Parameter                                                           | Conditions   | Min  | Тур  | Max                 | Unit |  |  |  |  |

| V                                   | PVD threshold 6                                                     | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |  |  |  |  |

| V <sub>PVD6</sub>                   |                                                                     | Falling edge | 2.56 | 2.68 | 2.8                 | V    |  |  |  |  |

| V                                   | PVD threshold 7                                                     | Rising edge  | 2.76 | 2.88 | 3                   | V    |  |  |  |  |

| V <sub>PVD7</sub>                   |                                                                     | Falling edge | 2.66 | 2.78 | 2.9                 | V    |  |  |  |  |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                                      | -            | -    | 100  | -                   | mV   |  |  |  |  |

| I <sub>DD(PVD)</sub>                | PVD current consumption                                             | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μA   |  |  |  |  |

Table 27. Programmable voltage detector characteristics (continued)

1. Guaranteed by design, not tested in production.

## 6.3.4 Embedded reference voltage

The parameters given in *Table 28* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                 | Parameter                                                           | Conditions                        | Min                  | Тур  | Max                | Unit   |  |  |  |  |

|------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|--|--|--|--|

| V <sub>REFINT</sub>    | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |  |  |  |  |

| t <sub>START</sub>     | ADC_IN17 buffer startup time                                        | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |  |  |  |  |

| t <sub>S_vrefint</sub> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |  |  |  |  |

| $\Delta V_{REFINT}$    | Internal reference voltage<br>spread over the<br>temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |  |  |  |  |

| T <sub>Coeff</sub>     | Temperature coefficient                                             | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |  |  |  |  |

Table 28. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

| Sym-                    | Poro                                                                             |                                |                                                              |                                                     | Тур                                                 | @V <sub>DD</sub> ( | V <sub>DD</sub> = V | / <sub>DDA</sub> ) |       | Max <sup>(1)</sup>        |                           |                            |      |                    |  |

|-------------------------|----------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------|---------------------|--------------------|-------|---------------------------|---------------------------|----------------------------|------|--------------------|--|

| Sym- Para-<br>bol meter |                                                                                  | Conditions                     |                                                              | 2.0 V                                               | 2.4 V                                               | 2.7 V              | 3.0 V               | 3.3 V              | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |                    |  |

|                         | Supply current in                                                                | mod                            | julator in run<br>de, all<br>illators OFF                    | 15.4                                                | 15.5                                                | 15.6               | 15.7                | 15.8               | 15.9  | 23 <sup>(2)</sup>         | 49                        | 68 <sup>(2)</sup>          |      |                    |  |

| I <sub>DD</sub>         | Stop<br>mode                                                                     | pow                            | ulator in low-<br>ver mode, all<br>illators OFF              | 3.2                                                 | 3.3                                                 | 3.4                | 3.5                 | 3.6                | 3.7   | 8(2)                      | 33                        | 51 <sup>(2)</sup>          |      |                    |  |

|                         | Supply current in                                                                | LSI<br>ON                      | ON and IWDG                                                  | 0.8                                                 | 1.0                                                 | 1.1                | 1.2                 | 1.3                | 1.4   | -                         | -                         | -                          |      |                    |  |

|                         | Standby<br>mode                                                                  | LSI<br>OFF                     | OFF and IWDG                                                 | 0.6                                                 | 0.7                                                 | 0.9                | 0.9                 | 1.0                | 1.1   | 2.1 <sup>(2)</sup>        | 2.6                       | 3.1 <sup>(2)</sup>         |      |                    |  |

|                         | Supply<br>current in<br>Stop<br>mode                                             | Supply                         |                                                              | NO                                                  | Regulator in<br>run mode, all<br>oscillators<br>OFF | 2.1                | 2.2                 | 2.3                | 2.5   | 2.6                       | 2.8                       | 3.5 <sup>(2)</sup>         | 3.6  | 4.6 <sup>(2)</sup> |  |

| :                       |                                                                                  | pp වූ                          | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 2.1                                                 | 2.2                                                 | 2.3                | 2.5                 | 2.6                | 2.8   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>         | μΑ   |                    |  |

|                         | Supply current in                                                                | VDC                            | LSI ON and<br>IWDG ON                                        | 2.5                                                 | 2.7                                                 | 2.8                | 3.0                 | 3.2                | 3.5   | -                         | -                         | -                          |      |                    |  |

| <br>                    | Standby<br>mode                                                                  |                                | LSI OFF and<br>IWDG OFF                                      | 1.9                                                 | 2.1                                                 | 2.2                | 2.3                 | 2.5                | 2.6   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>         |      |                    |  |

| 'DDA                    | I <sub>DDA</sub><br>Supply<br>current in<br>Stop<br>mode<br>Supply<br>current in | Supply                         | OFF                                                          | Regulator in<br>run mode, all<br>oscillators<br>OFF | 1.3                                                 | 1.3                | 1.4                 | 1.4                | 1.5   | 1.5                       | -                         | -                          | -    |                    |  |

|                         |                                                                                  | V <sub>DDA</sub> monitoring OF | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.3                                                 | 1.3                                                 | 1.4                | 1.4                 | 1.5                | 1.5   | -                         | -                         | -                          |      |                    |  |

|                         |                                                                                  | V <sub>DD</sub>                | LSI ON and<br>IWDG ON                                        | 1.7                                                 | 1.8                                                 | 1.9                | 2.0                 | 2.1                | 2.2   | -                         | -                         | -                          |      |                    |  |

|                         | Standby<br>mode                                                                  |                                | LSI OFF and<br>IWDG OFF                                      | 1.2                                                 | 1.2                                                 | 1.2                | 1.3                 | 1.3                | 1.4   | -                         | -                         | -                          |      |                    |  |

Table 31. Typical and maximum consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

2. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

| Symbol               |                                    | Conditions                                                                       | Тур @ V <sub>ВАТ</sub> |       |       |       |       |       |                           |                           |                            |      |

|----------------------|------------------------------------|----------------------------------------------------------------------------------|------------------------|-------|-------|-------|-------|-------|---------------------------|---------------------------|----------------------------|------|

|                      | Parameter                          |                                                                                  | 1.65 V                 | 1.8 V | 2.4 V | 2.7 V | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DD_VBAT</sub> | RTC<br>domain<br>supply<br>current | LSE & RTC ON; "Xtal<br>mode": lower driving<br>capability;<br>LSEDRV[1:0] = '00' | 0.5                    | 0.6   | 0.7   | 0.8   | 1.1   | 1.2   | 1.3                       | 1.7                       | 2.3                        | μA   |

|                      |                                    | LSE & RTC ON; "Xtal<br>mode" higher driving<br>capability;<br>LSEDRV[1:0] = '11' | 0.8                    | 0.9   | 1.1   | 1.2   | 1.4   | 1.6   | 1.7                       | 2.1                       | 2.8                        |      |

Table 32. Typical and maximum current consumption from the  $\rm V_{BAT}$  supply

1. Data based on characterization results, not tested in production.

# Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (for example control registers)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol             | Parameter  | Conditions                                                                           | Monitored        | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|--------------------|------------|--------------------------------------------------------------------------------------|------------------|------------------------------------------------|------|

| Symbol             |            | Conditions                                                                           | frequency band   | 8/48 MHz                                       | Onic |

|                    | Peak level | $V_{DD}$ = 3.6 V, $T_A$ = 25 °C,<br>LQFP100 package<br>compliant with<br>IEC 61967-2 | 0.1 to 30 MHz    | -2                                             |      |

| 0                  |            |                                                                                      | 30 to 130 MHz    | 27                                             | dBµV |

| S <sub>EMI</sub> P | reak level |                                                                                      | 130 MHz to 1 GHz | 17                                             |      |

|                    |            |                                                                                      | EMI Level        | 4                                              | -    |

#### Table 49. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol           | Description                                                                                          | Func<br>suscer     | Unit               |      |

|------------------|------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

|                  | Description                                                                                          | Negative injection | Positive injection | Unit |

| I <sub>INJ</sub> | Injected current on BOOT0 and PF1 pins                                                               | -0                 | NA                 |      |

|                  | Injected current on PC0 pin                                                                          | -0                 | +5                 |      |

|                  | Injected current on PA11 and PA12 pins with induced leakage current on adjacent pins less than -1 mA | -5                 | NA                 | mA   |

|                  | Injected current on all other FT and FTf pins                                                        | -5                 | NA                 |      |

|                  | Injected current on all other TTa, TC and RST pins                                                   | -5                 | +5                 |      |

## Table 52. I/O current injection susceptibility

# 6.3.14 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 53* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                     | Conditions                   | Min                                            | Тур                | Мах                                          | Unit |  |

|------------------|-------------------------------|------------------------------|------------------------------------------------|--------------------|----------------------------------------------|------|--|

|                  |                               | TC and TTa I/O               | -                                              | -                  | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  | -    |  |

| V <sub>IL</sub>  | Low lovel input               | FT and FTf I/O               | -                                              | -                  | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |  |

|                  | Low level input<br>voltage    | BOOT0                        | -                                              | -                  | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V    |  |

|                  |                               | All I/Os except<br>BOOT0 pin | -                                              | -                  | 0.3 V <sub>DDIOx</sub>                       |      |  |

|                  | High level input<br>voltage   | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                  | -                                            |      |  |

|                  |                               | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                  | -                                            |      |  |

| V <sub>IH</sub>  |                               | BOOT0                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                  | -                                            | V    |  |

|                  |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                  | -                                            |      |  |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis | TC and TTa I/O               | -                                              | 200 <sup>(1)</sup> | -                                            |      |  |

|                  |                               | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup> | -                                            | mV   |  |

|                  |                               | BOOT0                        | -                                              | 300 <sup>(1)</sup> | -                                            |      |  |

#### Table 53. I/O static characteristics

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                                                                              | Parameter                        | Conditions                                       | Min | Max | Unit |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------|-----|-----|------|--|--|

|                                        | f <sub>max(IO)out</sub>                                                             | Maximum frequency <sup>(3)</sup> | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$ |     | 2   | MHz  |  |  |

| Fm+<br>configuration                   | t <sub>f(IO)out</sub>                                                               | Output fall time                 |                                                  |     | 12  | ns   |  |  |

|                                        | t <sub>r(IO)out</sub>                                                               | Output rise time                 |                                                  |     | 34  |      |  |  |

| (4)                                    | f <sub>max(IO)out</sub>                                                             | Maximum frequency <sup>(3)</sup> |                                                  |     | 0.5 | MHz  |  |  |

|                                        | t <sub>f(IO)out</sub>                                                               | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                 | -   | 16  | ns   |  |  |

|                                        | t <sub>r(IO)out</sub>                                                               | Output rise time                 |                                                  | -   | 44  | 115  |  |  |

| -                                      | t <sub>EXTIpw</sub> Pulse width of external signals detected by the EXTI controller |                                  | -                                                | 10  | -   | ns   |  |  |

Table 55. I/O AC characteristics<sup>(1)(2)</sup> (continued)

The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32F0xxxx RM0091 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design, not tested in production.

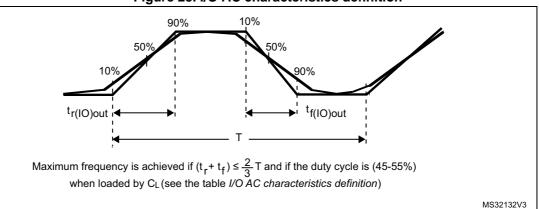

- 3. The maximum frequency is defined in *Figure 23*.

- 4. When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the STM32F0xxxx reference manual RM0091 for a detailed description of Fm+ I/O configuration.

#### Figure 23. I/O AC characteristics definition

# 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                | Parameter                     | Conditions | Min                                         | Тур | Мах                                      | Unit |

|-----------------------|-------------------------------|------------|---------------------------------------------|-----|------------------------------------------|------|

| V <sub>IL(NRST)</sub> | NRST input low level voltage  | -          | -                                           | -   | 0.3 V <sub>DD</sub> +0.07 <sup>(1)</sup> | V    |

| V <sub>IH(NRST)</sub> | NRST input high level voltage | -          | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -   | -                                        | v    |

Table 56. NRST pin characteristics

| Symbol                                 | Parameter                             | Conditions                                            | Min                                                                        | Тур | Max                                               | Unit                       |

|----------------------------------------|---------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|

| f <sub>TRIG</sub> <sup>(2)</sup>       | External trigger frequency            | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -                                                                          | -   | 823                                               | kHz                        |

|                                        |                                       | 12-bit resolution                                     | -                                                                          | -   | 17                                                | 1/f <sub>ADC</sub>         |

| V <sub>AIN</sub>                       | Conversion voltage range              | -                                                     | 0                                                                          | -   | V <sub>DDA</sub>                                  | V                          |

| R <sub>AIN</sub> <sup>(2)</sup>        | External input impedance              | See <i>Equation 1</i> and <i>Table 58</i> for details | -                                                                          | -   | 50                                                | kΩ                         |

| R <sub>ADC</sub> <sup>(2)</sup>        | Sampling switch resistance            | -                                                     | -                                                                          | -   | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(2)</sup>        | Internal sample and hold<br>capacitor | -                                                     | -                                                                          | -   | 8                                                 | pF                         |

| t <sub>CAL</sub> <sup>(2)(3)</sup>     | Calibration time                      | f <sub>ADC</sub> = 14 MHz                             |                                                                            | 5.9 |                                                   | μs                         |

| <sup>I</sup> CAL` /` /                 |                                       | -                                                     |                                                                            | 83  |                                                   | 1/f <sub>ADC</sub>         |

|                                        |                                       | ADC clock = HSI14                                     | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(2)(4)</sup> | ADC_DR register ready<br>latency      | ADC clock = PCLK/2                                    | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                       | ADC clock = PCLK/4                                    | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                       | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$               | 0.196                                                                      |     |                                                   | μs                         |

|                                        |                                       | $f_{ADC} = f_{PCLK}/2$                                | 5.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> (2)                  | Trigger conversion latency            | $f_{ADC} = f_{PCLK}/4 = 12 \text{ MHz}$               | 0.219                                                                      |     |                                                   | μs                         |

|                                        |                                       | $f_{ADC} = f_{PCLK}/4$                                | 10.5                                                                       |     | 1/f <sub>PCLK</sub>                               |                            |

|                                        |                                       | f <sub>ADC</sub> = f <sub>HSI14</sub> = 14 MHz        | 0.179                                                                      | -   | 0.250                                             | μs                         |

| Jitter <sub>ADC</sub>                  | ADC jitter on trigger conversion      | f <sub>ADC</sub> = f <sub>HSI14</sub>                 | -                                                                          | 1   | -                                                 | 1/f <sub>HSI14</sub>       |

| ts <sup>(2)</sup>                      | Sampling time                         | f <sub>ADC</sub> = 14 MHz                             | 0.107                                                                      | -   | 17.1                                              | μs                         |

| 0                                      |                                       | -                                                     | 1.5                                                                        | -   | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> <sup>(2)</sup>       | Stabilization time                    | -                                                     | 14                                                                         |     | 1/f <sub>ADC</sub>                                |                            |

| t <sub>CONV</sub> <sup>(2)</sup>       | Total conversion time                 | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | 1                                                                          | -   | 18                                                | μs                         |

| <sup>I</sup> CONV <sup>(-)</sup>       | (including sampling time)             | 12-bit resolution                                     | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     |                                                   | 1/f <sub>ADC</sub>         |

Table 57. ADC characteristics (continued)

1. During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu$ A on I<sub>DDA</sub> and 60  $\mu$ A on I<sub>DD</sub> should be taken into account.

2. Guaranteed by design, not tested in production.

3. Specified value includes only ADC timing. It does not include the latency of the register access.

4. This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

| Symbol           | Parameter             | Conditio                                 | Min <sup>(1)</sup>    | Тур | Max <sup>(1)</sup> | Unit |    |

|------------------|-----------------------|------------------------------------------|-----------------------|-----|--------------------|------|----|

|                  |                       | No hysteresis<br>(COMPxHYST[1:0]=00)     | -                     | -   | 0                  | -    |    |

|                  |                       |                                          | High speed mode       | 3   |                    | 13   |    |

|                  |                       | Low hysteresis<br>(COMPxHYST[1:0]=01)    | All other power modes | 5   | 8                  | 10   |    |

| V <sub>hys</sub> | Comparator hysteresis | Madium hystorasia                        | High speed mode       | 7   |                    | 26   | mV |

|                  |                       | Medium hysteresis<br>(COMPxHYST[1:0]=10) | All other power modes | 9   | 15                 | 19   |    |

|                  |                       | High bystorosis                          | High speed mode       | 18  |                    | 49   |    |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | All other power modes | 19  | 31                 | 40   |    |

| Table 61. Comparator | characteristics | (continued) |

|----------------------|-----------------|-------------|

|----------------------|-----------------|-------------|

1. Data based on characterization results, not tested in production.

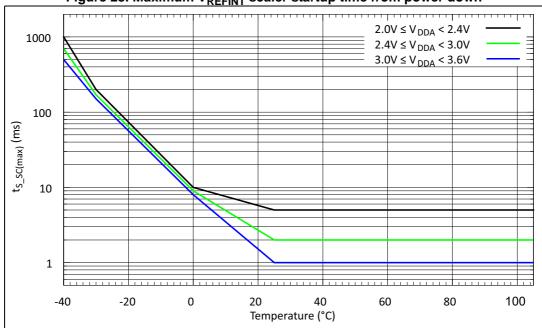

2. For more details and conditions see Figure 28: Maximum  $V_{REFINT}$  scaler startup time from power down.

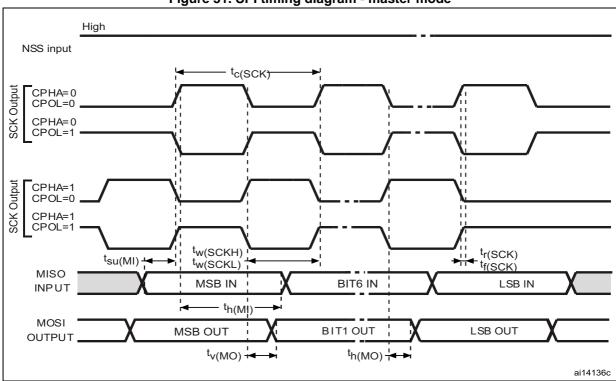

Figure 31. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

| Table | 69. | l <sup>2</sup> S | characteristics <sup>(1)</sup> |

|-------|-----|------------------|--------------------------------|

|-------|-----|------------------|--------------------------------|

| Symbol               | Parameter                                     | Conditions                                               | Min   | Мах   | Unit |  |

|----------------------|-----------------------------------------------|----------------------------------------------------------|-------|-------|------|--|

| f <sub>CK</sub>      | I <sup>2</sup> S clock frequency              | Master mode (data: 16 bits, Audio<br>frequency = 48 kHz) | 1.597 | 1.601 | MHz  |  |

| 1/t <sub>c(CK)</sub> |                                               | Slave mode                                               | 0     | 6.5   |      |  |

| t <sub>r(CK)</sub>   | I <sup>2</sup> S clock rise time              | Conscitive load C = 15 pE                                | -     | 10    |      |  |

| t <sub>f(CK)</sub>   | I <sup>2</sup> S clock fall time              | Capacitive load C <sub>L</sub> = 15 pF                   | -     | 12    |      |  |

| t <sub>w(CKH)</sub>  | I <sup>2</sup> S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio                 | 306   | -     |      |  |

| t <sub>w(CKL)</sub>  | I <sup>2</sup> S clock low time               | frequency = 48 kHz                                       | 312   | -     | ns   |  |

| t <sub>v(WS)</sub>   | WS valid time                                 | Master mode                                              | 2     | -     | 115  |  |

| t <sub>h(WS)</sub>   | WS hold time                                  | Master mode                                              | 2     | -     |      |  |

| t <sub>su(WS)</sub>  | WS setup time                                 | Slave mode                                               | 7     | -     |      |  |

| t <sub>h(WS)</sub>   | WS hold time                                  | Slave mode                                               | 0     | -     |      |  |

| DuCy(SCK)            | I <sup>2</sup> S slave input clock duty cycle | Slave mode                                               | 25    | 75    | %    |  |

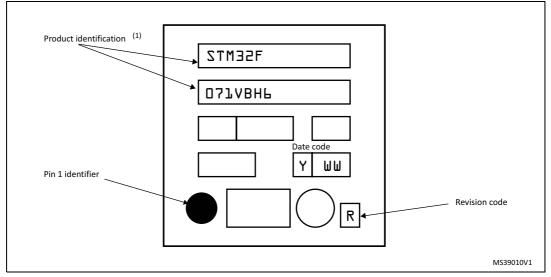

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 36. UFBGA100 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

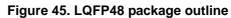

# 7.5 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

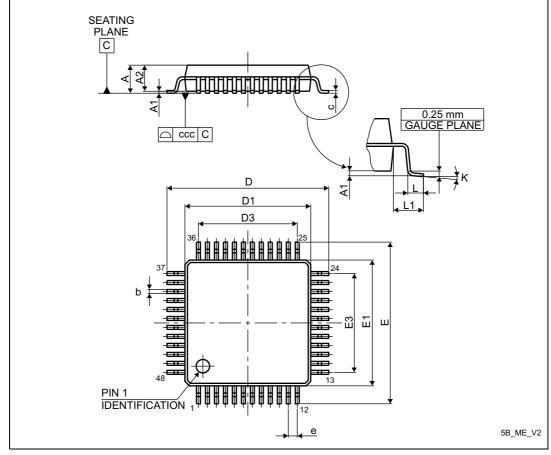

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 50. UFQFPN48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.