Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f071rbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.                | Block diagram                                                       | . 12  |

|--------------------------|---------------------------------------------------------------------|-------|

| Figure 2.                | Clock tree                                                          | . 16  |

| Figure 3.                | UFBGA100 package pinout                                             | . 28  |

| Figure 4.                | LQFP100 package pinout                                              | . 29  |

| Figure 5.                | LQFP64 package pinout                                               | 30    |

| Figure 6.                | LQFP48 package pinout                                               |       |

| Figure 7.                | UFQFPN48 package pinout                                             |       |

| Figure 8.                | WLCSP49 package pinout                                              |       |

| Figure 9.                | STM32F071xB memory map                                              |       |

| Figure 10.               | Pin loading conditions.                                             |       |

| Figure 11.               | Pin input voltage                                                   |       |

| Figure 12.               | Power supply scheme                                                 |       |

| Figure 13.               | Current consumption measurement scheme                              |       |

| Figure 14.               | High-speed external clock source AC timing diagram                  |       |

| Figure 15.               | Low-speed external clock source AC timing diagram                   |       |

| Figure 16.               | Typical application with an 8 MHz crystal                           |       |

| Figure 17.               | Typical application with a 32.768 kHz crystal                       |       |

| Figure 18.               | HSI oscillator accuracy characterization results for soldered parts |       |

| Figure 19.               | HSI14 oscillator accuracy characterization results                  |       |

| Figure 20.               | HSI48 oscillator accuracy characterization results                  |       |

| Figure 21.               | TC and TTa I/O input characteristics                                |       |

| Figure 22.               | Five volt tolerant (FT and FTf) I/O input characteristics           |       |

| Figure 23.               | I/O AC characteristics definition                                   |       |

| Figure 24.               | Recommended NRST pin protection                                     |       |

| Figure 25.               | ADC accuracy characteristics.                                       |       |

| Figure 26.               | Typical connection diagram using the ADC                            |       |

| Figure 27.               | 12-bit buffered / non-buffered DAC.                                 |       |

| Figure 28.               | Maximum $V_{REFINT}$ scaler startup time from power down            |       |

| Figure 29.               | SPI timing diagram - slave mode and CPHA = 0                        |       |

| Figure 30.               | SPI timing diagram - slave mode and CPHA = 1                        |       |

| Figure 31.               | SPI timing diagram - master mode                                    |       |

| Figure 32.               | I <sup>2</sup> S slave timing diagram (Philips protocol)            |       |

| Figure 33.               | I <sup>2</sup> S master timing diagram (Philips protocol).          |       |

| Figure 34.               | UFBGA100 package outline                                            |       |

| Figure 35.               | Recommended footprint for UFBGA100 package                          |       |

| Figure 36.               | UFBGA100 package marking example                                    |       |

| Figure 37.               | LQFP100 package outline                                             |       |

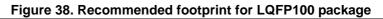

| Figure 38.               | Recommended footprint for LQFP100 package                           | 100   |

| Figure 39.               | LQFP100 package marking example                                     |       |

| Figure 39.               | LQFP 100 package marking example                                    |       |

| Figure 40.               | Recommended footprint for LQFP64 package                            |       |

| Figure 41.<br>Figure 42. | LQFP64 package marking example                                      |       |

|                          |                                                                     |       |

| Figure 43.               | WLCSP49 package outline                                             |       |

| Figure 44.               | WLCSP49 package marking example                                     |       |

| Figure 45.               | LQFP48 package outline                                              |       |

| Figure 46.               | Recommended footprint for LQFP48 package                            |       |

| Figure 47.               | LQFP48 package marking example                                      |       |

| Figure 48.               | UFQFPN48 package outline                                            | . TTZ |

# 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.5 **Power management**

#### 3.5.1 Power supply schemes

- V<sub>DD</sub> = V<sub>DDIO1</sub> = 2.0 to 3.6 V: external power supply for I/Os (V<sub>DDIO1</sub>) and the internal regulator. It is provided externally through VDD pins.

- V<sub>DDA</sub> = from V<sub>DD</sub> to 3.6 V: external analog power supply for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC are used). It is provided externally through VDDA pin. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be established first.

- V<sub>DDIO2</sub> = 1.65 to 3.6 V: external power supply for marked I/Os. V<sub>DDIO2</sub> is provided externally through the VDDIO2 pin. The V<sub>DDIO2</sub> voltage level is completely independent from V<sub>DD</sub> or V<sub>DDA</sub>, but it must not be provided without a valid supply on V<sub>DD</sub>. The V<sub>DDIO2</sub> supply is monitored and compared with the internal reference voltage (V<sub>REFINT</sub>). When the V<sub>DDIO2</sub> is below this threshold, all the I/Os supplied from this rail are disabled by hardware. The output of this comparator is connected to EXTI line 31 and it can be used to generate an interrupt. Refer to the pinout diagrams or tables for concerned I/Os list.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 12: Power supply scheme*.

## 3.5.2 Power supply supervisors

The device has integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold,  $V_{\text{POR/PDR}}$ , without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$

## 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

### 3.14.2 General-purpose timers (TIM2, 3, 14, 15, 16, 17)

There are six synchronizable general-purpose timers embedded in the STM32F071x8/xB devices (see *Table 7* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

#### TIM2, TIM3

STM32F071x8/xB devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### TIM14

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### TIM15, TIM16 and TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

| Na        | me                                                                                               | Abbreviation Definition                                                                           |                                                                  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| Pin r     | specified in brackets below the pin name, the pin function during and ame as the actual pin name |                                                                                                   |                                                                  |  |  |  |  |  |

|           |                                                                                                  | S                                                                                                 | Supply pin                                                       |  |  |  |  |  |

| Pin       | type                                                                                             | I                                                                                                 | Input-only pin                                                   |  |  |  |  |  |

|           |                                                                                                  | I/O                                                                                               | Input / output pin                                               |  |  |  |  |  |

|           |                                                                                                  | FT                                                                                                | 5 V-tolerant I/O                                                 |  |  |  |  |  |

|           |                                                                                                  | FTf                                                                                               | FTf 5 V-tolerant I/O, FM+ capable                                |  |  |  |  |  |

| I/O otr   | ucture                                                                                           | TTa                                                                                               | TTa 3.3 V-tolerant I/O directly connected to ADC                 |  |  |  |  |  |

| 1/O Sti   | ucture                                                                                           | TC                                                                                                | Standard 3.3 V I/O                                               |  |  |  |  |  |

|           |                                                                                                  | В                                                                                                 | Dedicated BOOT0 pin                                              |  |  |  |  |  |

|           |                                                                                                  | RST                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor      |  |  |  |  |  |

| Notes     |                                                                                                  | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset. |                                                                  |  |  |  |  |  |

| Pin       | Alternate<br>functions                                                                           | Functions selected                                                                                | Functions selected through GPIOx_AFR registers                   |  |  |  |  |  |

| functions | Additional functions                                                                             | Functions directly                                                                                | Functions directly selected/enabled through peripheral registers |  |  |  |  |  |

| Table 12 Legend/abbreviations used in the  | ningut tabla |

|--------------------------------------------|--------------|

| Table 12. Legend/abbreviations used in the | pinout table |

## Table 13. STM32F071x8/xB pin definitions

|          | Pin     | numb   | pers            |         |                                      |             |            |            | Pin functior         | IS                                         |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|------------|------------|----------------------|--------------------------------------------|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | type ts O/ |            | Alternate functions  | Additional<br>functions                    |

| B2       | 1       | -      | -               | -       | PE2                                  | I/O         | FT         | -          | TSC_G7_IO1, TIM3_ETR | -                                          |

| A1       | 2       | -      | -               | -       | PE3                                  | I/O         | FT         | -          | TSC_G7_IO2, TIM3_CH1 | -                                          |

| B1       | 3       | -      | -               | -       | PE4                                  | I/O         | FT         | -          | TSC_G7_IO3, TIM3_CH2 | -                                          |

| C2       | 4       | -      | -               | -       | PE5                                  | I/O         | FT         | -          | TSC_G7_IO4, TIM3_CH3 | -                                          |

| D2       | 5       | -      | -               | -       | PE6                                  | I/O         | FT         | -          | TIM3_CH4             | WKUP3,<br>RTC_TAMP3                        |

| E2       | 6       | 1      | 1               | B7      | VBAT                                 | S           | -          | -          | Backup power supply  |                                            |

| C1       | 7       | 2      | 2               | D5      | PC13                                 | I/O         | тс         | (1)<br>(2) | -                    | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |

| Pin name | AF0                 | AF1       | AF2        | AF3        | AF4        | AF5               |

|----------|---------------------|-----------|------------|------------|------------|-------------------|

| PB0      | EVENTOUT            | TIM3_CH3  | TIM1_CH2N  | TSC_G3_IO2 | USART3_CK  | -                 |

| PB1      | TIM14_CH1           | TIM3_CH4  | TIM1_CH3N  | TSC_G3_IO3 | USART3_RTS | -                 |

| PB2      | -                   | -         | -          | TSC_G3_IO4 | -          | -                 |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT  | TIM2_CH2   | TSC_G5_IO1 | -          | -                 |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1  | EVENTOUT   | TSC_G5_IO2 | -          | TIM17_BKIN        |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2  | TIM16_BKIN | I2C1_SMBA  | -          | -                 |

| PB6      | USART1_TX           | I2C1_SCL  | TIM16_CH1N | TSC_G5_IO3 | -          | -                 |

| PB7      | USART1_RX           | I2C1_SDA  | TIM17_CH1N | TSC_G5_IO4 | USART4_CTS | -                 |

| PB8      | CEC                 | I2C1_SCL  | TIM16_CH1  | TSC_SYNC   |            | -                 |

| PB9      | IR_OUT              | I2C1_SDA  | TIM17_CH1  | EVENTOUT   |            | SPI2_NSS, I2S2_W  |

| PB10     | CEC                 | I2C2_SCL  | TIM2_CH3   | TSC_SYNC   | USART3_TX  | SPI2_SCK, I2S2_CI |

| PB11     | EVENTOUT            | I2C2_SDA  | TIM2_CH4   | TSC_G6_IO1 | USART3_RX  | -                 |

| PB12     | SPI2_NSS, I2S2_WS   | EVENTOUT  | TIM1_BKIN  | TSC_G6_IO2 | USART3_CK  | TIM15_BKIN        |

| PB13     | SPI2_SCK, I2S2_CK   | -         | TIM1_CH1N  | TSC_G6_IO3 | USART3_CTS | I2C2_SCL          |

| PB14     | SPI2_MISO, I2S2_MCK | TIM15_CH1 | TIM1_CH2N  | TSC_G6_IO4 | USART3_RTS | I2C2_SDA          |

| PB15     | SPI2_MOSI, I2S2_SD  | TIM15_CH2 | TIM1_CH3N  | TIM15_CH1N | -          | -                 |

\_ - -- -- -- -\_ - ----\_ . \_

40/122

5

# 5 Memory mapping

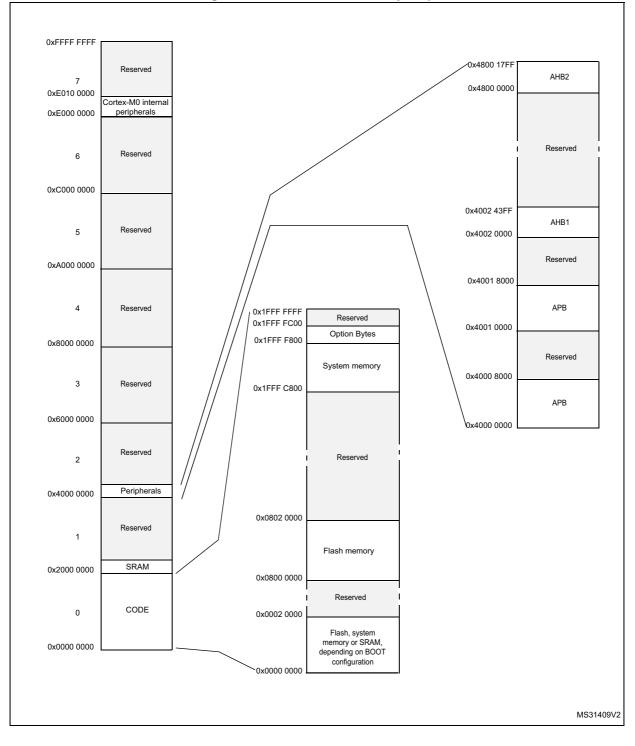

To the difference of STM32F071xB memory map in *Figure 9*, the two bottom code memory spaces of STM32F071x8 end at 0x0000 FFFF and 0x0800 FFFF, respectively.

Figure 9. STM32F071xB memory map

DocID025451 Rev 6

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

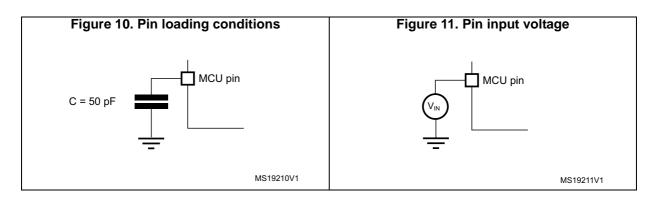

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

DocID025451 Rev 6

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 21: Voltage characteristics*, *Table 22: Current characteristics* and *Table 23: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                              | Ratings                                               | Min                               | Мах                     | Unit |

|-------------------------------------|-------------------------------------------------------|-----------------------------------|-------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>    | External main supply voltage                          | - 0.3                             | 4.0                     | V    |

| V <sub>DDIO2</sub> –V <sub>SS</sub> | External I/O supply voltage                           | - 0.3                             | 4.0                     | V    |

| $V_{DDA} - V_{SS}$                  | External analog supply voltage                        | - 0.3                             | 4.0                     | V    |

| V <sub>DD</sub> -V <sub>DDA</sub>   | Allowed voltage difference for $V_{DD} > V_{DDA}$     | -                                 | 0.4                     | V    |

| V <sub>BAT</sub> –V <sub>SS</sub>   | External backup supply voltage                        | - 0.3                             | 4.0                     | V    |

|                                     | Input voltage on FT and FTf pins                      | V <sub>SS</sub> - 0.3             | $V_{DDIOx} + 4.0^{(3)}$ | V    |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on TTa pins                             | V <sub>SS</sub> - 0.3             | 4.0                     | V    |

| VIN                                 | BOOT0                                                 | 0                                 | 9.0                     | V    |

|                                     | Input voltage on any other pin                        | V <sub>SS</sub> - 0.3             | 4.0                     | V    |

| ΔV <sub>DDx</sub>                   | Variations between different $V_{DD}$ power pins      | -                                 | 50                      | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub>  | Variations between all the different ground pins      | -                                 | 50                      | mV   |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage<br>(human body model) | see Section 6.3 sensitivity chara |                         | -    |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 22: Current characteristics* for the maximum allowed injected current values.

3. Valid only if the internal pull-up/pull-down resistors are disabled. If internal pull-up or pull-down resistor is enabled, the maximum limit is 4 V.

| Table 27. Programmable voltage detector characteristics (continued) |                         |              |      |      |                     |      |  |  |  |

|---------------------------------------------------------------------|-------------------------|--------------|------|------|---------------------|------|--|--|--|

| Symbol                                                              | Parameter               | Conditions   | Min  | Тур  | Max                 | Unit |  |  |  |

| V                                                                   | PVD threshold 6         | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |  |  |  |

| V <sub>PVD6</sub>                                                   |                         | Falling edge | 2.56 | 2.68 | 2.8                 | V    |  |  |  |

| V                                                                   | PVD threshold 7         | Rising edge  | 2.76 | 2.88 | 3                   | V    |  |  |  |

| V <sub>PVD7</sub>                                                   |                         | Falling edge | 2.66 | 2.78 | 2.9                 | V    |  |  |  |

| V <sub>PVDhyst</sub> <sup>(1)</sup>                                 | PVD hysteresis          | -            | -    | 100  | -                   | mV   |  |  |  |

| I <sub>DD(PVD)</sub>                                                | PVD current consumption | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μA   |  |  |  |

Table 27. Programmable voltage detector characteristics (continued)

1. Guaranteed by design, not tested in production.

#### 6.3.4 Embedded reference voltage

The parameters given in *Table 28* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                 | Parameter                                                           | Parameter Conditions              |                      | Тур  | Max                | Unit   |  |  |

|------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|--|--|

| V <sub>REFINT</sub>    | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |  |  |

| t <sub>START</sub>     | ADC_IN17 buffer startup time                                        | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |  |  |

| t <sub>S_vrefint</sub> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |  |  |

| $\Delta V_{REFINT}$    | Internal reference voltage<br>spread over the<br>temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |  |  |

| T <sub>Coeff</sub>     | Temperature coefficient                                             | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |  |  |

Table 28. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

|                 |                                                     |                       |                   | Α    | ll periphe          | erals ena            | bled                | All peripherals disabled |                     |                     |                     |      |

|-----------------|-----------------------------------------------------|-----------------------|-------------------|------|---------------------|----------------------|---------------------|--------------------------|---------------------|---------------------|---------------------|------|

| Symbol          | Parameter                                           | Conditions            | f <sub>HCLK</sub> |      | M                   | lax @ T <sub>A</sub> | (1)                 |                          | М                   | ax @ T <sub>A</sub> | (1)                 | Unit |

| Sy              | Para                                                |                       |                   | Тур  | 25 °C               | 85 °C                | 105 °C              | Тур                      | 25 °C               | 85 °C               | 105 °C              |      |

|                 |                                                     | HSI48                 | 48 MHz            | 23.1 | 25.4                | 25.8                 | 26.6                | 12.8                     | 13.5                | 13.7                | 13.9                |      |

|                 |                                                     |                       | 48 MHz            | 23.0 | 25.3 <sup>(2)</sup> | 25.7                 | 26.5 <sup>(2)</sup> | 12.6                     | 13.3 <sup>(2)</sup> | 13.5                | 13.8 <sup>(2)</sup> |      |

|                 | ode,<br>AM                                          | HSE bypass,<br>PLL on | 32 MHz            | 15.4 | 17.3                | 17.8                 | 18.3                | 7.96                     | 8.92                | 9.17                | 9.73                |      |

|                 | Supply current in Run mode, code executing from RAM |                       | 24 MHz            | 11.4 | 12.9                | 13.5                 | 13.7                | 6.48                     | 8.04                | 8.23                | 8.41                |      |

|                 | n Ru<br>g fro                                       | HSE bypass,           | 8 MHz             | 4.21 | 4.6                 | 4.89                 | 5.25                | 2.07                     | 2.3                 | 2.35                | 2.94                |      |

|                 | ent i<br>utinç                                      | PLL off               | 1 MHz             | 0.78 | 0.9                 | 0.92                 | 1.15                | 0.36                     | 0.48                | 0.59                | 0.82                |      |

|                 | curr<br>exec                                        |                       | 48 MHz            | 23.1 | 24.5                | 25.0                 | 25.2                | 12.6                     | 13.7                | 13.9                | 14.0                |      |

|                 | pply<br>ode                                         | HSI clock,<br>PLL on  | 32 MHz            | 15.4 | 17.4                | 17.7                 | 18.2                | 8.05                     | 8.85                | 9.16                | 9.94                |      |

|                 | Su                                                  |                       | 24 MHz            | 11.5 | 13.0                | 13.6                 | 13.9                | 6.49                     | 8.06                | 8.21                | 8.47                |      |

|                 |                                                     | HSI clock,<br>PLL off | 8 MHz             | 4.34 | 4.75                | 5.03                 | 5.41                | 2.11                     | 2.36                | 2.38                | 2.98                | mA   |

| I <sub>DD</sub> |                                                     | HSI48                 | 48 MHz            | 15.1 | 16.6                | 16.8                 | 17.5                | 3.08                     | 3.43                | 3.56                | 3.61                | IIIA |

|                 | 0                                                   |                       | 48 MHz            | 15.0 | 16.5 <sup>(2)</sup> | 16.7                 | 17.3 <sup>(2)</sup> | 2.93                     | 3.28 <sup>(2)</sup> | 3.41                | 3.46 <sup>(2)</sup> |      |

|                 | pode                                                | HSE bypass,<br>PLL on | 32 MHz            | 9.9  | 11.4                | 11.6                 | 11.9                | 2.0                      | 2.24                | 2.32                | 2.49                |      |

|                 | sep r                                               |                       | 24 MHz            | 7.43 | 8.17                | 8.71                 | 8.82                | 1.63                     | 1.82                | 1.88                | 1.9                 |      |

|                 | 1 Sle                                               | HSE bypass,           | 8 MHz             | 2.83 | 3.09                | 3.26                 | 3.66                | 0.76                     | 0.88                | 0.91                | 0.93                |      |

|                 | Supply current in Sleep mode                        | PLL off               | 1 MHz             | 0.42 | 0.54                | 0.55                 | 0.67                | 0.28                     | 0.39                | 0.41                | 0.43                |      |

|                 |                                                     |                       | 48 MHz            | 15.0 | 17.2                | 17.3                 | 17.9                | 3.04                     | 3.37                | 3.41                | 3.46                |      |

|                 |                                                     | HSI clock,<br>PLL on  | 32 MHz            | 9.93 | 11.3                | 11.6                 | 11.7                | 2.11                     | 2.35                | 2.44                | 2.65                |      |

|                 | Sup                                                 |                       | 24 MHz            | 7.53 | 8.45                | 8.87                 | 8.95                | 1.64                     | 1.83                | 1.9                 | 1.93                |      |

|                 |                                                     | HSI clock,<br>PLL off | 8 MHz             | 2.95 | 3.24                | 3.41                 | 3.8                 | 0.8                      | 0.92                | 0.94                | 0.97                |      |

| Table 29. Typical and maximum | current consumption from V <sub>DD</sub> | <sub>D</sub> supply at V <sub>DD</sub> = 3.6 V (continued) |

|-------------------------------|------------------------------------------|------------------------------------------------------------|

|                               |                                          |                                                            |

1. Data based on characterization results, not tested in production unless otherwise specified.

2. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

|                  |                   |                                |                   |                                                       |                    | = 2.4 V | -                  |                  |                    | = 3.6 \ |                    |    |

|------------------|-------------------|--------------------------------|-------------------|-------------------------------------------------------|--------------------|---------|--------------------|------------------|--------------------|---------|--------------------|----|

| Symbol           | Para-<br>meter    | Conditions<br>(1)              | f <sub>HCLK</sub> | f <sub>HCLK</sub> Max @ T <sub>A</sub> <sup>(2)</sup> |                    | Tura    | M                  | A <sup>(2)</sup> | Unit               |         |                    |    |

|                  |                   |                                |                   | Тур                                                   | 25 °C              | 85 °C   | 105 °C             | Тур              | 25 °C              | 85 °C   | 105 °C             |    |

|                  |                   | HSI48                          | 48 MHz            | 311                                                   | 326                | 334     | 343                | 322              | 337                | 345     | 354                |    |

|                  |                   | Supply<br>current in<br>Run or | 48 MHz            | 152                                                   | 170 <sup>(3)</sup> | 178     | 182 <sup>(3)</sup> | 165              | 184 <sup>(3)</sup> | 196     | 200 <sup>(3)</sup> |    |

|                  |                   |                                | 32 MHz            | 105                                                   | 121                | 126     | 128                | 113              | 129                | 136     | 138                |    |

|                  | Run or            |                                | 24 MHz            | 81.9                                                  | 95.9               | 99.5    | 101                | 88.7             | 102                | 107     | 108                |    |

|                  | Sleep<br>mode,    | HSE                            | 8 MHz             | 2.7                                                   | 3.8                | 4.3     | 4.6                | 3.6              | 4.7                | 5.2     | 5.5                |    |

| I <sub>DDA</sub> | code<br>executing | ode bypass,                    | 1 MHz             | 2.7                                                   | 3.8                | 4.3     | 4.6                | 3.6              | 4.7                | 5.2     | 5.5                | μA |

|                  | from              |                                | 48 MHz            | 223                                                   | 244                | 255     | 260                | 245              | 265                | 279     | 284                |    |

|                  | Flash<br>memory   | HSI clock,<br>PLL on           | 32 MHz            | 176                                                   | 195                | 203     | 206                | 193              | 212                | 221     | 224                |    |

| or RAM           | or RAM            |                                | 24 MHz            | 154                                                   | 171                | 178     | 181                | 168              | 185                | 192     | 195                |    |

|                  |                   | HSI clock,<br>PLL off          | 8 MHz             | 74.2                                                  | 83.4               | 86.4    | 87.3               | 83.4             | 92.5               | 95.3    | 96.6               |    |

Table 30. Typical and maximum current consumption from the  $\mathrm{V}_{\mathrm{DDA}}$  supply

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

3. Data based on characterization results and tested in production (using one common test limit for sum of I<sub>DD</sub> and I<sub>DDA</sub>).

| C. m             | Para-                                                   |                                |                                                              |                         | Тур ( | @V <sub>DD</sub> ( | V <sub>DD</sub> = V | / <sub>DDA</sub> ) | -     |                           | Max <sup>(1)</sup>        |                            |                    |  |

|------------------|---------------------------------------------------------|--------------------------------|--------------------------------------------------------------|-------------------------|-------|--------------------|---------------------|--------------------|-------|---------------------------|---------------------------|----------------------------|--------------------|--|

| Sym-<br>bol      |                                                         |                                | Conditions                                                   |                         | 2.4 V | 2.7 V              | 3.0 V               | 3.3 V              | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit               |  |

|                  | Supply current in                                       |                                | julator in run<br>de, all<br>illators OFF                    | 15.4                    | 15.5  | 15.6               | 15.7                | 15.8               | 15.9  | 23 <sup>(2)</sup>         | 49                        | 68 <sup>(2)</sup>          |                    |  |

| I <sub>DD</sub>  | Stop<br>mode                                            | pow                            | ulator in low-<br>ver mode, all<br>illators OFF              | 3.2                     | 3.3   | 3.4                | 3.5                 | 3.6                | 3.7   | 8 <sup>(2)</sup>          | 33                        | 51 <sup>(2)</sup>          |                    |  |

|                  | Supply current in                                       | LSI<br>ON                      | ON and IWDG                                                  | 0.8                     | 1.0   | 1.1                | 1.2                 | 1.3                | 1.4   | -                         | -                         | -                          |                    |  |

|                  | Standby<br>mode                                         | LSI<br>OFF                     | OFF and IWDG                                                 | 0.6                     | 0.7   | 0.9                | 0.9                 | 1.0                | 1.1   | 2.1 <sup>(2)</sup>        | 2.6                       | 3.1 <sup>(2)</sup>         |                    |  |

|                  | Stop<br>mode<br>Supply<br>current in<br>Standby<br>mode | NO                             | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 2.1                     | 2.2   | 2.3                | 2.5                 | 2.6                | 2.8   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>         |                    |  |

|                  |                                                         | V <sub>DDA</sub> monitoring O  | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 2.1                     | 2.2   | 2.3                | 2.5                 | 2.6                | 2.8   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>         | μΑ                 |  |

|                  |                                                         | current in<br>Standby<br>mode  | V <sub>DC</sub>                                              | LSI ON and<br>IWDG ON   | 2.5   | 2.7                | 2.8                 | 3.0                | 3.2   | 3.5                       | -                         | -                          | -                  |  |

| I                |                                                         |                                |                                                              | LSI OFF and<br>IWDG OFF | 1.9   | 2.1                | 2.2                 | 2.3                | 2.5   | 2.6                       | 3.5 <sup>(2)</sup>        | 3.6                        | 4.6 <sup>(2)</sup> |  |

| I <sub>DDA</sub> | Supply                                                  | OFF                            | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 1.3                     | 1.3   | 1.4                | 1.4                 | 1.5                | 1.5   | -                         | -                         | -                          |                    |  |

|                  | current in<br>Stop<br>mode                              | V <sub>DDA</sub> monitoring Of | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.3                     | 1.3   | 1.4                | 1.4                 | 1.5                | 1.5   | -                         | -                         | -                          |                    |  |

|                  | Supply current in                                       | V <sub>DD</sub>                | LSI ON and<br>IWDG ON                                        | 1.7                     | 1.8   | 1.9                | 2.0                 | 2.1                | 2.2   | -                         | -                         | -                          |                    |  |

|                  | Standby<br>mode                                         |                                | LSI OFF and<br>IWDG OFF                                      | 1.2                     | 1.2   | 1.2                | 1.3                 | 1.3                | 1.4   | -                         | -                         | -                          |                    |  |

Table 31. Typical and maximum consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

2. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

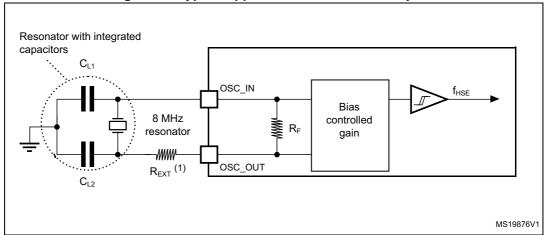

Figure 16. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Parameter Conditions <sup>(1)</sup>    |    | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|----------------------------------------|----|-----|--------------------|------|

|                                     |                         | low drive capability                   | -  | 0.5 | 0.9                |      |

|                                     | LSE current consumption | medium-low drive capability            | -  | -   | 1                  |      |

| I <sub>DD</sub>                     |                         | medium-high drive capability           | -  | -   | 1.3                | μA   |

|                                     | high drive capability   | high drive capability                  | -  | -   | 1.6                |      |

|                                     |                         | low drive capability                   | 5  | -   | -                  |      |

|                                     | Oscillator              | Oscillator medium-low drive capability |    | -   | -                  | µA/V |

| 9 <sub>m</sub>                      | transconductance        | medium-high drive capability           | 15 | -   | -                  | μΑνν |

|                                     |                         | high drive capability                  | 25 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DDIOx</sub> is stabilized       | -  | 2   | -                  | S    |

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

## High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                        | Conditions                    | Min                 | Тур | Мах                | Unit |

|-----------------------|----------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                        | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step           | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                       | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

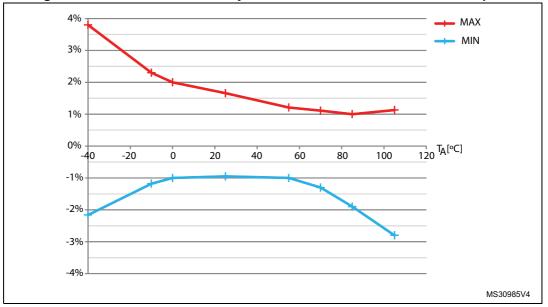

|                       |                                  | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       | Accuracy of the HSI oscillator   | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> |      |

|                       |                                  | $T_A = 0$ to $85^{\circ}C$    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | %    |

| ACC <sub>HSI</sub>    |                                  | $T_A = 0$ to $70^{\circ}C$    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | 70   |

|                       |                                  | $T_A = 0$ to 55°C             | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time      | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption | -                             | -                   | 80  | 100 <sup>(2)</sup> | μA   |

#### Table 41. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105°C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

4. Factory calibrated, parts not soldered.

#### Figure 18. HSI oscillator accuracy characterization results for soldered parts

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

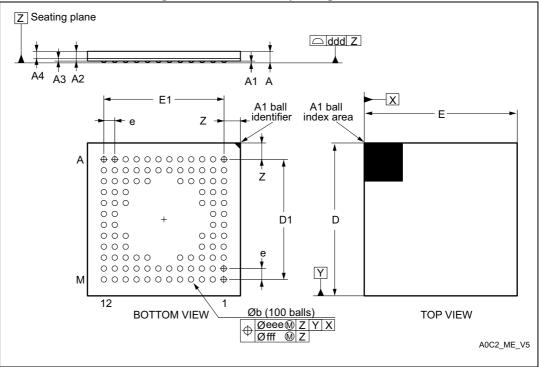

# 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 34. UFBGA100 package outline

1. Drawing is not to scale.

| Symbol |      | millimeters |       |      | inches <sup>(1)</sup> |        |

|--------|------|-------------|-------|------|-----------------------|--------|

| Symbol | Min. | Typ. Max.   |       | Min. | Тур.                  | Max.   |

| А      | -    | -           | 0.600 | -    | -                     | 0.0236 |

| A1     | -    | -           | 0.110 | -    | -                     | 0.0043 |

| A2     | -    | 0.450       | -     | -    | 0.0177                | -      |

| A3     | -    | 0.130       | -     | -    | 0.0051                | 0.0094 |

| A4     | -    | 0.320       | -     | -    | 0.0126                | -      |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |  |  |  |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|--|--|--|--|

| Symbol | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |  |  |  |  |

| b      | 0.240       | 0.290 | 0.340 | 0.0094                | 0.0114 | 0.0134 |  |  |  |  |  |

| D      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |  |  |  |  |  |

| D1     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |  |  |  |  |

| Е      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |  |  |  |  |  |

| E1     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |  |  |  |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |  |  |  |  |

| Z      | -           | 0.750 | -     | -                     | 0.0295 | -      |  |  |  |  |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |  |  |  |  |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |  |  |  |  |  |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |  |  |  |  |  |

Table 70. UFBGA100 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

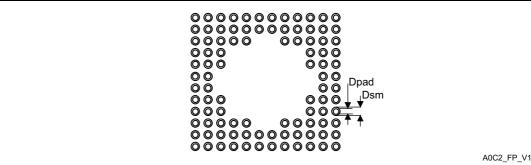

#### Table 71. UFBGA100 recommended PCB design rules

| Dimension         | Recommended values                                                |

|-------------------|-------------------------------------------------------------------|

| Pitch             | 0.5                                                               |

| Dpad              | 0.280 mm                                                          |

| Dsm               | 0.370 mm typ. (depends on the solder mask registration tolerance) |

| Stencil opening   | 0.280 mm                                                          |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                     |

| 0 mm h a l |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|------------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol     | Min    | Тур         | Мах    | Min    | Тур                   | Max    |

| E1         | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| E3         | -      | 12.000      | -      | -      | 0.4724                | -      |

| е          | -      | 0.500       | -      | -      | 0.0197                | -      |

| L          | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1         | -      | 1.000       | -      | -      | 0.0394                | -      |

| k          | 0.0°   | 3.5°        | 7.0°   | 0.0°   | 3.5°                  | 7.0°   |

| CCC        | -      | -           | 0.080  | -      | -                     | 0.0031 |

Table 72. LQPF100 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

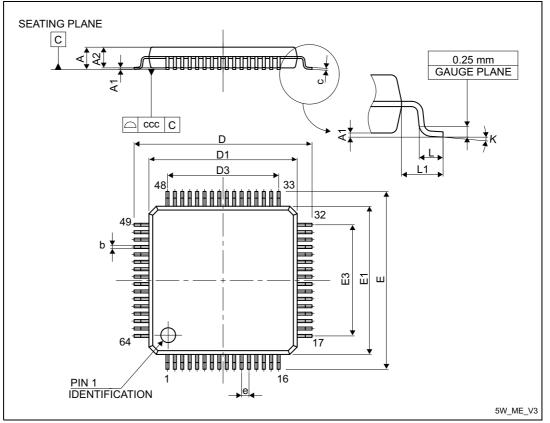

# 7.3 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 40. LQFP64 package outline

1. Drawing is not to scale.

| Table 73. LQFP64 | 4 package mechanical data | i |

|------------------|---------------------------|---|

|------------------|---------------------------|---|

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Max   | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

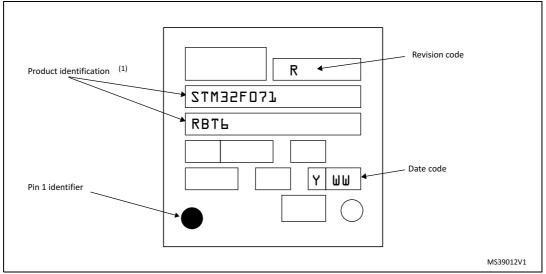

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

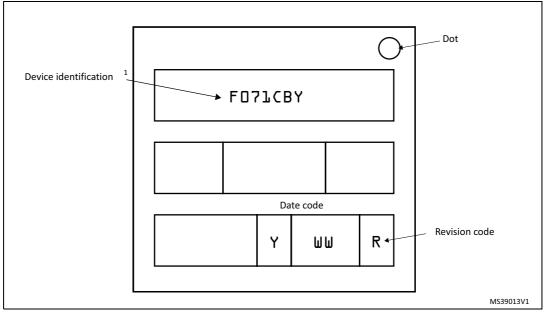

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 44. WLCSP49 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.