Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 87                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f071vbh6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                                |         |

|-----------|-----------------------------------------------------------------------------------------------|---------|

| Table 2.  | STM32F071x8/xB family device features and peripheral counts                                   | 11      |

| Table 3.  | Temperature sensor calibration values                                                         | 18      |

| Table 4.  | Internal voltage reference calibration values                                                 |         |

| Table 5.  | Capacitive sensing GPIOs available on STM32F071x8/xB devices                                  | 20      |

| Table 6.  | Number of capacitive sensing channels available                                               |         |

|           | on STM32F071x8/xB devices                                                                     | 21      |

| Table 7.  | Timer feature comparison.                                                                     |         |

| Table 8.  | Comparison of I <sup>2</sup> C analog and digital filters                                     | 24      |

| Table 9.  | STM32F071x8/xB I <sup>2</sup> C implementation                                                | 25      |

| Table 10. | STM32F071x8/xB USART implementation                                                           | 25      |

| Table 11. | STM32F071x8/xB SPI/I <sup>2</sup> S implementation                                            | 26      |

| Table 12. | Legend/abbreviations used in the pinout table                                                 | 32      |

| Table 13. | STM32F071x8/xB pin definitions                                                                | 32      |

| Table 14. | Alternate functions selected through GPIOA_AFR registers for port A                           | 39      |

| Table 15. | Alternate functions selected through GPIOB_AFR registers for port B                           | 40      |

| Table 16. | Alternate functions selected through GPIOC_AFR registers for port C                           | 41      |

| Table 17. | Alternate functions selected through GPIOD_AFR registers for port D                           | 41      |

| Table 18. | Alternate functions selected through GPIOE_AFR registers for port E                           | 42      |

| Table 19. | Alternate functions available on port F                                                       | 42      |

| Table 20. | STM32F071x8/xB peripheral register boundary addresses                                         | 44      |

| Table 21. | Voltage characteristics                                                                       | 49      |

| Table 22. | Current characteristics                                                                       | 50      |

| Table 23. | Thermal characteristics.                                                                      | 50      |

| Table 24. | General operating conditions                                                                  | 51      |

| Table 25. | Operating conditions at power-up / power-down                                                 | 52      |

| Table 26. | Embedded reset and power control block characteristics.                                       | 52      |

| Table 27. | Programmable voltage detector characteristics                                                 | 52      |

| Table 28. | Embedded internal reference voltage                                                           | 53      |

| Table 29. | Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V              | 54      |

| Table 30. | Typical and maximum current consumption from the V <sub>DDA</sub> supply                      | 56      |

| Table 31. | Typical and maximum consumption in Stop and Standby modes                                     | 57      |

| Table 32. | Typical and maximum current consumption from the V <sub>BAT</sub> supply                      | 58      |

| Table 33. | Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal | 59      |

| Table 34. | Switching output I/O current consumption                                                      |         |

| Table 35. | Peripheral current consumption                                                                |         |

| Table 36. | Low-power mode wakeup timings                                                                 |         |

| Table 37. | High-speed external user clock characteristics.                                               |         |

| Table 38. | Low-speed external user clock characteristics                                                 |         |

| Table 39. | HSE oscillator characteristics                                                                |         |

| Table 40. | LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ )                             |         |

| Table 41. | HSI oscillator characteristics                                                                |         |

| Table 42. | HSI14 oscillator characteristics.                                                             |         |

| Table 43. | HSI48 oscillator characteristics.                                                             |         |

| Table 44. | LSI oscillator characteristics                                                                |         |

| Table 45. | PLL characteristics                                                                           |         |

| Table 46. | Flash memory characteristics                                                                  |         |

|           |                                                                                               | · · · - |

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- Periodic wakeup unit with programmable resolution and period.

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- Three anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

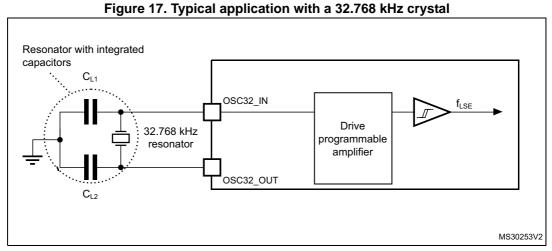

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s), Fast mode (up to 400 kbit/s) and Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive on most of the associated I/Os.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |  |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |  |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |  |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |  |

| Table 8. Comparison of I <sup>2</sup> C analog and digital filters | Table 8. Comparison of I | <sup>2</sup> C analog and digital filters |

|--------------------------------------------------------------------|--------------------------|-------------------------------------------|

|--------------------------------------------------------------------|--------------------------|-------------------------------------------|

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts

verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to *Table 9* for the differences between I2C1 and I2C2.

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | Х    | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive I/Os | Х    | Х    |

| Independent clock                                            | Х    | -    |

| SMBus                                                        | Х    | -    |

| Wakeup from STOP                                             | Х    | -    |

1. X = supported.

# 3.17 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds four universal synchronous/asynchronous receivers/transmitters (USART1, USART2, USART3, USART4) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 and USART2 support also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and have a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 and<br>USART2 | USART3 and<br>USART4 |

|---------------------------------------|----------------------|----------------------|

| Hardware flow control for modem       | Х                    | Х                    |

| Continuous communication using DMA    | X                    | х                    |

| Multiprocessor communication          | X                    | х                    |

| Synchronous mode                      | X                    | Х                    |

| Smartcard mode                        | Х                    | -                    |

| Single-wire half-duplex communication | X                    | Х                    |

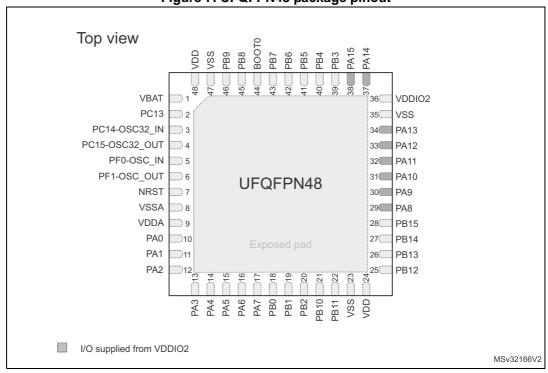

Figure 7. UFQFPN48 package pinout

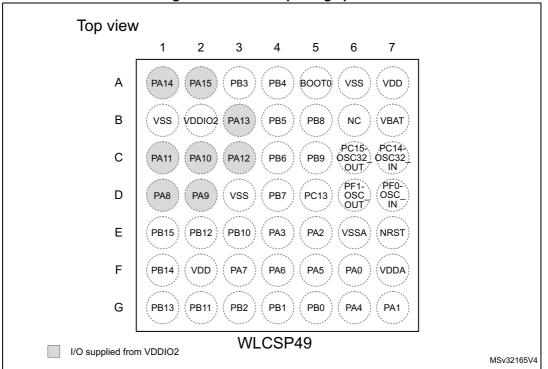

Figure 8. WLCSP49 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

|          | Pin     | numt   | pers            |         |                                      |             |               |            | Pin functior                                                               | IS                                                           |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|------------|----------------------------------------------------------------------------|--------------------------------------------------------------|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate functions                                                        | Additional<br>functions                                      |

| D1       | 8       | 3      | 3               | C7      | PC14-OSC32_IN<br>(PC14)              | I/O         | тс            | (1)<br>(2) | -                                                                          | OSC32_IN                                                     |

| E1       | 9       | 4      | 4               | C6      | PC15-<br>OSC32_OUT<br>(PC15)         | I/O         | тс            | (1)<br>(2) | -                                                                          | OSC32_OUT                                                    |

| F2       | 10      | -      | -               | -       | PF9                                  | I/O         | FT            | -          | TIM15_CH1                                                                  | -                                                            |

| G2       | 11      | -      | -               | -       | PF10                                 | I/O         | FT            | -          | TIM15_CH2                                                                  | -                                                            |

| F1       | 12      | 5      | 5               | D7      | PF0-OSC_IN<br>(PF0)                  | I/O         | FT            | -          | CRS_SYNC                                                                   | OSC_IN                                                       |

| G1       | 13      | 6      | 6               | D6      | PF1-OSC_OUT<br>(PF1)                 | I/O         | FT            | -          | -                                                                          | OSC_OUT                                                      |

| H2       | 14      | 7      | 7               | E7      | NRST                                 | I/O         | RST           | -          | Device reset input / internal reset output<br>(active low)                 |                                                              |

| H1       | 15      | 8      | -               | -       | PC0                                  | I/O         | TTa           | -          | EVENTOUT                                                                   | ADC_IN10                                                     |

| J2       | 16      | 9      | -               | -       | PC1                                  | I/O         | TTa           | -          | EVENTOUT                                                                   | ADC_IN11                                                     |

| J3       | 17      | 10     | -               | -       | PC2                                  | I/O         | ТТа           | -          | SPI2_MISO, I2S2_MCK,<br>EVENTOUT                                           | ADC_IN12                                                     |

| K2       | 18      | 11     | -               | -       | PC3                                  | I/O         | ТТа           | -          | SPI2_MOSI, I2S2_SD,<br>EVENTOUT                                            | ADC_IN13                                                     |

| J1       | 19      | -      | -               | -       | PF2                                  | I/O         | FT            | -          | EVENTOUT                                                                   | WKUP8                                                        |

| K1       | 20      | 12     | 8               | E6      | VSSA                                 | S           | -             | -          | Analog ground                                                              |                                                              |

| M1       | 21      | 13     | 9               | F7      | VDDA                                 | S           | -             | -          | Analog power supply                                                        |                                                              |

| L1       | 22      | -      | -               | -       | PF3                                  | I/O         | FT            | -          | EVENTOUT                                                                   |                                                              |

| L2       | 23      | 14     | 10              | F6      | PA0                                  | I/O         | ТТа           | -          | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX                   | RTC_TAMP2,<br>WKUP1,<br>COMP1_OUT,<br>ADC_IN0,<br>COMP1_INM6 |

| M2       | 24      | 15     | 11              | G7      | PA1                                  | I/O         | ТТа           | -          | USART2_RTS, TIM2_CH2,<br>TIM15_CH1N,<br>TSC_G1_IO2,<br>USART4_RX, EVENTOUT | ADC_IN1,<br>COMP1_INP                                        |

| Table 13. STM32F071x8/xB pin definitions (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

|          | Pin     | numb   | oers            |         | ble 13. STM32F0                      |             |               |       | Pin functions                                                                                                   |                                                    |  |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                                                             | Additional<br>functions                            |  |

| К3       | 25      | 16     | 12              | E5      | PA2                                  | I/O         | ТТа           | -     | USART2_TX, TIM2_CH3,<br>TIM15_CH1, TSC_G1_IO3                                                                   | ADC_IN2,<br>COMP2_OUT,<br>COMP2_INM6,<br>WKUP4     |  |

| L3       | 26      | 17     | 13              | E4      | PA3                                  | I/O         | ТТа           | -     | USART2_RX,TIM2_CH4,<br>TIM15_CH2, TSC_G1_IO4                                                                    | ADC_IN3,<br>COMP2_INP                              |  |

| D3       | 27      | 18     | -               | -       | VSS                                  | S           | -             | -     | Ground                                                                                                          |                                                    |  |

| H3       | 28      | 19     | -               | -       | VDD                                  | S           | -             | -     | Digital power su                                                                                                | ipply                                              |  |

| М3       | 29      | 20     | 14              | G6      | PA4                                  | I/O         | ТТа           | -     | SPI1_NSS, I2S1_WS,<br>TIM14_CH1, TSC_G2_IO1,<br>USART2_CK                                                       | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4,<br>DAC_OUT1 |  |

| K4       | 30      | 21     | 15              | F5      | PA5                                  | I/O         | ТТа           | -     | SPI1_SCK, I2S1_CK, CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2                                                          | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5,<br>DAC_OUT2 |  |

| L4       | 31      | 22     | 16              | F4      | PA6                                  | I/O         | ТТа           | -     | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TIM1_BKIN,<br>TIM16_CH1,<br>COMP1_OUT,<br>TSC_G2_IO3, EVENTOUT,<br>USART3_CTS | ADC_IN6                                            |  |

| M4       | 32      | 23     | 17              | F3      | PA7                                  | I/O         | ТТа           | _     | SPI1_MOSI, I2S1_SD,<br>TIM3_CH2, TIM14_CH1,<br>TIM1_CH1N, TIM17_CH1,<br>COMP2_OUT,<br>TSC_G2_IO4,<br>EVENTOUT   | ADC_IN7                                            |  |

| K5       | 33      | 24     | -               | -       | PC4                                  | I/O         | TTa           | -     | EVENTOUT, USART3_TX                                                                                             | ADC_IN14                                           |  |

| L5       | 34      | 25     | -               | -       | PC5                                  | I/O         | ТТа           | -     | TSC_G3_IO1,<br>USART3_RX                                                                                        | ADC_IN15,<br>WKUP5                                 |  |

| M5       | 35      | 26     | 18              | G5      | PB0                                  | I/O         | ТТа           | -     | TIM3_CH3, TIM1_CH2N,<br>TSC_G3_IO2, EVENTOUT,<br>USART3_CK                                                      | ADC_IN8                                            |  |

| M6       | 36      | 27     | 19              | G4      | PB1                                  | I/O         | ТТа           | -     | TIM3_CH4, USART3_RTS,<br>TIM14_CH1, TIM1_CH3N,<br>TSC_G3_IO3                                                    | ADC_IN9                                            |  |

| L6       | 37      | 28     | 20              | G3      | PB2                                  | I/O         | FT            |       | TSC_G3_IO4                                                                                                      | -                                                  |  |

| Table 13. STM32F071x8/xE | <b>B</b> pin definitions | (continued) |

|--------------------------|--------------------------|-------------|

|--------------------------|--------------------------|-------------|

|          | Pin     | numt   | oers            |         |                                      |             | _             |       | Pin function                                                                          | IS                      |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| M7       | 38      | -      | -               | -       | PE7                                  | I/O         | FT            | -     | TIM1_ETR                                                                              | -                       |

| L7       | 39      | -      | -               | -       | PE8                                  | I/O         | FT            | -     | TIM1_CH1N                                                                             | -                       |

| M8       | 40      | -      | -               | -       | PE9                                  | I/O         | FT            | -     | TIM1_CH1                                                                              | -                       |

| L8       | 41      | -      | -               | -       | PE10                                 | I/O         | FT            | -     | TIM1_CH2N                                                                             | -                       |

| M9       | 42      | -      | -               | -       | PE11                                 | I/O         | FT            | -     | TIM1_CH2                                                                              | -                       |

| L9       | 43      | -      | -               | -       | PE12                                 | I/O         | FT            | -     | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                                       | -                       |

| M10      | 44      | -      | -               | -       | PE13                                 | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                                        | -                       |

| M11      | 45      | -      | -               | -       | PE14                                 | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM1_CH4                                                      | -                       |

| M12      | 46      | -      | -               | -       | PE15                                 | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>TIM1_BKIN                                                      | -                       |

| L10      | 47      | 29     | 21              | E3      | PB10                                 | I/O         | FT            | -     | SPI2_SCK, I2C2_SCL,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3                          | -                       |

| L11      | 48      | 30     | 22              | G2      | PB11                                 | I/O         | FT            | -     | USART3_RX, TIM2_CH4,<br>EVENTOUT, TSC_G6_IO1,<br>I2C2_SDA                             | -                       |

| F12      | 49      | 31     | 23              | D3      | VSS                                  | S           | -             | -     | Ground                                                                                |                         |

| G12      | 50      | 32     | 24              | F2      | VDD                                  | S           | -             | I     | Digital power su                                                                      | ipply                   |

| L12      | 51      | 33     | 25              | E2      | PB12                                 | I/O         | FT            | -     | TIM1_BKIN, TIM15_BKIN,<br>SPI2_NSS, I2S2_WS,<br>USART3_CK,<br>TSC_G6_IO2,<br>EVENTOUT | -                       |

| K12      | 52      | 34     | 26              | G1      | PB13                                 | I/O         | FTf           | -     | SPI2_SCK, I2S2_CK,<br>I2C2_SCL, USART3_CTS,<br>TIM1_CH1N, TSC_G6_IO3                  | -                       |

| K11      | 53      | 35     | 27              | F1      | PB14                                 | I/O         | FTf           | -     | SPI2_MISO, I2S2_MCK,<br>I2C2_SDA, USART3_RTS,<br>TIM1_CH2N, TIM15_CH1,<br>TSC_G6_IO4  | -                       |

| Table 13. STM32F071x8/xB | pin definitions | (continued) |

|--------------------------|-----------------|-------------|

|                          | p               |             |

| Pin name | AF0                 | AF1       | AF2        | AF3        | AF4        | AF5               |

|----------|---------------------|-----------|------------|------------|------------|-------------------|

| PB0      | EVENTOUT            | TIM3_CH3  | TIM1_CH2N  | TSC_G3_IO2 | USART3_CK  | -                 |

| PB1      | TIM14_CH1           | TIM3_CH4  | TIM1_CH3N  | TSC_G3_IO3 | USART3_RTS | -                 |

| PB2      | -                   | -         | -          | TSC_G3_IO4 | -          | -                 |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT  | TIM2_CH2   | TSC_G5_IO1 | -          | -                 |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1  | EVENTOUT   | TSC_G5_IO2 | -          | TIM17_BKIN        |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2  | TIM16_BKIN | I2C1_SMBA  | -          | -                 |

| PB6      | USART1_TX           | I2C1_SCL  | TIM16_CH1N | TSC_G5_IO3 | -          | -                 |

| PB7      | USART1_RX           | I2C1_SDA  | TIM17_CH1N | TSC_G5_IO4 | USART4_CTS | -                 |

| PB8      | CEC                 | I2C1_SCL  | TIM16_CH1  | TSC_SYNC   |            | -                 |

| PB9      | IR_OUT              | I2C1_SDA  | TIM17_CH1  | EVENTOUT   |            | SPI2_NSS, I2S2_W  |

| PB10     | CEC                 | I2C2_SCL  | TIM2_CH3   | TSC_SYNC   | USART3_TX  | SPI2_SCK, I2S2_CI |

| PB11     | EVENTOUT            | I2C2_SDA  | TIM2_CH4   | TSC_G6_IO1 | USART3_RX  | -                 |

| PB12     | SPI2_NSS, I2S2_WS   | EVENTOUT  | TIM1_BKIN  | TSC_G6_IO2 | USART3_CK  | TIM15_BKIN        |

| PB13     | SPI2_SCK, I2S2_CK   | -         | TIM1_CH1N  | TSC_G6_IO3 | USART3_CTS | I2C2_SCL          |

| PB14     | SPI2_MISO, I2S2_MCK | TIM15_CH1 | TIM1_CH2N  | TSC_G6_IO4 | USART3_RTS | I2C2_SDA          |

| PB15     | SPI2_MOSI, I2S2_SD  | TIM15_CH2 | TIM1_CH3N  | TIM15_CH1N | -          | -                 |

\_ - -. . - -- -\_ - ----\_ . \_

40/122

5

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

| I                                    | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

|                                      | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| $\Sigma I_{IO(PIN)}$                 | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Total output current sourced by sum of all I/Os supplied by VDDIO2              | -40                  |      |

|                                      | Injected current on B, FT and FTf pins                                          | -5/+0 <sup>(4)</sup> | 1    |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  | 1    |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  | 1    |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 | 1    |

#### Table 22. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 21: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. On these I/Os, a positive injection is induced by  $V_{IN} > V_{DDA}$ . Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 59: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 23. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

| Sym-             | Poro                                                                            |                                |                                                              |       | Тур   | @V <sub>DD</sub> ( | V <sub>DD</sub> = V | / <sub>DDA</sub> )    |       |                           | Max <sup>(1)</sup>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |     |   |   |   |  |

|------------------|---------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------|-------|-------|--------------------|---------------------|-----------------------|-------|---------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|---|---|---|--|

| bol              | Para-<br>meter                                                                  |                                | Conditions                                                   | 2.0 V | 2.4 V | 2.7 V              | 3.0 V               | 3.3 V                 | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | $T_{A} = 105 °C$ $68^{(2)}$ $51^{(2)}$ $-$ $3.1^{(2)}$ $4.6^{(2)}$ $-$ $4.6^{(2)}$ $-$ $-$ $-$ $-$ $-$ $-$ $-$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Unit |     |   |   |   |  |

|                  | Supply current in                                                               | mod                            | julator in run<br>de, all<br>illators OFF                    | 15.4  | 15.5  | 15.6               | 15.7                | 15.8                  | 15.9  | 23 <sup>(2)</sup>         | 49                        | 68 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

| I <sub>DD</sub>  | Stop<br>mode                                                                    | pow                            | ulator in low-<br>ver mode, all<br>illators OFF              | 3.2   | 3.3   | 3.4                | 3.5                 | 3.6                   | 3.7   | 8(2)                      | 33                        | 51 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

|                  | Supply current in                                                               | LSI<br>ON                      | ON and IWDG                                                  | 0.8   | 1.0   | 1.1                | 1.2                 | 1.3                   | 1.4   | -                         | -                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

|                  | Standby<br>mode                                                                 | LSI<br>OFF                     | OFF and IWDG                                                 | 0.6   | 0.7   | 0.9                | 0.9                 | 1.0                   | 1.1   | 2.1 <sup>(2)</sup>        | 2.6                       | $     \begin{array}{r}       T_A = \\       105 °C \\       68^{(2)} \\       51^{(2)} \\       - \\       3.1^{(2)} \\       4.6^{(2)} \\       - \\       4.6^{(2)} \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\      - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - \\       - $ |      |     |   |   |   |  |

|                  | Supply<br>current in<br>Stop<br>mode<br>Supply<br>current in<br>Standby<br>mode | NO                             | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 2.1   | 2.2   | 2.3                | 2.5                 | 2.6                   | 2.8   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |   |   |   |  |

|                  |                                                                                 | V <sub>DDA</sub> monitoring O  | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 2.1   | 2.2   | 2.3                | 2.5                 | 2.6                   | 2.8   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | μΑ   |     |   |   |   |  |

|                  |                                                                                 |                                |                                                              |       |       |                    | VDC                 | LSI ON and<br>IWDG ON | 2.5   | 2.7                       | 2.8                       | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.2  | 3.5 | - | - | - |  |

| <br>             |                                                                                 |                                | LSI OFF and<br>IWDG OFF                                      | 1.9   | 2.1   | 2.2                | 2.3                 | 2.5                   | 2.6   | 3.5 <sup>(2)</sup>        | 3.6                       | 4.6 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |   |   |   |  |

| I <sub>DDA</sub> | Supply current in                                                               | OFF                            | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 1.3   | 1.3   | 1.4                | 1.4                 | 1.5                   | 1.5   | -                         | -                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

|                  | Stop<br>mode                                                                    | V <sub>DDA</sub> monitoring OI | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.3   | 1.3   | 1.4                | 1.4                 | 1.5                   | 1.5   | -                         | -                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

|                  | Supply current in                                                               | V <sub>DD</sub>                | LSI ON and<br>IWDG ON                                        | 1.7   | 1.8   | 1.9                | 2.0                 | 2.1                   | 2.2   | -                         | -                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

|                  | Standby<br>mode                                                                 |                                | LSI OFF and<br>IWDG OFF                                      | 1.2   | 1.2   | 1.2                | 1.3                 | 1.3                   | 1.4   | -                         | -                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     |   |   |   |  |

Table 31. Typical and maximum consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

2. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

|     | Peripheral                | rrent consumption (continued<br>Typical consumption at 25 °C | Unit   |

|-----|---------------------------|--------------------------------------------------------------|--------|

|     | APB-Bridge <sup>(2)</sup> | 2.8                                                          | onn    |

|     | ADC <sup>(3)</sup>        |                                                              |        |

|     |                           | 4.1                                                          |        |

|     | CEC                       | 1.5                                                          |        |

|     | CRS                       | 0.8                                                          |        |

|     | DAC <sup>(3)</sup>        | 4.7                                                          |        |

|     | DEBUG (MCU debug feature) | 0.1                                                          |        |

|     | I2C1                      | 3.9                                                          |        |

|     | I2C2                      | 4.0                                                          |        |

|     | PWR                       | 1.3                                                          |        |

|     | SPI1                      | 8.7                                                          |        |

|     | SPI2                      | 8.5                                                          |        |

|     | SYSCFG & COMP             | 1.7                                                          |        |

|     | TIM1                      | 14.9                                                         |        |

|     | TIM2                      | 15.5                                                         |        |

|     | TIM3                      | 11.4                                                         |        |