Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status | Active                                                                |  |

|-------------------------------|-----------------------------------------------------------------------|--|

|                               |                                                                       |  |

| Core Processor                | ARM® Cortex®-M0                                                       |  |

| Core Size                     | 32-Bit Single-Core                                                    |  |

| Speed                         | 48MHz                                                                 |  |

| Connectivity                  | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |  |

| Peripherals                   | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |  |

| Number of I/O                 | 87                                                                    |  |

| Program Memory Size           | 128KB (128K x 8)                                                      |  |

| Program Memory Type           | FLASH                                                                 |  |

| EEPROM Size                   | -                                                                     |  |

| RAM Size                      | 16K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd)    | 1.65V ~ 3.6V                                                          |  |

| Data Converters               | A/D 19x12b; D/A 2x12b                                                 |  |

| Oscillator Type               | Internal                                                              |  |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                     |  |

| Mounting Type                 | Surface Mount                                                         |  |

| Package / Case                | 100-LQFP                                                              |  |

| Supplier Device Package       | 100-LQFP (14x14)                                                      |  |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f071vbt6 |  |

# 2 Description

The STM32F071x8/xB microcontrollers incorporate the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0 32-bit RISC core operating at up to 48 MHz frequency, high-speed embedded memories (up to 128 Kbytes of Flash memory and 16 Kbytes of SRAM), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces (two I<sup>2</sup>Cs, two SPI/one I<sup>2</sup>S, one HDMI CEC and four USARTs), one 12-bit ADC, one 12-bit DAC with two channels, seven 16-bit timers, one 32-bit timer and an advanced-control PWM timer.

The STM32F071x8/xB microcontrollers operate in the -40 to +85 °C and -40 to +105 °C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F071x8/xB microcontrollers include devices in six different packages ranging from 48 pins to 100 pins with a die form also available upon request. Depending on the device chosen, different sets of peripherals are included.

These features make the STM32F071x8/xB microcontrollers suitable for a wide range of applications such as application control and user interfaces, hand-held equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms and HVACs.

47/

Table 2. STM32F071x8/xB family device features and peripheral counts

| Perip       | heral                                 | STM32              | F071Cx                                                                                                              | STM32F071RB              | STM32 | 2F071Vx        |  |  |  |  |

|-------------|---------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-------|----------------|--|--|--|--|

| Flash mem   | ory (Kbyte)                           | 64                 | 128                                                                                                                 | 128                      | 64    | 128            |  |  |  |  |

| SRAM        | (Kbyte)                               |                    | 16                                                                                                                  |                          |       |                |  |  |  |  |

|             | Advanced control                      |                    | 1 (16-bit)                                                                                                          |                          |       |                |  |  |  |  |

| Timers      | General<br>purpose                    |                    |                                                                                                                     | 5 (16-bit)<br>1 (32-bit) |       |                |  |  |  |  |

|             | Basic                                 |                    |                                                                                                                     | 2 (16-bit)               |       |                |  |  |  |  |

|             | SPI [I <sup>2</sup> S] <sup>(1)</sup> |                    | 2 [2]                                                                                                               |                          |       |                |  |  |  |  |

| Comm.       | I <sup>2</sup> C                      |                    | 2                                                                                                                   |                          |       |                |  |  |  |  |

| interfaces  | USART                                 |                    |                                                                                                                     | 4                        |       |                |  |  |  |  |

|             | CEC                                   |                    | 1                                                                                                                   |                          |       |                |  |  |  |  |

|             | t ADC<br>f channels)                  |                    | 1 (10 ext. + 3 int.) 1 (16 ext. + 3 int.)                                                                           |                          |       |                |  |  |  |  |

|             | t DAC<br>f channels)                  |                    | 1<br>(2)                                                                                                            |                          |       |                |  |  |  |  |

| Analog co   | omparator                             |                    |                                                                                                                     | 2                        |       |                |  |  |  |  |

| GP          | lOs                                   | 3                  | 7                                                                                                                   | 51                       | :     | 87             |  |  |  |  |

|             | e sensing<br>nnels                    | 1                  | 7                                                                                                                   | 18                       |       | 24             |  |  |  |  |

| Max. CPU    | frequency                             |                    |                                                                                                                     | 48 MHz                   | •     |                |  |  |  |  |

| Operatin    | g voltage                             |                    |                                                                                                                     | 2.0 to 3.6 V             |       |                |  |  |  |  |

| Operating t | emperature                            | A                  | Ambient operating temperature: -40°C to 85°C / -40°C to 105°C Junction temperature: -40°C to 105°C / -40°C to 125°C |                          |       |                |  |  |  |  |

| Pack        | ages                                  | LQF<br>UFQF<br>WLC | PN48                                                                                                                | LQFP64                   | •     | FP100<br>GA100 |  |  |  |  |

<sup>1.</sup> The SPI interface can be used either in SPI mode or in I<sup>2</sup>S audio mode.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 87 GPIOs can be connected to the 16 external interrupt lines.

## 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                      | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV)  | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference (V<sub>REFINT</sub>) provides a stable (bandgap) voltage output for the ADC and comparators. V<sub>REFINT</sub> is internally connected to the ADC\_IN17 input channel. The

Table 12. Legend/abbreviations used in the pinout table

| Na        | me                   | Abbreviation                      | Definition                                                                                        |  |  |  |  |

|-----------|----------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin r     | name                 |                                   | specified in brackets below the pin name, the pin function during and ame as the actual pin name  |  |  |  |  |

|           |                      | S                                 | Supply pin                                                                                        |  |  |  |  |

| Pin       | type                 | I                                 | Input-only pin                                                                                    |  |  |  |  |

|           |                      | I/O                               | Input / output pin                                                                                |  |  |  |  |

|           |                      | FT                                | 5 V-tolerant I/O                                                                                  |  |  |  |  |

|           |                      | FTf 5 V-tolerant I/O, FM+ capable |                                                                                                   |  |  |  |  |

| UO etr    | ucture               | TTa                               | 3.3 V-tolerant I/O directly connected to ADC                                                      |  |  |  |  |

| 1/0 511   | ucture               | TC                                | Standard 3.3 V I/O                                                                                |  |  |  |  |

|           |                      | В                                 | Dedicated BOOT0 pin                                                                               |  |  |  |  |

|           |                      | RST                               | Bidirectional reset pin with embedded weak pull-up resistor                                       |  |  |  |  |

| No        | tes                  | Unless otherwise reset.           | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset. |  |  |  |  |

| Pin       | Alternate functions  | Functions selected                | d through GPIOx_AFR registers                                                                     |  |  |  |  |

| functions | Additional functions | Functions directly                | selected/enabled through peripheral registers                                                     |  |  |  |  |

Table 13. STM32F071x8/xB pin definitions

|          | Pin     | numb   | ers             |         |                                      |             |         |            | Pin functions        |                                            |  |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------|------------|----------------------|--------------------------------------------|--|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | Not Not |            | Alternate functions  | Additional<br>functions                    |  |

| B2       | 1       | -      | -               | -       | PE2                                  | I/O         | FT      | -          | TSC_G7_IO1, TIM3_ETR | -                                          |  |

| A1       | 2       | ı      | -               | -       | PE3                                  | I/O         | FT      | -          | TSC_G7_IO2, TIM3_CH1 | -                                          |  |

| B1       | 3       | ı      | -               | -       | PE4                                  | I/O         | FT      | -          | TSC_G7_IO3, TIM3_CH2 | -                                          |  |

| C2       | 4       | -      | -               | -       | PE5                                  | I/O         | FT      | -          | TSC_G7_IO4, TIM3_CH3 | -                                          |  |

| D2       | 5       | i      | -               | -       | PE6                                  | I/O         | FT      | -          | TIM3_CH4             | WKUP3,<br>RTC_TAMP3                        |  |

| E2       | 6       | 1      | 1               | В7      | VBAT                                 | S           | -       | -          | Backup power s       | upply                                      |  |

| C1       | 7       | 2      | 2               | D5      | PC13                                 | I/O         | TC      | (1)<br>(2) | -                    | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |  |

Table 13. STM32F071x8/xB pin definitions (continued)

|          | Pin     | numb   | ers             |         |                                      |             |               |       | Pin function                                                                          | ıs                      |

|----------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| M7       | 38      | -      | -               | -       | PE7                                  | I/O         | FT            | -     | TIM1_ETR                                                                              | -                       |

| L7       | 39      | ı      | -               | -       | PE8                                  | I/O         | FT            | -     | TIM1_CH1N                                                                             | -                       |

| M8       | 40      | -      | -               | -       | PE9                                  | I/O         | FT            | -     | TIM1_CH1                                                                              | -                       |

| L8       | 41      | ı      | -               | -       | PE10                                 | I/O         | FT            | -     | TIM1_CH2N                                                                             | -                       |

| М9       | 42      | 1      | -               | -       | PE11                                 | I/O         | FT            | -     | TIM1_CH2                                                                              | -                       |

| L9       | 43      | -      | -               | -       | PE12                                 | I/O         | FT            | -     | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                                       | -                       |

| M10      | 44      | -      | -               | -       | PE13                                 | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                                        | -                       |

| M11      | 45      | -      | -               | -       | PE14                                 | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM1_CH4                                                      | -                       |

| M12      | 46      | -      | -               | -       | PE15                                 | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>TIM1_BKIN                                                      | -                       |

| L10      | 47      | 29     | 21              | E3      | PB10                                 | I/O         | FT            | -     | SPI2_SCK, I2C2_SCL,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3                          | -                       |

| L11      | 48      | 30     | 22              | G2      | PB11                                 | I/O         | FT            | -     | USART3_RX, TIM2_CH4,<br>EVENTOUT, TSC_G6_IO1,<br>I2C2_SDA                             | -                       |

| F12      | 49      | 31     | 23              | D3      | VSS                                  | S           | -             | -     | Ground                                                                                |                         |

| G12      | 50      | 32     | 24              | F2      | VDD                                  | S           | -             | -     | Digital power su                                                                      | ıpply                   |

| L12      | 51      | 33     | 25              | E2      | PB12                                 | I/O         | FT            | -     | TIM1_BKIN, TIM15_BKIN,<br>SPI2_NSS, I2S2_WS,<br>USART3_CK,<br>TSC_G6_IO2,<br>EVENTOUT | -                       |

| K12      | 52      | 34     | 26              | G1      | PB13                                 | I/O         | FTf           | -     | SPI2_SCK, I2S2_CK,<br>I2C2_SCL, USART3_CTS,<br>TIM1_CH1N, TSC_G6_IO3                  | -                       |

| K11      | 53      | 35     | 27              | F1      | PB14                                 | I/O         | FTf           | -     | SPI2_MISO, I2S2_MCK,<br>I2C2_SDA, USART3_RTS,<br>TIM1_CH2N, TIM15_CH1,<br>TSC_G6_IO4  | -                       |

Table 13. STM32F071x8/xB pin definitions (continued)

|          | Pin     | numb   | ers             |         |                                      |                          |    |            | Pin function                                                                 | ıs                      |

|----------|---------|--------|-----------------|---------|--------------------------------------|--------------------------|----|------------|------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin type Notes Notes (3) |    | Notes      | Alternate functions                                                          | Additional<br>functions |

| C11      | 73      | -      | -               | -       | PF6                                  | I/O                      | FT | (3)        | -                                                                            | -                       |

| F11      | 74      | 47     | 35              | B1      | VSS                                  | S                        | -  | -          | Ground                                                                       |                         |

| G11      | 75      | 48     | 36              | B2      | VDDIO2                               | S                        | -  | -          | Digital power su                                                             | ipply                   |

| A10      | 76      | 49     | 37              | A1      | PA14                                 | I/O                      | FT | (3)<br>(4) | USART2_TX, SWCLK                                                             | -                       |

| A9       | 77      | 50     | 38              | A2      | PA15                                 | I/O                      | FT | (3)        | SPI1_NSS, I2S1_WS,<br>USART2_RX,<br>USART4_RTS,<br>TIM2_CH1_ETR,<br>EVENTOUT | -                       |

| B11      | 78      | 51     | -               | -       | PC10                                 | I/O                      | FT | (3)        | USART3_TX, USART4_TX                                                         | -                       |

| C10      | 79      | 52     | -               | -       | PC11                                 | I/O                      | FT | (3)        | USART3_RX, USART4_RX                                                         | -                       |

| B10      | 80      | 53     | -               | -       | PC12                                 | I/O                      | FT | (3)        | USART3_CK,<br>USART4_CK                                                      | -                       |

| C9       | 81      | -      | -               | -       | PD0                                  | I/O                      | FT | (3)        | SPI2_NSS, I2S2_WS                                                            | -                       |

| В9       | 82      | -      | -               | -       | PD1                                  | I/O                      | FT | (3)        | SPI2_SCK, I2S2_CK                                                            | -                       |

| C8       | 83      | 54     | -               | -       | PD2                                  | I/O                      | FT | (3)        | USART3_RTS, TIM3_ETR                                                         | -                       |

| В8       | 84      | ı      | -               | 1       | PD3                                  | I/O                      | FT | -          | SPI2_MISO, I2S2_MCK,<br>USART2_CTS                                           | -                       |

| В7       | 85      | -      | -               | -       | PD4                                  | I/O                      | FT | -          | SPI2_MOSI, I2S2_SD,<br>USART2_RTS                                            | -                       |

| A6       | 86      | -      | -               | -       | PD5                                  | I/O                      | FT | -          | USART2_TX                                                                    | -                       |

| В6       | 87      | -      | -               | -       | PD6                                  | I/O                      | FT | -          | USART2_RX                                                                    | -                       |

| A5       | 88      | ı      | -               | -       | PD7                                  | I/O                      | FT | -          | USART2_CK                                                                    | -                       |

| A8       | 89      | 55     | 39              | A3      | PB3                                  | I/O                      | FT | -          | SPI1_SCK, I2S1_CK,<br>TIM2_CH2, TSC_G5_IO1,<br>EVENTOUT                      | -                       |

| A7       | 90      | 56     | 40              | A4      | PB4                                  | I/O                      | FT | -          | SPI1_MISO, I2S1_MCK,<br>TIM17_BKIN, TIM3_CH1,<br>TSC_G5_IO2, EVENTOUT        | -                       |

| C5       | 91      | 57     | 41              | B4      | PB5                                  | I/O                      | FT | -          | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA, TIM16_BKIN,<br>TIM3_CH2                    | WKUP6                   |

Table 18. Alternate functions selected through GPIOE\_AFR registers for port E

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_IO2          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | -                   |

| PE8      | TIM1_CH1N | -                   |

| PE9      | TIM1_CH1  | -                   |

| PE10     | TIM1_CH2N | -                   |

| PE11     | TIM1_CH2  | -                   |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

Table 19. Alternate functions available on port F

| Pin name | AF        |

|----------|-----------|

| PF0      | CRS_SYNC  |

| PF1      | -         |

| PF2      | EVENTOUT  |

| PF3      | EVENTOUT  |

| PF6      | -         |

| PF9      | TIM15_CH1 |

| PF10     | TIM15_CH2 |

# 6.1.7 Current consumption measurement

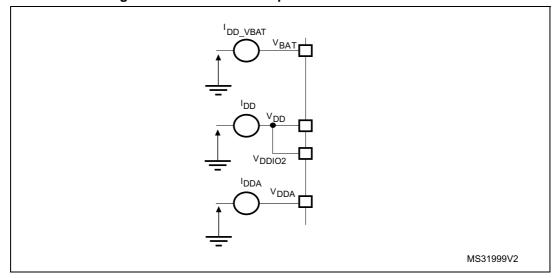

Figure 13. Current consumption measurement scheme

| Symbol                              | Parameter               | Conditions   | Min  | Тур  | Max                 | Unit |

|-------------------------------------|-------------------------|--------------|------|------|---------------------|------|

| V                                   | PVD threshold 6         | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |

| V <sub>PVD6</sub>                   | F VD tillesiloid o      | Falling edge | 2.56 | 2.68 | 2.8                 | V    |

| V                                   | PVD threshold 7         | Rising edge  | 2.76 | 2.88 | 3                   | V    |

| V <sub>PVD7</sub>                   | F VD tillesiloid 7      | Falling edge | 2.66 | 2.78 | 2.9                 | V    |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis          | -            | -    | 100  | -                   | mV   |

| I <sub>DD(PVD)</sub>                | PVD current consumption | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μΑ   |

Table 27. Programmable voltage detector characteristics (continued)

#### 6.3.4 Embedded reference voltage

The parameters given in *Table 28* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

|                        | Table 201 Elliboa                                             | aoa iiitoiiiai roioroiiot         | , ronag              | •    |                    |        |

|------------------------|---------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|

| Symbol                 | Parameter                                                     | Conditions                        | Min                  | Тур  | Max                | Unit   |

| $V_{REFINT}$           | Internal reference voltage                                    | -40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |

| t <sub>START</sub>     | ADC_IN17 buffer startup time                                  | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |

| t <sub>S_vrefint</sub> | ADC sampling time when reading the internal reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |

| $\Delta V_{REFINT}$    | Internal reference voltage spread over the temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |

| T <sub>Coeff</sub>     | Temperature coefficient                                       | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |

Table 28. Embedded internal reference voltage

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 13: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>1.</sup> Guaranteed by design, not tested in production.

Table 29. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD}$  = 3.6 V (continued)

|                 | ī                                                   |                       |                   | Α    | II periphe                          | rals ena | bled                | All  | periphe                             | rals disa | abled               |      |

|-----------------|-----------------------------------------------------|-----------------------|-------------------|------|-------------------------------------|----------|---------------------|------|-------------------------------------|-----------|---------------------|------|

| Symbol          | Parameter                                           | Conditions            | f <sub>HCLK</sub> |      | Max @ T <sub>A</sub> <sup>(1)</sup> |          |                     |      | Max @ T <sub>A</sub> <sup>(1)</sup> |           |                     | Unit |

| Sy              | S <sub>)</sub>                                      |                       |                   | Тур  | 25 °C                               | 85 °C    | 105 °C              | Тур  | 25 °C                               | 85 °C     | 105 °C              |      |

|                 |                                                     | HSI48                 | 48 MHz            | 23.1 | 25.4                                | 25.8     | 26.6                | 12.8 | 13.5                                | 13.7      | 13.9                |      |

|                 |                                                     |                       | 48 MHz            | 23.0 | 25.3 <sup>(2)</sup>                 | 25.7     | 26.5 <sup>(2)</sup> | 12.6 | 13.3 <sup>(2)</sup>                 | 13.5      | 13.8 <sup>(2)</sup> |      |

|                 | Supply current in Run mode, code executing from RAM | HSE bypass,<br>PLL on | 32 MHz            | 15.4 | 17.3                                | 17.8     | 18.3                | 7.96 | 8.92                                | 9.17      | 9.73                |      |

|                 | upply current in Run mode code executing from RAM   |                       | 24 MHz            | 11.4 | 12.9                                | 13.5     | 13.7                | 6.48 | 8.04                                | 8.23      | 8.41                |      |

|                 | n Ru<br>g froi                                      | HSE bypass,           | 8 MHz             | 4.21 | 4.6                                 | 4.89     | 5.25                | 2.07 | 2.3                                 | 2.35      | 2.94                |      |

|                 | ent i<br>uting                                      | PLL off               | 1 MHz             | 0.78 | 0.9                                 | 0.92     | 1.15                | 0.36 | 0.48                                | 0.59      | 0.82                |      |

| curre           | curr                                                |                       | 48 MHz            | 23.1 | 24.5                                | 25.0     | 25.2                | 12.6 | 13.7                                | 13.9      | 14.0                |      |

|                 | pply<br>ode (                                       | HSI clock,<br>PLL on  | 32 MHz            | 15.4 | 17.4                                | 17.7     | 18.2                | 8.05 | 8.85                                | 9.16      | 9.94                |      |

|                 | lns                                                 |                       | 24 MHz            | 11.5 | 13.0                                | 13.6     | 13.9                | 6.49 | 8.06                                | 8.21      | 8.47                |      |

|                 |                                                     | HSI clock,<br>PLL off | 8 MHz             | 4.34 | 4.75                                | 5.03     | 5.41                | 2.11 | 2.36                                | 2.38      | 2.98                | mA   |

| I <sub>DD</sub> |                                                     | HSI48                 | 48 MHz            | 15.1 | 16.6                                | 16.8     | 17.5                | 3.08 | 3.43                                | 3.56      | 3.61                | IIIA |

|                 |                                                     |                       | 48 MHz            | 15.0 | 16.5 <sup>(2)</sup>                 | 16.7     | 17.3 <sup>(2)</sup> | 2.93 | 3.28 <sup>(2)</sup>                 | 3.41      | 3.46 <sup>(2)</sup> |      |

|                 | Poor                                                | HSE bypass,<br>PLL on | 32 MHz            | 9.9  | 11.4                                | 11.6     | 11.9                | 2.0  | 2.24                                | 2.32      | 2.49                |      |

|                 | u də;                                               |                       | 24 MHz            | 7.43 | 8.17                                | 8.71     | 8.82                | 1.63 | 1.82                                | 1.88      | 1.9                 |      |

|                 | Sle                                                 | HSE bypass,           | 8 MHz             | 2.83 | 3.09                                | 3.26     | 3.66                | 0.76 | 0.88                                | 0.91      | 0.93                |      |

|                 | ant ir                                              | PLL off               | 1 MHz             | 0.42 | 0.54                                | 0.55     | 0.67                | 0.28 | 0.39                                | 0.41      | 0.43                |      |

|                 | curre                                               |                       | 48 MHz            | 15.0 | 17.2                                | 17.3     | 17.9                | 3.04 | 3.37                                | 3.41      | 3.46                |      |

|                 | Supply current in Sleep mode                        | HSI clock,<br>PLL on  | 32 MHz            | 9.93 | 11.3                                | 11.6     | 11.7                | 2.11 | 2.35                                | 2.44      | 2.65                |      |

|                 | Sup                                                 |                       | 24 MHz            | 7.53 | 8.45                                | 8.87     | 8.95                | 1.64 | 1.83                                | 1.9       | 1.93                |      |

|                 |                                                     | HSI clock,<br>PLL off | 8 MHz             | 2.95 | 3.24                                | 3.41     | 3.8                 | 0.8  | 0.92                                | 0.94      | 0.97                |      |

<sup>1.</sup> Data based on characterization results, not tested in production unless otherwise specified.

<sup>2.</sup> Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions <sup>(1)</sup>                                                                                                        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency        | -                                                                                                                                | 4                  | 8   | 32                 | MHz  |

| $R_{F}$                             | Feedback resistor           | -                                                                                                                                | -                  | 200 | -                  | kΩ   |

|                                     |                             | During startup <sup>(3)</sup>                                                                                                    | -                  | -   | 8.5                |      |

|                                     |                             | $V_{DD} = 3.3 \text{ V},$<br>$Rm = 30 \Omega,$<br>CL = 10  pF@8 MHz                                                              | -                  | 0.4 | -                  |      |

|                                     |                             | $V_{DD}$ = 3.3 V,<br>Rm = 45 $\Omega$ ,<br>CL = 10 pF@8 MHz                                                                      | -                  | 0.5 | -                  |      |

| I <sub>DD</sub>                     | HSE current consumption     | $V_{DD}$ = 3.3 V,<br>Rm = 30 $\Omega$ ,<br>CL = 5 pF@32 MHz                                                                      | -                  | 0.8 | -                  | mA   |

|                                     |                             | $V_{DD}$ = 3.3 V,<br>Rm = 30 $\Omega$ ,<br>CL = 10 pF@32 MHz                                                                     | -                  | 1   | -                  |      |

|                                     |                             | $V_{DD} = 3.3 \text{ V},$ $Rm = 30 \Omega,$ $CL = 5 \text{ pF}@32 \text{ MHz}$ $V_{DD} = 3.3 \text{ V},$ $Rm = 30 \Omega,$ $-$ 1 | -                  |     |                    |      |

| 9 <sub>m</sub>                      | Oscillator transconductance | Startup                                                                                                                          | 10                 | -   | -                  | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                | V <sub>DD</sub> is stabilized                                                                                                    | -                  | 2   | -                  | ms   |

Table 39. HSE oscillator characteristics

- 1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Guaranteed by design, not tested in production.

- 3. This consumption level occurs during the first 2/3 of the  $t_{\text{SU(HSE)}}$  startup time

- 4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

| Symbol             | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |

|--------------------|----------------|----------------------------------------------------|--------------------|--------|--|

| N <sub>END</sub>   | Endurance      | $T_A = -40 \text{ to } +105 ^{\circ}\text{C}$      | 10                 | kcycle |  |

| t <sub>RET</sub> [ |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |

|                    | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |

|                    |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |

Table 47. Flash memory endurance and data retention

- 1. Data based on characterization results, not tested in production.

- 2. Cycling performed over the whole temperature range.

#### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

Level/ **Parameter Symbol Conditions Class**  $V_{DD} = 3.3 \text{ V, LQFP100, T}_{A} = +25 ^{\circ}\text{C,}$ Voltage limits to be applied on any I/O pin  $f_{HCLK} = 48 \text{ MHz},$ 2B  $V_{\text{FESD}}$ to induce a functional disturbance conforming to IEC 61000-4-2 Fast transient voltage burst limits to be  $V_{DD} = 3.3 \text{ V, LQFP100, } T_A = +25^{\circ}\text{C,}$  $f_{HCLK}$  = 48 MHz, applied through 100 pF on  $V_{DD}$  and  $V_{SS}$ 4B  $V_{EFTB}$ pins to induce a functional disturbance conforming to IEC 61000-4-4

**Table 48. EMS characteristics**

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol                 | Parameter                                       | Conditions                        | Min                | Тур | Max                | Unit |

|------------------------|-------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis         | -                                 | -                  | 200 | -                  | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |

| V                      | NRST input not filtered pulse                   | 2.7 < V <sub>DD</sub> < 3.6       | 300 <sup>(3)</sup> | -   | -                  | ns   |

| V <sub>NF(NRST)</sub>  | TWNOT Imput not intered pulse                   | 2.0 < V <sub>DD</sub> < 3.6       | 500 <sup>(3)</sup> | -   | -                  | 113  |

Table 56. NRST pin characteristics (continued)

- 1. Data based on design simulation only. Not tested in production.

- 2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

- 3. Data based on design simulation only. Not tested in production.

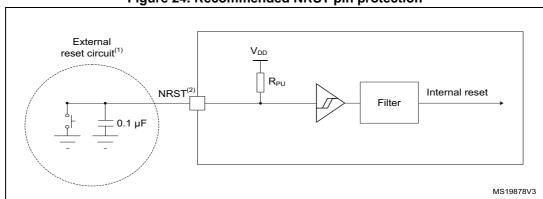

Figure 24. Recommended NRST pin protection

- 1. The external capacitor protects the device against parasitic resets.

- 2. The user must ensure that the level on the NRST pin can go below the  $V_{\rm IL(NRST)}$  max level specified in *Table 56: NRST pin characteristics*. Otherwise the reset will not be taken into account by the device.

#### 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

**Symbol Conditions** Unit **Parameter** Min Тур Max Analog supply voltage for 2.4 3.6 ٧  $V_{DDA}$ ADC ON Current consumption of  $V_{DDA} = 3.3 V$ 0.9 mA I<sub>DDA</sub> (ADC) the ADC<sup>(1)</sup> ADC clock frequency 0.6 14 MHz  $f_{ADC}$  $f_S^{(2)}$ Sampling rate 12-bit resolution 0.043 1 MHz

Table 57. ADC characteristics

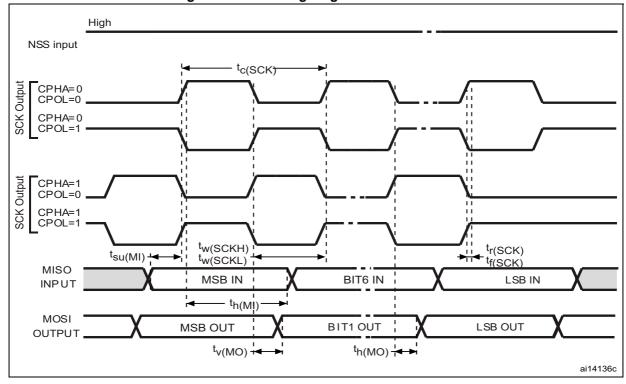

Figure 31. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\rm DD}$  and 0.7  $V_{\rm DD}$ .

Table 69. I<sup>2</sup>S characteristics<sup>(1)</sup>

| Symbol               | Parameter                                     | Conditions                                            | Min   | Max   | Unit |

|----------------------|-----------------------------------------------|-------------------------------------------------------|-------|-------|------|

| f <sub>CK</sub>      | I <sup>2</sup> S clock frequency              | Master mode (data: 16 bits, Audio frequency = 48 kHz) | 1.597 | 1.601 | MHz  |

| 1/t <sub>c(CK)</sub> |                                               | Slave mode                                            | 0     | 6.5   |      |

| t <sub>r(CK)</sub>   | I <sup>2</sup> S clock rise time              | Canacitive lead C = 15 pE                             | -     | 10    |      |

| t <sub>f(CK)</sub>   | I <sup>2</sup> S clock fall time              | Capacitive load C <sub>L</sub> = 15 pF                | -     | 12    |      |

| t <sub>w(CKH)</sub>  | I <sup>2</sup> S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio              | 306   | -     |      |

| t <sub>w(CKL)</sub>  | I <sup>2</sup> S clock low time               | frequency = 48 kHz                                    | 312   | -     |      |

| t <sub>v(WS)</sub>   | WS valid time                                 | Master mode                                           | 2     | -     | ns   |

| t <sub>h(WS)</sub>   | WS hold time                                  | Master mode                                           | 2     | -     |      |

| t <sub>su(WS)</sub>  | WS setup time                                 | Slave mode                                            | 7     | -     |      |

| t <sub>h(WS)</sub>   | WS hold time                                  | Slave mode                                            | 0     | -     |      |

| DuCy(SCK)            | I <sup>2</sup> S slave input clock duty cycle | Slave mode                                            | 25    | 75    | %    |

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

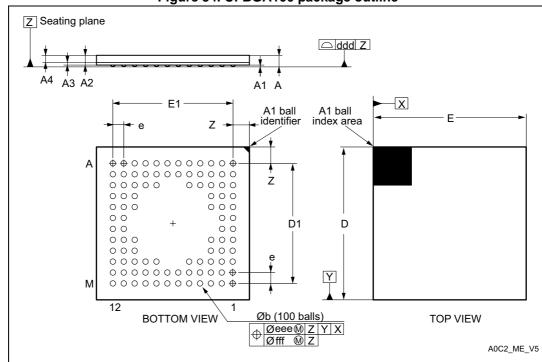

# 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 34. UFBGA100 package outline

1. Drawing is not to scale.

Table 70. UFBGA100 package mechanical data

| Sumbal |      | millimeters |       |      | inches <sup>(1)</sup> |        |

|--------|------|-------------|-------|------|-----------------------|--------|

| Symbol | Min. | Тур.        | Max.  | Min. | Тур.                  | Max.   |

| Α      | -    | -           | 0.600 | -    | -                     | 0.0236 |

| A1     | -    | -           | 0.110 | -    | -                     | 0.0043 |

| A2     | -    | 0.450       | -     | -    | 0.0177                | -      |

| A3     | -    | 0.130       | -     | -    | 0.0051                | 0.0094 |

| A4     | -    | 0.320       | -     | -    | 0.0126                | -      |

|          | rable 70. Of BOATOO package mechanical data (continued) |             |                             |        |                       |        |  |

|----------|---------------------------------------------------------|-------------|-----------------------------|--------|-----------------------|--------|--|

| Complead |                                                         | millimeters | eters inches <sup>(1)</sup> |        | inches <sup>(1)</sup> |        |  |

| Symbol   | Min.                                                    | Тур.        | Max.                        | Min.   | Тур.                  | Max.   |  |

| b        | 0.240                                                   | 0.290       | 0.340                       | 0.0094 | 0.0114                | 0.0134 |  |

| D        | 6.850                                                   | 7.000       | 7.150                       | 0.2697 | 0.2756                | 0.2815 |  |

| D1       | -                                                       | 5.500       | -                           | -      | 0.2165                | -      |  |

| Е        | 6.850                                                   | 7.000       | 7.150                       | 0.2697 | 0.2756                | 0.2815 |  |

| E1       | -                                                       | 5.500       | -                           | -      | 0.2165                | -      |  |

| е        | -                                                       | 0.500       | -                           | -      | 0.0197                | -      |  |

| Z        | -                                                       | 0.750       | -                           | -      | 0.0295                | -      |  |

| ddd      | -                                                       | -           | 0.080                       | -      | -                     | 0.0031 |  |

| eee      | -                                                       | -           | 0.150                       | -      | -                     | 0.0059 |  |

| fff      | -                                                       | -           | 0.050                       | -      | -                     | 0.0020 |  |

Table 70. UFBGA100 package mechanical data (continued)

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

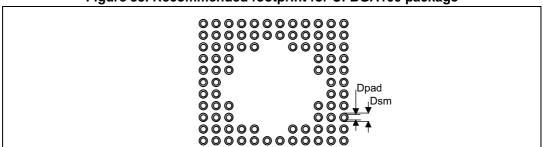

Figure 35. Recommended footprint for UFBGA100 package

Table 71. UFBGA100 recommended PCB design rules

| Dimension         | Recommended values                                                |

|-------------------|-------------------------------------------------------------------|

| Pitch             | 0.5                                                               |

| Dpad              | 0.280 mm                                                          |

| Dsm               | 0.370 mm typ. (depends on the solder mask registration tolerance) |

| Stencil opening   | 0.280 mm                                                          |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                     |

98/122 DocID025451 Rev 6

A0C2\_FP\_V1

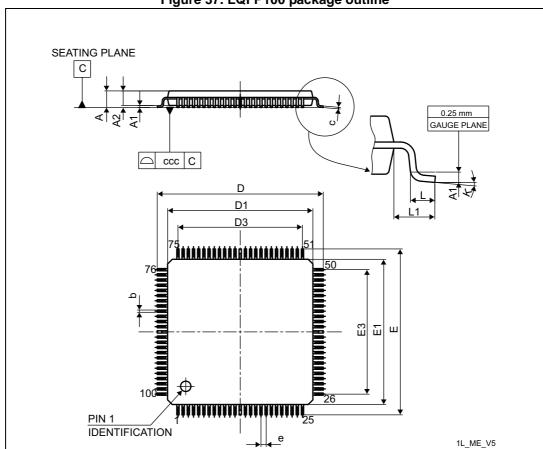

# 7.2 LQFP100 package information

LQFP100 is a100-pin, 14 x 14 mm low-profile quad flat package.

Figure 37. LQFP100 package outline

1. Drawing is not to scale.

Table 72. LQPF100 package mechanical data

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min    | Тур         | Max    | Min    | Тур                   | Max    |

| Α      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

## 7.7 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 24: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O}$$

max =  $\Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DDIOx} - V_{OH}) \times I_{OH})$ ,

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol | Parameter                                                              | Value | Unit |

|--------|------------------------------------------------------------------------|-------|------|

|        | Thermal resistance junction-ambient UFBGA100 - 7 × 7 mm                | 55    |      |

|        | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm            | 42    |      |

| ΘЈΑ    | Thermal resistance junction-ambient LQFP64 - 10 × 10 mm / 0.5 mm pitch | 44    | °C/W |

|        | Thermal resistance junction-ambient LQFP48 - 7 × 7 mm                  | 54    | C/VV |

|        | Thermal resistance junction-ambient UFQFPN48 - 7 × 7 mm                | 32    |      |

|        | Thermal resistance junction-ambient WLCSP49 - 0.4 mm pitch             | 49    |      |

Table 77. Package thermal characteristics

#### 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

## 7.7.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

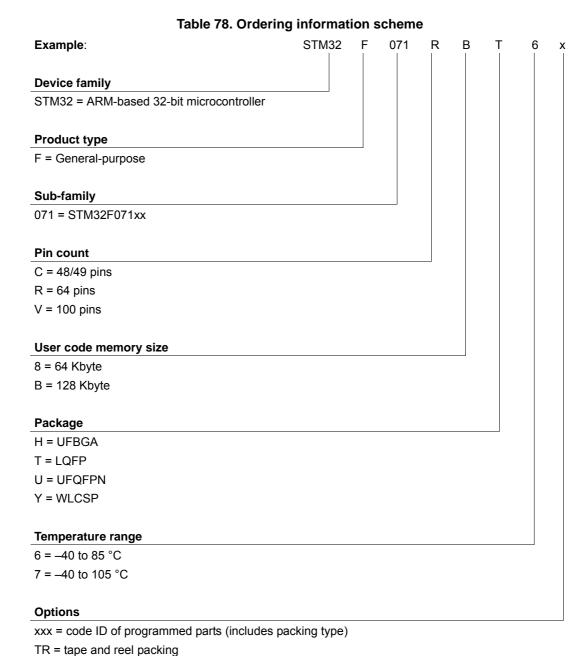

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID025451 Rev 6

blank = tray packing

Table 79. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Sep-2016 | 5        | Section 6: Electrical characteristics:  - Figure 29: SPI timing diagram - slave mode and CPHA = 0 and Figure 30: SPI timing diagram - slave mode and CPHA = 1 updated - modified NSS timing waveforms (among other changes)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10-Jan-2017 | 6        | Section 6: Electrical characteristics:  - Table 40: LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz) - information on configuring different drive capabilities removed. See the corresponding reference manual.  - Table 28: Embedded internal reference voltage - V <sub>REFINT</sub> values  - Table 60: DAC characteristics - min. R <sub>LOAD</sub> to V <sub>DDA</sub> defined  - Figure 29: SPI timing diagram - slave mode and CPHA = 0 and Figure 30: SPI timing diagram - slave mode and CPHA = 1 enhanced and corrected  Section 8: Ordering information:  - The name of the section changed from the previous "Part numbering" |