Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |  |

|----------------------------|-------------------------------------------------------------------------|--|

| Product Status             | Active                                                                  |  |

| Core Processor             | ARM® Cortex®-M0                                                         |  |

| Core Size                  | 32-Bit Single-Core                                                      |  |

| Speed                      | 48MHz                                                                   |  |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |  |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                 |  |

| Number of I/O              | 87                                                                      |  |

| Program Memory Size        | 128KB (128K x 8)                                                        |  |

| Program Memory Type        | FLASH                                                                   |  |

| EEPROM Size                | -                                                                       |  |

| RAM Size                   | 16K x 8                                                                 |  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |  |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                   |  |

| Oscillator Type            | Internal                                                                |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |  |

| Mounting Type              | Surface Mount                                                           |  |

| Package / Case             | 100-LQFP                                                                |  |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f071vbt6tr |  |

# **Contents**

| 1 | Intro | duction   |                                                   | 9  |

|---|-------|-----------|---------------------------------------------------|----|

| 2 | Desc  | ription . |                                                   | 10 |

| 3 | Fund  | tional o  | verview                                           | 13 |

|   | 3.1   | ARM®-     | Cortex <sup>®</sup> -M0 core                      | 13 |

|   | 3.2   | Memori    | ies                                               | 13 |

|   | 3.3   | Boot m    | odes                                              | 13 |

|   | 3.4   | Cyclic r  | redundancy check calculation unit (CRC)           | 14 |

|   | 3.5   | Power     | management                                        | 14 |

|   |       | 3.5.1     | Power supply schemes                              | 14 |

|   |       | 3.5.2     | Power supply supervisors                          | 14 |

|   |       | 3.5.3     | Voltage regulator                                 | 15 |

|   |       | 3.5.4     | Low-power modes                                   | 15 |

|   | 3.6   | Clocks    | and startup                                       | 15 |

|   | 3.7   | Genera    | ıl-purpose inputs/outputs (GPIOs)                 | 17 |

|   | 3.8   | Direct n  | memory access controller (DMA)                    | 17 |

|   | 3.9   | Interrup  | ots and events                                    | 17 |

|   |       | 3.9.1     | Nested vectored interrupt controller (NVIC)       |    |

|   |       | 3.9.2     | Extended interrupt/event controller (EXTI)        | 18 |

|   | 3.10  | Analog-   | -to-digital converter (ADC)                       | 18 |

|   |       | 3.10.1    | Temperature sensor                                | 18 |

|   |       | 3.10.2    | Internal voltage reference (V <sub>REFINT</sub> ) | 18 |

|   |       | 3.10.3    | V <sub>BAT</sub> battery voltage monitoring       | 19 |

|   | 3.11  | Digital-t | to-analog converter (DAC)                         | 19 |

|   | 3.12  | Compa     | rators (COMP)                                     | 19 |

|   | 3.13  | Touch s   | sensing controller (TSC)                          | 20 |

|   | 3.14  | Timers    | and watchdogs                                     | 21 |

|   |       | 3.14.1    | Advanced-control timer (TIM1)                     | 22 |

|   |       | 3.14.2    | General-purpose timers (TIM2, 3, 14, 15, 16, 17)  | 22 |

|   |       | 3.14.3    | Basic timers TIM6 and TIM7                        | 23 |

|   |       | 3.14.4    | Independent watchdog (IWDG)                       | 23 |

|   |       | 3.14.5    | System window watchdog (WWDG)                     | 23 |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F071x8/xB microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website <a href="https://www.st.com">www.st.com</a>.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

POWER SWCLK SWDIO as AF Serial Wire VOLT.REG  $V_{DD} = 2 \text{ to } 3.6 \text{ V}$ Debug 3.3 V to 1.8 V g Flash Cr memory interface Flash GPL up to 128 KB 32-bit CORTEX-M0 CPU f<sub>MAX</sub> = 48 MHz SUPPLY V<sub>DDIO2</sub> OKIN ◀ SUPERVISION POR ◀ SRAM NRST Bus matrix SRAM controller Reset ◀  $V_{DDA}$ 16 KB POR/PDR Int ◀  $V_{\text{SSA}}$ NVIC @ V<sub>DDA</sub> V<sub>DD</sub> HSI14 PVD RC 14 MHz HSI RC 8 MHz @ V<sub>DDA</sub> PLLCLK @ V<sub>DD</sub> LSI GP DMA RC 40 kHz XTAL OSC OSC\_IN OSC\_OUT 7 channels HSI48 RC 48MHz Ind. Window WDG GPIO port A PA[15:0] < RESET & CLOCK CONTROL ... V<sub>BAT</sub> = 1.65 to 3.6 V PB[15:0] GPIO port B @ V<sub>BAT</sub> OSC32\_IN OSC32\_OUT decoder PC[15:0] GPIO port C System and peripheral XTAL32 kHz clocks 3 TAMPER-RTC (ALARM OUT) GPIO port D PD[15:0] Backup RTC AHB reg PE[15:0] GPIO port E RTC interface PF[10:9], PF6 PF[3:0] CRS GPIO port F SYNC CRC 4 channels 3 compl. channels BRK, ETR input as AF PAD PWM TIMER 1 8 groups of 4 channels Touch Analog Sensing Controller switches TIMER 2 32-bit 4 ch., ETR as AF AHB SYNC APB 4 ch., ETR as AF TIMER 3 87 AF EXT. IT WKUP TIMER 14 1 channel as AF 2 channels 1 compl, BRK as AF TIMER 15 MOSI/SD 1 channel 1 compl, BRK as AF TIMER 16 MISO/MCK SCK/CK SPI1/I2S1 Window WDG 1 channel 1 compl, BRK as AF NSS/WS as AF TIMER 17 MOSI/SD IR\_OUT as AF MISO/MCK SCK/CK SPI2/I2S2 DBGMCU NSS/WS as AF\_ RX, TX,CTS, RTS, CK as AF USART1 RX, TX,CTS, RTS, CK as AF USART2 SYSCFG IF RX, TX,CTS, RTS, CK as AF USART3 INPUT + RX, TX,CTS, RTS, CK as AF GP comparator 1 USART4 INPUT -GP comparator 2 as AF @ V<sub>DDA</sub> SCL, SDA, SMBA (20 mA FM+) as AF 12C1 SCL. SDA 12C2 (20 mA FM+) as AF sensor 16x HDMI-CEC CEC as AF 12-bit ADC IF AD input TIMER 6 12-bit DAC → DAC\_OUT1  $V_{DDA} \ V_{SSA}$ TIMER 7 12-bit DAC ►DAC\_OUT2 @ V<sub>DDA</sub> @ V<sub>DDA</sub> Power domain of analog blocks :  $V_{BAT}$  $V_{DD}$  $V_{DDA}$ MSv30976V3

Figure 1. Block diagram

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.14.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

## 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.20 Clock recovery system (CRS)

The STM32F071x8/xB embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.21 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

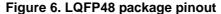

Top view VBAT □ □ VDDIO2 47 🗆 VSS PC13 [ PC14-OSC32\_IN [ 46 PA13 45 PA12 PC15-OSC32\_OUT 4 PF0-OSC\_IN [ 44 PA11 43 PA10 PF1-OSC\_OUT ☐ 6 NRST 🗆 7 42 PA9 PC0 ☐ 8 41 PA8 LQFP64 PC1 [ 40 PC9 39 PC8 PC2 🗆 10 PC3 🗆 11 38 PC7 37 PC6 VSSA ☐ 12 36 PB15 35 PB14 VDDA □ PA0 🗆 14 PA1 □ 34 🗆 PB13 PA2 16 33 🗆 PB12 ■ I/O supplied from VDDIO2 MSv31411V2

Figure 5. LQFP64 package pinout

577

## 6 Electrical characteristics

#### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

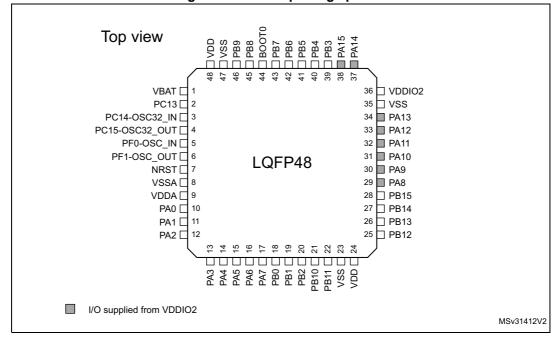

### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 11.

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 21: Voltage characteristics*, *Table 22: Current characteristics* and *Table 23: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 21. Voltage characteristics<sup>(1)</sup>

| Symbol                              | Ratings                                                 | Min                                                        | Max                         | Unit |

|-------------------------------------|---------------------------------------------------------|------------------------------------------------------------|-----------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>    | External main supply voltage                            | - 0.3                                                      | 4.0                         | V    |

| V <sub>DDIO2</sub> -V <sub>SS</sub> | External I/O supply voltage                             | - 0.3                                                      | 4.0                         | V    |

| V <sub>DDA</sub> -V <sub>SS</sub>   | External analog supply voltage                          | - 0.3                                                      | 4.0                         | V    |

| V <sub>DD</sub> -V <sub>DDA</sub>   | Allowed voltage difference for $V_{DD} > V_{DDA}$       | -                                                          | 0.4                         | ٧    |

| V <sub>BAT</sub> -V <sub>SS</sub>   | External backup supply voltage                          | - 0.3                                                      | 4.0                         | V    |

|                                     | Input voltage on FT and FTf pins                        | V <sub>SS</sub> - 0.3                                      | $V_{\rm DDIOx} + 4.0^{(3)}$ | ٧    |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on TTa pins                               | V <sub>SS</sub> - 0.3                                      | 4.0                         | V    |

| VIN.                                | BOOT0                                                   | 0                                                          | 9.0                         | V    |

|                                     | Input voltage on any other pin                          | V <sub>SS</sub> - 0.3                                      | 4.0                         | ٧    |

| ΔV <sub>DDx</sub>                   | Variations between different V <sub>DD</sub> power pins | -                                                          | 50                          | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub>  | Variations between all the different ground pins        | -                                                          | 50                          | mV   |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage (human body model)      | see Section 6.3.12: Electrical sensitivity characteristics |                             |      |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

<sup>2.</sup> V<sub>IN</sub> maximum must always be respected. Refer to *Table 22: Current characteristics* for the maximum allowed injected current values.

<sup>3.</sup> Valid only if the internal pull-up/pull-down resistors are disabled. If internal pull-up or pull-down resistor is enabled, the maximum limit is 4 V.

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 24. General operating conditions

| Symbol             | Parameter                                                             | Conditions                                             | Min             | Max                                  | Unit    |  |

|--------------------|-----------------------------------------------------------------------|--------------------------------------------------------|-----------------|--------------------------------------|---------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                          | -                                                      | 0               | 48                                   | MHz     |  |

| f <sub>PCLK</sub>  | Internal APB clock frequency                                          | -                                                      | 0               | 48                                   | IVII IZ |  |

| $V_{DD}$           | Standard operating voltage                                            | -                                                      | 2.0             | 3.6                                  | V       |  |

| V <sub>DDIO2</sub> | I/O supply voltage                                                    | Must not be supplied if V <sub>DD</sub> is not present | 1.65            | 3.6                                  | V       |  |

| V                  | Analog operating voltage (ADC and DAC not used)                       | Must have a potential equal                            | $V_{DD}$        | 3.6                                  | V       |  |

| $V_{DDA}$          | Analog operating voltage (ADC and DAC used)                           | to or higher than V <sub>DD</sub>                      | 2.4             | 3.6                                  | V       |  |

| V <sub>BAT</sub>   | Backup operating voltage                                              | -                                                      | 1.65            | 3.6                                  | V       |  |

|                    |                                                                       | TC and RST I/O                                         | -0.3            | V <sub>DDIOx</sub> +0.3              |         |  |

| V                  | I/O input voltage                                                     | TTa I/O                                                | -0.3            | V <sub>DDA</sub> +0.3 <sup>(1)</sup> | V       |  |

| $V_{IN}$           |                                                                       | FT and FTf I/O                                         | -0.3            | 5.5 <sup>(1)</sup>                   |         |  |

|                    |                                                                       | BOOT0                                                  | 0               | 5.5                                  |         |  |

|                    |                                                                       | UFBGA100                                               | -               | 364                                  |         |  |

|                    |                                                                       | LQFP100                                                | -               | 476                                  |         |  |

|                    | Power dissipation at $T_A = 85$ °C for suffix 6 or $T_A = 105$ °C for | LQFP64                                                 | -               | 455                                  | mW      |  |

| $P_{D}$            |                                                                       | LQFP48                                                 | _               | 370                                  |         |  |

|                    | suffix 7 <sup>(2)</sup>                                               | UFQFPN48                                               | -               | 625                                  |         |  |

|                    |                                                                       | WLCSP49                                                | -               | 408                                  |         |  |

|                    | Ambient temperature for the                                           | Maximum power dissipation                              | -40             | 85                                   | °C      |  |

| т.                 | suffix 6 version                                                      | Low power dissipation <sup>(3)</sup>                   | -40             | 105                                  | °C      |  |

| TA                 | Ambient temperature for the                                           | Maximum power dissipation                              | <del>-4</del> 0 | 105                                  | 0.0     |  |

|                    | suffix 7 version                                                      | Low power dissipation <sup>(3)</sup>                   | -40             | 125                                  | °C      |  |

| т.                 | lunation temporature range                                            | Suffix 6 version                                       | -40             | 105                                  | °C      |  |

| TJ                 | Junction temperature range                                            | Suffix 7 version                                       | -40             | 125                                  |         |  |

<sup>1.</sup> For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

## 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 25* are derived from tests performed under the ambient temperature condition summarized in *Table 24*.

<sup>2.</sup> If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.7: Thermal characteristics.

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.7: Thermal characteristics).

Table 35. Peripheral current consumption (continued)

|     | Peripheral                | Typical consumption at 25 °C | Unit   |

|-----|---------------------------|------------------------------|--------|

|     | APB-Bridge <sup>(2)</sup> | 2.8                          |        |

|     | ADC <sup>(3)</sup>        | 4.1                          |        |

|     | CEC                       | 1.5                          |        |

|     | CRS                       | 0.8                          |        |

|     | DAC <sup>(3)</sup>        | 4.7                          |        |

|     | DEBUG (MCU debug feature) | 0.1                          |        |

|     | I2C1                      | 3.9                          |        |

|     | I2C2                      | 4.0                          |        |

|     | PWR                       | 1.3                          |        |

|     | SPI1                      | 8.7                          |        |

|     | SPI2                      | 8.5                          |        |

|     | SYSCFG & COMP             | 1.7                          |        |

|     | TIM1                      | 14.9                         |        |

|     | TIM2                      | 15.5                         |        |

|     | TIM3                      | 11.4                         |        |

| APB | TIM6                      | 2.5                          | μΑ/MHz |

|     | TIM7                      | 2.3                          |        |

|     | TIM14                     | 5.3                          |        |

|     | TIM15                     | 9.1                          |        |

|     | TIM16                     | 6.6                          |        |

|     | TIM17                     | 6.8                          |        |

|     | USART1                    | 17.0                         |        |

|     | USART2                    | 16.7                         |        |

|     | USART3                    | 5.4                          |        |

|     | USART4                    | 5.4                          |        |

|     | WWDG                      | 1.4                          |        |

|     | All APB peripherals       | 162.4                        |        |

<sup>1.</sup> The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

<sup>2.</sup> The APB Bridge is automatically active when at least one peripheral is ON on the Bus.

<sup>3.</sup> The power consumption of the analog part  $(I_{DDA})$  of peripherals such as ADC, DAC, Comparators, is not included. Refer to the tables of characteristics in the subsequent sections.

## Low-speed internal (LSI) RC oscillator

Table 44. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  |                                  | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 105 °C unless otherwise specified.

## 6.3.9 PLL characteristics

The parameters given in *Table 45* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

Table 45. PLL characteristics

| Complete              | Parameter                      |                   | Unit |                    |       |

|-----------------------|--------------------------------|-------------------|------|--------------------|-------|

| Symbol                | Farameter                      | Min               | Тур  | Max                | Offic |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz   |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %     |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz   |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs    |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps    |

Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL OUT</sub>.

## 6.3.10 Memory characteristics

#### Flash memory

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

Table 46. Flash memory characteristics

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                    | Supply ourrant          | Write mode                       | -   | -    | 10                 | mA   |

| IDD                | Supply current          | Erase mode                       | -   | -    | 12                 | mA   |

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

Symbol Unit **Parameter Conditions** Min Тур Max TC, FT and FTf I/O TTa in digital mode ± 0.1  $V_{SS} \le V_{IN} \le V_{DDIOx}$ TTa in digital mode 1 Input leakage  $V_{\text{DDIO}X} \le V_{\text{IN}} \le V_{\text{DDA}}$  $I_{lkg}$ μΑ current(2) TTa in analog mode ± 0.2  $V_{SS} \le V_{IN} \le V_{DDA}$ FT and FTf I/O 10  $V_{DDIOx} \le V_{IN} \le 5 V$ Weak pull-up  $R_{PU}$ equivalent resistor  $V_{IN} = V_{SS}$ 25 40 55 kΩ Weak pull-down  $V_{IN} = -V_{DDIOx}$  $R_{PD}$ equivalent 25 40 55 kΩ resistor(3) рF

Table 53. I/O static characteristics (continued)

I/O pin capacitance

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in Figure 21 for standard I/Os, and in Figure 22 for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

5

$C_{IO}$

Data based on design simulation only. Not tested in production.

The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 52:

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

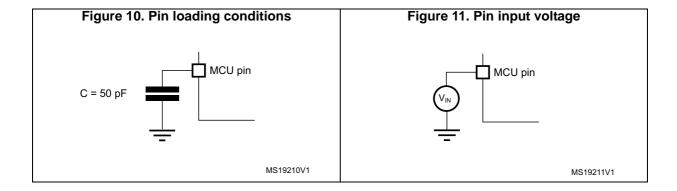

| Symbol                 | Parameter                                       | Conditions                        | Min                | Тур | Max                | Unit |

|------------------------|-------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis         | -                                 | -                  | 200 | -                  | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                   | 2.7 < V <sub>DD</sub> < 3.6       | 300 <sup>(3)</sup> | -   | -                  | ns   |

|                        | TWNOT Imput not intered pulse                   | 2.0 < V <sub>DD</sub> < 3.6       | 500 <sup>(3)</sup> | -   | -                  | 113  |

Table 56. NRST pin characteristics (continued)

- 1. Data based on design simulation only. Not tested in production.

- 2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

- 3. Data based on design simulation only. Not tested in production.

Figure 24. Recommended NRST pin protection

- 1. The external capacitor protects the device against parasitic resets.

- 2. The user must ensure that the level on the NRST pin can go below the  $V_{\rm IL(NRST)}$  max level specified in *Table 56: NRST pin characteristics*. Otherwise the reset will not be taken into account by the device.

#### 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

**Symbol Conditions** Unit **Parameter** Min Тур Max Analog supply voltage for 2.4 3.6 ٧  $V_{DDA}$ ADC ON Current consumption of  $V_{DDA} = 3.3 V$ 0.9 mA I<sub>DDA</sub> (ADC) the ADC<sup>(1)</sup> ADC clock frequency 0.6 14 MHz  $f_{ADC}$  $f_S^{(2)}$ Sampling rate 12-bit resolution 0.043 1 MHz

Table 57. ADC characteristics

82/122 DocID025451 Rev 6

| тако остато с получина интосия рогоси из то инте (201) |              |                                |                                |      |  |  |

|--------------------------------------------------------|--------------|--------------------------------|--------------------------------|------|--|--|

| Prescaler divider                                      | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |

| /4                                                     | 0            | 0.1                            | 409.6                          |      |  |  |

| /8                                                     | 1            | 0.2                            | 819.2                          |      |  |  |

| /16                                                    | 2            | 0.4                            | 1638.4                         |      |  |  |

| /32                                                    | 3            | 0.8                            | 3276.8                         | ms   |  |  |

| /64                                                    | 4            | 1.6                            | 6553.6                         |      |  |  |

| /128                                                   | 5            | 3.2                            | 13107.2                        |      |  |  |

| /256                                                   | 6 or 7       | 6.4                            | 26214.4                        |      |  |  |

Table 65. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Table 66. WWD6 Hillymax timeout value at 40 MHz (1 621) |                                                     |        |         |      |  |  |

|---------------------------------------------------------|-----------------------------------------------------|--------|---------|------|--|--|

| Prescaler                                               | Prescaler WDGTB Min timeout value Max timeout value |        | Unit    |      |  |  |

| 1                                                       | 0                                                   | 0.0853 | 5.4613  |      |  |  |

| 2                                                       | 1                                                   | 0.1706 | 10.9226 | ms   |  |  |

| 4                                                       | 2                                                   | 0.3413 | 21.8453 | 1115 |  |  |

| 8                                                       | 3                                                   | 0.6826 | 43.6906 |      |  |  |

Table 66. WWDG min/max timeout value at 48 MHz (PCLK)

### 6.3.22 Communication interfaces

## I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{\rm DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

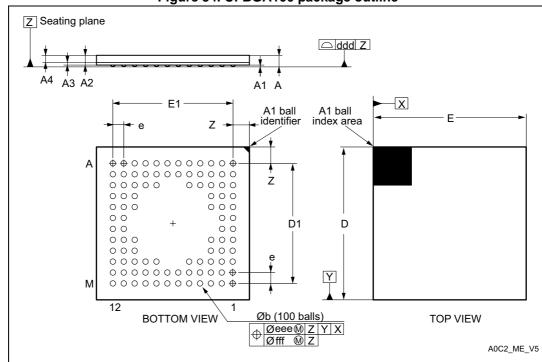

# 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 34. UFBGA100 package outline

1. Drawing is not to scale.

Table 70. UFBGA100 package mechanical data

| Sumbal |      | millimeters |       |      | inches <sup>(1)</sup> |        |

|--------|------|-------------|-------|------|-----------------------|--------|

| Symbol | Min. | Тур.        | Max.  | Min. | Тур.                  | Max.   |

| Α      | -    | -           | 0.600 | -    | -                     | 0.0236 |

| A1     | -    | -           | 0.110 | -    | -                     | 0.0043 |

| A2     | -    | 0.450       | -     | -    | 0.0177                | -      |

| A3     | -    | 0.130       | -     | -    | 0.0051                | 0.0094 |

| A4     | -    | 0.320       | -     | -    | 0.0126                | -      |

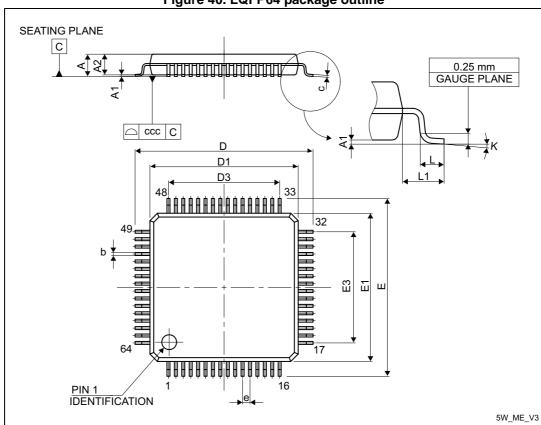

# 7.3 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 40. LQFP64 package outline

1. Drawing is not to scale.

Table 73. LQFP64 package mechanical data

| rabio for Earl of package moonamed data |             |        |       |                       |        |        |

|-----------------------------------------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol                                  | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|                                         | Min         | Тур    | Max   | Min                   | Тур    | Max    |

| Α                                       | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1                                      | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2                                      | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b                                       | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С                                       | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D                                       | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1                                      | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3                                      | -           | 7.500  | -     | -                     | 0.2953 | -      |

| Е                                       | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1                                      | -           | 10.000 | -     | -                     | 0.3937 | -      |

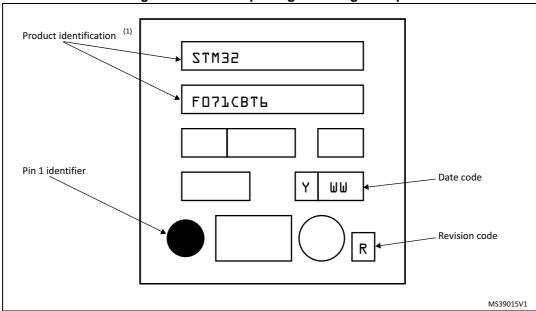

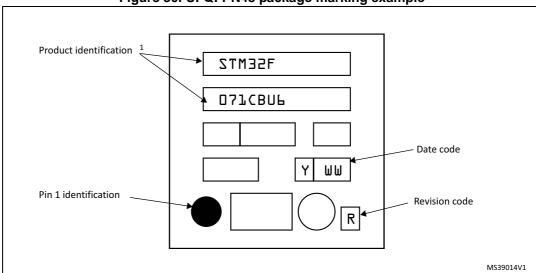

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 47. LQFP48 package marking example

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

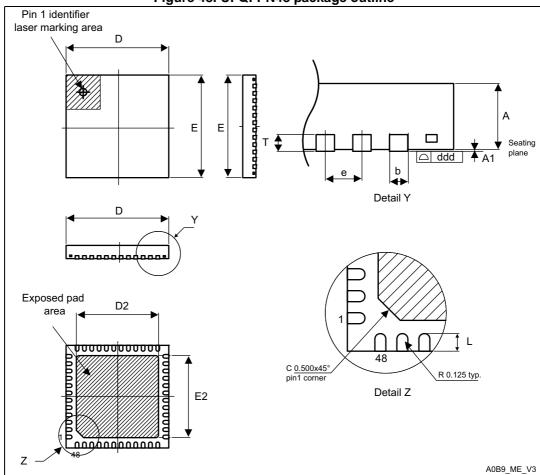

# 7.6 UFQFPN48 package information

UFQFPN48 is a 48-lead, 7x7 mm, 0.5 mm pitch, ultra-thin fine-pitch quad flat package.

Figure 48. UFQFPN48 package outline

- 1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

577

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 50. UFQFPN48 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

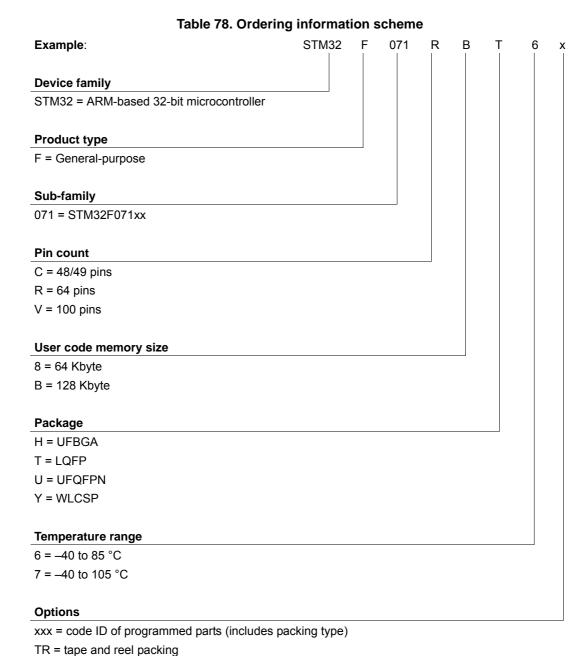

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID025451 Rev 6

blank = tray packing