Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | -                                                                               |

| Core Size                  | -                                                                               |

| Speed                      | -                                                                               |

| Connectivity               | -                                                                               |

| Peripherals                | -                                                                               |

| Number of I/O              | -                                                                               |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | -                                                                               |

| EEPROM Size                | -                                                                               |

| RAM Size                   | -                                                                               |

| Voltage - Supply (Vcc/Vdd) | -                                                                               |

| Data Converters            | -                                                                               |

| Oscillator Type            | -                                                                               |

| Operating Temperature      | -                                                                               |

| Mounting Type              | -                                                                               |

| Package / Case             | -                                                                               |

| Supplier Device Package    | -                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f363a6dfb-u0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

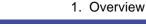

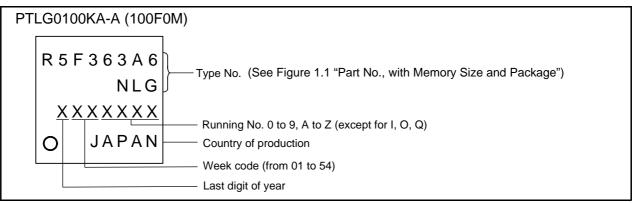

Figure 1.1 Part No., with Memory Size and Package

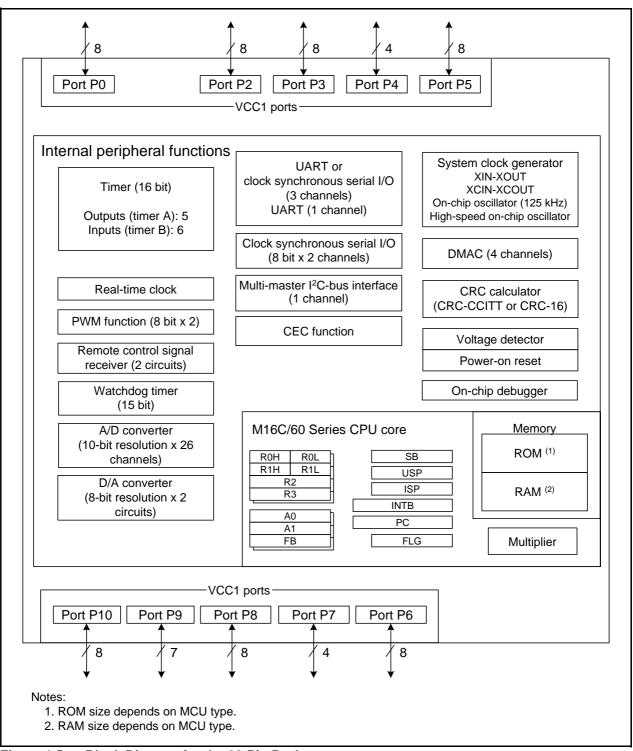

Figure 1.5 Block Diagram for the 80-Pin Package

| Dia Ma  | Control Din | Port |             | I/O Pii     | n for Peripheral Function |                                 |

|---------|-------------|------|-------------|-------------|---------------------------|---------------------------------|

| Pin No. | Control Pin | Port | Interrupt   | Timer       | Serial interface          | A/D converter,<br>D/A converter |

| 1       |             | P9_5 |             |             | CLK4                      | ANEX0                           |

| 2       |             | P9_4 |             | TB4IN/PWM1  |                           | DA1                             |

| 3       |             | P9_3 |             | TB3IN/PWM0  |                           | DA0                             |

| 4       |             | P9_2 |             | TB2IN/PMC0  | SOUT3                     |                                 |

| 5       |             | P9_0 |             | TB0IN       | CLK3                      |                                 |

| 6       | CNVSS       |      |             |             |                           |                                 |

| 7       | XCIN        | P8_7 |             |             |                           |                                 |

| 8       | XCOUT       | P8_6 |             |             |                           |                                 |

| 9       | RESET       |      |             |             |                           |                                 |

| 10      | XOUT        |      |             |             |                           |                                 |

| 11      | VSS         |      |             |             |                           |                                 |

| 12      | XIN         |      |             |             |                           |                                 |

| 13      | VCC1        |      |             |             |                           |                                 |

| 14      |             | P8_5 | NMI         |             | CEC                       |                                 |

| 15      |             | P8_4 | INT2        | ZP          |                           |                                 |

| 16      |             | P8_3 | INT1        |             |                           |                                 |

| 17      |             | P8_2 | <b>INTO</b> |             |                           |                                 |

| 18      |             | P8_1 |             | TA4IN       | CTS5/RTS5                 |                                 |

| 19      |             | P8_0 |             | TA4OUT      | RXD5/SCL5                 |                                 |

| 20      |             | P7_7 |             | TA3IN       | CLK5                      |                                 |

| 21      |             | P7_6 |             | TA3OUT      | TXD5/SDA5                 |                                 |

| 22      |             | P7_1 |             | TA0IN/TB5IN | RXD2/SCL2/SCLMM           |                                 |

| 23      |             | P7_0 |             | TA0OUT      | TXD2/SDA2/SDAMM           |                                 |

| 24      |             | P6_7 |             |             | TXD1/SDA1                 |                                 |

| 25      |             | P6_6 |             |             | RXD1/SCL1                 |                                 |

| 26      |             | P6_5 |             |             | CLK1                      |                                 |

| 27      |             | P6_4 |             |             | CTS1/RTS1/CTS0/           |                                 |

| 28      |             | P6_3 |             |             | CLKS1<br>TXD0/SDA0        |                                 |

| 20      |             | P6_2 |             |             | RXD0/SCL0                 |                                 |

| 30      |             | P6_1 |             |             | CLK0                      |                                 |

| 31      |             | P6_0 |             | TRHO        | CTS0/RTS0                 |                                 |

| 32      | CLKOUT      | P5_7 |             |             | 0100/1100                 |                                 |

| 33      | 0_11001     | P5_6 |             |             |                           |                                 |

| 34      |             | P5_5 |             |             |                           |                                 |

| 35      |             | P5_4 |             |             |                           |                                 |

| 36      |             | P5_3 |             |             |                           |                                 |

| 37      |             | P5_2 |             |             |                           |                                 |

| 38      |             | P5_1 |             |             |                           |                                 |

| 39      |             | P5_0 |             |             |                           |                                 |

| 40      |             | P4_3 |             |             |                           |                                 |

# Table 1.8 Pin Names for the 80-Pin Package (1/2)

#### **Central Processing Unit (CPU)** 2.

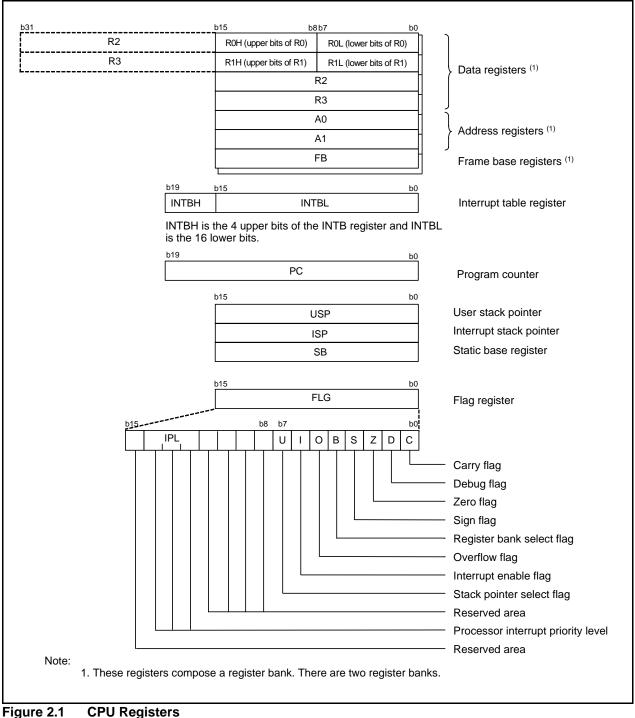

Figure 2.1 shows the CPU registers. Seven registers (R0, R1, R2, R3, A0, A1, and FB) out of 13 compose a register bank, and there are two register banks.

# 2.8.7 Interrupt Enable Flag (I Flag)

The I flag enables maskable interrupts.

Maskable interrupts are disabled when the I flag is 0, and enabled when it is 1. The I flag becomes 0 when an interrupt request is accepted.

# 2.8.8 Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is 0. USP is selected when the U flag is 1. The U flag becomes 0 when a hardware interrupt request is accepted, or the INT instruction of software interrupt number 0 to 31 is executed.

# 2.8.9 Processor Interrupt Priority Level (IPL)

IPL is 3 bits wide and assigns processor interrupt priority levels from 0 to 7. If a requested interrupt has higher priority than IPL, the interrupt request is enabled.

# 2.8.10 Reserved Areas

Only set these bits to 0. The read value is undefined.

# 4. Special Function Registers (SFRs)

# 4.1 SFRs

An SFR is a control register for a peripheral function.

| Address | Register                                      | Symbol   | Reset Value                                                                          |

|---------|-----------------------------------------------|----------|--------------------------------------------------------------------------------------|

| 0000h   |                                               |          |                                                                                      |

| 0001h   |                                               |          |                                                                                      |

| 0002h   |                                               |          |                                                                                      |

| 0003h   |                                               |          |                                                                                      |

| 0004h   | Processor Mode Register 0                     | PM0      | 0000 0000b<br>(CNVSS pin is low)<br>0000 0011b<br>(CNVSS pin is high) <sup>(2)</sup> |

| 0005h   | Processor Mode Register 1                     | PM1      | 0000 1000b                                                                           |

| 0006h   | System Clock Control Register 0               | CM0      | 0100 1000b                                                                           |

| 0007h   | System Clock Control Register 1               | CM1      | 0010 0000b                                                                           |

| 0008h   | Chip Select Control Register                  | CSR      | 01h                                                                                  |

| 0009h   | External Area Recovery Cycle Control Register | EWR      | XXXX XX00b                                                                           |

| 000Ah   | Protect Register                              | PRCR     | 00h                                                                                  |

| 000Bh   | Data Bank Register                            | DBR      | 00h                                                                                  |

| 000Ch   | Oscillation Stop Detection Register           | CM2      | 0X00 0010b <sup>(3)</sup>                                                            |

| 000Dh   |                                               |          |                                                                                      |

| 000Eh   |                                               |          |                                                                                      |

| 000Fh   |                                               |          |                                                                                      |

| 0010h   | Program 2 Area Control Register               | PRG2C    | XXXX XX00b                                                                           |

| 0011h   | External Area Wait Control Expansion Register | EWC      | 00h                                                                                  |

| 0012h   | Peripheral Clock Select Register              | PCLKR    | 0000 0011b                                                                           |

| 0013h   | Sub Clock Division Control Register           | SCM0     | XXXX X000b                                                                           |

| 0014h   |                                               |          |                                                                                      |

| 0015h   | Clock Prescaler Reset Flag                    | CPSRF    | 0XXX XXXXb                                                                           |

| 0016h   | Peripheral Clock Stop Register 1              | PCLKSTP1 | X000 0000b                                                                           |

| 0017h   |                                               |          |                                                                                      |

| 0018h   | Reset Source Determine Register               | RSTFR    | XX00 001Xb<br>(hardware reset) <sup>(4)</sup>                                        |

| 0019h   | Voltage Detector 2 Flag Register              | VCR1     | 0000 1000b <sup>(5)</sup>                                                            |

| 001Ah   | Voltage Detector Operation Enable Register    | VCR2     | 00h (5)                                                                              |

| 001Bh   | Chip Select Expansion Control Register        | CSE      | 00h                                                                                  |

| 001Ch   |                                               |          |                                                                                      |

| 001Dh   |                                               |          |                                                                                      |

| 001Eh   | Processor Mode Register 2                     | PM2      | XX00 0X01b                                                                           |

| 001Fh   |                                               |          |                                                                                      |

Table 4.1SFR Information (1) (1)

X: Undefined

Notes:

- 1. The blank areas are reserved. No access is allowed.

- 2. Software reset, watchdog timer reset, oscillator stop detect reset, voltage monitor 1 reset, and voltage monitor 2 reset do not affect the following bits: bits PM01 and PM00 in the PM0 register.

- 3. Oscillator stop detect reset does not affect bits CM20, CM21, and CM27.

- 4. The state of bits in the RSTFR register depends on the reset type.

- 5. This is the reset value after hardware reset. Refer to the explanation of each register for details.

|         |                                           |          | Description of the |

|---------|-------------------------------------------|----------|--------------------|

| Address | Register                                  | Symbol   | Reset Value        |

| 0240h   |                                           |          |                    |

| 0241h   |                                           |          |                    |

| 0242h   |                                           |          |                    |

| 0243h   |                                           |          |                    |

| 0244h   | UART0 Special Mode Register 4             | U0SMR4   | 00h                |

| 0245h   | UART0 Special Mode Register 3             | U0SMR3   | 000X 0X0Xb         |

| 0246h   | UART0 Special Mode Register 2             | U0SMR2   | X000 0000b         |

| 0247h   | UART0 Special Mode Register               | U0SMR    | X000 0000b         |

| 0248h   | UART0 Transmit/Receive Mode Register      | U0MR     | 00h                |

| 0249h   | UART0 Bit Rate Register                   | U0BRG    | XXh                |

| 024Ah   | UART0 Transmit Buffer Register            | UOTB     | XXh                |

| 024Bh   |                                           | 0015     | XXh                |

| 024Ch   | UART0 Transmit/Receive Control Register 0 | U0C0     | 0000 1000b         |

| 024Dh   | UART0 Transmit/Receive Control Register 1 | U0C1     | 00XX 0010b         |

| 024Eh   | UART0 Receive Buffer Register             | UORB     | XXh                |

| 024Fh   |                                           |          | XXh                |

| 0250h   | UART Transmit/Receive Control Register 2  | UCON     | X000 0000b         |

| 0251h   |                                           |          |                    |

| 0252h   | UART Clock Select Register                | UCLKSEL0 | X0h                |

| 0253h   |                                           |          |                    |

| 0254h   | UART1 Special Mode Register 4             | U1SMR4   | 00h                |

| 0255h   | UART1 Special Mode Register 3             | U1SMR3   | 000X 0X0Xb         |

| 0256h   | UART1 Special Mode Register 2             | U1SMR2   | X000 0000b         |

| 0257h   | UART1 Special Mode Register               | U1SMR    | X000 0000b         |

| 0258h   | UART1 Transmit/Receive Mode Register      | U1MR     | 00h                |

| 0259h   | UART1 Bit Rate Register                   | U1BRG    | XXh                |

| 025Ah   | LIADTA Transmit Duffer Desister           | LIATE    | XXh                |

| 025Bh   | UART1 Transmit Buffer Register            | U1TB     | XXh                |

| 025Ch   | UART1 Transmit/Receive Control Register 0 | U1C0     | 0000 1000b         |

| 025Dh   | UART1 Transmit/Receive Control Register 1 | U1C1     | 00XX 0010b         |

| 025Eh   |                                           | 1400     | XXh                |

| 025Fh   | UART1 Receive Buffer Register             | U1RB     | XXh                |

| 0260h   |                                           |          |                    |

| 0261h   |                                           |          |                    |

| 0262h   |                                           |          |                    |

| 0263h   |                                           |          |                    |

| 0264h   | UART2 Special Mode Register 4             | U2SMR4   | 00h                |

| 0265h   | UART2 Special Mode Register 3             | U2SMR3   | 000X 0X0Xb         |

| 0266h   | UART2 Special Mode Register 2             | U2SMR2   | X000 0000b         |

| 0267h   | UART2 Special Mode Register               | U2SMR    | X000 0000b         |

| 0268h   | UART2 Transmit/Receive Mode Register      | U2MR     | 00h                |

| 0269h   | UART2 Bit Rate Register                   | U2BRG    | XXh                |

| 026Ah   |                                           |          | XXh                |

| 026Bh   | UART2 Transmit Buffer Register            | U2TB     | XXh                |

| 026Ch   | UART2 Transmit/Receive Control Register 0 | U2C0     | 0000 1000b         |

| 026Dh   | UART2 Transmit/Receive Control Register 1 | U2C1     | 0000 0010b         |

| 026Eh   | Ŭ                                         |          | XXh                |

| 026Fh   | UART2 Receive Buffer Register             | U2RB     | XXh                |

|         |                                           |          | Villadofino        |

### Table 4.9SFR Information (9) (1)

X: Undefined

Note:

1. The blank areas are reserved. No access is allowed.

| Address  | Register                              | Symbol  | Reset Value               |

|----------|---------------------------------------|---------|---------------------------|

| 0360h    | Pull-Up Control Register 0            | PUR0    | 00h                       |

| 0361h    | Pull-Up Control Register 1            | PUR1    | 0000 0000b <sup>(2)</sup> |

|          |                                       |         | 0000 0010b                |

| 0362h    | Pull-Up Control Register 2            | PUR2    | 00h                       |

| 0363h    |                                       |         |                           |

| 0364h    |                                       |         |                           |

| 0365h    |                                       |         |                           |

| 0366h    | Port Control Register                 | PCR     | 0000 0XX0b                |

| 0367h    |                                       |         |                           |

| 0368h    |                                       |         |                           |

| 0369h    | NMI/SD Digital Filter Register        | NMIDF   | XXXX X000b                |

| 036Ah    |                                       |         |                           |

| 036Bh    |                                       |         |                           |

| 036Ch    |                                       |         |                           |

| 036Dh    |                                       |         |                           |

| 036Eh    |                                       |         |                           |

| 036Fh    |                                       |         |                           |

| 0370h    | PWM Control Register 0                | PWMCON0 | 00h                       |

| 0371h    |                                       |         |                           |

| 0372h    | PWM0 Prescaler                        | PWMPRE0 | 00h                       |

| 0373h    | PWM0 Register                         | PWMREG0 | 00h                       |

| 0374h    | PWM1 Prescaler                        | PWMPRE1 | 00h                       |

| 0375h    | PWM1 Register                         | PWMREG1 | 00h                       |

| 0376h    | PWM Control Register 1                | PWMCON1 | 00h                       |

| 0377h    |                                       |         |                           |

| 0378h    |                                       |         |                           |

| 0379h    |                                       |         |                           |

| 037Ah    |                                       |         |                           |

| 037Bh    |                                       |         |                           |

| 037Ch    | Count Source Protection Mode Register | CSPR    | 00h <sup>(3)</sup>        |

| 037Dh    | Watchdog Timer Refresh Register       | WDTR    | XXh                       |

| 037Eh    | Watchdog Timer Start Register         | WDTS    | XXh                       |

| 037Fh    | Watchdog Timer Control Register       | WDC     | 00XX XXXXb                |

| 0380h to |                                       |         |                           |

| 038Fh    |                                       |         | X: Unde                   |

### Table 4.14SFR Information (14) (1)

Notes:

2. Values after hardware reset, power-on reset, or voltage monitor 0 reset are as follows:

- 00000000b when a low-level signal is input to the CNVSS pin

- 00000010b when a high-level signal is input to the CNVSS pin

Values after voltage monitor 1 reset, voltage monitor 2 reset, software reset, watchdog timer reset, or oscillation stop detect reset are as follows:

- 00000000b when bits PM01 and PM00 in the PM0 register are 00b (single-chip mode).

- 00000010b when bits PM01 and PM00 in the PM0 register are 01b (memory expansion mode) or 11b (microprocessor mode).

3. When the CSPROINI bit in the OFS1 address is 0, the reset value is 1000 0000b.

<sup>1.</sup> The blank areas are reserved. No access is allowed.

# 5.1.2 Recommended Operating Conditions

# Table 5.2 Recommended Operating Conditions (1/4)

$V_{CC1} = V_{CC2} = 1.8$  to 5.5 V at  $T_{opr} = -20^{\circ}$ C to  $85^{\circ}$ C/-40°C to  $85^{\circ}$ C unless otherwise specified.

| Symbol           | Parameter                                         |                                                                                                            |                                                             |                      | Standard         | ł                    | Unit |

|------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|------------------|----------------------|------|

| Symbol           |                                                   | Faranteler                                                                                                 |                                                             | Min.                 | Тур.             | Max.                 | Unit |

| V <sub>CC1</sub> | Supply                                            |                                                                                                            |                                                             |                      |                  | 5.5                  | V    |

|                  | voltage                                           | CEC function is not used ( $V_{CC1} = V_{C0}$                                                              | C2)                                                         | 1.8                  |                  | 5.5                  | V    |

|                  |                                                   | CEC function is used                                                                                       |                                                             | 2.7                  |                  | 3.63                 | V    |

| V <sub>CC2</sub> | Supply volt                                       | age                                                                                                        | $V_{CC1} \ge 2.7$                                           | 2.7                  |                  | V <sub>CC1</sub>     | V    |

|                  |                                                   |                                                                                                            | V <sub>CC1</sub> < 2.7                                      |                      | V <sub>CC1</sub> |                      | V    |

| AV <sub>CC</sub> | Analog sup                                        | ply voltage                                                                                                |                                                             |                      | V <sub>CC1</sub> |                      | V    |

| V <sub>SS</sub>  | Supply volt                                       | age                                                                                                        |                                                             |                      | 0                |                      | V    |

| AV <sub>SS</sub> | Analog sup                                        | ply voltage                                                                                                |                                                             |                      | 0                |                      | V    |

| VIH              | High input                                        | P3_1 to P3_7, P4_0 to P4_7,<br>P5_0 to P5_7                                                                | $2.7 \text{ V} \le \text{V}_{CC1} \le 5.5 \text{ V}$        | 0.8V <sub>CC2</sub>  |                  | V <sub>CC2</sub>     | V    |

|                  | voltage                                           |                                                                                                            | $1.8 \text{ V} \le \text{V}_{\text{CC1}} < 2.7 \text{ V}$   | 0.85V <sub>CC2</sub> |                  | V <sub>CC2</sub>     | V    |

|                  | <br> | P0_0 to P0_7, P1_0 to P1_7,<br>P2_0 to P2_7, P3_0<br>(in single-chip mode)                                 | $2.7 \text{ V} \le \text{V}_{CC1} \le 5.5 \text{ V}$        | 0.8V <sub>CC2</sub>  |                  | V <sub>CC2</sub>     | V    |

|                  |                                                   |                                                                                                            | $1.8 \text{ V} \le \text{V}_{\text{CC1}} < 2.7 \text{ V}$   | 0.85V <sub>CC2</sub> |                  | V <sub>CC2</sub>     | V    |

|                  |                                                   | P0_0 to P0_7, P1_0 to P1_7,                                                                                | $2.7~\text{V} \leq \text{V}_{\text{CC1}} \leq 5.5~\text{V}$ | 0.5V <sub>CC2</sub>  |                  | V <sub>CC2</sub>     | V    |

|                  |                                                   | P2_0 to P2_7, P3_0<br>(data input in memory expansion<br>and microprocessor modes)                         | $1.8 \text{ V} \le \text{V}_{\text{CC1}} < 2.7 \text{ V}$   | 0.55V <sub>CC2</sub> |                  | V <sub>CC2</sub>     | V    |

|                  |                                                   | P6_0 to P6_7, P7_2 to P7_7,                                                                                | $2.7 \text{ V} \le \text{V}_{\text{CC1}} \le 5.5 \text{ V}$ | 0.8V <sub>CC1</sub>  |                  | V <sub>CC1</sub>     | V    |

|                  |                                                   | P8_0 to P8_4, P8_6, P8_7, P9_0<br>to P9_7, P10_0 to P10_7,<br>XIN, RESET, CNVSS, BYTE                      | $1.8 \text{ V} \le \text{V}_{\text{CC1}} < 2.7 \text{ V}$   | 0.85V <sub>CC1</sub> |                  | V <sub>CC1</sub>     | V    |

|                  |                                                   | P7_0, P7_1, P8_5                                                                                           | $2.7~V \leq V_{CC1} \leq 5.5~V$                             | 0.8V <sub>CC1</sub>  |                  | 6.5                  | V    |

|                  |                                                   |                                                                                                            | $1.8 \text{ V} \le \text{V}_{\text{CC1}} < 2.7 \text{ V}$   | 0.85V <sub>CC1</sub> |                  | 6.5                  | V    |

|                  |                                                   | CEC                                                                                                        |                                                             | 0.7V <sub>CC1</sub>  |                  |                      | V    |

| V <sub>IL</sub>  | Low input                                         | P3_1 to P3_7, P4_0 to P4_7, P5_0                                                                           | ) to P5_7                                                   | 0                    |                  | 0.2V <sub>CC2</sub>  | V    |

|                  | voltage                                           | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(in single-chip mode)                                    |                                                             | 0                    |                  | 0.2V <sub>CC2</sub>  | V    |

|                  |                                                   | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input in memory expansion and microprocessor mode) |                                                             | 0                    |                  | 0.16V <sub>CC2</sub> | V    |

|                  |                                                   | P6_0 to P6_7, P7_0 to P7_7, P8_0<br>P10_0 to P10_7<br>XIN, RESET, CNVSS, BYTE                              | 0 to P8_7, P9_0 to P9_7,                                    | 0                    |                  | 0.2V <sub>CC1</sub>  | V    |

|                  |                                                   | CEC                                                                                                        |                                                             |                      |                  | 0.26V <sub>CC1</sub> | V    |

### Table 5.11 Flash Memory (Data Flash) Electrical Characteristics

$V_{CC1}$  = 2.7 to 5.5 V at  $T_{opr}$  = -20 to 85°C/-40 to 85°C, unless otherwise specified.

| Symbol                 | Parameter                                                              | Conditions                                                      | Standard   |      | ard                         | Unit  |

|------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|------------|------|-----------------------------|-------|

| Symbol                 | Falameter                                                              | Conditions                                                      | Min.       | Тур. | Max.                        | Unit  |

| -                      | Program and erase cycles <sup>(1), (3), (4)</sup>                      | $V_{CC1} = 3.3 \text{ V}, \text{ T}_{opr} = 25^{\circ}\text{C}$ | 10,000 (2) |      |                             | times |

| -                      | 2 word program time                                                    | $V_{CC1} = 3.3 \text{ V}, \text{ T}_{opr} = 25^{\circ}\text{C}$ |            | 300  | 4000                        | μS    |

| -                      | Lock bit program time                                                  | $V_{CC1} = 3.3 \text{ V}, \text{ T}_{opr} = 25^{\circ}\text{C}$ |            | 140  | 3000                        | μS    |

| -                      | Block erase time                                                       | V <sub>CC1</sub> = 3.3 V, T <sub>opr</sub> = 25°C               |            | 0.2  | 3.0                         | S     |

| t <sub>d(SR-SUS)</sub> | Time delay from suspend request until suspend                          |                                                                 |            |      | $5 + \frac{3}{f(BCLK)}$     | ms    |

| -                      | Interval from erase start/restart until following suspend request      |                                                                 | 0          |      |                             | μs    |

| -                      | Suspend interval necessary for auto-erasure to complete <sup>(7)</sup> |                                                                 | 20         |      |                             | ms    |

| -                      | Time from suspend until erase restart                                  |                                                                 |            |      | $30 + \frac{1}{f_{(BCLK)}}$ | μs    |

| -                      | Program, erase voltage                                                 |                                                                 | 2.7        |      | 5.5                         | V     |

| -                      | Read voltage                                                           |                                                                 | 2.7        |      | 5.5                         | V     |

| -                      | Program, erase temperature                                             |                                                                 | -20/-40    |      | 85                          | °C    |

| t <sub>PS</sub>        | Flash memory circuit stabilization wa                                  | ait time                                                        |            |      | 50                          | μS    |

| -                      | Data hold time <sup>(6)</sup>                                          | Ambient temperature = 55°C                                      | 20         |      |                             | year  |

Notes:

1. Definition of program and erase cycles

The program and erase cycles refer to the number of per-block erasures.

If the program and erase cycles are n (n = 10,000), each block can be erased n times.

For example, if a 4 KB block is erased after writing 2 word data 1,024 times, each to a different address, this counts as one program and erase cycles. Data cannot be written to the same address more than once without erasing the block (rewrite prohibited).

2. Cycles to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 3. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 256 groups before erasing them all in one operation. In addition, averaging the erasure cycles between blocks A and B can further reduce the actual erasure cycles. It is also advisable to retain data on the erasure cycles of each block and limit the number of erase operations to a certain number.

- 4. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 5. Customers desiring program/erase failure rate information should contact a Renesas Electronics sales office.

6. The data hold time includes time that the power supply is off or the clock is not supplied.

7. After an erase start or erase restart, if an interval of at least 20 ms is not set before the next suspend request, the erase sequence cannot be completed.

### Table 5.14 Voltage Detector 2 Electrical Characteristics

The measurement condition is  $V_{CC1}$  = 1.8 to 5.5 V,  $T_{opr}$  = -20°C to 85°C/-40°C to 85°C, unless otherwise specified.

| Symbol              | Parameter                                                                | Condition                                                    |      | Unit |      |      |

|---------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| Symbol              | i arameter                                                               | Condition                                                    | Min. | Тур. | Max. | Onit |

| V <sub>det2</sub>   | Voltage detection level Vdet2_0                                          | When V <sub>CC1</sub> is falling                             | 3.70 | 4.00 | 4.30 | V    |

| -                   | Hysteresis width at the rising of V <sub>CC1</sub> in voltage detector 2 |                                                              |      | 0.15 |      | V    |

| -                   | Voltage detector 2 response time <sup>(2)</sup>                          | When V <sub>CC1</sub> falls from 5<br>V to (Vdet2_0 - 0.1) V |      |      | 200  | μS   |

| -                   | Voltage detector self power consumption                                  | VC27 = 1, V <sub>CC1</sub> = 5.0 V                           |      | 1.7  |      | μΑ   |

| t <sub>d(E-A)</sub> | Waiting time until voltage detector operation starts <sup>(1)</sup>      |                                                              |      |      | 100  | μs   |

Notes:

1. Necessary time until the voltage detector operates after setting to 1 again after setting the VC27 bit in the VCR2 register to 0.

2. Time from when passing the V<sub>det2</sub> until when a voltage monitor 2 reset is generated.

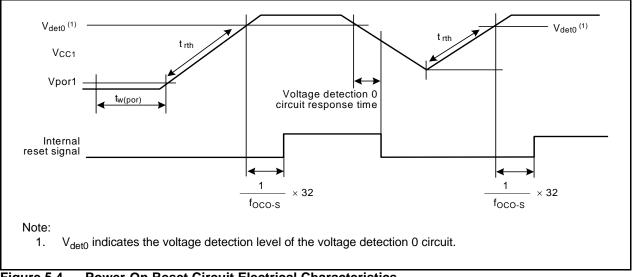

### Table 5.15Power-On Reset Circuit

The measurement condition is  $V_{CC1}$  = 2.0 to 5.5 V,  $T_{opr}$  = -20°C to 85°C/ -40°C to 85°C, unless otherwise specified.

| Symbol              | Parameter                                              | Condition |      | Unit |       |       |

|---------------------|--------------------------------------------------------|-----------|------|------|-------|-------|

|                     | i arameter                                             |           | Min. | Тур. | Max.  | Offic |

| V <sub>por1</sub>   | Voltage at which power-on reset enabled <sup>(1)</sup> |           |      |      | 0.5   | V     |

| t <sub>rth</sub>    | External power V <sub>CC1</sub> rise gradient          |           | 2.0  |      | 50000 | mV/ms |

| t <sub>w(por)</sub> | Time necessary to enable power-on reset                |           | 300  |      |       | ms    |

Note: 1.

To use the power-on reset function, enable voltage monitor 0 reset by setting the LVDAS bit in the OFS1 address to 0. Also, set the VDSEL1 bit to 0 (Vdet0\_2).

Figure 5.4 Power-On Reset Circuit Electrical Characteristics

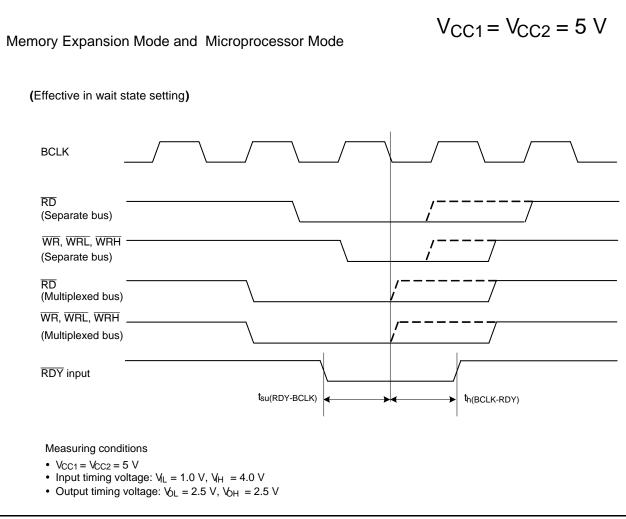

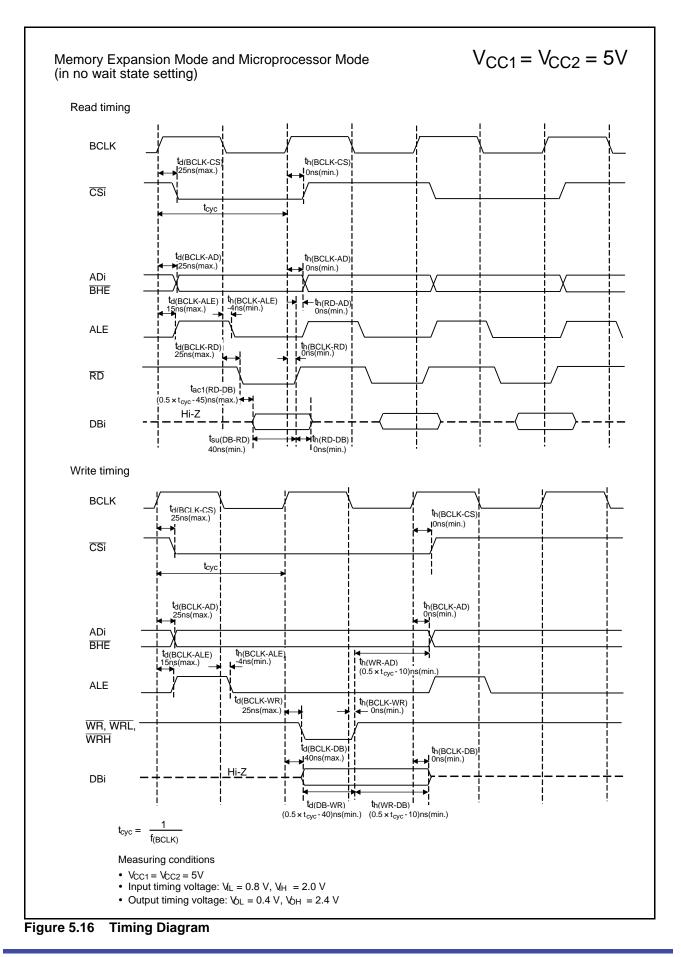

Figure 5.14 Timing Diagram

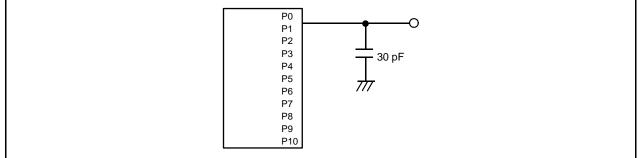

Figure 5.15 Ports P0 to P10 Measurement Circuit

RENESAS

$V_{CC1} = V_{CC2} = 3 V$

### **Switching Characteristics**

(V<sub>CC1</sub> = V<sub>CC2</sub> = 3 V, V<sub>SS</sub> = 0 V, at T<sub>opr</sub> = -20°C to  $85^{\circ}$ C/-40°C to  $85^{\circ}$ C unless otherwise specified)

# 5.3.4.4 In Wait State Setting $2\phi + 3\phi$ , $2\phi + 4\phi$ , $3\phi + 4\phi$ , and $4\phi + 5\phi$ , and When Accessing External Area

# Table 5.60Memory Expansion and Microprocessor Modes (in Wait State Setting $2\phi + 3\phi$ , $2\phi + 4\phi$ ,<br/> $3\phi + 4\phi$ , and $4\phi + 5\phi$ , and When Accessing External Area)

| Symbol                    | Parameter                                                  | Measuring   | Stan     | Unit      |    |

|---------------------------|------------------------------------------------------------|-------------|----------|-----------|----|

| Symbol                    | Palameter                                                  | Condition   | Min.     | Min. Max. |    |

| t <sub>d(BCLK-AD)</sub>   | Address output delay time                                  |             |          | 30        | ns |

| t <sub>h(BCLK-AD</sub> )  | Address output hold time (in relation to BCLK)             |             | 0        |           | ns |

| t <sub>h(RD-AD</sub> )    | Address output hold time (in relation to RD)               |             | 0        |           | ns |

| t <sub>h(WR-AD)</sub>     | Address output hold time (in relation to WR)               |             | (Note 2) |           | ns |

| t <sub>d(BCLK-CS)</sub>   | Chip select output delay time                              |             |          | 30        | ns |

| t <sub>h(BCLK-CS)</sub>   | Chip select output hold time (in relation to BCLK)         |             | 0        |           | ns |

| t <sub>d(BCLK-ALE)</sub>  | ALE signal output delay time                               |             |          | 25        | ns |

| t <sub>h(BCLK-ALE</sub> ) | ALE signal output hold time                                | See         | -4       |           | ns |

| t <sub>d(BCLK-RD)</sub>   | RD signal output delay time                                | Figure 5.30 |          | 30        | ns |

| t <sub>h(BCLK-RD)</sub>   | RD signal output hold time                                 |             | 0        |           | ns |

| t <sub>d(BCLK-WR)</sub>   | WR signal output delay time                                |             |          | 30        | ns |

| t <sub>h(BCLK-WR)</sub>   | WR signal output hold time                                 |             | 0        |           | ns |

| t <sub>d(BCLK-DB)</sub>   | Data output delay time (in relation to BCLK)               |             |          | 40        | ns |

| t <sub>h(BCLK-DB)</sub>   | Data output hold time (in relation to BCLK) <sup>(3)</sup> |             | 0        |           | ns |

| t <sub>d(DB-WR)</sub>     | Data output delay time (in relation to WR)                 |             | (Note 1) |           | ns |

| t <sub>h(WR-DB)</sub>     | Data output hold time (in relation to WR) (3)              |             | (Note 2) |           | ns |

Notes:

1. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)\times 10^9}{f_{(BCLK)}} - 40[ns] \qquad \text{n is 3 for } 2\phi + 3\phi, 4 \text{ for } 2\phi + 4\phi, 4 \text{ for } 3\phi + 4\phi, \text{ and 5 for } 4\phi + 5\phi.$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f_{(BCLK)}} - 10[ns]$$

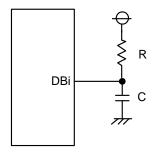

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pullup (pull-down) resistance value. Hold time of data bus is expressed in  $t = -CR \times \ln(1 - V_{OL}/V_{CC2})$ by a circuit of the right figure. For example, when  $V_{OL} = 0.2V_{CC2}$ , C = 30 pF, R = 1 k $\Omega$ , hold time of output low level is t = -30 pF  $\times$  1 k $\Omega \times \ln(1 - 0.2V_{CC2}/V_{CC2})$ = 6.7 ns.

# $V_{CC1} = V_{CC2} = 1.8 V$

### **Timing Requirements**

$(V_{CC1} = V_{CC2} = 1.8 \text{ V}, V_{SS} = 0 \text{ V}, \text{ at } T_{opr} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}/-40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise specified})$

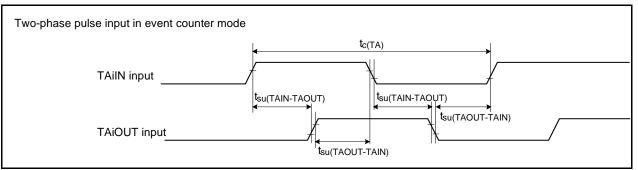

| Table 5.71 | Timer A Input | (Two-Phase Pulse Input | in Event Counter Mode) |

|------------|---------------|------------------------|------------------------|

|            |               |                        |                        |

| Symbol                      | Parameter               | Stan | Unit |      |

|-----------------------------|-------------------------|------|------|------|

|                             |                         | Min. | Max. | Onit |

| t <sub>c(TA)</sub>          | TAiIN input cycle time  | 3    |      | μS   |

| t <sub>su(TAIN-TAOUT)</sub> | TAiOUT input setup time | 800  |      | ns   |

| t <sub>su(TAOUT-TAIN)</sub> | TAilN input setup time  | 800  |      | ns   |

Figure 5.39 Timer A Input (Two-Phase Pulse Input in Event Counter Mode)

# $V_{CC1} = V_{CC2} = 1.8 V$

### **Timing Requirements**

$(V_{CC1} = V_{CC2} = 1.8 \text{ V}, V_{SS} = 0 \text{ V}, \text{ at } T_{opr} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}/-40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise specified})$

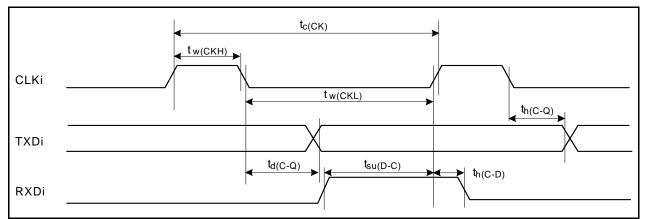

# 5.4.2.5 Serial Interface

### Table 5.75Serial Interface

| Symbol               | Parameter                   | Standard |      | Unit  |

|----------------------|-----------------------------|----------|------|-------|

|                      |                             | Min.     | Max. | Offic |

| t <sub>c(CK)</sub>   | CLKi input cycle time       | 800      |      | ns    |

| t <sub>w(CKH)</sub>  | CLKi input high pulse width | 400      |      | ns    |

| t <sub>w(CKL)</sub>  | CLKi input low pulse width  | 400      |      | ns    |

| t <sub>d(C-Q)</sub>  | TXDi output delay time      |          | 240  | ns    |

| t <sub>h(C-Q)</sub>  | TXDi hold time              | 0        |      | ns    |

| t <sub>su(D-C)</sub> | RXDi input setup time       | 200      |      | ns    |

| t <sub>h(C-D)</sub>  | RXDi input hold time        | 90       |      | ns    |

### Figure 5.41 Serial Interface

# 5.4.2.6 External Interrupt INTi Input

### Table 5.76 External Interrupt INTi Input

| Symbol              | Parameter                   | Standard |      | Unit |

|---------------------|-----------------------------|----------|------|------|

|                     |                             | Min.     | Max. | Onit |

| t <sub>w(INH)</sub> | INTi input high pulse width | 1000     |      | ns   |

| t <sub>w(INL)</sub> | INTi input low pulse width  | 1000     |      | ns   |

| tr(INT)             | INTi input rising time      |          | 100  | μs   |

| tf(INT)             | INTi input falling time     |          | 100  | μs   |

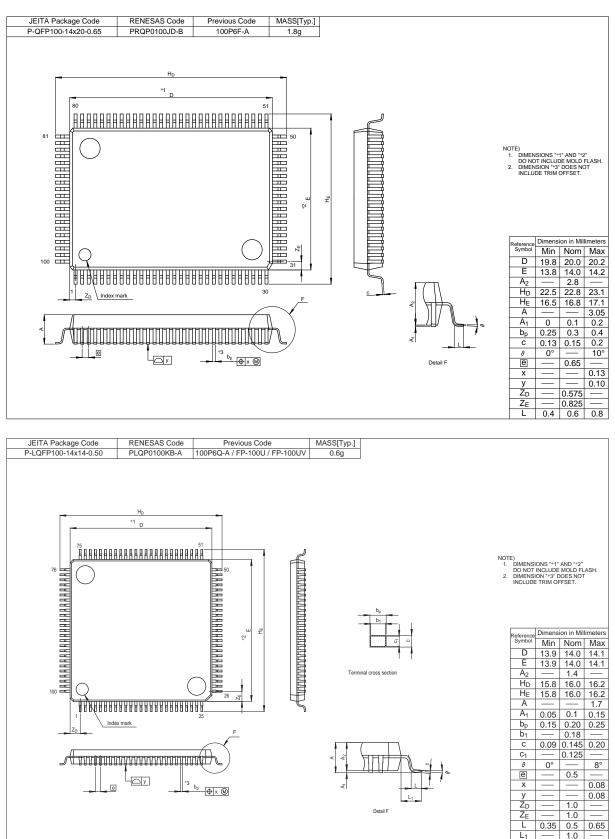

# **Appendix 1. Package Dimensions**

The information on the latest package dimensions or packaging may be obtained from "Packages" on the Renesas Electronics website.

# REVISION HISTORY

# M16C/63 Group Datasheet

|       |                                   |                     | Description                                                                                                  |  |  |  |  |

|-------|-----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Rev.  | Date                              | Page                | Summary                                                                                                      |  |  |  |  |

| 0.30  | Jul 15, 2009                      | -                   | First Edition issued.                                                                                        |  |  |  |  |

| 0.40  | Aug 18, 2009                      | 3                   | Table 1.2 "Specifications for the 100-Pin Package (2/2)" partially modified                                  |  |  |  |  |

| 01.10 | ,                                 | 6                   | Table 1.5 "Product List" partially modified                                                                  |  |  |  |  |

|       |                                   | 7                   | Figure 1.1 "Part No., with Memory Size and Package" partially modified                                       |  |  |  |  |

|       |                                   | 12                  | Figure 1.7 "Pin Assignment for the 100-Pin Package" added                                                    |  |  |  |  |

|       |                                   | 13                  | Table 1.6 "Pin Names for the 100-Pin Package (1/2)" partially modified                                       |  |  |  |  |

|       |                                   | 14                  | Table 1.7 "Pin Names for the 100-Pin Package (2/2)" partially modified                                       |  |  |  |  |

|       |                                   | 107                 | Table 5.65 "External Clock Input (XIN Input)" partially modified                                             |  |  |  |  |

|       |                                   | 112                 | Appendix 1. "Package Dimensions" PTLG0100KA-A added                                                          |  |  |  |  |

| 0.41  | Aug 25, 2009                      | 6                   | Table 1.5 "Product List" Part No. partially modified                                                         |  |  |  |  |

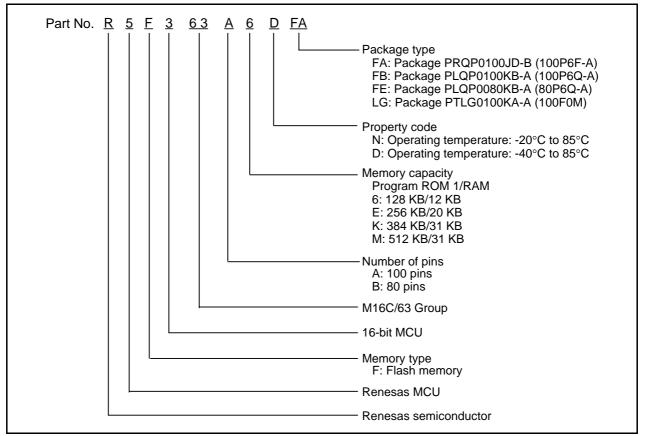

|       |                                   | 7                   | Figure 1.3 "Marking Diagram (Top View) (2/2)" added                                                          |  |  |  |  |

| 1.00  | Sep 15, 2009                      | 52                  | Table 5.6 "A/D Conversion Characteristics (1/2)" note 3 added                                                |  |  |  |  |

| 2.00  | Feb 07, 2011                      | Overall             | 001Ah Voltage Detector Operation Enable Register: Changed reset value from "000X 0000b".                     |  |  |  |  |

|       |                                   | Overall             | 002Ah Voltage Monitor 0 Control Register: Changed reset value from "1100 XX10b".                             |  |  |  |  |

|       |                                   | Overall             | 002Bh Voltage Monitor 1 Control Register: Changed reset value from "1000 1X10b".                             |  |  |  |  |

|       |                                   | Overall             | 0324h Increment/Decrement Flag: Changed name from Up/Down Flag.                                              |  |  |  |  |

|       |                                   | Overall             | 03DCh D/A Control Register: Changed reset value from "XXXX XX00b".                                           |  |  |  |  |

|       |                                   | Overall             | D08Ah to D08Bh PMC0 Counter Value Register: Deleted.                                                         |  |  |  |  |

|       |                                   | Overall             | D09Eh to D09Fh PMC1 Counter Value Register: Deleted.                                                         |  |  |  |  |

|       |                                   | Overview            |                                                                                                              |  |  |  |  |

|       |                                   | 3, 5                | Table 1.2 and Table 1.4 Specifications for the 100/80-Pin Package: Deleted note 1.                           |  |  |  |  |

|       |                                   | 6                   | Table 1.5 Product List: Changed the development status.                                                      |  |  |  |  |

|       |                                   | 10                  | Table 1.10 Pin Functions for the 100-Pin Package (1/3):                                                      |  |  |  |  |

|       |                                   | 18                  | Changed the descriptions of the HOLD pin.                                                                    |  |  |  |  |

|       |                                   | Address Space       |                                                                                                              |  |  |  |  |

|       |                                   | 27                  | Figure 3.2 Memory Map: Added note 1 and 3 to the reserved areas.                                             |  |  |  |  |

|       |                                   | Special Fund        | tion Registers (SFRs)                                                                                        |  |  |  |  |

|       | 29 Table 4.1 SFR Information (1): |                     |                                                                                                              |  |  |  |  |

|       |                                   |                     | Deleted "the VCR1 register, the VCR2 register" from note 2.                                                  |  |  |  |  |

|       |                                   | 30                  | Deleted notes 5 to 6 and added note 5. Table 4.2 SFR Information (2): Deleted notes 2 to 7 and added note 2. |  |  |  |  |

|       |                                   | 47                  |                                                                                                              |  |  |  |  |

|       |                                   |                     | 4.2.1 Register Settings: Added the description regarding read-modify-write instructions.                     |  |  |  |  |

|       |                                   | 48<br>Electrical Ch | Table 4.20 Read-Modify-Write Instructions: Added. aracteristics                                              |  |  |  |  |

|       |                                   |                     | Table 5.1 Absolute Maximum Ratings:                                                                          |  |  |  |  |

|       |                                   | 49                  | Divide a row for T <sub>opr</sub> (Flash program erase) into Program area and Data area.                     |  |  |  |  |

|       |                                   | 50                  | Table 5.2 Recommended Operating Conditions (1/4):                                                            |  |  |  |  |

|       |                                   | 50                  | Added rows for the CEC value to $V_{CC1}$ , $V_{IH}$ , and $V_{IL}$ .                                        |  |  |  |  |

|       |                                   | 56                  | Table 5.9 CPU Clock When Operating Flash Memory (f <sub>(BCLK)</sub> ): Added note 3.                        |  |  |  |  |

|       |                                   | 56                  | Table 5.10 Flash Memory (Program ROM 1, 2) Electrical Characteristics:                                       |  |  |  |  |

|       |                                   | 50                  | Added a condition to the Read voltage row.                                                                   |  |  |  |  |

|       |                                   | 59                  | Table 5.15 Power-On Reset Circuit:                                                                           |  |  |  |  |

|       |                                   |                     | <ul> <li>Changed the maximum value for V<sub>por1</sub> from 0.1.</li> </ul>                                 |  |  |  |  |

|       |                                   |                     | • Added the t <sub>w(por)</sub> row.                                                                         |  |  |  |  |

|       |                                   |                     | Added the last line in note 1.                                                                               |  |  |  |  |

|       |                                   | 59                  | Figure 5.4 Power-On Reset Circuit Electrical Characteristics: Deleted note 2.                                |  |  |  |  |

|       |                                   | 61                  | Table 5.17 40 MHz On-Chip Oscillator Electrical Characteristics: Deleted note 1.                             |  |  |  |  |

|       |                                   | 63                  | Table 5.20 Electrical Characteristics (2): Added "ZP, IDU, IDV, IDW" to the $V_{T+} - V_{T-}$ row.           |  |  |  |  |

|       |                                   | 70, 91, 113         | 5.2.2.7, 5.3.2.7, and 5.4.2.7 Multi-master I <sup>2</sup> C-bus: Added.                                      |  |  |  |  |

|       |                                   | 71                  | Table 5.35 Memory Expansion Mode and Microprocessor Mode:                                                    |  |  |  |  |

|       |                                   |                     | Changed RDY input setup time from 30.                                                                        |  |  |  |  |

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.