Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l063c8t6 |

Contents STM32L063x8

# **Contents**

| 1 | Intro | duction                                                  | . 8  |

|---|-------|----------------------------------------------------------|------|

| 2 | Desc  | ription                                                  | . 9  |

|   | 2.1   | Device overview                                          | 10   |

|   | 2.2   | Ultra-low-power device continuum                         | 12   |

| 3 | Func  | tional overview                                          | 13   |

|   | 3.1   | Low-power modes                                          | 13   |

|   | 3.2   | Interconnect matrix                                      | 18   |

|   | 3.3   | ARM® Cortex®-M0+ core with MPU                           | 19   |

|   | 3.4   | Reset and supply management                              | 20   |

|   |       | 3.4.1 Power supply schemes                               | . 20 |

|   |       | 3.4.2 Power supply supervisor                            | . 20 |

|   |       | 3.4.3 Voltage regulator                                  | . 21 |

|   | 3.5   | Clock management                                         | 21   |

|   | 3.6   | Low-power real-time clock and backup registers           | 25   |

|   | 3.7   | General-purpose inputs/outputs (GPIOs)                   | 25   |

|   | 3.8   | Memories                                                 | 26   |

|   | 3.9   | Boot modes                                               | 26   |

|   | 3.10  | Direct memory access (DMA)                               | 27   |

|   | 3.11  | Liquid crystal display (LCD)                             | 27   |

|   | 3.12  | Analog-to-digital converter (ADC)                        | 27   |

|   | 3.13  | Temperature sensor                                       | 28   |

|   |       | 3.13.1 Internal voltage reference (V <sub>REFINT</sub> ) | . 28 |

|   |       | 3.13.2 V <sub>LCD</sub> voltage monitoring               | . 29 |

|   | 3.14  | Digital-to-analog converter (DAC)                        | 29   |

|   | 3.15  | Ultra-low-power comparators and reference voltage        | 29   |

|   | 3.16  | System configuration controller                          | 29   |

|   | 3.17  | Touch sensing controller (TSC)                           | 30   |

|   | 3.18  | AES                                                      | 31   |

|   | 3.19  | Timers and watchdogs                                     | 31   |

|   |       | 3.19.1 General-purpose timers (TIM2, TIM21 and TIM22)    | . 31 |

STM32L063x8 List of figures

# List of figures

| Figure 1.  | STM32L063x8 block diagram                                                 | 11  |

|------------|---------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                | 23  |

| Figure 3.  | STM32L063x8 LQFP64 pinout - 10 x 10 mm                                    | 37  |

| Figure 4.  | STM32L063x8 LQFP48 pinout - 7 x 7 mm                                      | 38  |

| Figure 5.  | Memory map                                                                | 48  |

| Figure 6.  | Pin loading conditions                                                    | 49  |

| Figure 7.  | Pin input voltage                                                         | 49  |

| Figure 8.  | Power supply scheme                                                       | 50  |

| Figure 9.  | Optional LCD power supply scheme                                          | 51  |

| Figure 10. | Current consumption measurement scheme                                    | 51  |

| Figure 11. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from           |     |

| _          | Flash memory, Range 2, HSE, 1WS                                           | 60  |

| Figure 12. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from           |     |

| · ·        | Flash memory, Range 2, HSI16, 1WS                                         | 60  |

| Figure 13. | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Low-power run mode, code running |     |

| Ü          | from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                          | 64  |

| Figure 14. | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled       |     |

| · ·        | and running on LSE Low drive                                              | 65  |

| Figure 15. | IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC disabled,      |     |

| · ·        | all clocks off                                                            | 65  |

| Figure 16. | High-speed external clock source AC timing diagram                        | 71  |

| Figure 17. | Low-speed external clock source AC timing diagram                         |     |

| Figure 18. | HSE oscillator circuit diagram                                            |     |

| Figure 19. | Typical application with a 32.768 kHz crystal                             |     |

| Figure 20. | HSI16 minimum and maximum value versus temperature                        |     |

| Figure 21. | VIH/VIL versus VDD (CMOS I/Os)                                            | 85  |

| Figure 22. | VIH/VIL versus VDD (TTL I/Os)                                             |     |

| Figure 23. | I/O AC characteristics definition                                         | 88  |

| Figure 24. | Recommended NRST pin protection                                           | 89  |

| Figure 25. | ADC accuracy characteristics                                              | 92  |

| Figure 26. | Typical connection diagram using the ADC                                  | 92  |

| Figure 27. | 12-bit buffered/non-buffered DAC                                          |     |

| Figure 28. | SPI timing diagram - slave mode and CPHA = 0                              | 101 |

| Figure 29. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>               | 102 |

| Figure 30. | SPI timing diagram - master mode <sup>(1)</sup>                           | 102 |

| Figure 31. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>   | 104 |

| Figure 32. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>  | 104 |

| Figure 33. | USB timings: definition of data signal rise and fall time                 | 106 |

| Figure 34. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline         |     |

| Figure 35. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint   | 109 |

| Figure 36. | LQFP64 marking example (package top view)                                 |     |

| Figure 37. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline           |     |

| Figure 38. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint     |     |

| Figure 39. | LQFP48 marking example (package top view)                                 |     |

| Figure 40. | Thermal resistance                                                        | 114 |

STM32L063x8 Description

# 2 Description

The ultra-low-power STM32L063x8 microcontrollers incorporate the connectivity power of the universal serial bus (USB 2.0 crystal-less) with the high-performance ARM® Cortex®-M0+ 32-bit RISC core operating at a 32 MHz frequency, a memory protection unit (MPU), high-speed embedded memories (64 Kbytes of Flash program memory, 2 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L063x8 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L063x8 devices offer several analog features, one 12-bit ADC with hardware oversampling, one DAC, two ultra-low-power comparators, AES, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers and one basic timer, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L063x8 devices embed standard and advanced communication interfaces: up to two I2C, two SPIs, one I2S, two USARTs, a low-power UART (LPUART), and a crystal-less USB. The devices offer up to 24 capacitive sensing channels to simply add touch sensing functionality to any application.

The STM32L063x8 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

Finally, their integrated LCD controller has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with contrast independent of the supply voltage.

The ultra-low-power STM32L063x8 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

#### Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB/USART/I2C/LPUART/LPTIMER wakeup events.

### Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Note:

The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode. The LCD is not stopped automatically by entering Stop mode.

14/121 DocID025660 Rev 6

Table 4. Functionalities depending on the working mode (from Run/active down to standby) <sup>(1)</sup>

|                                           |            | Transactive | Low-         | Low-           |                  | Stop                 |   | Standby              |

|-------------------------------------------|------------|-------------|--------------|----------------|------------------|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep       | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Υ          |             | Y            |                |                  |                      |   |                      |

| Flash memory                              | 0          | 0           | 0            | 0              |                  |                      |   |                      |

| RAM                                       | Υ          | Υ           | Y            | Y              | Υ                |                      |   |                      |

| Backup registers                          | Y          | Y           | Y            | Y              | Υ                |                      | Υ |                      |

| EEPROM                                    | 0          | 0           | 0            | 0              |                  |                      |   |                      |

| Brown-out reset (BOR)                     | 0          | 0           | 0            | 0              | 0                | 0                    | 0 | 0                    |

| DMA                                       | 0          | 0           | 0            | 0              |                  |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0           | 0            | 0              | 0                | 0                    | - |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y           | Y            | Y              | Υ                | Y                    | Υ | Υ                    |

| High Speed<br>Internal (HSI)              | 0          | 0           |              |                | (2)              |                      |   |                      |

| High Speed<br>External (HSE)              | 0          | 0           | 0            | 0              |                  |                      |   |                      |

| Low Speed Internal (LSI)                  | 0          | 0           | 0            | 0              | 0                |                      | 0 |                      |

| Low Speed<br>External (LSE)               | 0          | 0           | 0            | 0              | 0                |                      | 0 |                      |

| Multi-Speed<br>Internal (MSI)             | 0          | 0           | Υ            | Y              |                  |                      |   |                      |

| Inter-Connect<br>Controller               | Y          | Y           | Y            | Y              | Υ                |                      |   |                      |

| RTC                                       | 0          | 0           | 0            | 0              | 0                | 0                    | 0 |                      |

| RTC Tamper                                | 0          | 0           | 0            | 0              | 0                | 0                    | 0 | 0                    |

| Auto WakeUp<br>(AWU)                      | 0          | 0           | 0            | 0              | 0                | 0                    | 0 | 0                    |

| LCD                                       | 0          | 0           | 0            | 0              | 0                |                      |   |                      |

| USB                                       | 0          | 0           |              |                |                  | 0                    |   |                      |

| USART                                     | 0          | 0           | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |

| LPUART                                    | 0          | 0           | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |

| SPI                                       | 0          | 0           | 0            | 0              |                  |                      |   |                      |

| I2C                                       | 0          | 0           | 0            | 0              | O <sup>(4)</sup> | 0                    |   |                      |

| ADC                                       | 0          | 0           |              |                |                  |                      |   |                      |

STM32L063x8 Functional overview

# 3.3 ARM® Cortex®-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L063x8 are compatible with all ARM tools and software.

## **Nested vectored interrupt controller (NVIC)**

The ultra-low-power STM32L063x8 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- · provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

#### Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

## • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled. Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

22/121 DocID025660 Rev 6

#### 3.8 **Memories**

The STM32L063x8 devices have the following features:

8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

- The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the nonvolatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

#### **Boot modes** 3.9

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32™ microcontroller system memory boot mode AN2606 for details.

26/121 DocID025660 Rev 6

Table 11. STM32L063x8 I<sup>2</sup>C implementation (continued)

| I2C features <sup>(1)</sup> | I2C1 | I2C2 |

|-----------------------------|------|------|

| SMBus                       | Х    | -    |

| Wakeup from STOP            | Х    | -    |

<sup>1.</sup> X = supported.

# 3.20.2 Universal synchronous/asynchronous receiver transmitter (USART)

The two USART interfaces (USART1, USART2) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. They also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

Table 12 for the supported modes and features of USART interfaces.

Table 12. USART implementation

| USART modes/features <sup>(1)</sup>         | USART1 and USART2 |

|---------------------------------------------|-------------------|

| Hardware flow control for modem             | X                 |

| Continuous communication using DMA          | Х                 |

| Multiprocessor communication                | Х                 |

| Synchronous mode <sup>(2)</sup>             | X                 |

| Smartcard mode                              | Х                 |

| Single-wire half-duplex communication       | Х                 |

| IrDA SIR ENDEC block                        | X                 |

| LIN mode                                    | Х                 |

| Dual clock domain and wakeup from Stop mode | Х                 |

| Receiver timeout interrupt                  | X                 |

| Modbus communication                        | X                 |

| Auto baud rate detection (4 modes)          | Х                 |

| Driver Enable                               | X                 |

<sup>1.</sup> X = supported.

# 3.20.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire

34/121 DocID025660 Rev 6

<sup>2.</sup> See Table 15: STM32L063x8 pin definitions for the list of I/Os that feature Fast Mode Plus capability

<sup>2.</sup> This mode allows using the USART as an SPI master.

STM32L063x8 Pin descriptions

Table 15. STM32L063x8 pin definitions (continued)

| Р      |           |                                    |          |               |       | pin definitions (continu                                                                            | ,                               |

|--------|-----------|------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------|---------------------------------|

| LQFP48 | LQFP64 ag | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                 | Additional functions            |

| 18     | 26        | PB0                                | I/O      | FT            | -     | EVENTOUT, LCD_SEG5,<br>TSC_G3_IO2                                                                   | LCD_VLCD3, ADC_IN8,<br>VREF_OUT |

| 19     | 27        | PB1                                | I/O      | FT            | -     | LCD_SEG6,<br>TSC_G3_IO3,<br>LPUART1_RTS_DE                                                          | ADC_IN9, VREF_OUT               |

| 20     | 28        | PB2                                | I/O      | FT            | -     | LPTIM1_OUT,<br>TSC_G3_IO4                                                                           | LCD_VLCD1                       |

| 21     | 29        | PB10                               | I/O      | FT            | -     | LCD_SEG10, TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX,<br>SPI2_SCK, I2C2_SCL                              | -                               |

| 22     | 30        | PB11                               | I/O      | FT            | i     | EVENTOUT,<br>LCD_SEG11, TIM2_CH4,<br>TSC_G6_IO1,<br>LPUART1_RX, I2C2_SDA                            | -                               |

| 23     | 31        | VSS                                | S        |               | -     | -                                                                                                   | -                               |

| 24     | 32        | VDD                                | S        |               | -     | -                                                                                                   | -                               |

| 25     | 33        | PB12                               | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LCD_SEG12,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA, EVENTOUT            | LCD_VLCD2                       |

| 26     | 34        | PB13                               | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>LCD_SEG13,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL, TIM21_CH1               | -                               |

| 27     | 35        | PB14                               | I/O      | FTf           | -     | SPI2_MISO/I2S2_MCK,<br>LCD_SEG14, RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA, TIM21_CH2 | -                               |

| 28     | 36        | PB15                               | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>LCD_SEG15,<br>RTC_REFIN                                                       | -                               |

| -      | 37        | PC6                                | I/O      | FT            | -     | TIM22_CH1,<br>LCD_SEG24,<br>TSC_G8_IO1                                                              | -                               |

# 6.1.7 Optional LCD power supply scheme

Figure 9. Optional LCD power supply scheme

- 1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

- Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

# 6.1.8 Current consumption measurement

N × 100 nF + 1 × 10 μF NxVSS

Figure 10. Current consumption measurement scheme

| Symbol            | Parameter          | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|--------------------|-------------------------------------------|------|------|------|------|

| V                 | PVD threshold 6    | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

| V <sub>PVD6</sub> | PVD tillesiloid o  | Rising edge                               | 3.08 | 3.15 | 3.20 | V    |

|                   |                    | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 25. Embedded reset and power control block characteristics (continued)

# 6.3.3 Embedded internal reference voltage

The parameters given in *Table 27* are based on characterization results, unless otherwise specified.

Table 26. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

Table 27. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                                 | Parameter                                                             | Conditions                                                     | Min   | Тур   | Max   | Unit   |

|----------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup> | Internal reference voltage                                            | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                   | Internal reference startup time                                       | -                                                              | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                 | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure   | -                                                              | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                 | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup> | Including uncertainties due to ADC and V <sub>DDA</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>      | Temperature coefficient                                               | -40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>      | Long-term stability                                                   | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>    | Voltage coefficient                                                   | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> (4)(5)          | ADC sampling time when reading the internal reference voltage         | -                                                              | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>    | Startup time of reference voltage buffer for ADC                      | -                                                              | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>    | Consumption of reference voltage buffer for ADC                       | -                                                              | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>   | VREF_OUT output current <sup>(6)</sup>                                | -                                                              | -     | -     | 1     | μΑ     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>   | VREF_OUT output load                                                  | -                                                              | -     | -     | 50    | pF     |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

Electrical characteristics STM32L063x8

Table 36. Typical and maximum current consumptions in Standby mode

| Symbol          | Parameter                      | Conditi                                 | Тур                                        | Max <sup>(1)</sup> | Unit |           |

|-----------------|--------------------------------|-----------------------------------------|--------------------------------------------|--------------------|------|-----------|

|                 |                                |                                         | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 1.3                | 1.7  |           |

|                 |                                |                                         | T <sub>A</sub> = 55 °C                     | -                  | 2.9  |           |

|                 |                                | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C                     | -                  | 3.3  |           |

|                 | Supply current in Standby mode | u 20. 0                                 | T <sub>A</sub> = 105 °C                    | -                  | 4.1  | -<br>- μΑ |

| I <sub>DD</sub> |                                |                                         | T <sub>A</sub> = 125 °C                    | -                  | 8.5  |           |

| (Standby)       |                                | Independent watchdog<br>and LSI off     | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0.29               | 0.6  |           |

|                 |                                |                                         | T <sub>A</sub> = 55 °C                     | 0.32               | 0.9  |           |

|                 |                                |                                         | T <sub>A</sub> = 85 °C                     | 0.5                | 2.3  |           |

|                 |                                |                                         | T <sub>A</sub> = 105 °C                    | 0.94               | 3    |           |

|                 |                                |                                         | T <sub>A</sub> = 125 °C                    | 2.6                | 7    |           |

<sup>1.</sup> Guaranteed by characterization results at 125 °C, unless otherwise specified

Table 37. Average current consumption during Wakeup

| Symbol                                | parameter                                   | System frequency     | Current<br>consumption<br>during wakeup | Unit |

|---------------------------------------|---------------------------------------------|----------------------|-----------------------------------------|------|

|                                       |                                             | HSI                  | 1                                       |      |

|                                       |                                             | HSI/4                | 0,7                                     |      |

| I <sub>DD</sub> (Wakeup from<br>Stop) | Supply current during Wakeup from Stop mode | MSI clock = 4,2 MHz  | 0,7                                     |      |

|                                       |                                             | MSI clock = 1,05 MHz | 0,4                                     |      |

|                                       |                                             | MSI clock = 65 KHz   | 0,1                                     | mA   |

| I <sub>DD</sub> (Reset)               | Reset pin pulled down                       | -                    | 0,21                                    | 117. |

| I <sub>DD</sub> (Power-up)            | BOR on                                      | -                    | 0,23                                    |      |

| I <sub>DD</sub> (Wakeup from          | With Fast wakeup set                        | MSI clock = 2,1 MHz  | 0,5                                     |      |

| StandBy)                              | With Fast wakeup disabled                   | MSI clock = 2,1 MHz  | 0,12                                    |      |

**Electrical characteristics** STM32L063x8

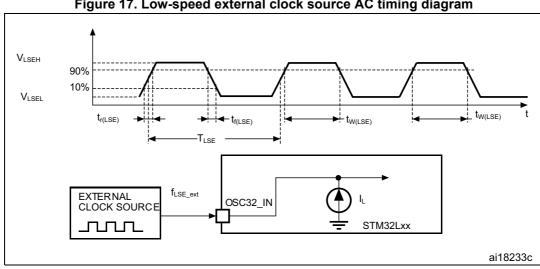

# Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in Table 24.

Table 42. Low-speed external user clock characteristics<sup>(1)</sup>

| Symbol                                                 | Parameter                             | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------------------|---------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                                   | User external clock source frequency  |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                                      | OSC32_IN input pin high level voltage |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                                      | OSC32_IN input pin low level voltage  | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | V    |

| t <sub>w(LSE)</sub>                                    | OSC32_IN high or low time             |                                  | 465                | -      | -                  | ns   |

| $\begin{matrix} t_{r(LSE)} \\ t_{f(LSE)} \end{matrix}$ | OSC32_IN rise or fall time            |                                  | -                  | -      | 10                 | 113  |

| C <sub>IN(LSE)</sub>                                   | OSC32_IN input capacitance            | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                                  | Duty cycle                            | -                                | 45                 | -      | 55                 | %    |

| IL                                                     | OSC32_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production

Figure 17. Low-speed external clock source AC timing diagram

Electrical characteristics STM32L063x8

The analog spike filter is compliant with I<sup>2</sup>C timings requirements only for the following voltage ranges:

- Fast mode Plus: 2.7 V ≤ V<sub>DD</sub> ≤ 3.6 V and voltage scaling Range 1

- Fast mode:

- 2 V ≤ V<sub>DD</sub> ≤ 3.6 V and voltage scaling Range 1 or Range 2.

- V<sub>DD</sub> < 2 V, voltage scaling Range 1 or Range 2, C<sub>load</sub> < 200 pF.

In other ranges, the analog filter should be disabled. The digital filter can be used instead.

Note: In Standard mode, no spike filter is required.

Table 71. I2C analog filter characteristics<sup>(1)</sup>

| Symbol | Parameter                                                              | Conditions | Min               | Max                | Unit |

|--------|------------------------------------------------------------------------|------------|-------------------|--------------------|------|

|        |                                                                        | Range 1    |                   | 100 <sup>(3)</sup> |      |

|        | Maximum pulse width of spikes that are suppressed by the analog filter | Range 2    | 50 <sup>(2)</sup> | -                  | ns   |

|        |                                                                        | Range 3    |                   | -                  |      |

- 1. Guaranteed by characterization results.

- 2. Spikes with widths below  $t_{\text{AF}(\text{min})}$  are filtered.

- 3. Spikes with widths above  $t_{\text{AF}(\text{max})}$  are not filtered

## **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

Table 72. USART/LPUART characteristics

| Symbol   | Parameter Conditions                  |                                                               | Тур | Max  | Unit |

|----------|---------------------------------------|---------------------------------------------------------------|-----|------|------|

|          |                                       | Stop mode with main regulator in Run mode, Range 2 or 3       | -   | 8.7  |      |

| twuusart |                                       | Stop mode with main regulator in Run mode, Range 1            | -   | 8.1  | μs   |

| WOOSAKT  | allowing to wake up from<br>Stop mode | Stop mode with main regulator in low-power mode, Range 2 or 3 | -   | 12   |      |

|          |                                       | Stop mode with main regulator in low-power mode, Range 1      | -   | 11.4 |      |

### **SPI** characteristics

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

Table 73. SPI characteristics in voltage Range 1 (1)

| Symbol                                    | Parameter                         | Conditions                                                  | Min     | Тур   | Max               | Unit |

|-------------------------------------------|-----------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

|                                           |                                   | Master mode                                                 |         |       | 16                |      |

|                                           |                                   | Slave mode receiver                                         | -       | -     | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency               | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                           |                                   | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                     | Duty cycle of SPI clock frequency | Slave mode                                                  | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                      | NSS setup time                    | Slave mode, SPI<br>presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                       | NSS hold time                     | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub>                      | SCK high and low time             | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+            |      |

| t <sub>su(MI)</sub>                       | Data input actus time             | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                       | Data input setup time             | Slave mode                                                  | 3       | -     | -                 |      |

| t <sub>h(MI)</sub>                        | Data input hold time              | Master mode                                                 | 7       | -     | -                 |      |

| t <sub>h(SI)</sub>                        | Data input noid time              | Slave mode                                                  | 3.5     | -     | -                 | ns   |

| t <sub>a(SO</sub>                         | Data output access time           | Slave mode                                                  | 15      | ı     | 36                |      |

| t <sub>dis(SO)</sub>                      | Data output disable time          | Slave mode                                                  | 10      | -     | 30                |      |

| +                                         |                                   | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

| t <sub>v(SO)</sub>                        | Data output valid time            | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |

| t <sub>v(MO)</sub>                        |                                   | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                        | Data output hold time             | Slave mode                                                  | 10      | _     | -                 |      |

| t <sub>h(MO)</sub>                        | Data output Hold tillle           | Master mode                                                 | 0       | -     | -                 |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while  $\text{Duty}_{(SCK)} = 50\%$ .

### **USB** characteristics

The USB interface is USB-IF certified (full speed).

Table 77. USB startup time

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

<sup>1.</sup> Guaranteed by design.

Table 78. USB DC electrical characteristics

| Symbol                         | Parameter                                                                     | Conditions                               | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |

|--------------------------------|-------------------------------------------------------------------------------|------------------------------------------|---------------------|---------------------|------|--|

| Input leve                     | Input levels                                                                  |                                          |                     |                     |      |  |

| V <sub>DD</sub>                | USB operating voltage                                                         | -                                        | 3.0                 | 3.6                 | V    |  |

| V <sub>DI</sub> <sup>(2)</sup> | Differential input sensitivity                                                | I(USB_DP, USB_DM)                        | 0.2                 | -                   |      |  |

| V <sub>CM</sub> <sup>(2)</sup> | Differential common mode range                                                | Includes V <sub>DI</sub> range           | 0.8                 | 2.5                 | V    |  |

| V <sub>SE</sub> <sup>(2)</sup> | Single ended receiver threshold                                               | -                                        | 1.3                 | 2.0                 |      |  |

| Output levels                  |                                                                               |                                          |                     |                     |      |  |

| V <sub>OL</sub> <sup>(3)</sup> | Static output level low $R_L$ of 1.5 k $\Omega$ to 3.6 V <sup>(4)</sup> - 0.3 |                                          | 0.3                 | V                   |      |  |

| V <sub>OH</sub> <sup>(3)</sup> | Static output level high                                                      | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(4)}$ | 2.8                 | 3.6                 | V    |  |

<sup>1.</sup> All the voltages are measured from the local ground potential.

<sup>2.</sup> Guaranteed by characterization results.

<sup>3.</sup> Guaranteed by test in production.

<sup>4.</sup>  $R_L$  is the load connected on the USB drivers.

Table 80. LCD controller characteristics (continued)

| Symbol                           | Parameter                                                        | Min  | Тур                  | Max              | Unit |  |

|----------------------------------|------------------------------------------------------------------|------|----------------------|------------------|------|--|

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 2.2 V                        | -    | 3.3                  | -                | μA   |  |

| 'LCD`                            | Supply current at V <sub>DD</sub> = 3.0 V                        | -    | 3.1                  | -                | μΑ   |  |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                        | 5.28 | 6.6                  | 7.92             | МΩ   |  |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                         | 192  | 240                  | 288              | kΩ   |  |

| V <sub>44</sub>                  | Segment/Common highest level voltage                             | -    | -                    | V <sub>LCD</sub> | V    |  |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                                 | -    | 3/4 V <sub>LCD</sub> | -                |      |  |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                                 | -    | 2/3 V <sub>LCD</sub> | -                |      |  |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                                 | -    | 1/2 V <sub>LCD</sub> | -                | V    |  |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                                 | -    | 1/3 V <sub>LCD</sub> | -                | V    |  |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                                 | -    | 1/4 V <sub>LCD</sub> | -                |      |  |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                              | 0    | -                    | -                |      |  |

| ΔVxx <sup>(3)</sup>              | Segment/Common level voltage error T <sub>A</sub> = -40 to 85 °C | -    | -                    | ± 50             | mV   |  |

LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Guaranteed by characterization results.

Package information STM32L063x8

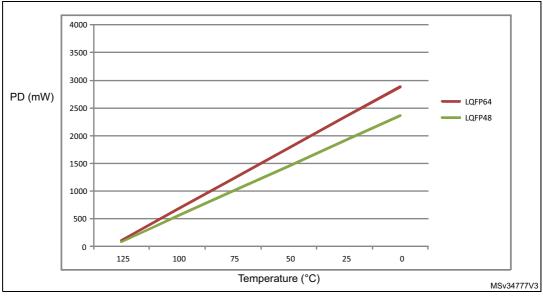

#### 7.3 Thermal characteristics

The maximum chip-junction temperature, T<sub>J</sub> max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O}$$

max =  $\Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DD} - V_{OH}) \times I_{OH})$ ,

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                               | Value | Unit |

|---------------|-------------------------------------------------------------------------|-------|------|

| 0             | Thermal resistance junction-ambient LQFP64 - 10 x 10 mm / 0.5 mm pitch  | 45    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch | 55    | C/VV |

**Table 83. Thermal characteristics**

Figure 40. Thermal resistance

#### 7.3.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

114/121 DocID025660 Rev 6

Revision history STM32L063x8

Table 85. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                        |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | Updated number of SPIs on cover page and in <i>Table 1: Ultra-low-power STM32L063x8 device features and peripheral counts</i> . Changed minimum comparator supply voltage to 1.65 V on cover page.                                                                             |

|             |          | Added number of fast and standard channels in Section 3.12: Analog-to-digital converter (ADC).                                                                                                                                                                                 |

|             |          | Changed LCD_VLCD1 into LCD_VLCD2 in Section 3.13.2: VLCD voltage monitoring.                                                                                                                                                                                                   |

|             |          | Updated Section 3.20.2: Universal synchronous/asynchronous receiver transmitter (USART) and Section 3.20.4: Serial peripheral interface (SPI)/Inter-integrated sound (I2S) to mention the fact that USARTs with synchronous mode feature can be used as SPI master interfaces. |

|             |          | Added baudrate allowing to wake up the MCU from Stop mode in Section 3.20.2: Universal synchronous/asynchronous receiver transmitter (USART) and Section 3.20.3: Low-power universal asynchronous receiver transmitter (LPUART).                                               |

| 22-Mar-2016 | 6        | In Section 6: Electrical characteristics, updated all the notes related to values guaranteed by characterization.                                                                                                                                                              |

|             |          | Section 6.3.15: 12-bit ADC characteristics:                                                                                                                                                                                                                                    |

|             |          | - Table 62: ADC characteristics:                                                                                                                                                                                                                                               |

|             |          | Distinction made between $V_{\text{DDA}}$ for fast and standard channels; added note 1.                                                                                                                                                                                        |

|             |          | Added note 4. related to R <sub>ADC</sub> .                                                                                                                                                                                                                                    |

|             |          | Updated f <sub>TRIG</sub> .                                                                                                                                                                                                                                                    |

|             |          | Updated t <sub>S</sub> and t <sub>CONV</sub> .                                                                                                                                                                                                                                 |

|             |          | - Updated equation 1 description.                                                                                                                                                                                                                                              |

|             |          | <ul> <li>Updated Table 63: RAIN max for fADC = 16 MHz for f<sub>ADC</sub> = 16 MHz<br/>and distinction made between fast and standard channels.</li> </ul>                                                                                                                     |

|             |          | Added Table 72: USART/LPUART characteristics.                                                                                                                                                                                                                                  |

|             |          | Updated R <sub>O</sub> and added Note 1. in Table 65: DAC characteristics.                                                                                                                                                                                                     |

|             |          | Updated Figure 39: LQFP48 marking example (package top view).                                                                                                                                                                                                                  |