Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l063r8t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

The ultra-low-power STM32L063x8 are offered in 48- and 64-pin packages. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L063x8 microcontrollers suitable for a wide range of applications:

- Gas/water meters and industrial sensors

- Healthcare and fitness equipment

- Remote control and user interface

- PC peripherals, gaming, GPS equipment

- Alarm system, wired and wireless sensors, video intercom

This STM32L063x8 datasheet should be read in conjunction with the STM32L0x3xx reference manual (RM0367).

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core please refer to the Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the www.arm.com website.

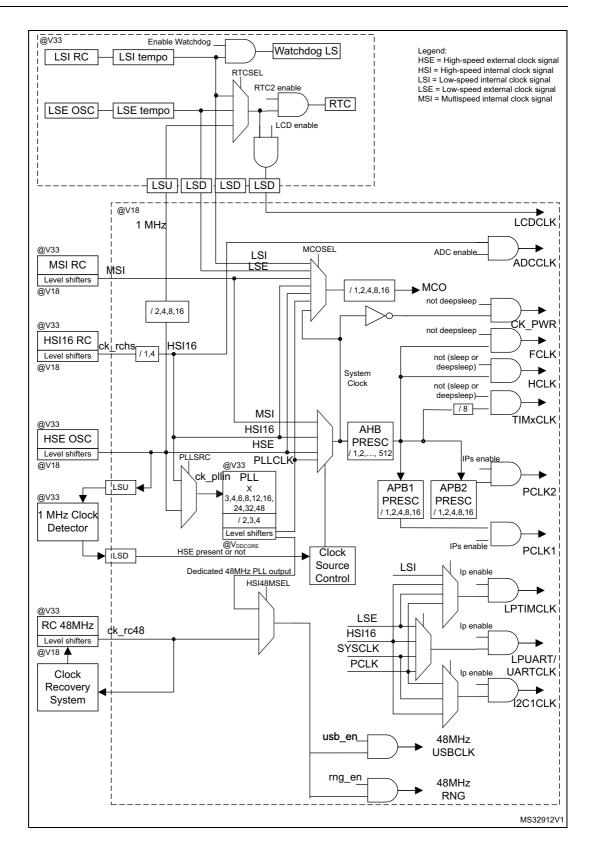

Figure 1 shows the general block diagram of the device family.

# 2.1 Device overview

### Table 1. Ultra-low-power STM32L063x8 device features and peripheral counts

| Peri                                                            | pheral           | STM32L063C8                                                                                         | STM32L063R8                                           |  |  |  |

|-----------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Flash (Kbytes)                                                  |                  | 6                                                                                                   | 4                                                     |  |  |  |

| Data EEPROM (Kb                                                 | ytes)            | 2                                                                                                   | 2                                                     |  |  |  |

| RAM (Kbytes)                                                    |                  | 8                                                                                                   | 3                                                     |  |  |  |

| AES                                                             |                  | ,                                                                                                   | 1                                                     |  |  |  |

|                                                                 | General-purpose  | 3                                                                                                   | 3                                                     |  |  |  |

| Timers                                                          | Basic            |                                                                                                     | 1                                                     |  |  |  |

| AES<br>Timers<br>RTC/SYSTICK/IWD<br>Communication<br>interfaces | LPTIMER          |                                                                                                     | 1                                                     |  |  |  |

| RTC/SYSTICK/IWE                                                 | )G/WWDG          | 1/1/                                                                                                | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |

|                                                                 | SPI/I2S          | 4(2) <sup>(</sup>                                                                                   | <sup>(1)</sup> /1                                     |  |  |  |

| Communication<br>interfaces                                     | l <sup>2</sup> C | 2                                                                                                   |                                                       |  |  |  |

|                                                                 | USART            | 2                                                                                                   |                                                       |  |  |  |

|                                                                 | LPUART           | 1                                                                                                   |                                                       |  |  |  |

|                                                                 | USB/(VDD_USB)    | 1/(1)                                                                                               |                                                       |  |  |  |

| GPIOs                                                           |                  | 37                                                                                                  | 51                                                    |  |  |  |

| Clocks: HSE/LSE/                                                | HSI/MSI/LSI      | 1/1/                                                                                                | 1/1/1                                                 |  |  |  |

|                                                                 |                  | 1<br>10                                                                                             |                                                       |  |  |  |

| 12-bit DAC<br>Number of channe                                  | els              |                                                                                                     |                                                       |  |  |  |

| LCD<br>COM x SEG                                                |                  | 1<br>4x18                                                                                           | 1<br>4x32 or 8x28                                     |  |  |  |

| Comparators                                                     |                  | 2                                                                                                   | 2                                                     |  |  |  |

| Capacitive sensing                                              | g channels       | 17                                                                                                  | 24                                                    |  |  |  |

| Max. CPU frequen                                                | су               | 32 MHz                                                                                              |                                                       |  |  |  |

| Operating voltage                                               |                  | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option |                                                       |  |  |  |

| Operating tempera                                               | atures           |                                                                                                     | ure: –40 to +125 °C<br>ure: –40 to +130 °C            |  |  |  |

| Packages                                                        |                  | LQFP48                                                                                              | LQFP64                                                |  |  |  |

1. 2 SPI interfaces are USARTs operating in SPI master mode.

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

|                                         | Functionalitie                                                  | Functionalities depending on the operating power supply range |                            |                           |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|----------------------------|---------------------------|--|--|--|

| Operating power<br>supply range         | DAC and ADC<br>operation<br>Dynamic<br>voltage scaling<br>range |                                                               | I/O operation              | USB                       |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V        | ADC only,<br>conversion time<br>up to 570 ksps                  | Range 2 or<br>range 3                                         | Degraded speed performance | Not functional            |  |  |  |

| $V_{DD}$ = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps                 | Range 1, range 2<br>or range 3                                | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>  | Conversion time<br>up to 1.14 Msps                              | Range1, range 2<br>or range 3                                 | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V          | Conversion time<br>up to<br>1.14 Msps                           | Range 1, range 2<br>or range 3                                | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V          | Conversion time<br>up to<br>1.14 Msps                           | Range 1, range 2<br>or range 3                                | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |

| Table 2 Eurotionalities dependin  | a on the operating newer supply range  |

|-----------------------------------|----------------------------------------|

| Table 2. Functionalities dependin | ng on the operating power supply range |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

#### Table 3. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

# 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L063x8 are compatible with all ARM tools and software.

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L063x8 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

#### STM32L063x8

DocID025660 Rev 6

## 3.20.5 Universal serial bus (USB)

The STM32L063x8 embed a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use a HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

# 3.21 Clock recovery system (CRS)

The STM32L063x8 embed a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.22 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.23 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

| -         |        |                                    |          |               |       |                                                                                                     |                                 |  |

|-----------|--------|------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------|---------------------------------|--|

| Pi<br>num |        |                                    |          |               |       |                                                                                                     |                                 |  |

| LQFP48    | LQFP64 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                 | Additional functions            |  |

| 18        | 26     | PB0                                | I/O      | FT            | -     | EVENTOUT, LCD_SEG5,<br>TSC_G3_IO2                                                                   | LCD_VLCD3, ADC_IN8,<br>VREF_OUT |  |

| 19        | 27     | PB1                                | I/O      | FT            | -     | LCD_SEG6,<br>TSC_G3_IO3,<br>LPUART1_RTS_DE                                                          | ADC_IN9, VREF_OUT               |  |

| 20        | 28     | PB2                                | I/O      | FT            | -     | LPTIM1_OUT,<br>TSC_G3_IO4                                                                           | LCD_VLCD1                       |  |

| 21        | 29     | PB10                               | I/O      | FT            | -     | LCD_SEG10, TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX,<br>SPI2_SCK, I2C2_SCL                              | -                               |  |

| 22        | 30     | PB11                               | I/O      | FT            | -     | EVENTOUT,<br>LCD_SEG11, TIM2_CH4,<br>TSC_G6_IO1,<br>LPUART1_RX, I2C2_SDA                            | -                               |  |

| 23        | 31     | VSS                                | S        |               | -     | -                                                                                                   | -                               |  |

| 24        | 32     | VDD                                | S        |               | -     | -                                                                                                   | -                               |  |

| 25        | 33     | PB12                               | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LCD_SEG12,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA, EVENTOUT            | LCD_VLCD2                       |  |

| 26        | 34     | PB13                               | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>LCD_SEG13,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL, TIM21_CH1               | -                               |  |

| 27        | 35     | PB14                               | I/O      | FTf           | -     | SPI2_MISO/I2S2_MCK,<br>LCD_SEG14, RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA, TIM21_CH2 | -                               |  |

| 28        | 36     | PB15                               | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>LCD_SEG15,<br>RTC_REFIN                                                       | -                               |  |

| -         | 37     | PC6                                | I/O      | FT            | -     | TIM22_CH1,<br>LCD_SEG24,<br>TSC_G8_IO1                                                              | -                               |  |

## Table 15. STM32L063x8 pin definitions (continued)

|        |     | Table 20. Alternate function port H |

|--------|-----|-------------------------------------|

| P      | ort | AF0                                 |

| Port   |     | USB                                 |

| Port H | PH0 | USB_CRS_SYNC                        |

| FULT   | PH1 | -                                   |

47/121

STM32L063x8

### STM32L063x8

#### 2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter                                     |                                         | Conditions                                         |                                                                       | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|-----------------------------------------------|-----------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------|------|--------------------|------|

| - ,             |                                               |                                         |                                                    | T <sub>A</sub> = − 40 to 25°C                                         | 8.5  | 10                 |      |

|                 |                                               |                                         |                                                    | $T_A = 40.025 \text{ C}$<br>$T_A = 85 \text{ °C}$                     | 11.5 | 48                 | l    |

|                 |                                               |                                         | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz  | $T_{A} = 85 \text{ C}$<br>$T_{A} = 105 \text{ °C}$                    | 15.5 | 40<br>53           | 1    |

|                 |                                               |                                         | HOLK                                               | $T_{A} = 105 \text{ C}$<br>$T_{A} = 125 \text{ °C}$                   | 27.5 | 130                | 1    |

|                 |                                               |                                         |                                                    | $T_{A} = 125 \text{ C}$<br>$T_{A} = -40 \text{ °C to } 25 \text{ °C}$ | 10   | 150                | 1    |

|                 |                                               | All peripherals<br>off, code            |                                                    |                                                                       | 15.5 |                    | 1    |

|                 |                                               | executed from                           | MSI clock= 65 kHz,<br>f <sub>HCLK</sub> = 65 kHz   | T <sub>A</sub> = 85 °C                                                |      | 50                 | 1    |

|                 |                                               | RAM, Flash<br>switched off,             | HCLK - 00 KHZ                                      | T <sub>A</sub> = 105 °C                                               | 19.5 | 54                 | l    |

|                 |                                               | V <sub>DD</sub> from 1.65               |                                                    | T <sub>A</sub> = 125 °C                                               | 31.5 | 130                | I    |

|                 | Supply<br>current in<br>Low-power<br>run mode | to 3.6 V                                |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$                            | 20   | 25                 | I    |

|                 |                                               |                                         | MSI clock= 131 kHz,<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 55 °C                                                | 23   | 50                 | - μΑ |

|                 |                                               |                                         |                                                    | T <sub>A</sub> = 85 °C                                                | 25.5 | 55                 |      |

|                 |                                               |                                         |                                                    | T <sub>A</sub> = 105 °C                                               | 29.5 | 64                 |      |

| I <sub>DD</sub> |                                               |                                         |                                                    | T <sub>A</sub> = 125 °C                                               | 40   | 140                |      |

| (LP Run)        |                                               | All peripherals                         | MSI clock= 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz   | $T_A = -40$ to 25°C                                                   | 22   | 28                 |      |

|                 |                                               |                                         |                                                    | T <sub>A</sub> = 85 °C                                                | 26   | 68                 |      |

|                 |                                               |                                         |                                                    | T <sub>A</sub> = 105 °C                                               | 31   | 75                 |      |

|                 |                                               |                                         |                                                    | T <sub>A</sub> = 125 °C                                               | 44   | 95                 |      |

|                 |                                               |                                         |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$                            | 27.5 | 33                 |      |

|                 |                                               | off, code                               | MSI clock = 65 kHz,                                | T <sub>A</sub> = 85 °C                                                | 31.5 | 73                 |      |

|                 |                                               | executed from<br>Flash, V <sub>DD</sub> | f <sub>HCLK</sub> = 65 kHz                         | T <sub>A</sub> = 105 °C                                               | 36.5 | 80                 |      |

|                 |                                               | from 1.65 V to                          |                                                    | T <sub>A</sub> = 125 °C                                               | 49   | 100                |      |

|                 |                                               | 3.6 V                                   |                                                    | $T_A = -40 \text{ to } 25^{\circ}\text{C}$                            | 39   | 46                 |      |

|                 |                                               |                                         | MSI clock =                                        | T <sub>A</sub> = 55 °C                                                | 41   | 80                 |      |

|                 |                                               |                                         | 131 kHz,                                           | T <sub>A</sub> = 85 °C                                                | 44   | 86                 | l    |

|                 |                                               |                                         | f <sub>HCLK</sub> = 131 kHz                        | T <sub>A</sub> = 105 °C                                               | 49.5 | 100                | l    |

|                 |                                               |                                         |                                                    | T <sub>A</sub> = 125 °C                                               | 60   | 120                | I    |

#### Table 33. Current consumption in Low-power run mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

| Symbol                     | Derinheral                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | Unit |

|----------------------------|------------------------------|------------------------|-------------------------------|------|

| Symbol                     | Peripheral                   | V <sub>DD</sub> =1.8 V |                               | Onit |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |      |

| I <sub>REFINT</sub>        | -                            | -                      | 1.4                           |      |

| -                          | LSE Low drive <sup>(2)</sup> | 0,1                    | 0,1                           |      |

| -                          | - LPTIM1, Input 100 Hz       |                        | 0,01                          | μΑ   |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                             |      |

| -                          | - LPUART1<br>- RTC           |                        | 0,2                           |      |

| -                          |                              |                        | 0,48                          |      |

| - LCD1 (static duty)       |                              | 0,15                   | 0,15                          |      |

| -                          | LCD1 (1/8 duty)              | 1,6                    | 2,6                           | μΑ   |

| Table 39. Peripheral current | consumption in Stop and Standby mode <sup>(1)</sup> |

|------------------------------|-----------------------------------------------------|

|------------------------------|-----------------------------------------------------|

1. LPTIM peripheral cannot operate in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

## 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

## 6.3.9 Memory characteristics

## **RAM** memory

| Ś | Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|---|--------|------------------------------------|----------------------|------|-----|-----|------|

|   | VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 50. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|--|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |  |

| +                 | Programming time for word or half-page                                         | Erasing                                         | -    | 3.28 | 3.94               | 20   |  |  |

| t <sub>prog</sub> |                                                                                | Programming                                     | -    | 3.28 | 3.94               | ms   |  |  |

|                   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |  |  |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |  |

## Table 51. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 52. Flash memory | and data EEPROM enduranc | e and retention |

|------------------------|--------------------------|-----------------|

|                        |                          |                 |

| Symbol                          | Parameter                                     | Conditions                       | Value              | Unit    |

|---------------------------------|-----------------------------------------------|----------------------------------|--------------------|---------|

| Symbol                          | Falameter                                     | Conditions                       | Min <sup>(1)</sup> | Omt     |

|                                 | Cycling (erase / write)<br>Program memory     | T 40°C to 105 °C                 | 10                 |         |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C | 100                | kcycles |

| INCYC (                         | Cycling (erase / write)<br>Program memory     | T 40°C to 125 °C                 | 0.2                | KUYUUUS |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 125 °C | 2                  |         |

## 6.3.13 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the conditions summarized in *Table 24*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                                                                    | Min                 | Тур                                | Max                                | Unit |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                                                                      | -                   | -                                  | 0.3V <sub>DD</sub>                 |      |

|                  |                                                   | BOOT0 pin                                                                                                                                                     | -                   | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |

| V <sub>IH</sub>  | Input high level voltage                          | All I/Os                                                                                                                                                      | 0.7 V <sub>DD</sub> | -                                  | -                                  | V    |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                                                                 | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                                                                     | -                   | 0.01                               | -                                  |      |

|                  |                                                   | $\label{eq:VSS} \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ \mbox{All I/Os except for} \\ \mbox{PA11, PA12, BOOT0} \\ \mbox{and FTf I/Os} \end{array}$ | -                   | -                                  | ±50                                |      |

|                  |                                                   | $V_{SS} \le V_{IN} \le V_{DD}$ , PA11 and PA12 I/Os                                                                                                           | -                   | -                                  | -50/+250                           | nA   |

|                  |                                                   | $V_{SS} \le V_{IN} \le V_{DD}$<br>FTf I/Os                                                                                                                    | -                   | -                                  | ±100                               |      |

| l <sub>lkg</sub> | Input leakage current <sup>(4)</sup>              | $\label{eq:VDD} \begin{array}{c} V_{DD}{}^{\leq}V_{IN}{}^{\leq}5V\\ \mbox{All I/Os except for}\\ \mbox{PA11, PA12, BOOT0}\\ \mbox{and FTf I/Os} \end{array}$  | -                   | -                                  | 200                                | nA   |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>FTf I/Os                                                                                                                       | -                   | -                                  | 500                                |      |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>PA11, PA12 and BOOT0                                                                                                           | -                   | -                                  | 10                                 | μΑ   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | $V_{IN} = V_{SS}$                                                                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                                                                             | -                   | 5                                  | -                                  | pF   |

1. Guaranteed by characterization.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 200 mV. Guaranteed by characterization results.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

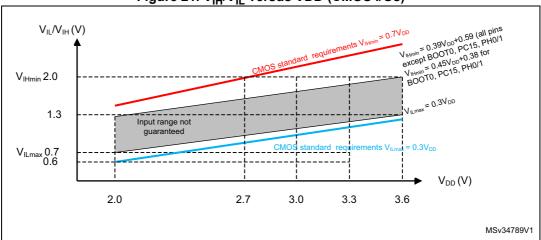

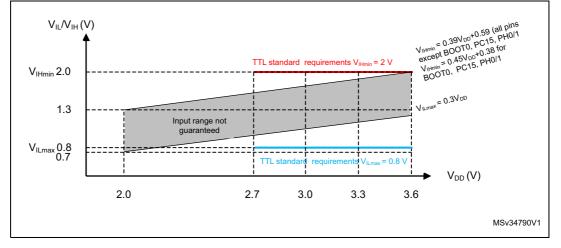

Figure 21. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (CMOS I/Os)

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 15$  mA with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 59*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD(Σ)</sub> (see *Table 22*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS(Σ)</sub> (see *Table 22*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*. All I/Os are CMOS and TTL compliant.

| Symbol                               | Parameter                                | Conditions                                                                                                                                                               | Min                   | Max  | Unit |

|--------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA                                                                                                                    | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin | $1_{O} = +0.01$ A $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                             | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin  | $\begin{array}{c} {\sf TTL} \; {\sf port}^{(2)}, \\ {\sf I}_{IO} \; \mbox{=} + \; 8 \; \mbox{mA} \\ 2.7 \; {\sf V} \leq {\sf V}_{DD} \leq \; 3.6 \; {\sf V} \end{array}$ | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $\begin{array}{c} \text{TTL port}^{(2)},\\ \text{I}_{\text{IO}} \texttt{=} -6 \text{ mA}\\ 2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq \ 3.6 \text{ V} \end{array}$     | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin  | $\begin{array}{l} \text{I}_{IO} = +15 \text{ mA} \\ 2.7 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                                   | -                     | 1.3  | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $\begin{array}{l} \text{I}_{\text{IO}} \text{ = -15 mA} \\ \text{2.7 V} \leq \text{V}_{DD} \leq \ \text{3.6 V} \end{array}$                                              | V <sub>DD</sub> -1.3  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin  | $I_{IO}$ = +4 mA<br>1.65 V $\leq$ V <sub>DD</sub> < 3.6 V                                                                                                                | -                     | 0.45 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin | $\begin{array}{l} \text{I}_{IO} = \text{-4 mA} \\ 1.65 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                                    | V <sub>DD</sub> -0.45 | -    |      |

| V <sub>OLFM+</sub> <sup>(1)(4)</sup> | Output low level voltage for an FTf      | $\begin{array}{l} \text{I}_{IO} = 20 \text{ mA} \\ 2.7 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                                    | -                     | 0.4  |      |

| VOLEM+                               | I/O pin in Fm+ mode                      | $\begin{array}{l} {\sf I}_{IO} = 10 \mbox{ mA} \\ 1.65 \mbox{ V} \leq {\sf V}_{DD} \leq \ 3.6 \mbox{ V} \end{array}$                                                     | -                     | 0.4  |      |

#### Table 59. Output voltage characteristics

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 22*. The sum of the currents sunk by all the I/Os (I/O ports and control pins) must always be respected and must not exceed ΣI<sub>IO(PIN)</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 22. The sum of the currents sourced by all the I/Os (I/O ports and control pins) must always be respected and must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Guaranteed by characterization results.

| Symbol                  | Parameter                                                                                                                                                 | Conditions                                                                 | Min | Тур | Мах | Unit  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| dGain/dT <sup>(1)</sup> | Gain error temperature                                                                                                                                    | $V_{DDA} = 3.3V$<br>$T_A = 0$ to 50 °C<br>DAC output buffer off            | -10 | -2  | 0   | μV/°C |

|                         | coefficient                                                                                                                                               | $V_{DDA} = 3.3V$<br>$T_A = 0$ to 50 °C<br>DAC output buffer on             | -40 | -8  | 0   | μν/ Ο |

| TUE <sup>(1)</sup>      | Total upadiusted error                                                                                                                                    | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | 12  | 30  | LSB   |

| IUE'                    | Total unadjusted error                                                                                                                                    | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off           | -   | 8   | 12  | LOD   |

| tSETTLING               | Settling time (full scale: for a<br>12-bit code transition between<br>the lowest and the highest<br>input codes till DAC_OUT<br>reaches final value ±1LSB | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$                 | -   | 7   | 12  | μs    |

| Update rate             | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                         | -   | -   | 1   | Msps  |

| twakeup                 | Wakeup time from off state<br>(setting the ENx bit in the DAC<br>Control register) <sup>(8)</sup>                                                         | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                         | -   | 9   | 15  | μs    |

| PSRR+                   | V <sub>DDA</sub> supply rejection ratio<br>(static DC measurement)                                                                                        | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                         | -   | -60 | -35 | dB    |

| Table 65 | DAC | characteristics | (continued) |

|----------|-----|-----------------|-------------|

|----------|-----|-----------------|-------------|

1. Guaranteed by design, not tested in production.

2. Connected between DAC\_OUT and  $V_{SSA}$ .

3. Difference between two consecutive codes - 1 LSB.

4. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

5. Difference between the value measured at Code (0x800) and the ideal value =  $V_{DDA}/2$ .

6. Difference between the value measured at Code (0x001) and the ideal value.

7. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is off, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is on.

8. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

| Symbol                   | Parameter                                                      | Conditions                                                                                                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                                                                         | -                  | 7   | 10                 | 116       |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                                                                         | -                  | 3   | 10                 | μs        |

| Voffset                  | Comparator offset                                              | -                                                                                                                                                         | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $\label{eq:VDDA} \begin{split} V_{DDA} &= 3.6 \text{ V},  V_{IN+} = 0 \text{ V}, \\ V_{IN-} &= V_{REFINT},  T_A \text{ = } 25 ^\circ\text{C} \end{split}$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                                                                         | -                  | 160 | 260                | nA        |

Table 68. Comparator 1 characteristics (continued)

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

|                     |                                               |                                                                                                                                                                           |      |     |                    | 1          |

|---------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|

| Symbol              | Parameter                                     | Conditions                                                                                                                                                                | Min  | Тур | Max <sup>(1)</sup> | Unit       |

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                                                         | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                                                         | 0    | -   | V <sub>DDA</sub>   | V          |

| +                   | Comparator startup time                       | Fast mode                                                                                                                                                                 | -    | 15  | 20                 |            |

| t <sub>START</sub>  | Comparator startup time                       | Slow mode                                                                                                                                                                 | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | $1.65~V \leq V_{DDA} \leq 2.7~V$                                                                                                                                          | -    | 1.8 | 3.5                |            |

| t <sub>d slow</sub> | Fropagation delay 7 in slow mode              | $2.7~V \leq V_{DDA} \leq 3.6~V$                                                                                                                                           | -    | 2.5 | 6                  | - µs       |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | $1.65~V \leq V_{DDA} \leq 2.7~V$                                                                                                                                          | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | Flopagation delay / in last mode              | $2.7~V \leq V_{DDA} \leq 3.6~V$                                                                                                                                           | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       |                                                                                                                                                                           | -    | ±4  | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V, T_A = 0 \text{ to } 50 \text{ °C},$<br>V- = V <sub>REFINT</sub> ,<br>3/4 V <sub>REFINT</sub> ,<br>1/2 V <sub>REFINT</sub> ,<br>1/4 V <sub>REFINT</sub> . | -    | 15  | 30                 | ppm<br>/°C |

| 1                   | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                                                 | -    | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                                                 | -    | 0.5 | 2                  | μA         |

#### Table 69. Comparator 2 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (required for comparator operation) is not included.

### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Cteristics in voltag                                        | Min     |       | Мах               | Unit |

|----------------------------------------------|--------------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

| Symbol                                       | Parameter                            | Conditions                                                  | IVIIII  | Тур   | wax               | Unit |

|                                              |                                      | Master mode                                                 |         |       | 16                |      |

|                                              |                                      | Slave mode<br>receiver                                      | -       | -     | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                              |                                      | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                                  | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI<br>presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+<br>2       |      |

| t <sub>su(MI)</sub>                          | Data input actus time                | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                                  | 3       | -     | -                 |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                 | 7       | -     | -                 |      |

| t <sub>h(SI)</sub>                           | Data input noid time                 | Slave mode                                                  | 3.5     | -     | -                 | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                                  | 15      | -     | 36                |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                                  | 10      | -     | 30                |      |

| +                                            |                                      | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                                  | 10      | -     | -                 |      |

|                                              |                                      | Master mode                                                 | 0       | -     |                   | 1    |

| Table 73. SPI characteristics | in voltage Range 1 <sup>(1)</sup> |

|-------------------------------|-----------------------------------|

|-------------------------------|-----------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while  $Duty_{(SCK)} = 50\%$ .

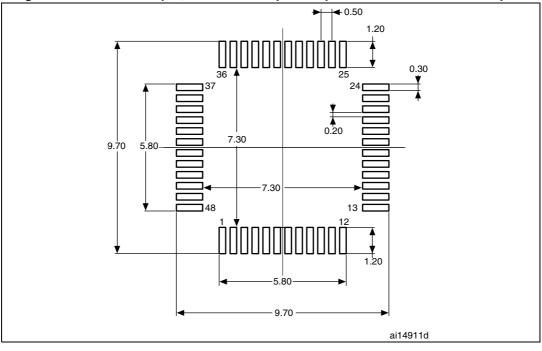

Figure 38. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

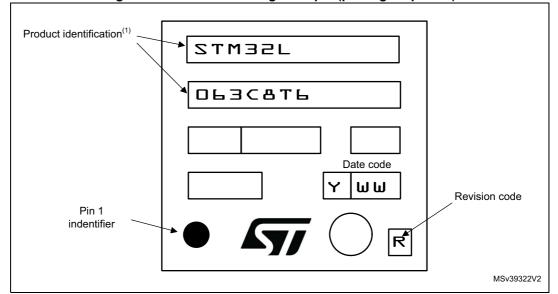

#### **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Figure 39. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID025660 Rev 6

| Date Re     | evision | Changes           Removed note 1 in Table 1: Ultra-low-power STM32L063x8 device features and peripheral counts.           Updated all pinout/ballout schematics to highlight pin/ball supplied through VDD_USB.           Updated current consumption in Run mode in Section : Features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |         | features and peripheral counts.<br>Updated all pinout/ballout schematics to highlight pin/ball supplied<br>through VDD_USB.<br>Updated current consumption in Run mode in <i>Section : Features</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 08-Sep-2015 | 5       | Renamed BOOT1 into nBOOT1.<br>Changed USARTx_RTS into USARTx_RTS_DE and LPUARTx_RTS<br>into LPUARTx_RTS_DE.<br>Updated VLCD in section Analog to digital converter (ADC).<br>ADC no more available in Low-power run and Low-power Sleep modes<br>in Table 4: Functionalities depending on the working mode (from<br><i>Run/active down to standby</i> ).<br>Updated Figure 4: STM32L063x8 LQFP48 pinout - 7 x 7 mm and<br>Figure 3: STM32L063x8 LQFP64 pinout - 10 x 10 mm. Changed I/O<br>structure for PC5 in Table 15: STM32L063x8 pin definitions.<br>Updated VDD_USB in Table 24: General operating conditions.<br>Changed temperature condition in Table 7: Internal voltage reference<br>measured values and Table 26: Embedded internal reference voltage<br>calibration values.<br>Updated T <sub>Coeff</sub> in Table 27: Embedded internal reference voltage.<br>Added note related to Standby mode in Table 39: Peripheral current<br>consumption in Stop and Standby mode.<br>Updated Figure 13: IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Low-<br>power run mode, code running from RAM, Range 3, MSI (Range 0) at<br>Figure 15: IDD vs VDD, at TA= 25/55/ 85/105/125 °C,<br>Stop mode with RTC enabled and running on LSE Low drive and<br>Figure 15: IDD vs VDD, at TA= 25/55/ 85/105/125 °C,<br>Stop mode with RTC enabled and running on LSE Low drive and<br>Figure 15: IDD vs VDD, at TA= 25/55/85/105/125 °C,<br>Stop mode with RTC enabled and running on LSE Low drive and<br>Figure 15: IDD vs VDD, at TA= 25/55/85/105/125 °C,<br>Stop mode with RTC enabled and running on LSE Low drive and<br>Figure 15: IDD vs VDD, at TA= 25/55/85/105/125 °C,<br>Stop mode with RTC enabled 62: ADC characteristics.<br>Updated Table 53: EMS characteristics and Table 54: EMI<br>characteristics.<br>Added t <sub>UP_LDO</sub> in Table 62: ADC characteristics.<br>Updated Table 57: I/O current injection susceptibility, Table 58: I/O<br>static characteristics (I <sub>lkg</sub> ) and Table 60: I/O AC characteristics.<br>Updated Figure 28: SPI timing diagram - slave mode and CPHA = 0,<br>Table 73: SPI characteristics in voltage Range 1, Table 74: SPI<br>characteristics in voltage Range 2 and Table 75: S |

Table 85. Document revision history (continued)