#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M0+Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6VData ConvertersA/D 16x12b; D/A 1x12b |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                       |

| Speed32MHzConnectivityI²C, IrDA, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                  |

| ConnectivityI²C, IrDA, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                            |

| PeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                                                                       |

| Number of I/O51Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                                                                                                                                      |

| Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                                                                                                                                                     |

| Program Memory TypeFLASHEEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                                                                                                                                                                                      |

| EEPROM Size2K x 8RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                                                                                                                                                                                                              |

| RAM Size         8K x 8           Voltage - Supply (Vcc/Vdd)         1.65V ~ 3.6V                                                                                                                                                                                                                                                                                                  |

| Voltage - Supply (Vcc/Vdd) 1.65V ~ 3.6V                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                    |

| Data ConvertersA/D 16x12b; D/A 1x12b                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                    |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                                                                           |

| Operating Temperature -40°C ~ 85°C (TA)                                                                                                                                                                                                                                                                                                                                            |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                                                                        |

| Package / Case 64-LQFP                                                                                                                                                                                                                                                                                                                                                             |

| Supplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                             |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l063r8t6tr                                                                                                                                                                                                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                           |            |       | Low-         | Low-           |                  | Stop                 |   | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|------------------|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          |       | Y            |                |                  |                      |   |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Υ                |                      |   |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Υ                |                      | Y |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| Brown-out reset<br>(BOR)                  | 0          | О     | 0            | 0              | 0                | Ο                    | 0 | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | 0              | 0                | 0                    | - |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y                | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (2)              |                      |   |                      |

| High Speed<br>External (HSE)              | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| Low Speed Internal<br>(LSI)               | 0          | 0     | 0            | 0              | 0                |                      | 0 |                      |

| Low Speed<br>External (LSE)               | 0          | 0     | 0            | 0              | 0                |                      | 0 |                      |

| Multi-Speed<br>Internal (MSI)             | 0          | 0     | Y            | Y              |                  |                      |   |                      |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | Y                |                      |   |                      |

| RTC                                       | 0          | 0     | 0            | 0              | 0                | 0                    | 0 |                      |

| RTC Tamper                                | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| Auto WakeUp<br>(AWU)                      | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| LCD                                       | 0          | 0     | 0            | 0              | 0                |                      |   |                      |

| USB                                       | 0          | 0     |              |                |                  | 0                    |   |                      |

| USART                                     | 0          | 0     | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |

| LPUART                                    | 0          | 0     | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |

| SPI                                       | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| I2C                                       | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    |   |                      |

| ADC                                       | 0          | 0     |              |                |                  |                      |   |                      |

# Table 4. Functionalities depending on the working mode (from Run/active down to standby) <sup>(1)</sup>

## 3.8 Memories

The STM32L063x8 devices have the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

• Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

## 3.10 Direct memory access (DMA)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, DAC, and ADC.

# 3.11 Liquid crystal display (LCD)

The LCD drives up to 8 common terminals and 32 segment terminals to drive up to 224 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

- V<sub>LCD</sub> rails decoupling capability

# 3.12 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L063x8 device. It has up to 16 external channels and 3 internal channels (temperature sensor, voltage reference,  $V_{LCD}$  voltage measurement). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~200  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

DocID025660 Rev 6

communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

## 3.20.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to Table 13 for the differences between SPI1 and SPI2.

| SPI1 | SPI2 |

|------|------|

| Х    | Х    |

| -    | Х    |

| Х    | Х    |

|      | X    |

#### Table 13. SPI/I2S implementation

1. X = supported.

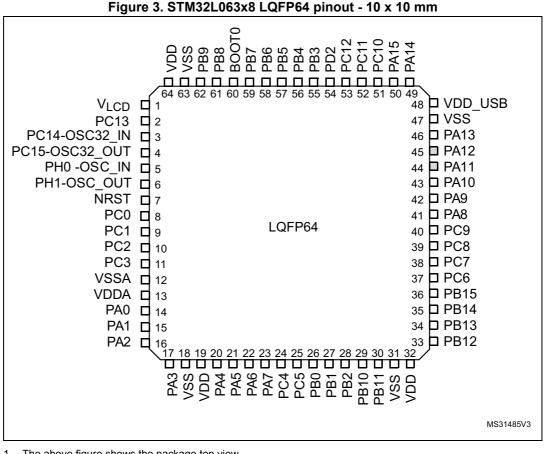

# 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

| -         |        |                                    |          |               |       | pin definitions (continu                                                                            |                                 |

|-----------|--------|------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------|---------------------------------|

| Pi<br>num |        |                                    |          |               |       |                                                                                                     |                                 |

| LQFP48    | LQFP64 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                 | Additional functions            |

| 18        | 26     | PB0                                | I/O      | FT            | -     | EVENTOUT, LCD_SEG5,<br>TSC_G3_IO2                                                                   | LCD_VLCD3, ADC_IN8,<br>VREF_OUT |

| 19        | 27     | PB1                                | I/O      | FT            | -     | LCD_SEG6,<br>TSC_G3_IO3,<br>LPUART1_RTS_DE                                                          | ADC_IN9, VREF_OUT               |

| 20        | 28     | PB2                                | I/O      | FT            | -     | LPTIM1_OUT,<br>TSC_G3_IO4                                                                           | LCD_VLCD1                       |

| 21        | 29     | PB10                               | I/O      | FT            | -     | LCD_SEG10, TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX,<br>SPI2_SCK, I2C2_SCL                              | -                               |

| 22        | 30     | PB11                               | I/O      | FT            | -     | EVENTOUT,<br>LCD_SEG11, TIM2_CH4,<br>TSC_G6_IO1,<br>LPUART1_RX, I2C2_SDA                            | -                               |

| 23        | 31     | VSS                                | S        |               | -     | -                                                                                                   | -                               |

| 24        | 32     | VDD                                | S        |               | -     | -                                                                                                   | -                               |

| 25        | 33     | PB12                               | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LCD_SEG12,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA, EVENTOUT            | LCD_VLCD2                       |

| 26        | 34     | PB13                               | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>LCD_SEG13,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL, TIM21_CH1               | -                               |

| 27        | 35     | PB14                               | I/O      | FTf           | -     | SPI2_MISO/I2S2_MCK,<br>LCD_SEG14, RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA, TIM21_CH2 | -                               |

| 28        | 36     | PB15                               | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>LCD_SEG15,<br>RTC_REFIN                                                       | -                               |

| -         | 37     | PC6                                | I/O      | FT            | -     | TIM22_CH1,<br>LCD_SEG24,<br>TSC_G8_IO1                                                              | -                               |

## Table 15. STM32L063x8 pin definitions (continued)

| 44/121            |        |      |                                 |           | Table 16. Alter        | nate function    | port A            |            |          |           |

|-------------------|--------|------|---------------------------------|-----------|------------------------|------------------|-------------------|------------|----------|-----------|

| 21                |        |      | AF0                             | AF1       | AF2                    | AF3              | AF4               | AF5        | AF6      | AF7       |

|                   | Po     | ort  | SPI1/TIM21/SYS_A<br>F/EVENTOUT/ | LCD       | USB/TIM2/<br>EVENTOUT/ | TSC/<br>EVENTOUT | USART1/2/3        | TIM2/21/22 | EVENTOUT | COMP1/2   |

|                   |        | PA0  | -                               | -         | TIM2_CH1               | TSC_G1_IO1       | USART2_CTS        | TIM2_ETR   | -        | COMP1_OUT |

|                   |        | PA1  | EVENTOUT                        | LCD_SEG0  | TIM2_CH2               | TSC_G1_IO2       | USART2_RTS_<br>DE | TIM21_ETR  | -        | -         |

|                   |        | PA2  | TIM21_CH1                       | LCD_SEG1  | TIM2_CH3               | TSC_G1_IO3       | USART2_TX         | -          | -        | COMP2_OUT |

|                   |        | PA3  | TIM21_CH2                       | LCD_SEG2  | TIM2_CH4               | TSC_G1_IO4       | USART2_RX         | -          | -        | -         |

|                   |        | PA4  | SPI1_NSS                        | -         | -                      | TSC_G2_IO1       | USART2_CK         | TIM22_ETR  | -        | -         |

|                   |        | PA5  | SPI1_SCK                        | -         | TIM2_ETR               | TSC_G2_IO2       | -                 | TIM2_CH1   | -        | -         |

| D                 |        | PA6  | SPI1_MISO                       | LCD_SEG3  | -                      | TSC_G2_IO3       | LPUART1_CTS       | TIM22_CH1  | EVENTOUT | COMP1_OUT |

| cIDC              |        | PA7  | SPI1_MOSI                       | LCD_SEG4  | -                      | TSC_G2_IO4       | -                 | TIM22_CH2  | EVENTOUT | COMP2_OUT |

| DocID025660 Rev 6 | Port A | PA8  | MCO                             | LCD_COM0  | USB_CRS_SYNC           | EVENTOUT         | USART1_CK         | -          | -        | -         |

| 60 R              |        | PA9  | MCO                             | LCD_COM1  | -                      | TSC_G4_IO1       | USART1_TX         | -          | -        | -         |

| lev 6             |        | PA10 | -                               | LCD_COM2  | -                      | TSC_G4_IO2       | USART1_RX         | -          | -        | -         |

| 0,                |        | PA11 | SPI1_MISO                       | -         | EVENTOUT               | TSC_G4_IO3       | USART1_CTS        | -          | -        | COMP1_OUT |

|                   |        | PA12 | SPI1_MOSI                       | -         | EVENTOUT               | TSC_G4_IO4       | USART1_RTS_<br>DE | -          | -        | COMP2_OUT |

|                   |        | PA13 | SWDIO                           | -         | USB_OE                 | -                | -                 | -          | -        | -         |

|                   |        | PA14 | SWCLK                           | -         | -                      | -                | USART2_TX         | -          | -        | -         |

|                   |        | PA15 | SPI1_NSS                        | LCD_SEG17 | TIM2_ETR               | EVENTOUT         | USART2_RX         | TIM2_CH1   | -        | -         |

STM32L063x8

| Symbol            | Parameter          | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|--------------------|-------------------------------------------|------|------|------|------|

| V                 | PVD threshold 6    | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

| V <sub>PVD6</sub> |                    | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |

|                   |                    | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

#### Table 25. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 27* are based on characterization results, unless otherwise specified.

| Table 26. Embedde   | ed internal reference voltage | calibration values |

|---------------------|-------------------------------|--------------------|

| ibration value name | Description                   | Memory address     |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

|                        | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

### Table 27. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                                   | Parameter                                                           | Conditions                                                     | Min   | Тур   | Max   | Unit   |

|------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                          | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                     | -                                                              | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure | -                                                              | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>      | Including uncertainties due to ADC and V <sub>DDA</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                             | –40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                 | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                 | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage | -                                                              | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                    | -                                                              | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                     | -                                                              | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                              | -                                                              | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                | -                                                              | -     | -     | 50    | pF     |

|                                         |                                                                     |            | •   | ,   |      |                          |

|-----------------------------------------|---------------------------------------------------------------------|------------|-----|-----|------|--------------------------|

| Symbol                                  | Parameter                                                           | Conditions | Min | Тур | Max  | Unit                     |

| I <sub>LPBUF</sub> <sup>(4)</sup>       | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP | -          | -   | 730 | 1200 | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup> | 1/4 reference voltage                                               | -          | 24  | 25  | 26   |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup> | 1/2 reference voltage                                               | -          | 49  | 50  | 51   | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup> | 3/4 reference voltage                                               | -          | 74  | 75  | 76   |                          |

Table 27. Embedded internal reference voltage<sup>(1)</sup> (continued)

Refer to Table 39: Peripheral current consumption in Stop and Standby mode for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

4. Guaranteed by design.

5. Shortest sampling time can be determined in the application by multiple iterations.

6. To guarantee less than 1% VREF\_OUT deviation.

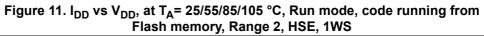

## 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise.

The current consumption values are derived from the tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on fHCLK frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled  $f_{APB1} = f_{APB2} = f_{APB}$

- When PLL is on, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in *Table 41: High-speed external user clock characteristics*

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise

The parameters given in *Table 49*, *Table 24* and *Table 25* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

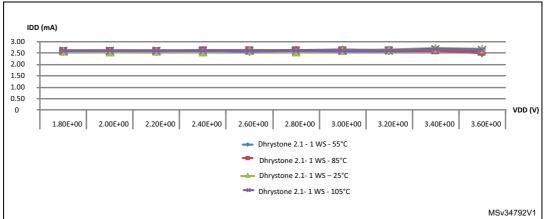

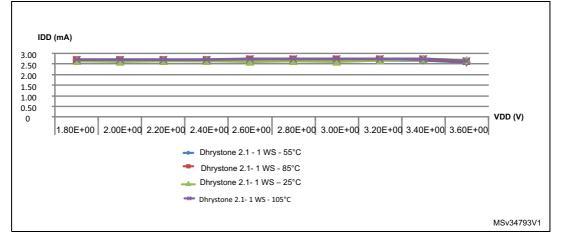

Figure 12.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSI16, 1WS

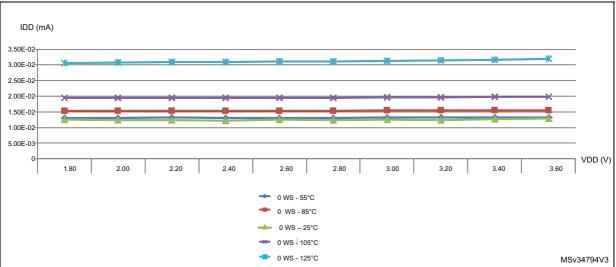

# Figure 13. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25/55/ 85/105/125 °C, Low-power run mode, code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS

| Symbol | Parameter                                       |                             | Conditions                                                      |                                            | Тур                | Max <sup>(1)</sup> | Unit |

|--------|-------------------------------------------------|-----------------------------|-----------------------------------------------------------------|--------------------------------------------|--------------------|--------------------|------|

|        |                                                 |                             | MSI clock = 65 kHz,<br>f <sub>HCLK</sub> = 32 kHz,<br>Flash off | T <sub>A</sub> = − 40 to 25°C              | 4.7 <sup>(2)</sup> | -                  |      |

| 00     |                                                 |                             |                                                                 | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 17                 | 23                 |      |

|        |                                                 |                             | MSI clock = 65 kHz,                                             | T <sub>A</sub> = 85 °C                     | 19.5               | 63                 |      |

|        |                                                 | n off, V <sub>DD</sub> from | f <sub>HCLK</sub> = 32 kHz,<br>Flash on                         | T <sub>A</sub> = 105 °C                    | 23                 | 69                 | μA   |

|        | Supply<br>current in<br>Low-power<br>sleep mode |                             |                                                                 | T <sub>A</sub> = 125 °C                    | 32.5               | 90                 |      |

|        |                                                 |                             | MSI clock =65 kHz,<br>f <sub>HCLK</sub> = 65 kHz,<br>Flash on   | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 17                 | 23                 |      |

|        |                                                 |                             |                                                                 | T <sub>A</sub> = 85 °C                     | 20                 | 63                 |      |

|        |                                                 |                             |                                                                 | T <sub>A</sub> = 105 °C                    | 23.5               | 69                 |      |

|        |                                                 |                             |                                                                 | T <sub>A</sub> = 125 °C                    | 32.5               | 90                 | -    |

|        |                                                 |                             |                                                                 | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 19.5               | 36                 |      |

|        |                                                 |                             | MSI clock = 131 kHz,                                            | T <sub>A</sub> = 55 °C                     | 20.5               | 64                 |      |

|        |                                                 |                             | f <sub>HCLK</sub> = 131 kHz,                                    | T <sub>A</sub> = 85 °C                     | 22.5               | 66                 |      |

|        |                                                 |                             | Flash on                                                        | T <sub>A</sub> = 105 °C                    | 26                 | 72                 |      |

|        |                                                 |                             |                                                                 | T <sub>A</sub> = 125 °C                    | 35                 | 95                 |      |

| Table 34. Current consumption | n in Low-power sleep mode |

|-------------------------------|---------------------------|

|-------------------------------|---------------------------|

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. As the CPU is in Sleep mode, the difference between the current consumption with Flash on and off (nearly 12  $\mu A$ ) is the same whatever the clock frequency.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           |            | Conditions                                          | Monitored       | Max             | vs. f <sub>osc</sub> / |                  |      |

|------------------|------------|-----------------------------------------------------|-----------------|-----------------|------------------------|------------------|------|

|                  | Parameter  |                                                     | frequency band  | 8 MHz/<br>4 MHz | 8 MHz/<br>16 MHz       | 8 MHz/<br>32 MHz | Unit |

|                  |            | V 26V                                               | 0.1 to 30 MHz   | -21             | -15                    | -12              | dBµV |

| \$               | Peak level | V <sub>DD</sub> = 3.6 V,<br>T <sub>A</sub> = 25 °C, | 30 to 130 MHz   | -14             | -12                    | -1               |      |

| S <sub>EMI</sub> | reak level | compliant with IEC                                  | 130 MHz to 1GHz | -10             | -11                    | -7               |      |

|                  |            | 61967-2                                             | EMI Level       | 1               | 1                      | 1                | -    |

Table 54. EMI characteristics

## 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                                     | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)          | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             |      |

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 56. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |

## 6.3.13 I/O port characteristics

### General input/output characteristics

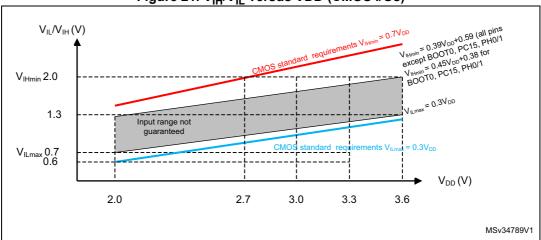

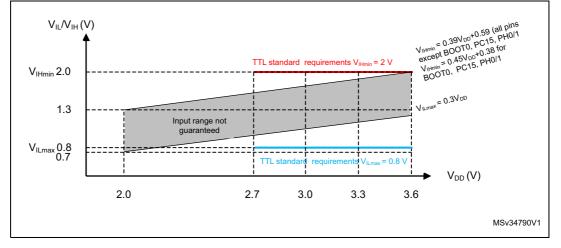

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the conditions summarized in *Table 24*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                                                                    | Min                 | Тур                                | Max                                | Unit |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                                                                      | -                   | -                                  | 0.3V <sub>DD</sub>                 |      |

|                  |                                                   | BOOT0 pin                                                                                                                                                     | -                   | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |

| V <sub>IH</sub>  | Input high level voltage                          | All I/Os                                                                                                                                                      | 0.7 V <sub>DD</sub> | -                                  | -                                  | V    |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                                                                 | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                                                                     | -                   | 0.01                               | -                                  |      |

|                  |                                                   | $\label{eq:VSS} \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ \mbox{All I/Os except for} \\ \mbox{PA11, PA12, BOOT0} \\ \mbox{and FTf I/Os} \end{array}$ | -                   | -                                  | ±50                                |      |

|                  | Input leakage current <sup>(4)</sup>              | $V_{SS} \le V_{IN} \le V_{DD}$ , PA11 and PA12 I/Os                                                                                                           | -                   | -                                  | -50/+250                           | nA   |

|                  |                                                   | $V_{SS} \le V_{IN} \le V_{DD}$<br>FTf I/Os                                                                                                                    | -                   | -                                  | ±100                               |      |

| l <sub>lkg</sub> |                                                   | $\label{eq:VDD} \begin{array}{c} V_{DD}{}^{\leq}V_{IN}{}^{\leq}5V\\ \mbox{All I/Os except for}\\ \mbox{PA11, PA12, BOOT0}\\ \mbox{and FTf I/Os} \end{array}$  | -                   | -                                  | 200                                | nA   |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>FTf I/Os                                                                                                                       | -                   | -                                  | 500                                |      |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>PA11, PA12 and<br>BOOT0                                                                                                        | -                   | -                                  | 10                                 | μΑ   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | V <sub>IN</sub> = V <sub>SS</sub>                                                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                                                                             | -                   | 5                                  | -                                  | pF   |

1. Guaranteed by characterization.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 200 mV. Guaranteed by characterization results.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

Figure 21. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (CMOS I/Os)

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 15$  mA with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 59*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD(Σ)</sub> (see *Table 22*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS(Σ)</sub> (see *Table 22*).

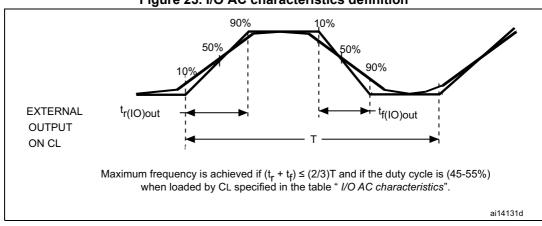

#### Figure 23. I/O AC characteristics definition

## 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$ , except when it is internally driven low (see *Table 61*).

Unless otherwise specified, the parameters given in *Table 61* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| Symbol                                | Parameter                                          | Conditions                                                   | Min      | Тур                               | Max      | Unit |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------------------|----------|-----------------------------------|----------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                       | -                                                            | $V_{SS}$ | -                                 | 0.8      |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high level voltage                      | -                                                            | 1.4      | -                                 | $V_{DD}$ |      |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low level                              | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    |          | 04                                | V        |      |

| VOL(NRST)`´                           | voltage                                            | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -        | -                                 | 0.4      |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage<br>hysteresis         | -                                                            | -        | 10%V <sub>DD</sub> <sup>(2)</sup> | -        | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent<br>resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30       | 45                                | 60       | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                          | -                                                            | -        | -                                 | 50       | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST input not filtered pulse                      | -                                                            | 350      | _                                 | -        | ns   |

| Table | 61          | NRST | nin  | characteristics |

|-------|-------------|------|------|-----------------|

| Table | <b>U</b> 1. |      | pill | Characteristics |

1. Guaranteed by design.

2. 200 mV minimum value

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

#### **USB** characteristics

The USB interface is USB-IF certified (full speed).

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design.

| Symbol                         | Parameter                       | Conditions                                                       | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |  |  |

|--------------------------------|---------------------------------|------------------------------------------------------------------|---------------------|---------------------|------|--|--|--|

| Input levels                   |                                 |                                                                  |                     |                     |      |  |  |  |

| V <sub>DD</sub>                | USB operating voltage           | -                                                                | 3.0                 | 3.6                 | V    |  |  |  |

| V <sub>DI</sub> <sup>(2)</sup> | Differential input sensitivity  | I(USB_DP, USB_DM)                                                | 0.2                 | -                   |      |  |  |  |

| V <sub>CM</sub> <sup>(2)</sup> | Differential common mode range  | Includes V <sub>DI</sub> range                                   | 0.8                 | 2.5                 | V    |  |  |  |

| V <sub>SE</sub> <sup>(2)</sup> | Single ended receiver threshold | -                                                                | 1.3                 | 2.0                 |      |  |  |  |

| Output lev                     | vels                            |                                                                  |                     |                     |      |  |  |  |

| V <sub>OL</sub> <sup>(3)</sup> | Static output level low         | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(4)}$       | -                   | 0.3                 | V    |  |  |  |

| V <sub>OH</sub> <sup>(3)</sup> | Static output level high        | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | 3.6                 | v    |  |  |  |

1. All the voltages are measured from the local ground potential.

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

4.  $\ R_L$  is the load connected on the USB drivers.

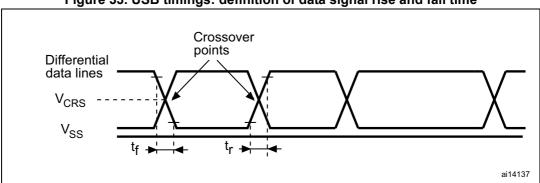

#### Figure 33. USB timings: definition of data signal rise and fall time

#### Table 79. USB: full speed electrical characteristics

| Driver characteristics <sup>(1)</sup> |                                 |                                |     |     |      |  |  |  |  |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|--|--|

| Symbol                                | Parameter                       | Conditions                     | Min | Max | Unit |  |  |  |  |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |

| t <sub>f</sub>                        | Fall Time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |  |

| V <sub>CRS</sub>                      | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

## 6.3.21 LCD controller

The devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the  $V_{DD}$  voltage. An external capacitor  $C_{ext}$  must be connected to the  $V_{LCD}$  pin to decouple this converter.

| Symbol            | Parameter                             | Min | Тур  | Max | Unit |

|-------------------|---------------------------------------|-----|------|-----|------|

| V <sub>LCD</sub>  | LCD external voltage                  | -   | -    | 3.6 |      |

| V <sub>LCD0</sub> | LCD internal reference voltage 0      | -   | 2.6  | -   |      |

| V <sub>LCD1</sub> | LCD internal reference voltage 1      | -   | 2.73 | -   |      |

| V <sub>LCD2</sub> | LCD internal reference voltage 2      | -   | 2.86 | -   |      |

| V <sub>LCD3</sub> | LCD internal reference voltage 3      | -   | 2.98 | -   | V    |

| V <sub>LCD4</sub> | LCD internal reference voltage 4      | -   | 3.12 | -   |      |

| V <sub>LCD5</sub> | LCD internal reference voltage 5      | -   | 3.26 | -   |      |

| V <sub>LCD6</sub> | LCD internal reference voltage 6      | -   | 3.4  | -   |      |

| V <sub>LCD7</sub> | LCD internal reference voltage 7      | -   | 3.55 | -   |      |

| C <sub>ext</sub>  | V <sub>LCD</sub> external capacitance | 0.1 | -    | 2   | μF   |

Table 80. LCD controller characteristics

DocID025660 Rev 6

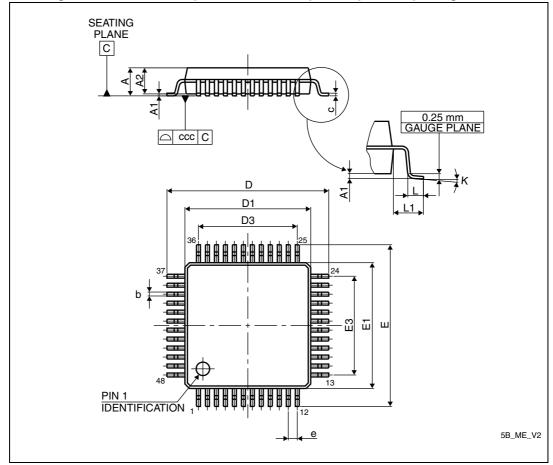

# 7.2 LQFP48 package information

Figure 37. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Date Re     | evision | Changes<br>Removed note 1 in <i>Table 1: Ultra-low-power STM32L063x8 device</i><br><i>features and peripheral counts.</i><br>Updated all pinout/ballout schematics to highlight pin/ball supplied<br>through VDD_USB.<br>Updated current consumption in Run mode in <i>Section : Features</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |         | <i>features and peripheral counts.</i><br>Updated all pinout/ballout schematics to highlight pin/ball supplied through VDD_USB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 08-Sep-2015 | 5       | Renamed BOOT1 into nBOOT1.<br>Changed USART <sub>x</sub> RTS into USART <sub>x</sub> RTS_DE and LPUART <sub>x</sub> RTS<br>into LPUART <sub>x</sub> RTS_DE.<br>Updated VLCD in section Analog to digital converter (ADC).<br>ADC no more available in Low-power run and Low-power Sleep modes<br>in Table 4: Functionalities depending on the working mode (from<br><i>Run/active down to standby</i> ).<br>Updated Figure 4: STM32L063x8 LQFP48 pinout - 7 x 7 mm and<br>Figure 3: STM32L063x8 LQFP44 pinout - 10 x 10 mm. Changed I/O<br>structure for PC5 in Table 15: STM32L063x8 pin definitions.<br>Updated VDD_USB in Table 24: General operating conditions.<br>Changed temperature condition in Table 7: Internal voltage reference<br>measured values and Table 26: Embedded internal reference voltage<br>calibration values.<br>Updated T <sub>Coeff</sub> in Table 27: Embedded internal reference voltage.<br>Added note related to Standby mode in Table 39: Peripheral current<br>consumption in Stop and Standby mode.<br>Updated Figure 13: IDD vs VDD, at TA= 25/55/85/105/125 °C, Low-<br>power run mode, code running from RAM, Range 3, MSI (Range 0) at<br>64 KHz, 0 WS, Figure 14: IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop<br>mode with RTC enabled and running on LSE Low drive and<br>Figure 15: IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with<br>RTC disabled, all clocks off.<br>Updated Table 40: Low-power mode wakeup timings.<br>Updated Table 53: EMS characteristics and Table 54: EMI<br>characteristics.<br>Updated Table 57: I/O current injection susceptibility, Table 58: I/O<br>static characteristics.<br>Updated Table 57: I/O current injection susceptibility, Table 58: I/O<br>static characteristics (I <sub>lkg</sub> ) and Table 60: I/O AC characteristics.<br>Section : Input/output AC characteristics: updated introduction and<br>Table 71: 12C analog filter characteristics:<br>Updated Figure 28: SPI timing diagram - slave mode and CPHA = 0,<br>Table 73: SPI characteristics in voltage Range 1 and Figure 74: SPI<br>characteristics in voltage Range 2 and Table 75: SPI characteristics in<br>voltage Range 3 and Table 76: 12S characteristics.<br>Added Section : Device marking for LQFP |

Table 85. Document revision history (continued)