Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | ARM® Cortex®-M4                                                                |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                          |

| Number of I/O              | 26                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                          |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 32-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l432kbu6tr        |

| Table 43. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)          | 89  |

|-----------|-------------------------------------------------------------------------|-----|

| Table 44. | HSI16 oscillator characteristics.                                       |     |

| Table 45. | MSI oscillator characteristics                                          |     |

| Table 46. | HSI48 oscillator characteristics.                                       |     |

| Table 47. | LSI oscillator characteristics                                          |     |

| Table 48. | PLL, PLLSAI1 characteristics                                            |     |

| Table 49. | Flash memory characteristics                                            |     |

| Table 50. | Flash memory endurance and data retention                               |     |

| Table 51. | EMS characteristics                                                     |     |

| Table 52. | EMI characteristics                                                     |     |

| Table 53. | ESD absolute maximum ratings                                            |     |

| Table 54. | Electrical sensitivities                                                |     |

| Table 55. | I/O current injection susceptibility                                    |     |

| Table 56. | I/O static characteristics                                              |     |

| Table 57. | Output voltage characteristics                                          |     |

| Table 58. | I/O AC characteristics                                                  |     |

| Table 59. | NRST pin characteristics                                                |     |

| Table 60. | Analog switches booster characteristics                                 |     |

| Table 61. | ADC characteristics                                                     |     |

| Table 62. | Maximum ADC RAIN                                                        |     |

| Table 63. | ADC accuracy - limited test conditions 1                                |     |

| Table 64. | ADC accuracy - limited test conditions 2                                |     |

| Table 65. | ADC accuracy - limited test conditions 3                                |     |

| Table 66. | ADC accuracy - limited test conditions 4                                |     |

| Table 67. | DAC characteristics                                                     |     |

| Table 68. | DAC accuracy                                                            |     |

| Table 69. | COMP characteristics                                                    |     |

| Table 70. | OPAMP characteristics                                                   | 127 |

| Table 71. | TS characteristics                                                      | 130 |

| Table 72. | TIMx characteristics                                                    | 130 |

| Table 73. | IWDG min/max timeout period at 32 kHz (LSI)                             | 131 |

| Table 74. | WWDG min/max timeout value at 80 MHz (PCLK)                             | 131 |

| Table 75. | I2C analog filter characteristics                                       |     |

| Table 76. | SPI characteristics                                                     | 133 |

| Table 77. | Quad SPI characteristics in SDR mode                                    | 136 |

| Table 78. | QUADSPI characteristics in DDR mode                                     | 137 |

| Table 79. | SAI characteristics                                                     |     |

| Table 80. | USB electrical characteristics                                          | 141 |

| Table 81. | SWPMI electrical characteristics                                        | 142 |

| Table 82. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|           | package mechanical data                                                 | 144 |

| Table 83. | Package thermal characteristics                                         |     |

| Table 84. | STM32L432xx ordering information scheme                                 |     |

| Table 85. | Document revision history                                               | 148 |

# 3.11 Clocks and startup

The clock controller (see *Figure 3*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock source: four different clock sources can be used to drive the master clock SYSCLK:

- High Speed External clock (HSE) can supply a PLL.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. In this mode the MSI can feed the USB device. The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- RC48 with clock recovery system (HSI48): internal RC48 MHz clock source can be used to drive the USB or the RNG peripherals. This clock can be output on the MCO.

- Auxiliary clock source: two ultralow-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock accuracy is ±5% accuracy.

- Peripheral clock sources: Several peripherals (USB, RNG, SAI, USARTs, I2Cs, LPTimers, ADC, SWPMI) have their own independent clock whatever the system clock. Two PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the USB/RNG and the SAI.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes.

to IWDG LSI RC 32 kHz LSCO to RTC OSC32\_OUT LSE OSC /32 OSC32\_IN LSE LSI HSE мсо / 1→16 to PWR SYSCLK HSI to AHB bus, core, memory and DMA Clock HSI48 source HCLK FCLK Cortex free running clock AHB PRESC control / 1,2,..512 CK\_IN to Cortex system timer HSE Clock detector /8 MSI SYSCLK PCLK1 HSI APB1 PRESC / 1,2,4,8,16 to APB1 peripherals x1 or x2 to TIMx 16 MHz x=2,6,7 LSE HSI SYSCLK to USARTx X=2..3 to LPUART1 HSI-SYSCLK-MSI RC to I2Cx 100 kHz – 48 MHz x=1,2,3 to LPTIMx HSIto SWPMI MSI PCLK2 HSI / M PLL APR2 PRESC HSE to APB2 peripherals PLLSAI1CLK / 1,2,4,8,16 vco F<sub>vcc</sub> / P PLLUSB1CLK /Q x1 or x2 to TIMx PLLCLK x=1,15,16 to USART1 PLLSAI1 PLLSAI2CLK VCO F<sub>VCO</sub> / P PLLUSB2CLK /Q 48 MHz clock to USB, RNG PLLADC1CLK SYSCLK to ADC HSI HSI RC 48 MHz to SAI1 HSI CRS SAI1 EXTCLK MSv39217V3

Figure 3. Clock tree

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous/ one shot mode

- Selectable software/hardware input trigger

- Selectable clock source

- Internal clock sources: LSE, LSI, HSI16 or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by pulse counter application).

- Programmable digital glitch filter

- Encoder mode (LPTIM1 only)

#### 3.21.5 Infrared interface (IRTIM)

The STM32L432xx includes one infrared interface (IRTIM). It can be used with an infrared LED to perform remote control functions. It uses TIM15 and TIM16 output channels to generate output signal waveforms on IR OUT pin.

#### 3.21.6 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC (LSI) and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.21.7 System window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.21.8 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

# 4 Pinouts and pin description

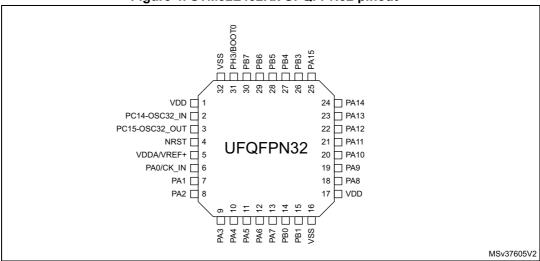

Figure 4. STM32L432Kx UFQFPN32 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

Table 12. Legend/abbreviations used in the pinout table

| Na        | me                   | Abbreviation                                                     | Definition                                                                 |  |  |  |  |

|-----------|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| Pin r     | name                 | Unless otherwise specified in reset is the same as the actu      | brackets below the pin name, the pin function during and after al pin name |  |  |  |  |

|           |                      | S                                                                | Supply pin                                                                 |  |  |  |  |

| Pin       | type                 | I                                                                | Input only pin                                                             |  |  |  |  |

|           |                      | I/O                                                              | Input / output pin                                                         |  |  |  |  |

|           |                      | FT                                                               | 5 V tolerant I/O                                                           |  |  |  |  |

|           |                      | TT                                                               | 3.6 V tolerant I/O                                                         |  |  |  |  |

|           |                      | RST                                                              | Bidirectional reset pin with embedded weak pull-up resistor                |  |  |  |  |

| I/O str   | ructure              | Option for TT or FT I/Os                                         |                                                                            |  |  |  |  |

|           |                      | _f <sup>(1)</sup>                                                | I/O, Fm+ capable                                                           |  |  |  |  |

|           |                      | _u <sup>(2)</sup>                                                | I/O, with USB function supplied by V <sub>DDUSB</sub>                      |  |  |  |  |

|           |                      | _a <sup>(3)</sup>                                                | I/O, with Analog switch function supplied by V <sub>DDA</sub>              |  |  |  |  |

| No        | otes                 | Unless otherwise specified by                                    | y a note, all I/Os are set as analog inputs during and after reset.        |  |  |  |  |

| Pin       | Alternate functions  | Functions selected through GPIOx_AFR registers                   |                                                                            |  |  |  |  |

| functions | Additional functions | Functions directly selected/enabled through peripheral registers |                                                                            |  |  |  |  |

- 1. The related I/O structures in *Table 13* are: FT\_f, FT\_fa.

- 2. The related I/O structures in Table 13 is: FT\_u.

- 3. The related I/O structures in *Table 13* are: FT\_a, FT\_fa, TT\_a.

57

Table 13. STM32L432xx pin definitions (continued)

| Pin      |                                       |          |               |       | L432XX pm dennitions (con                                                                                                  | · · ·                |

|----------|---------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------|----------------------|

| Number   | e<br>ifter                            |          |               |       | Pin func                                                                                                                   | tions                |

| UFQFPN32 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                        | Additional functions |

| 24       | PA14<br>(JTCK-<br>SWCLK)              | I/O      | FT            | (3)   | JTCK-SWCLK, LPTIM1_OUT,<br>I2C1_SMBA, SWPMI1_RX,<br>SAI1_FS_B, EVENTOUT                                                    | -                    |

| 25       | PA15<br>(JTDI)                        | I/O      | FT            | (3)   | JTDI, TIM2_CH1, TIM2_ETR, USART2_RX, SPI1_NSS, SPI3_NSS, USART3_RTS_DE, TSC_G3_IO1, SWPMI1_SUSPEND, EVENTOUT               | -                    |

| 26       | PB3<br>(JTDO-<br>TRACE<br>SWO)        | I/O      | FT_a          | (3)   | JTDO-TRACESWO, TIM2_CH2, SPI1_SCK, SPI3_SCK, USART1_RTS_DE, SAI1_SCK_B, EVENTOUT                                           | COMP2_INM            |

| 27       | PB4<br>(NJTRST)                       | I/O      | FT_fa         | (3)   | NJTRST, I2C3_SDA, SPI1_MISO, SPI3_MISO, USART1_CTS, TSC_G2_IO1, SAI1_MCLK_B, EVENTOUT                                      | COMP2_INP            |

| 28       | PB5                                   | I/O      | FT            | 1     | LPTIM1_IN1, I2C1_SMBA,<br>SPI1_MOSI, SPI3_MOSI,<br>USART1_CK, TSC_G2_IO2,<br>COMP2_OUT, SAI1_SD_B,<br>TIM16_BKIN, EVENTOUT | -                    |

| 29       | PB6                                   | I/O      | FT_fa         | ı     | LPTIM1_ETR, I2C1_SCL,<br>USART1_TX, TSC_G2_IO3,<br>SAI1_FS_B, TIM16_CH1N,<br>EVENTOUT                                      | COMP2_INP            |

| 30       | PB7                                   | I/O      | FT_fa         | -     | LPTIM1_IN2, I2C1_SDA,<br>USART1_RX, TSC_G2_IO4,<br>EVENTOUT                                                                | COMP2_INM, PVD_IN    |

| 31       | PH3/<br>BOOT0                         | I/O      | FT            | -     | EVENTOUT                                                                                                                   | воото                |

| 32       | VSS                                   | S        | -             | -     | -                                                                                                                          | -                    |

| 1        | VDD                                   | S        | -             | -     | -                                                                                                                          | -                    |

PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC14 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After reset, these pins are configured as JTAG/SW debug alternate functions, and the internal pull-up on PA15, PA13, PB4 pins and the internal pull-down on PA14 pin are activated.

After a Backup domain power-up, PC14 and PC15 operate as GPIOs. Their function then depends on the

content of the RTC registers which are not reset by the system reset. For details on how to manage these

GPIOs, refer to the Backup domain and RTC register descriptions in the RM0393 reference manual.

Table 15. Alternate function AF8 to AF15 (for AF0 to AF7 see Table 14)

|        |      | AF8         | AF9        | AF10                | AF11 | AF12                       | AF13        | AF14                        | AF15     |

|--------|------|-------------|------------|---------------------|------|----------------------------|-------------|-----------------------------|----------|

| Po     | ort  | LPUART1     | CAN1/TSC   | USB/QUADSPI         | -    | COMP1/<br>COMP2/<br>SWPMI1 | SAI1        | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |

|        | PA0  | -           | -          | -                   | -    | COMP1_OUT                  | SAI1_EXTCLK | TIM2_ETR                    | EVENTOUT |

|        | PA1  | -           | -          | -                   | -    | -                          | -           | TIM15_CH1N                  | EVENTOUT |

|        | PA2  | LPUART1_TX  | -          | QUADSPI_<br>BK1_NCS | -    | COMP2_OUT                  | -           | TIM15_CH1                   | EVENTOUT |

|        | PA3  | LPUART1_RX  | -          | QUADSPI_CLK         | -    | -                          | SAI1_MCLK_A | TIM15_CH2                   | EVENTOUT |

|        | PA4  | -           | -          | -                   | -    | -                          | SAI1_FS_B   | LPTIM2_OUT                  | EVENTOUT |

|        | PA5  | -           | -          | -                   | -    | -                          | -           | LPTIM2_ETR                  | EVENTOUT |

|        | PA6  | LPUART1_CTS | -          | QUADSPI_<br>BK1_IO3 | -    | TIM1_BKIN_<br>COMP2        | -           | TIM16_CH1                   | EVENTOUT |

| Port A | PA7  | -           | -          | QUADSPI_<br>BK1_IO2 | -    | COMP2_OUT                  | -           | -                           | EVENTOUT |

| POILA  | PA8  | -           | -          | -                   | -    | SWPMI1_IO                  | SAI1_SCK_A  | LPTIM2_OUT                  | EVENTOUT |

|        | PA9  | -           | -          | -                   | -    | -                          | SAI1_FS_A   | TIM15_BKIN                  | EVENTOUT |

|        | PA10 | -           | -          | USB_CRS_<br>SYNC    | -    | -                          | SAI1_SD_A   | -                           | EVENTOUT |

|        | PA11 | -           | CAN1_RX    | USB_DM              | -    | TIM1_BKIN2_<br>COMP1       | -           | -                           | EVENTOUT |

|        | PA12 | -           | CAN1_TX    | USB_DP              | -    | -                          | -           | -                           | EVENTOUT |

|        | PA13 | -           | -          | USB_NOE             | -    | SWPMI1_TX                  | SAI1_SD_B   | -                           | EVENTOUT |

|        | PA14 | -           | -          | -                   | -    | SWPMI1_RX                  | SAI1_FS_B   | -                           | EVENTOUT |

|        | PA15 | -           | TSC_G3_IO1 | -                   | -    | SWPMI1_<br>SUSPEND         | -           | -                           | EVENTOUT |

# 5 Memory mapping

0xFFFF FFFF 0xBFFF FFFF Reserved Cortex™-M4 0xA000 1400 with FPU 7 **QUADSPI** registers Internal 0xA000 1000 Peripherals 0xE000 0000 0x5FFF FFFF Reserved 6 0x5006 0C00 AHB2 0x4800 0000 0xC000 0000 Reserved 0x4002 4400 **QUADSPI** AHB1 registers 5 0x4002 0000 Reserved 0xA000 1000 0x4001 5800 APB2 0xA000 0000 0x4001 0000 QUADSPI Flash Reserved bank 0x4000 9800 0x9000 0000 APB1 0x4000 0000 0x1FFF FFFF 0x8000 0000 3 Reserved 0x6000 0000 0x1FFF 7810 Options Bytes 2 0x1FFF 7800 Reserved 0x1FFF 7400 Peripherals OTP area 0x4000 0000 0x1FFF 7000 System memory 1 0x1FFF 0000 SRAM2 Reserved 0x2000 C000 0x1000 4000 SRAM1 SRAM2 0x2000 0000 0x1000 0000 Reserved 0 0x0804 0000 CODE Flash memory 0x0800 0000 Reserved 0x0000 0000 0x0004 0000 Flash, system memory or SRAM, depending on BOOT configuration 0x0000 0000 Reserved MSv36892V2

Figure 5. STM32L432xx memory map

# 6.3 Operating conditions

# 6.3.1 General operating conditions

Table 20. General operating conditions

| Symbol             | Parameter                                                                                       | Conditions                           | Min             | Max                                                                                                          | Unit |

|--------------------|-------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                    | -                                    | 0               | 80                                                                                                           |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                   | -                                    | 0               | 80                                                                                                           | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                   | -                                    | 0               | 80                                                                                                           |      |

| V <sub>DD</sub>    | Standard operating voltage                                                                      | -                                    | 1.71            | 3.6                                                                                                          | V    |

|                    |                                                                                                 | ADC or COMP used                     | 1.62            |                                                                                                              |      |

| $V_{DDA}$          | Analog supply voltage                                                                           | DAC or OPAMP used                    | 1.8             | 3.6                                                                                                          | V    |

| - DDA              | Thanks outpry, Tollago                                                                          | ADC, DAC, OPAMP, COMP not used       | 0               | 5.5                                                                                                          | -    |

| V                  | LICD complete selfore                                                                           | USB used                             | 3.0             | 3.6                                                                                                          | V    |

| $V_{DDUSB}$        | USB supply voltage                                                                              | USB not used                         | 0               | 3.6                                                                                                          | ] V  |

|                    |                                                                                                 | TT_xx I/O                            | -0.3            | V <sub>DDIOx</sub> +0.3                                                                                      |      |

| V <sub>IN</sub> I  | I/O input voltage                                                                               | All I/O except TT_xx                 | -0.3            | $\begin{array}{c} {\rm MIN(MIN(V_{DD},V_{DDA},}\\ {\rm V_{DDUSB})+3.6V,}\\ {\rm 5.5V)^{(2)(3)}} \end{array}$ | V    |

| $P_D$              | Power dissipation at T <sub>A</sub> = 125 °C for suffix 3 <sup>(4)</sup>                        | UFQFPN32                             | -               | 128                                                                                                          | mW   |

| P <sub>D</sub>     | Power dissipation at<br>$T_A = 85$ °C for suffix 6<br>or<br>$T_A = 105$ °C for suffix $7^{(4)}$ | UFQFPN32                             | -               | 523                                                                                                          | mW   |

|                    | Ambient temperature for the                                                                     | Maximum power dissipation            | <del>-4</del> 0 | 85                                                                                                           |      |

|                    | suffix 6 version                                                                                | Low-power dissipation <sup>(5)</sup> | -40             | 105                                                                                                          |      |

| TA                 | Ambient temperature for the                                                                     | Maximum power dissipation            | -40             | 105                                                                                                          | °C   |

| IA                 | suffix 7 version                                                                                | Low-power dissipation <sup>(5)</sup> | -40             | 125                                                                                                          |      |

|                    | Ambient temperature for the                                                                     | Maximum power dissipation            | -40             | 125                                                                                                          | 1    |

|                    | suffix 3 version                                                                                | Low-power dissipation <sup>(5)</sup> | -40             | 130                                                                                                          |      |

|                    |                                                                                                 | Suffix 6 version                     | <del>-4</del> 0 | 105                                                                                                          |      |

| $T_J$              | Junction temperature range                                                                      | Suffix 7 version                     | <del>-4</del> 0 | 125                                                                                                          | °C   |

|                    |                                                                                                 | Suffix 3 version                     | -40             | 130                                                                                                          |      |

<sup>1.</sup> When RESET is released functionality is guaranteed down to  $\rm V_{\rm BOR0}$  Min.

<sup>2.</sup> This formula has to be applied only on the power supplies related to the IO structure described by the pin definition table. Maximum I/O input voltage is the smallest value between MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDUSB}$ )+3.6 V and 5.5V.

<sup>3.</sup> For operation with voltage higher than Min (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

<sup>4.</sup> If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.2: Thermal characteristics).

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 9: Current consumption measurement scheme*.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted with the minimum wait states number, depending on the f<sub>HCLK</sub> frequency (refer to the table "Number of wait states according to CPU clock (HCLK) frequency" available in the RM0393 reference manual).

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 24* to *Table 36* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

Table 31. Current consumption in Low-power sleep modes, Flash in power-down

|                          | Symbol Parameter        | Conditions                                            |                 | ТҮР               |       |       |       | MAX <sup>(1)</sup> |        |       |       |       |        |        |      |

|--------------------------|-------------------------|-------------------------------------------------------|-----------------|-------------------|-------|-------|-------|--------------------|--------|-------|-------|-------|--------|--------|------|

| Symbol                   |                         | -                                                     | Voltage scaling | f <sub>HCLK</sub> | 25 °C | 55 °C | 85 °C | 105 °C             | 125 °C | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | Unit |

|                          |                         |                                                       |                 | 2 MHz             | 58.7  | 70.7  | 103.2 | 153.7              | 248.5  | 80    | 113   | 180   | 330    | 641    |      |

| I <sub>DD</sub> (LPSleep | in low nower            | Supply current   f <sub>HCLK</sub> = f <sub>MSI</sub> |                 | 1 MHz             | 39.4  | 47.2  | 79.3  | 129.6              | 224.8  | 53    | 86    | 154   | 304    | 616    | μA   |

| sleep mode               | all peripherals disable | 400 kHz                                               | 20.8            | 30.8              | 62.1  | 112.5 | 207.8 | 35                 | 67     | 137   | 286   | 597   | μΛ     |        |      |

|                          |                         |                                                       |                 | 100 kHz           | 14.3  | 23.1  | 55.1  | 105.7              | 201.5  | 27    | 58    | 130   | 279    | 590    |      |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

Table 32. Current consumption in Stop 2 mode

| Symbol                   | Parameter                      | Conditions                                                 |                 |       |       | TYP   |        |        | MAX <sup>(1)</sup> |       |       |        |        | Unit |

|--------------------------|--------------------------------|------------------------------------------------------------|-----------------|-------|-------|-------|--------|--------|--------------------|-------|-------|--------|--------|------|

| Symbol Parameter         |                                | -                                                          | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C              | 55 °C | 85 °C | 105 °C | 125 °C | Unit |

|                          |                                |                                                            | 1.8 V           | 1     | 2.54  | 8.74  | 19.8   | 43.4   | 2.0                | 5.6   | 21.1  | 50.8   | 116.0  |      |

| I <sub>DD</sub> (Stop 2) | Supply current in Stop 2 mode, |                                                            | 2.4 V           | 1.02  | 2.59  | 8.89  | 20.2   | 44.3   | 2.1                | 5.8   | 21.6  | 52.3   | 119.6  | μA   |

| IDD (Glob 2)             | RTC disabled                   | -                                                          | 3 V             | 1.06  | 2.67  | 9.11  | 20.7   | 45.5   | 2.1                | 5.9   | 22.2  | 53.7   | 123.2  | μΛ   |

|                          |                                |                                                            | 3.6 V           | 1.23  | 2.88  | 9.56  | 21.6   | 47.3   | 2.3                | 6.1   | 23.0  | 55.8   | 127.9  |      |

|                          |                                |                                                            | 1.8 V           | 1.3   | 2.82  | 9.02  | 20.1   | 43.6   | 2.5                | 6.2   | 21.6  | 51.3   | 116.3  |      |

|                          |                                | RTC clocked by LSI                                         | 2.4 V           | 1.39  | 2.95  | 9.24  | 20.5   | 44.6   | 2.8                | 6.4   | 22.3  | 52.8   | 120.0  |      |

|                          |                                |                                                            | 3 V             | 1.5   | 3.11  | 9.55  | 21.1   | 45.8   | 3.0                | 6.8   | 23.0  | 54.5   | 123.8  |      |

|                          |                                |                                                            | 3.6 V           | 1.76  | 3.42  | 10.1  | 22.1   | 47.8   | 3.3                | 7.2   | 24.1  | 56.7   | 128.7  |      |

|                          |                                |                                                            | 1.8 V           | 1.36  | 2.9   | 9.1   | 20.1   | 43.7   | -                  | -     | -     | -      | -      |      |

| I <sub>DD</sub> (Stop 2  | Supply current in Stop 2 mode, | RTC clocked by LSE                                         | 2.4 V           | 1.48  | 3.09  | 9.44  | 20.8   | 45     | -                  | -     | -     | -      | -      | μA   |

| with RTC)                | RTC enabled                    | bypassed at 32768 Hz                                       | 3 V             | 1.83  | 3.67  | 10.4  | 22.3   | 47.3   | -                  | -     | -     | -      | -      | μΛ   |

|                          |                                |                                                            | 3.6 V           | 3.58  | 6.17  | 13.9  | 26.6   | 53     | -                  | -     | -     | -      | -      |      |

|                          |                                |                                                            | 1.8 V           | 1.28  | 2.81  | 9.13  | 20.8   | -      | -                  | -     | -     | -      | -      |      |

|                          |                                | RTC clocked by LSE quartz <sup>(2)</sup> in low drive mode | 2.4 V           | 1.39  | 2.93  | 9.34  | 21.3   | -      | -                  | -     | -     | -      | -      |      |

|                          |                                |                                                            | 3 V             | 1.59  | 3.1   | 9.64  | 21.8   | -      | -                  | -     | -     | -      | -      |      |

|                          |                                |                                                            | 3.6 V           | 1.86  | 3.45  | 10.2  | 22.8   | -      | -                  | -     | -     | -      | -      |      |

| Table 46. HSI48 oscillator | characteristics(1) | (continued) |

|----------------------------|--------------------|-------------|

|----------------------------|--------------------|-------------|

| Symbol                | Parameter                                                                  | Conditions | Min | Тур                    | Max | Unit |

|-----------------------|----------------------------------------------------------------------------|------------|-----|------------------------|-----|------|

| N <sub>T</sub> jitter | Next transition jitter<br>Accumulated jitter on 28 cycles <sup>(4)</sup>   | -          | -   | +/-0.15 <sup>(2)</sup> | -   | ns   |

| P <sub>T</sub> jitter | Paired transition jitter<br>Accumulated jitter on 56 cycles <sup>(4)</sup> | -          | -   | +/-0.25 <sup>(2)</sup> | -   | ns   |

- 1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 125°C unless otherwise specified.

- 2. Guaranteed by design.

- 3. Guaranteed by characterization results.

- 4. Jitter measurement are performed without clock source activated in parallel.

Figure 16. HSI48 frequency versus temperature 6 4 2 0 -2 -6 -50 -30 70 -10 10 30 50 90 110 130 °C --- Avg --- min - max MSv40989V1

Low-speed internal (LSI) RC oscillator

Table 47. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                                 | Parameter                         | Conditions                                      | Min  | Тур | Max   | Unit  |

|----------------------------------------|-----------------------------------|-------------------------------------------------|------|-----|-------|-------|

| f <sub>LSI</sub>                       | I SI Fraguency                    | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C |      | -   | 32.96 | kHz   |

|                                        | LSI Frequency                     | $V_{DD}$ = 1.62 to 3.6 V, TA = -40 to 125 °C    | 29.5 | -   | 34    | KI IZ |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time  | -                                               | 1    | 80  | 130   | μs    |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator stabilization time | 5% of final frequency                           | 1    | 125 | 180   | μs    |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption  | -                                               | -    | 110 | 180   | nA    |

- 1. Guaranteed by characterization results.

- 2. Guaranteed by design.

### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                            | Monitored frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |  |

|------------------|------------|-------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------|------|--|

|                  |            |                                                                                                       | moquonoy bana            | 8 MHz/ 80 MHz                                     |      |  |

|                  |            | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C,<br>UFQFPN32 package<br>compliant with IEC<br>61967-2 | 0.1 MHz to 30 MHz        | 1                                                 |      |  |

|                  |            |                                                                                                       | 30 MHz to 130 MHz        | 0                                                 | dΒμV |  |

| S <sub>EMI</sub> | Peak level |                                                                                                       | 130 MHz to 1 GHz         | -1                                                |      |  |

|                  |            |                                                                                                       | 1 GHz to 2 GHz           | 7                                                 |      |  |

|                  |            |                                                                                                       | EMI Level                | 1                                                 | -    |  |

Table 52. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Conditions                                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESDA/JEDEC<br>JS-001 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C,<br>conforming to ANSI/ESD<br>STM5.3.1      | C3    | 250                             | V    |

Table 53. ESD absolute maximum ratings

<sup>1.</sup> Guaranteed by characterization results.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOX</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 17: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see Table 17: Voltage characteristics).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT OR TT unless otherwise specified).

Table 57. Output voltage characteristics<sup>(1)</sup>

| Symbol                         | Parameter                                                                       | Conditions                                                                | Min                      | Max               | Unit |

|--------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------|-------------------|------|

| V <sub>OL</sub>                | Output low level voltage for an I/O pin                                         | CMOS port <sup>(2)</sup>                                                  | -                        | 0.4               |      |

| V <sub>OH</sub>                | Output high level voltage for an I/O pin                                        | I <sub>IO</sub>   = 8 mA<br> V <sub>DDIOx</sub> ≥ 2.7 V                   | V <sub>DDIOx</sub> -0.4  | -                 |      |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | TTL port <sup>(2)</sup>                                                   | -                        | 0.4               |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | I <sub>IO</sub>   = 8 mA<br> V <sub>DDIOx</sub> ≥ 2.7 V                   | 2.4                      | -                 |      |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | I <sub>IO</sub>   = 20 mA                                                 | -                        | 1.3               |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | V <sub>DDIOx</sub> ≥ 2.7 V                                                | V <sub>DDIOx</sub> -1.3  | -                 |      |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | I <sub>IO</sub>   = 4 mA                                                  | -                        | 0.45              |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | V <sub>DDIOx</sub> ≥ 1.62 V                                               | V <sub>DDIOx</sub> -0.45 | -                 | V    |

| V <sub>OL</sub> <sup>(3)</sup> | Output low level voltage for an I/O pin                                         | I <sub>IO</sub>   = 2 mA                                                  | -                        | $0.35_xV_{DDIOx}$ |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin                                        | 1.62 V ≥ V <sub>DDIOx</sub> ≥ 1.08 V                                      | $0.65_xV_{DDIOx}$        | -                 |      |

|                                | Output low level voltage for an FT I/O pin in FM+ mode (FT I/O with "f" option) | $ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$               | -                        | 0.4               |      |

| V <sub>OLFM+</sub>             |                                                                                 | I <sub>IO</sub>   = 10 mA<br>V <sub>DDIOx</sub> ≥ 1.62 V                  | -                        | 0.4               |      |

|                                |                                                                                 | $ I_{IO}  = 2 \text{ mA}$<br>1.62 V $\ge$ V <sub>DDIOX</sub> $\ge$ 1.08 V | -                        | 0.4               |      |

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 17:

Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 18* and *Table 58*, respectively.

<sup>2.</sup> TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

<sup>3.</sup> Guaranteed by design.

Table 66. ADC accuracy - limited test conditions 4<sup>(1)(2)(3)</sup>

| Sym-<br>bol | Parameter                          | (                                                                                                  | Conditions <sup>(4)</sup> |                                       |      | Тур  | Max | Unit  |

|-------------|------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------|------|------|-----|-------|

|             |                                    | Singl                                                                                              |                           | Fast channel (max speed)              |      | 5    | 5.4 |       |

| ET          | Total                              |                                                                                                    | ended                     | Slow channel (max speed)              | -    | 4    | 5   |       |

|             | unadjusted<br>error                |                                                                                                    | Differential              | Fast channel (max speed)              | -    | 4    | 5   |       |

|             |                                    |                                                                                                    | Dillerential              | Slow channel (max speed)              | -    | 3.5  | 4.5 |       |

|             |                                    |                                                                                                    | Single                    | Fast channel (max speed)              | -    | 2    | 4   |       |

| EO          | Offset                             |                                                                                                    | ended                     | Slow channel (max speed)              | -    | 2    | 4   |       |

|             | error                              |                                                                                                    | Differential              | Fast channel (max speed)              | -    | 2    | 3.5 |       |

|             |                                    |                                                                                                    | Dillerential              | Slow channel (max speed)              | -    | 2    | 3.5 |       |

|             |                                    |                                                                                                    | Single                    | Fast channel (max speed)              | -    | 4    | 4.5 |       |

| EG          | Gain error                         |                                                                                                    | ended                     | Slow channel (max speed)              | -    | 4    | 4.5 | LCD   |

| EG          | Gain enoi                          | ADC clock frequency ≤ 26 MHz, - 1.65 V ≤ V <sub>DDA</sub> = VREF+ ≤ 3.6 V, Voltage scaling Range 2 | Differential              | Fast channel (max speed)              | -    | 3    | 4   | - LSB |

|             |                                    |                                                                                                    | Dillerential              | Slow channel (max speed)              | -    | 3    | 4   |       |

|             |                                    |                                                                                                    | Single                    | Fast channel (max speed)              | -    | 1    | 1.5 |       |

|             | Differential<br>linearity<br>error |                                                                                                    | ended                     | Slow channel (max speed)              | -    | 1    | 1.5 |       |

|             |                                    |                                                                                                    | Differential              | Fast channel (max speed)              | -    | 1    | 1.2 |       |

|             |                                    |                                                                                                    |                           | Slow channel (max speed)              | -    | 1    | 1.2 |       |

|             | Integral<br>linearity<br>error     |                                                                                                    | Single<br>ended           | Fast channel (max speed)              | -    | 2.5  | 3   |       |

| EL          |                                    |                                                                                                    |                           | Slow channel (max speed)              | -    | 2.5  | 3   |       |

|             |                                    |                                                                                                    | Differential              | Fast channel (max speed)              | -    | 2    | 2.5 |       |

|             |                                    |                                                                                                    |                           | Slow channel (max speed)              | -    | 2    | 2.5 |       |

|             |                                    | interestive sumber of                                                                              | Single<br>ended           | Fast channel (max speed)              | 10.2 | 10.5 | -   |       |

| ENOB        | Effective                          |                                                                                                    |                           | Slow channel (max speed)              | 10.2 | 10.5 | -   | bits  |

| LINOB       | bits                               |                                                                                                    | Differential              | Fast channel (max speed)              | 10.6 | 10.7 | ı   | Dita  |

|             |                                    |                                                                                                    | Dillerential              | Slow channel (max speed)              | 10.6 | 10.7 | -   | 1     |

|             | Signal-to-                         |                                                                                                    | Single                    | Fast channel (max speed)              | 63   | 65   | -   |       |

| SINAD       | noise and                          |                                                                                                    | ended                     | Slow channel (max speed)              | 63   | 65   | ı   |       |

| OIIVAD      | distortion ratio                   |                                                                                                    | Differential              | Fast channel (max speed)              | 65   | 66   | ı   |       |

|             | Tatio                              |                                                                                                    | Dillerential              | Slow channel (max speed)              | 65   | 66   | -   | dB    |

|             |                                    |                                                                                                    | Single                    | Fast channel (max speed)              | 64   | 65   | -   | ub    |

| SNR         | Signal-to-                         |                                                                                                    | ended                     | Slow channel (max speed)              | 64   | 65   | ı   | ]     |

| SINIX       | noise ratio                        |                                                                                                    | Differential              | Fast channel (max speed)              | 66   | 67   | -   |       |

|             |                                    |                                                                                                    | Dilletetilial             | Differential Slow channel (max speed) | 66   | 67   | -   |       |

-73

-72

|                               | (community) |                                                |                          |                          |     |     |     |      |  |  |

|-------------------------------|-------------|------------------------------------------------|--------------------------|--------------------------|-----|-----|-----|------|--|--|

| Sym-<br>bol                   | Parameter   | Conditions <sup>(4)</sup>                      |                          |                          |     |     | Max | Unit |  |  |

|                               |             | ADC clock frequency ≤                          | Single                   | Fast channel (max speed) | -   | -71 | -69 |      |  |  |

| THD Total harmonic distortion | ,           | 26 MHz,<br>1.65 V ≤ V <sub>DDA</sub> = VREF+ ≤ | ended                    | Slow channel (max speed) |     | -71 | -69 | dB   |  |  |

|                               | 3.6  V,     | Differential                                   | Fast channel (max speed) | -                        | -73 | -72 | uБ  |      |  |  |

|                               | 1           | 1                                              | Dinordinal               |                          |     |     |     |      |  |  |

Slow channel (max speed)

Table 66. ADC accuracy - limited test conditions  $4^{(1)(2)(3)}$  (continued)

- Guaranteed by design.

- ADC DC accuracy values are measured after internal calibration. 2.

Voltage scaling Range 2

- ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- The I/O analog switch voltage booster is enable when  $V_{DDA}$  < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when  $V_{DDA}$  < 2.4 V). It is disable when  $V_{DDA} \ge 2.4$  V. No oversampling.

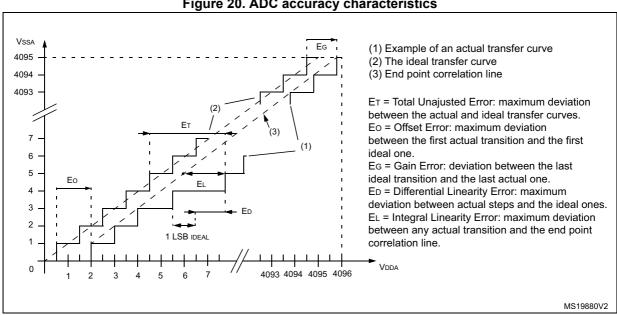

Figure 20. ADC accuracy characteristics

Table 67. DAC characteristics<sup>(1)</sup> (continued)

| Symbol                 | Parameter                                                                           |                                                                       | enditions                                          | Min | Тур                                           | Max                                | Unit |

|------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|-----|-----------------------------------------------|------------------------------------|------|

| <sup>t</sup> SAMP      | Sampling time in sample and hold mode (code transition between the                  |                                                                       | DAC output buffer<br>ON, C <sub>SH</sub> = 100 nF  | -   | 0.7                                           | 3.5                                | ms   |

|                        |                                                                                     |                                                                       | DAC output buffer<br>OFF, C <sub>SH</sub> = 100 nF | ı   | 10.5                                          | 18                                 |      |

|                        | lowest input code and the highest input code when DACOUT reaches final value ±1LSB) | DAC_OUT<br>pin not<br>connected<br>(internal<br>connection<br>only)   | DAC output buffer<br>OFF                           | 1   | 2                                             | 3.5                                | μs   |

| I <sub>leak</sub>      | Output leakage current                                                              | Sample and ho DAC_OUT pin                                             |                                                    | -   | -                                             | _(3)                               | nA   |

| Cl <sub>int</sub>      | Internal sample and hold capacitor                                                  |                                                                       | -                                                  | 5.2 | 7                                             | 8.8                                | pF   |

| t <sub>TRIM</sub>      | Middle code offset trim time                                                        | DAC output bu                                                         | ffer ON                                            | 50  | -                                             | -                                  | μs   |

|                        | Middle code offset for 1                                                            | V <sub>REF+</sub> = 3.6 V                                             |                                                    | -   | 1500                                          | -                                  | μV   |

| V <sub>offset</sub>    | trim code step                                                                      | V <sub>REF+</sub> = 1.8 V                                             |                                                    | -   | 750                                           | -                                  | μν   |

|                        | DAC consumption from V <sub>DDA</sub>                                               | DAC output<br>buffer ON                                               | No load, middle code (0x800)                       | -   | 315                                           | 500                                | μΑ   |

|                        |                                                                                     |                                                                       | No load, worst code (0xF1C)                        | ı   | 450                                           | 670                                |      |

| I <sub>DDA</sub> (DAC) |                                                                                     | DAC output buffer OFF                                                 | No load, middle code (0x800)                       | -   | -                                             | 0.2                                |      |

|                        |                                                                                     | Sample and hold mode, C <sub>SH</sub> = 100 nF                        |                                                    | 1   | 315 <sub>x</sub><br>Ton/(Ton<br>+Toff)<br>(4) | 670 x<br>Ton/(Ton<br>+Toff)<br>(4) |      |

|                        | DAC consumption from V <sub>REF+</sub>                                              | DAC output<br>buffer ON                                               | No load, middle code (0x800)                       | -   | 185                                           | 240                                |      |

|                        |                                                                                     |                                                                       | No load, worst code (0xF1C)                        | -   | 340                                           | 400                                |      |

| I <sub>DDV</sub> (DAC) |                                                                                     | DAC output buffer OFF                                                 | No load, middle code (0x800)                       | -   | 155                                           | 205                                |      |

|                        |                                                                                     | Sample and hold mode, buffer ON, C <sub>SH</sub> = 100 nF, worst case |                                                    | -   | 185 <sub>x</sub><br>Ton/(Ton<br>+Toff)<br>(4) | 400 x<br>Ton/(Ton<br>+Toff)<br>(4) | μА   |

|                        |                                                                                     | Sample and ho<br>C <sub>SH</sub> = 100 nF,                            | old mode, buffer OFF,<br>worst case                | -   | 155 x<br>Ton/(Ton<br>+Toff)<br>(4)            | 205 x<br>Ton/(Ton<br>+Toff)<br>(4) |      |

<sup>1.</sup> Guaranteed by design.

<sup>2.</sup> In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

# Table 75. I2C analog filter characteristics<sup>(1)</sup>

| Symbol          | Parameter                                                              | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

- 1. Guaranteed by design.

- 2. Spikes with widths below  $t_{\mbox{\scriptsize AF}(\mbox{\scriptsize min})}$  are filtered.

- 3. Spikes with widths above  $t_{\text{AF}(\text{max})}$  are not filtered

| Table 73. OAI characteristics (continued) |                        |                                                                  |                  |      |      |  |  |  |  |

|-------------------------------------------|------------------------|------------------------------------------------------------------|------------------|------|------|--|--|--|--|

| Symbol                                    | Parameter Conditions   |                                                                  | Min              | Max  | Unit |  |  |  |  |

| t <sub>v(SD_B_ST)</sub>                   | Data output valid time | Slave transmitter (after enable edge) $2.7 \le V_{DD} \le 3.6$   |                  | 22   | ns   |  |  |  |  |

|                                           |                        | Slave transmitter (after enable edge) $1.71 \le V_{DD} \le 3.6$  | i                | 34   | 115  |  |  |  |  |

| t <sub>h(SD_B_ST)</sub>                   | Data output hold time  | Slave transmitter (after enable edge)                            | 10               | -    | ns   |  |  |  |  |

| t <sub>v(SD_A_MT)</sub>                   | Data output valid time | Master transmitter (after enable edge) $2.7 \le V_{DD} \le 3.6$  | enable edge) - 2 |      | - ns |  |  |  |  |

|                                           |                        | Master transmitter (after enable edge) $1.71 \le V_{DD} \le 3.6$ | -                | - 40 |      |  |  |  |  |

| t <sub>h(SD_A_MT)</sub>                   | Data output hold time  | Master transmitter (after enable edge)                           | 10               | -    | ns   |  |  |  |  |

Table 79. SAI characteristics<sup>(1)</sup> (continued)

- 1. Guaranteed by characterization results.

- 2. APB clock frequency must be at least twice SAI clock frequency.

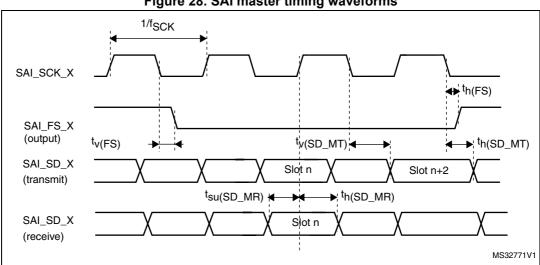

Figure 28. SAI master timing waveforms

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved