Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | ARM® Cortex®-M4                                                                |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                          |

| Number of I/O              | 26                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                          |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 32-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l432kcu3          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of tables

| Table 1.  | STM32L432Kx family device features and peripheral counts                         | 10 |

|-----------|----------------------------------------------------------------------------------|----|

| Table 2.  | Access status versus readout protection level and execution modes                |    |

| Table 3.  | Functionalities depending on the working mode                                    |    |

| Table 4.  | STM32L432xx peripherals interconnect matrix                                      |    |

| Table 5.  | DMA implementation                                                               |    |

| Table 6.  | Temperature sensor calibration values                                            |    |

| Table 7.  | Internal voltage reference calibration values                                    |    |

| Table 8.  | Timer feature comparison                                                         |    |

| Table 9.  | I2C implementation                                                               | 38 |

| Table 10. | STM32L432xx USART/LPUART features                                                |    |

| Table 11. | SAI implementation                                                               |    |

| Table 12. | Legend/abbreviations used in the pinout table                                    |    |

| Table 13. | STM32L432xx pin definitions                                                      |    |

| Table 14. | Alternate function AF0 to AF7 (for AF8 to AF15 see <i>Table 15</i> )             |    |

| Table 15. | Alternate function AF8 to AF15 (for AF0 to AF7 see <i>Table 14</i> )             |    |

| Table 16. | STM32L432xx memory map and peripheral register boundary addresses                |    |

| Table 17. | Voltage characteristics                                                          |    |

| Table 18. | Current characteristics                                                          | 61 |

| Table 19. | Thermal characteristics                                                          | 61 |

| Table 20. | General operating conditions                                                     |    |

| Table 21. | Operating conditions at power-up / power-down                                    |    |

| Table 22. | Embedded reset and power control block characteristics                           |    |

| Table 23. | Embedded internal voltage reference                                              |    |

| Table 24. | Current consumption in Run and Low-power run modes, code with data processing    |    |

|           | running from Flash, ART enable (Cache ON Prefetch OFF)                           | 68 |

| Table 25. | Current consumption in Run and Low-power run modes, code with data processing    |    |

|           | running from Flash, ART disable                                                  | 69 |

| Table 26. | Current consumption in Run and Low-power run modes, code with data processing    |    |

|           | running from SRAM1                                                               | 70 |

| Table 27. | Typical current consumption in Run and Low-power run modes, with different codes |    |

|           | running from Flash, ART enable (Cache ON Prefetch OFF)                           | 71 |

| Table 28. | Typical current consumption in Run and Low-power run modes, with different codes |    |

|           | running from Flash, ART disable                                                  | 72 |

| Table 29. | Typical current consumption in Run and Low-power run modes, with different codes |    |

|           | running from SRAM1                                                               | 72 |

| Table 30. | Current consumption in Sleep and Low-power sleep modes, Flash ON                 | 73 |

| Table 31. | Current consumption in Low-power sleep modes, Flash in power-down                | 74 |

| Table 32. | Current consumption in Stop 2 mode                                               | 74 |

| Table 33. | Current consumption in Stop 1 mode                                               | 76 |

| Table 34. | Current consumption in Stop 0                                                    | 77 |

| Table 35. | Current consumption in Standby mode                                              | 78 |

| Table 36. | Current consumption in Shutdown mode                                             | 79 |

| Table 37. | Peripheral current consumption                                                   |    |

| Table 38. | Low-power mode wakeup timings                                                    | 84 |

| Table 39. | Regulator modes transition times                                                 |    |

| Table 40. | Wakeup time using USART/LPUART                                                   | 86 |

| Table 41. | High-speed external user clock characteristics                                   | 87 |

| Table 42  | Low-speed external user clock characteristics                                    | 88 |

# **List of figures**

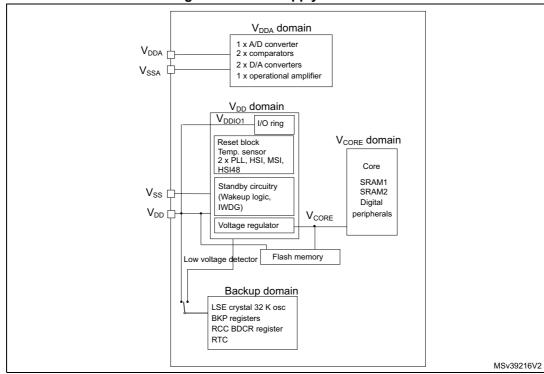

| Figure 1.  | STM32L432xx block diagram                                               | 12  |

|------------|-------------------------------------------------------------------------|-----|

| Figure 2.  | Power supply overview                                                   |     |

| Figure 3.  | Clock tree                                                              |     |

| Figure 4.  | STM32L432Kx UFQFPN32 pinout <sup>(1)</sup>                              | 46  |

| Figure 5.  | STM32L432xx memory map                                                  | 54  |

| Figure 6.  | Pin loading conditions                                                  | 58  |

| Figure 7.  | Pin input voltage                                                       | 58  |

| Figure 8.  | Power supply scheme                                                     | 59  |

| Figure 9.  | Current consumption measurement scheme                                  | 60  |

| Figure 10. | VREFINT versus temperature                                              | 66  |

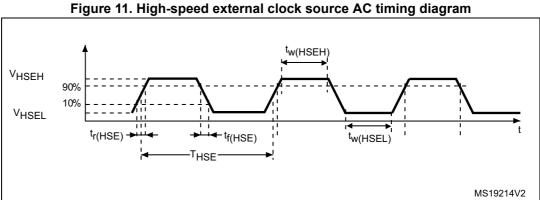

| Figure 11. | High-speed external clock source AC timing diagram                      | 87  |

| Figure 12. | Low-speed external clock source AC timing diagram                       | 88  |

| Figure 13. | Typical application with a 32.768 kHz crystal                           | 89  |

| Figure 14. | HSI16 frequency versus temperature                                      | 91  |

| Figure 15. | Typical current consumption versus MSI frequency                        | 95  |

| Figure 16. | HSI48 frequency versus temperature                                      | 96  |

| Figure 17. | I/O input characteristics                                               | 103 |

| Figure 18. | I/O AC characteristics definition <sup>(1)</sup>                        | 107 |

| Figure 19. | Recommended NRST pin protection                                         | 108 |

| Figure 20. | ADC accuracy characteristics                                            |     |

| Figure 21. | Typical connection diagram using the ADC                                | 121 |

| Figure 22. | 12-bit buffered / non-buffered DAC                                      | 124 |

| Figure 23. | SPI timing diagram - slave mode and CPHA = 0                            |     |

| Figure 24. | SPI timing diagram - slave mode and CPHA = 1                            | 135 |

| Figure 25. | SPI timing diagram - master mode                                        | 135 |

| Figure 26. | Quad SPI timing diagram - SDR mode                                      |     |

| Figure 27. | Quad SPI timing diagram - DDR mode                                      | 138 |

| Figure 28. | SAI master timing waveforms                                             |     |

| Figure 29. | SAI slave timing waveforms                                              | 141 |

| Figure 30. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|            | package outline                                                         | 143 |

| Figure 31. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|            | package recommended footprint                                           |     |

| Figure 32. | UFQFPN32 marking (package top view)                                     | 145 |

The whole non-volatile memory embeds the error correction code (ECC) feature supporting:

- single error detection and correction

- double error detection.

- The address of the ECC fail can be read in the ECC register

#### 3.5 Embedded SRAM

STM32L432xx devices feature 64 Kbyte of embedded SRAM. This SRAM is split into two blocks:

- 48 Kbyte mapped at address 0x2000 0000 (SRAM1)

- 16 Kbyte located at address 0x1000 0000 with hardware parity check (SRAM2).

This memory is also mapped at address 0x2000 C000, offering a contiguous address space with the SRAM1 (16 Kbyte aliased by bit band)

This block is accessed through the ICode/DCode buses for maximum performance.

These 16 Kbyte SRAM can also be retained in Standby mode.

The SRAM2 can be write-protected with 1 Kbyte granularity.

The memory can be accessed in read/write at CPU clock speed with 0 wait states.

### 3.6 Firewall

The device embeds a Firewall which protects code sensitive and secure data from any access performed by a code executed outside of the protected areas.

Each illegal access generates a reset which kills immediately the detected intrusion.

The Firewall main features are the following:

- Three segments can be protected and defined thanks to the Firewall registers:

- Code segment (located in Flash or SRAM1 if defined as executable protected area)

- Non-volatile data segment (located in Flash)

- Volatile data segment (located in SRAM1)

- The start address and the length of each segments are configurable:

- code segment: up to 1024 Kbyte with granularity of 256 bytes

- Non-volatile data segment: up to 1024 Kbyte with granularity of 256 bytes

- Volatile data segment: up to 48 Kbyte with a granularity of 64 bytes

- Specific mechanism implemented to open the Firewall to get access to the protected areas (call gate entry sequence)

- Volatile data segment can be shared or not with the non-protected code

- Volatile data segment can be executed or not depending on the Firewall configuration

The Flash readout protection must be set to level 2 in order to reach the expected level of protection.

Figure 2. Power supply overview

### 3.9.2 Power supply supervisor

The device has an integrated ultra-low-power brown-out reset (BOR) active in all modes except Shutdown and ensuring proper operation after power-on and during power down. The device remains in reset mode when the monitored supply voltage V<sub>DD</sub> is below a specified threshold, without the need for an external reset circuit.

The lowest BOR level is 1.71V at power on, and other higher thresholds can be selected through option bytes. The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the VPVD threshold and/or when  $V_{DD}$  is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

In addition, the devices embed a Peripheral Voltage Monitor which compares the independent supply voltage  $V_{DDA}$  with a fixed threshold in order to ensure that the peripheral is in its functional supply range.

### 3.21.2 General-purpose timers (TIM2, TIM15, TIM16)

There are up to three synchronizable general-purpose timers embedded in the STM32L432xx (see *Table 8* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

#### TIM2

It is a full-featured general-purpose timer:

TIM2 has a 32-bit auto-reload up/downcounter and 32-bit prescaler.

This timer features 4 independent channels for input capture/output compare, PWM or one-pulse mode output. It can work with the other general-purpose timers via the Timer Link feature for synchronization or event chaining.

The counter can be frozen in debug mode.

It has independent DMA request generation and support quadrature encoder.

TIM15 and 16

They are general-purpose timers with mid-range features:

They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM15 has 2 channels and 1 complementary channel

- TIM16 has 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

### 3.21.3 Basic timers (TIM6 and TIM7)

The basic timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit timebases.

#### 3.21.4 Low-power timer (LPTIM1 and LPTIM2)

The devices embed two low-power timers. These timers have an independent clock and are running in Stop mode if they are clocked by LSE, LSI or an external clock. They are able to wakeup the system from Stop mode.

LPTIM1 is active in Stop 0, Stop 1 and Stop 2 modes.

LPTIM2 is active in Stop 0 and Stop 1 mode.

| SAI features                                           | Support <sup>(1)</sup> |

|--------------------------------------------------------|------------------------|

| I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97         | X                      |

| Mute mode                                              | X                      |

| Stereo/Mono audio frame capability.                    | X                      |

| 16 slots                                               | X                      |

| Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit | X                      |

| FIFO Size                                              | X (8 Word)             |

| SPDIF                                                  | X                      |

Table 11. SAI implementation

### 3.28 Single wire protocol master interface (SWPMI)

The Single wire protocol master interface (SWPMI) is the master interface corresponding to the Contactless Frontend (CLF) defined in the ETSI TS 102 613 technical specification. The main features are:

- full-duplex communication mode

- automatic SWP bus state management (active, suspend, resume)

- configurable bitrate up to 2 Mbit/s

- automatic SOF, EOF and CRC handling

SWPMI can be served by the DMA controller.

## 3.29 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

The CAN peripheral supports:

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1 Mbit/s

<sup>1.</sup> X: supported

Table 13. STM32L432xx pin definitions (continued)

| Pin      | n lable 13. STM32L432XX pin definitions (continued) |          |               |       |                                                                                                                            |                      |  |  |  |  |

|----------|-----------------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Number   | e<br>ifter                                          |          |               |       | Pin func                                                                                                                   | tions                |  |  |  |  |

| UFQFPN32 | Pin name<br>(function after<br>reset)               | Pin type | I/O structure | Notes | Alternate functions                                                                                                        | Additional functions |  |  |  |  |

| 24       | PA14<br>(JTCK-<br>SWCLK)                            | I/O      | FT            | (3)   | JTCK-SWCLK, LPTIM1_OUT,<br>I2C1_SMBA, SWPMI1_RX,<br>SAI1_FS_B, EVENTOUT                                                    | -                    |  |  |  |  |

| 25       | PA15<br>(JTDI)                                      | I/O      | FT            | (3)   | JTDI, TIM2_CH1, TIM2_ETR, USART2_RX, SPI1_NSS, SPI3_NSS, USART3_RTS_DE, TSC_G3_IO1, SWPMI1_SUSPEND, EVENTOUT               | -                    |  |  |  |  |

| 26       | PB3<br>(JTDO-<br>TRACE<br>SWO)                      | I/O      | FT_a          | (3)   | JTDO-TRACESWO, TIM2_CH2, SPI1_SCK, SPI3_SCK, USART1_RTS_DE, SAI1_SCK_B, EVENTOUT                                           | COMP2_INM            |  |  |  |  |

| 27       | PB4<br>(NJTRST)                                     | I/O      | FT_fa         | (3)   | NJTRST, I2C3_SDA, SPI1_MISO, SPI3_MISO, USART1_CTS, TSC_G2_IO1, SAI1_MCLK_B, EVENTOUT                                      | COMP2_INP            |  |  |  |  |

| 28       | PB5                                                 | I/O      | FT            | 1     | LPTIM1_IN1, I2C1_SMBA,<br>SPI1_MOSI, SPI3_MOSI,<br>USART1_CK, TSC_G2_IO2,<br>COMP2_OUT, SAI1_SD_B,<br>TIM16_BKIN, EVENTOUT | -                    |  |  |  |  |

| 29       | PB6                                                 | I/O      | FT_fa         | ı     | LPTIM1_ETR, I2C1_SCL,<br>USART1_TX, TSC_G2_IO3,<br>SAI1_FS_B, TIM16_CH1N,<br>EVENTOUT                                      | COMP2_INP            |  |  |  |  |

| 30       | PB7                                                 | I/O      | FT_fa         | -     | LPTIM1_IN2, I2C1_SDA,<br>USART1_RX, TSC_G2_IO4,<br>EVENTOUT                                                                | COMP2_INM, PVD_IN    |  |  |  |  |

| 31       | PH3/<br>BOOT0                                       | I/O      | FT            | -     | EVENTOUT                                                                                                                   | воото                |  |  |  |  |

| 32       | VSS                                                 | S        | -             | -     | -                                                                                                                          | -                    |  |  |  |  |

| 1        | VDD                                                 | S        | -             | -     | -                                                                                                                          | -                    |  |  |  |  |

PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC14 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After reset, these pins are configured as JTAG/SW debug alternate functions, and the internal pull-up on PA15, PA13, PB4 pins and the internal pull-down on PA14 pin are activated.

After a Backup domain power-up, PC14 and PC15 operate as GPIOs. Their function then depends on the

content of the RTC registers which are not reset by the system reset. For details on how to manage these

GPIOs, refer to the Backup domain and RTC register descriptions in the RM0393 reference manual.

Table 14. Alternate function AF0 to AF7 (for AF8 to AF15 see Table 15) (continued)

|        |      | AF0                          | AF1                  | AF2       | AF3    | AF4            | AF5       | AF6       | AF7                          |

|--------|------|------------------------------|----------------------|-----------|--------|----------------|-----------|-----------|------------------------------|

| Port   |      | SYS_AF                       | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2 | USART2 | I2C1/I2C2/I2C3 | SPI1/SPI2 | SPI3      | USART1/<br>USART2/<br>USART3 |

|        | PB0  | -                            | TIM1_CH2N            | -         | -      | -              | SPI1_NSS  | -         | USART3_CK                    |

|        | PB1  | -                            | TIM1_CH3N            | -         | -      | -              | -         | -         | USART3_RTS_<br>DE            |

| Port B | PB3  | JTDO-<br>TRACESWO TIM2_CH2 - |                      | -         | -      | -              | SPI1_SCK  | SPI3_SCK  | USART1_RTS_<br>DE            |

|        | PB4  | NJTRST                       | -                    | -         | -      | I2C3_SDA       | SPI1_MISO | SPI3_MISO | USART1_CTS                   |

|        | PB5  | -                            | LPTIM1_IN1           | -         | -      | I2C1_SMBA      | SPI1_MOSI | SPI3_MOSI | USART1_CK                    |

|        | PB6  | -                            | LPTIM1_ETR           | -         | -      | I2C1_SCL       | -         | -         | USART1_TX                    |

|        | PB7  | -                            | LPTIM1_IN2           | -         | -      | I2C1_SDA       | -         | -         | USART1_RX                    |

| Port C | PC14 | -                            | -                    | -         | -      | -              | -         | -         | -                            |

| POILC  | PC15 | -                            | -                    | -         | -      | -              | -         | -         | -                            |

| Port H | PH3  | -                            | -                    | -         | -      | -              | -         | -         | -                            |

Table 15. Alternate function AF8 to AF15 (for AF0 to AF7 see *Table 14*) (continued)

|        |      | AF8                | AF9        | AF10                | AF11 | AF12                       | AF13        | AF14                        | AF15     |  |

|--------|------|--------------------|------------|---------------------|------|----------------------------|-------------|-----------------------------|----------|--|

| Port   |      | LPUART1            | CAN1/TSC   | USB/QUADSPI         | -    | COMP1/<br>COMP2/<br>SWPMI1 | SAI1        | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |  |

|        | PB0  | -                  | -          | QUADSPI_<br>BK1_IO1 | -    | COMP1_OUT                  | SAI1_EXTCLK | -                           | EVENTOUT |  |

|        | PB1  | LPUART1_RTS<br>_DE | -          | QUADSPI_<br>BK1_IO0 | -    | -                          | -           | LPTIM2_IN1                  | EVENTOUT |  |

| Port B | PB3  | -                  | -          | -                   | -    | -                          | SAI1_SCK_B  | -                           | EVENTOUT |  |

| . 0    | PB4  | -                  | TSC_G2_IO1 | -                   | -    | -                          | SAI1_MCLK_B | -                           | EVENTOUT |  |

| ,      | PB5  | -                  | TSC_G2_IO2 | -                   | -    | COMP2_OUT                  | SAI1_SD_B   | TIM16_BKIN                  | EVENTOUT |  |

| •      | PB6  | -                  | TSC_G2_IO3 | -                   | -    | -                          | SAI1_FS_B   | TIM16_CH1N                  | EVENTOUT |  |

| •      | PB7  | -                  | TSC_G2_IO4 | -                   | -    | -                          | -           | -                           | EVENTOUT |  |

| Dort C | PC14 | -                  | -          | -                   | -    | -                          | -           | -                           | EVENTOUT |  |

| Port C | PC15 | -                  | -          | -                   | -    | -                          | -           | -                           | EVENTOUT |  |

| Port H | PH3  | -                  | -          | -                   | _    | -                          | -           | -                           | EVENTOUT |  |

### 6.1.6 Power supply scheme

Caution:

Each power supply pair ( $V_{DD}/V_{SS}$ ,  $V_{DDA}/V_{SSA}$  etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

### 6.1.7 Current consumption measurement

IDD\_USB

VDDUSB

VDDUSB

VDD

VDD

VDD

MSv41630V1

Figure 9. Current consumption measurement scheme

### 6.2 Absolute maximum ratings

60/149

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics* and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                                      | Min                  | Max                                                            | Unit |

|------------------------------------|------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|------|

| V <sub>DDX</sub> - V <sub>SS</sub> | External main supply voltage (including $V_{DD}$ , $V_{DDA}$ , $V_{DDUSB}$ ) | -0.3                 | 4.0                                                            | ٧    |

| (0)                                | Input voltage on FT_xxx pins                                                 | V <sub>SS</sub> -0.3 | min ( $V_{DD}$ , $V_{DDA}$ , $V_{DDUSB}$ )<br>+ $4.0^{(3)(4)}$ |      |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on TT_xx pins                                                  | V <sub>SS</sub> -0.3 | 4.0                                                            | V    |

|                                    | Input voltage on any other pins                                              | V <sub>SS</sub> -0.3 | 4.0                                                            |      |

| $ \Delta V_{DDx} $                 | Variations between different V <sub>DDX</sub> power pins of the same domain  | -                    | 50                                                             | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub>  | Variations between all the different ground pins <sup>(5)</sup>              | -                    | 50                                                             | mV   |

Table 17. Voltage characteristics<sup>(1)</sup>

DocID028798 Rev 2

All main power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>,) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum must always be respected. Refer to Table 18: Current characteristics for the maximum allowed injected current values.

<sup>3.</sup> This formula has to be applied only on the power supplies related to the IO structure described in the pin definition table.

- 4. To sustain a voltage higher than 4 V the internal pull-up/pull-down resistors must be disabled.

- 5. Include VREF- pin.

**Table 18. Current characteristics**

| Symbol                    | Ratings                                                                            | Max                  | Unit |

|---------------------------|------------------------------------------------------------------------------------|----------------------|------|

| $\Sigma IV_{DD}$          | Total current into sum of all V <sub>DD</sub> power lines (source) <sup>(1)</sup>  | 140                  |      |

| ΣIV <sub>SS</sub>         | Total current out of sum of all V <sub>SS</sub> ground lines (sink) <sup>(1)</sup> | 140                  |      |

| IV <sub>DD(PIN)</sub>     | Maximum current into each V <sub>DD</sub> power pin (source) <sup>(1)</sup>        | 100                  |      |

| IV <sub>SS(PIN)</sub>     | Maximum current out of each V <sub>SS</sub> ground pin (sink) <sup>(1)</sup>       | 100                  |      |

|                           | Output current sunk by any I/O and control pin except FT_f                         | 20                   |      |

| I <sub>IO(PIN)</sub>      | Output current sunk by any FT_f pin                                                | 20                   |      |

|                           | Output current sourced by any I/O and control pin                                  | 20                   | mA   |

| <b>7</b> 1                | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>       | 100                  |      |

| $\Sigma I_{IO(PIN)}$      | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup>    | 100                  |      |

| I <sub>INJ(PIN)</sub> (3) | Injected current on FT_xxx, TT_xx, RST and B pins, except PA4, PA5                 | -5/+0 <sup>(4)</sup> |      |

|                           | Injected current on PA4, PA5                                                       | -5/0                 |      |

| $\Sigma  I_{INJ(PIN)} $   | Total injected current (sum of all I/Os and control pins) <sup>(5)</sup>           | 25                   |      |

- 1. All main power  $(V_{DD}, V_{DDA}, V_{DDUSB})$  and ground  $(V_{SS}, V_{SSA})$  pins must always be connected to the external power supplies, in the permitted range.

- 2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

- 3. Positive injection (when  $V_{IN} > V_{DDIOx}$ ) is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer also to *Table 17: Voltage characteristics* for the maximum allowed input voltage values.

- When several inputs are submitted to a current injection, the maximum ∑|I<sub>INJ(PIN)</sub>| is the absolute sum of the negative injected currents (instantaneous values).

Table 19. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150         | °C   |

### 6.3.4 Embedded voltage reference

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

Table 23. Embedded internal voltage reference

| Symbol                                    | Parameter                                                                         | Conditions                        | Min              | Тур   | Max                 | Unit                     |

|-------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------|------------------|-------|---------------------|--------------------------|

| V <sub>REFINT</sub>                       | Internal reference voltage                                                        | -40 °C < T <sub>A</sub> < +130 °C | 1.182            | 1.212 | 1.232               | V                        |

| t <sub>S_vrefint</sub> (1)                | ADC sampling time when reading the internal reference voltage                     | -                                 | 4 <sup>(2)</sup> | -     | 1                   | μs                       |

| t <sub>start_vrefint</sub>                | Start time of reference voltage buffer when ADC is enable                         | -                                 | -                | 8     | 12 <sup>(2)</sup>   | μs                       |

| I <sub>DD</sub> (V <sub>REFINTBUF</sub> ) | V <sub>REFINT</sub> buffer consumption from V <sub>DD</sub> when converted by ADC | -                                 | -                | 12.5  | 20 <sup>(2)</sup>   | μΑ                       |

| $\Delta V_{REFINT}$                       | Internal reference voltage spread over the temperature range                      | V <sub>DD</sub> = 3 V             | -                | 5     | 7.5 <sup>(2)</sup>  | mV                       |

| T <sub>Coeff</sub>                        | Temperature coefficient                                                           | -40°C < T <sub>A</sub> < +130°C   | -                | 30    | 50 <sup>(2)</sup>   | ppm/°C                   |

| A <sub>Coeff</sub>                        | Long term stability                                                               | 1000 hours, T = 25°C              | -                | -     | TBD <sup>(2)</sup>  | ppm                      |

| V <sub>DDCoeff</sub>                      | Voltage coefficient                                                               | 3.0 V < V <sub>DD</sub> < 3.6 V   | -                | 250   | 1200 <sup>(2)</sup> | ppm/V                    |

| V <sub>REFINT_DIV1</sub>                  | 1/4 reference voltage                                                             |                                   | 24               | 25    | 26                  |                          |

| V <sub>REFINT_DIV2</sub>                  | 1/2 reference voltage                                                             | -                                 | 49               | 50    | 51                  | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub>                  | 3/4 reference voltage                                                             |                                   | 74               | 75    | 76                  | INLFIINT                 |

<sup>1.</sup> The shortest sampling time can be determined in the application by multiple iterations.

<sup>2.</sup> Guaranteed by design.

Table 32. Current consumption in Stop 2 mode (continued)

| Symbol                                 | Symbol Parameter Conditions |                                                                                |          | ТҮР   |       |       |        | MAX <sup>(1)</sup> |       |       |       | Unit   |        |      |

|----------------------------------------|-----------------------------|--------------------------------------------------------------------------------|----------|-------|-------|-------|--------|--------------------|-------|-------|-------|--------|--------|------|

| Symbol                                 | Parameter                   | -                                                                              | $V_{DD}$ | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | Onic |

| I <sub>DD</sub> (wakeup<br>from Stop2) | 2) from Stop 2              | Wakeup clock is<br>MSI = 48 MHz,<br>voltage Range 1.<br>See <sup>(3)</sup> .   | 3 V      | 1.85  | -     | -     | -      | -                  | -     | -     | -     | -      | -      |      |

|                                        |                             | Wakeup clock is<br>MSI = 4 MHz,<br>voltage Range 2.<br>See <sup>(3)</sup> .    | 3 V      | 1.52  | -     | -     | -      | -                  | -     | -     | -     | -      | -      | mA   |

|                                        |                             | Wakeup clock is<br>HSI16 = 16 MHz,<br>voltage Range 1.<br>See <sup>(3)</sup> . | 3 V      | 1.54  | -     | -     | -      | -                  | -     | 1     | -     | -      | -      |      |

<sup>1.</sup> Guaranteed based on test during characterization, unless otherwise specified.

<sup>2.</sup> Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

<sup>3.</sup> Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in *Table 38: Low-power mode wakeup timings*.

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 37*. The MCU is placed under the following conditions:

- All I/O pins are in Analog mode

- The given value is calculated by measuring the difference of the current consumptions:

- when the peripheral is clocked on

- when the peripheral is clocked off

- Ambient operating temperature and supply voltage conditions summarized in Table 17: Voltage characteristics

- The power consumption of the digital part of the on-chip peripherals is given in *Table 37*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

Table 37. Peripheral current consumption

|      | Peripheral                        | Range 1 | Range 2 | Low-power run and sleep | Unit   |

|------|-----------------------------------|---------|---------|-------------------------|--------|

|      | Bus Matrix <sup>(1)</sup>         | 3.2     | 2.9     | 3.1                     |        |

|      | ADC independent clock domain      | 0.4     | 0.1     | 0.2                     |        |

|      | ADC clock domain                  | 2.1     | 1.9     | 1.9                     |        |

|      | CRC                               | 0.4     | 0.2     | 0.3                     |        |

|      | DMA1                              | 1.4     | 1.3     | 1.4                     |        |

|      | DMA2                              | 1.5     | 1.3     | 1.4                     |        |

|      | FLASH                             | 6.2     | 5.2     | 5.8                     | 1      |

|      | GPIOA <sup>(2)</sup>              | 1.7     | 1.4     | 1.6                     |        |

| AHB  | GPIOB <sup>(2)</sup> )            | 1.6     | 1.3     | 1.6                     |        |

| АПВ  | GPIOC <sup>(2)</sup>              | 1.7     | 1.5     | 1.6                     |        |

|      | GPIOH <sup>(2)</sup>              | 0.6     | 0.6     | 0.5                     |        |

|      | QSPI                              | 7.0     | 5.8     | 7.3                     | µA/MHz |

|      | RNG independent clock domain      | 2.2     | NA      | NA                      |        |

|      | RNG clock domain                  | 0.5     | NA      | NA                      |        |

|      | SRAM1                             | 0.8     | 0.9     | 0.7                     |        |

|      | SRAM2                             | 1.0     | 0.8     | 0.8                     |        |

|      | TSC                               | 1.6     | 1.3     | 1.3                     |        |

|      | All AHB Peripherals               | 21.7    | 18.5    | 20.3                    |        |

|      | AHB to APB1 bridge <sup>(3)</sup> | 0.9     | 0.7     | 0.9                     |        |

|      | CAN1                              | 4.1     | 3.2     | 3.9                     |        |

| APB1 | DAC1                              | 2.4     | 1.8     | 2.2                     |        |

|      | RTCA                              | 1.7     | 1.1     | 2.1                     |        |

|      | CRS                               | 0.3     | 0.3     | 0.6                     |        |

82/149 DocID028798 Rev 2

Table 37. Peripheral current consumption (continued)

| Peripheral |                                  | Range 1 | Range 2 | Low-power run and sleep | Unit   |

|------------|----------------------------------|---------|---------|-------------------------|--------|

|            | USB FS independent clock domain  | 2.9     | NA      | NA                      |        |

|            | USB FS clock domain              | 2.3     | NA      | NA                      |        |

|            | I2C1 independent clock domain    | 3.5     | 2.8     | 3.4                     |        |

|            | I2C1 clock domain                | 1.1     | 0.9     | 1.0                     |        |

|            | I2C3 independent clock domain    | 2.9     | 2.3     | 2.5                     |        |

|            | I2C3 clock domain                | 0.9     | 0.4     | 0.8                     |        |

|            | LPUART1 independent clock domain | 1.9     | 1.6     | 1.8                     |        |

|            | LPUART1 clock domain             | 0.6     | 0.6     | 0.6                     |        |

|            | LPTIM1 independent clock domain  | 2.9     | 2.4     | 2.8                     |        |

|            | LPTIM1 clock domain              | 0.8     | 0.4     | 0.7                     |        |

|            | LPTIM2 independent clock domain  | 3.1     | 2.7     | 3.9                     |        |

| APB1       | LPTIM2 clock domain              | 0.8     | 0.7     | 0.8                     |        |

|            | OPAMP                            | 0.4     | 0.2     | 0.4                     |        |

|            | PWR                              | 0.4     | 0.1     | 0.4                     |        |

|            | SPI3                             | 1.7     | 1.3     | 1.6                     | μΑ/MHz |

|            | SWPMI1 independent clock domain  | 1.9     | 1.6     | 1.9                     |        |

|            | SWPMI1 clock domain              | 0.9     | 0.7     | 0.8                     |        |

|            | TIM2                             | 6.2     | 5.0     | 5.9                     |        |

|            | TIM6                             | 1.0     | 0.6     | 0.9                     |        |

|            | TIM7                             | 1.0     | 0.6     | 0.6                     |        |

|            | USART2 independent clock domain  | 4.1     | 3.6     | 3.8                     |        |

|            | USART2 clock domain              | 1.3     | 0.9     | 1.1                     |        |

|            | WWDG                             | 0.5     | 0.5     | 0.5                     |        |

|            | All APB1 on                      | 40.2    | 26.7    | 37.9                    |        |

|            | AHB to APB2 <sup>(4)</sup>       | 1.0     | 0.9     | 0.9                     |        |

|            | FW                               | 0.2     | 0.2     | 0.2                     |        |

| ADDO       | SAI1 independent clock domain    | 2.3     | 1.8     | 1.9                     |        |

| APB2       | SAI1 clock domain                | 2.1     | 1.8     | 2.0                     |        |

|            | SPI1                             | 1.8     | 1.6     | 1.7                     |        |

|            | SYSCFG/COMP                      | 0.6     | 0.5     | 0.6                     |        |

#### 6.3.7 **External clock source characteristics**

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 11: High-speed external clock source AC timing diagram.

Table 41. High-speed external user clock characteristics<sup>(1)</sup>

| Symbol                                       | Parameter                            | Conditions Min             |                        | Тур             | Max                    | Unit |    |

|----------------------------------------------|--------------------------------------|----------------------------|------------------------|-----------------|------------------------|------|----|

| £                                            | User external clock source frequency | Voltage scaling<br>Range 1 |                        | 8               | 48                     | MHz  |    |

| f <sub>HSE_ext</sub>                         | Oser external clock source frequency | Voltage scaling<br>Range 2 | e scaling 8 26         | IVITIZ          |                        |      |    |

| V <sub>HSEH</sub>                            | CK_IN input pin high level voltage   | -                          | 0.7 V <sub>DDIOx</sub> | -               | $V_{DDIOx}$            | V    |    |

| V <sub>HSEL</sub>                            | CK_IN input pin low level voltage    | -                          | V <sub>SS</sub>        | -               | 0.3 V <sub>DDIOx</sub> |      |    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | CK IN high or low time               | Voltage scaling<br>Range 1 | /oltage scaling 7 -    |                 | -                      |      |    |

|                                              | CK_IN high or low time               | Voltage scaling<br>Range 2 | 9 9 18 1               | g <sub>18</sub> | -                      | -    | ns |

<sup>1.</sup> Guaranteed by design.

Table 45. MSI oscillator characteristics<sup>(1)</sup> (continued)

| Symbol                                 | Parameter                                  |                                                 | Conditions                       | (0000000                            | Min  | Тур  | Max   | Unit |

|----------------------------------------|--------------------------------------------|-------------------------------------------------|----------------------------------|-------------------------------------|------|------|-------|------|

|                                        |                                            |                                                 | Pango 0 to 2                     | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -1.2 | -    | 0.5   |      |

|                                        |                                            |                                                 | Range 0 to 3                     | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.5 | -    | 0.5   |      |

| A (MGI)(2)                             | MSI oscillator frequency drift             | MCI mada                                        | to 3.6 V                         | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -2.5 | -    | 0.7   | %    |

| $\Delta_{VDD}(MSI)^{(2)}$              | over V <sub>DD</sub><br>(reference is 3 V) | MSI mode                                        | Range 4 to 7                     | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.8 | -    | 0.7   | 70   |

|                                        |                                            |                                                 | Danga 9 to 11                    | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -5   | -    | _ 1   |      |

|                                        |                                            |                                                 | Range 8 to 11                    | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -1.6 | -    |       |      |

| AFCAMPLING                             | Frequency                                  |                                                 | $T_A = -40 \text{ to } 85^\circ$ | °C                                  | -    | 1    | 2     |      |

| $\Delta F_{SAMPLING} \ (MSI)^{(2)(6)}$ | variation in sampling mode <sup>(3)</sup>  | MSI mode                                        | T <sub>A</sub> = -40 to 125      | °C                                  | -    | 2    | 4     | %    |

| P_USB                                  | , , , ,                                    | jitter for PLL mode ock <sup>(4)</sup> Range 11 | for next transition              | -                                   | -    | -    | 3.458 |      |

| Jitter(MSI) <sup>(6)</sup>             |                                            |                                                 | for paired transition            | -                                   | -    | -    | 3.916 | ns   |

| MT_USB                                 | 3/5                                        |                                                 | for next<br>transition           | -                                   | -    | -    | 2     | no   |

| Jitter(MSI) <sup>(6)</sup>             |                                            |                                                 | for paired transition            | -                                   | -    | -    | 1     | ns   |

| CC jitter(MSI) <sup>(6)</sup>          | RMS cycle-to-<br>cycle jitter              | PLL mode Range 11                               |                                  | -                                   | -    | 60   | -     | ps   |

| P jitter(MSI) <sup>(6)</sup>           | RMS Period jitter                          | PLL mode R                                      | PLL mode Range 11                |                                     | -    | 50   | -     | ps   |

|                                        |                                            | Range 0                                         |                                  | -                                   | -    | 10   | 20    |      |

|                                        |                                            | Range 1 Range 2                                 |                                  | -                                   | -    | 5    | 10    |      |

| (1.401)(6)                             | MSI oscillator                             |                                                 |                                  | -                                   | -    | 4    | 8     |      |

| t <sub>SU</sub> (MSI) <sup>(6)</sup>   | start-up time                              | Range 3                                         | Range 3 - Range 4 to 7 -         |                                     | -    | 3    | 7     | us   |

|                                        | Range 4                                    | Range 4 to 7                                    |                                  |                                     | -    | - 3  | 6     | -    |

|                                        |                                            | Range 8 to 11                                   |                                  | -                                   | -    | 2.5  | 6     |      |

| t <sub>STAB</sub> (MSI) <sup>(6)</sup> |                                            |                                                 | 10 % of final frequency          | -                                   | -    | 0.25 | 0.5   |      |

|                                        | MSI oscillator stabilization time          | PLL mode<br>Range 11                            | 5 % of final frequency           | -                                   | -    | 0.5  | 1.25  | ms   |

|                                        |                                            |                                                 | 1 % of final frequency           | -                                   | -    | -    | 2.5   |      |

Table 64. ADC accuracy - limited test conditions  $2^{(1)(2)(3)}$

| Sym-<br>bol | Parameter                          | Conditions <sup>(4)</sup>                                                                                |                 |                          |         |      | Max | Unit |

|-------------|------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|--------------------------|---------|------|-----|------|

|             |                                    |                                                                                                          | Single          | Fast channel (max speed) | -       | 4    | 6.5 |      |

| ET          | Total<br>unadjusted                |                                                                                                          | ended           | Slow channel (max speed) | -       | 4    | 6.5 |      |

|             | error                              |                                                                                                          | Differential    | Fast channel (max speed) | -       | 3.5  | 5.5 |      |

|             |                                    |                                                                                                          | Dillerential    | Slow channel (max speed) | -       | 3.5  | 5.5 |      |

|             |                                    |                                                                                                          | Single          | Fast channel (max speed) | -       | 1    | 4.5 |      |

| EO          | Offset                             |                                                                                                          | ended           | Slow channel (max speed) | -       | 1    | 5   |      |

|             | error                              |                                                                                                          | Differential    | Fast channel (max speed) | -       | 1.5  | 3   |      |

|             |                                    |                                                                                                          | Dillerential    | Slow channel (max speed) | -       | 1.5  | 3   |      |

|             |                                    |                                                                                                          | Single          | Fast channel (max speed) | -       | 2.5  | 6   |      |

| EG          | Gain error                         |                                                                                                          | ended           | Slow channel (max speed) | -       | 2.5  | 6   | LSB  |

| EG          | Gain enoi                          |                                                                                                          | Differential    | Fast channel (max speed) | -       | 2.5  | 3.5 | LSB  |

|             |                                    |                                                                                                          | Dillerential    | Slow channel (max speed) | -       | 2.5  | 3.5 |      |

|             |                                    | rity ADC clock frequency $\leq$ 80 MHz, Sampling rate $\leq$ 5.33 Msps, 1 V $\leq$ V $\leq$ V $\leq$ DDA | Single          | Fast channel (max speed) | -       | 1    | 1.5 |      |

| ED          | Differential<br>linearity<br>error |                                                                                                          | ended           | Slow channel (max speed) | -       | 1    | 1.5 |      |

|             |                                    |                                                                                                          | Differential    | Fast channel (max speed) | -       | 1    | 1.2 |      |

|             |                                    |                                                                                                          |                 | Slow channel (max speed) | -       | 1    | 1.2 |      |

|             |                                    |                                                                                                          | Single<br>ended | Fast channel (max speed) | -       | 1.5  | 3.5 |      |

| EL          | Integral<br>linearity<br>error     |                                                                                                          |                 | Slow channel (max speed) | -       | 1.5  | 3.5 |      |

| EL          |                                    |                                                                                                          | Differential    | Fast channel (max speed) | -       | 1    | 3   |      |

|             |                                    |                                                                                                          |                 | Slow channel (max speed) | -       | 1    | 2.5 |      |

|             |                                    | fective<br>Imber of                                                                                      | Single<br>ended | Fast channel (max speed) | 10 10.5 | -    |     |      |

| ENOB        | Effective                          |                                                                                                          |                 | Slow channel (max speed) | 10      | 10.5 | -   | bits |

| LINOB       | bits                               |                                                                                                          | Differential    | Fast channel (max speed) | 10.7    | 10.9 | -   | טונס |

|             |                                    |                                                                                                          | Dillerential    | Slow channel (max speed) | 10.7    | 10.9 | -   |      |

|             | Signal-to-                         |                                                                                                          | Single          | Fast channel (max speed) | 62      | 65   | -   |      |

| SINAD       | noise and                          | nd                                                                                                       | ended           | Slow channel (max speed) | 62      | 65   | -   |      |

| SINAD       | distortion                         |                                                                                                          | Differential    | Fast channel (max speed) | 66      | 67.4 | -   |      |

|             | ratio                              |                                                                                                          | Dillerential    | Slow channel (max speed) | 66      | 67.4 | -   | dB   |

|             |                                    |                                                                                                          | Single          | Fast channel (max speed) | 64      | 66   | -   | ub   |

| SNR         | Signal-to-                         |                                                                                                          | ended           | Slow channel (max speed) | 64      | 66   | -   |      |

| SINK        | noise ratio                        |                                                                                                          | Difforential    | Fast channel (max speed) | 66.5    | 68   | -   |      |

|             |                                    |                                                                                                          | Differential    | Slow channel (max speed) | 66.5    | 68   | ı   |      |

- 3. Refer to Table 56: I/O static characteristics.

- 4. Ton is the Refresh phase duration. Toff is the Hold phase duration. Refer to RM0393 reference manual for more details.

Buffered/non-buffered DAC

Buffer (1)

12-bit digital to analog converter

DACX\_OUT

RLOAD

CLOAD

ai17157d

Figure 22. 12-bit buffered / non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly

without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the

DAC\_CR register.

Table 68. DAC accuracy<sup>(1)</sup>

| Symbol    | Parameter                                 | Conditio                                                     | Min                       | Тур                       | Max | Unit |      |

|-----------|-------------------------------------------|--------------------------------------------------------------|---------------------------|---------------------------|-----|------|------|

| DNL       | Differential non                          | DAC output buffer ON                                         | •                         |                           | -   | ±2   |      |

| DINL      | linearity (2)                             | DAC output buffer OFF                                        |                           |                           | -   | ±2   |      |

| -         | monotonicity                              | 10 bits                                                      |                           | guaranteed                |     |      |      |

| INL       | Integral non                              | DAC output buffer ON CL ≤ 50 pF, RL ≥ 5 kΩ                   |                           | -                         | -   | ±4   |      |

| INL       | linearity <sup>(3)</sup>                  | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                   |                           | -                         | -   | ±4   |      |

|           | Offset error at code 0x800 <sup>(3)</sup> | DAC output buffer ON CL ≤ 50 pF, RL ≥ 5 kΩ                   | V <sub>REF+</sub> = 3.6 V | -                         | -   | ±12  | 1.00 |

| Offset    |                                           |                                                              | V <sub>REF+</sub> = 1.8 V | -                         | -   | ±25  | LSB  |

|           |                                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                   |                           | -                         | -   | ±8   |      |

| Offset1   | Offset error at code 0x001 <sup>(4)</sup> | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                   |                           | -                         | -   | ±5   |      |

| OffsetCal | Offset Error at                           | code 0x800 $CL \le 50 \text{ pF, } RL \ge 5 \text{ k}\Omega$ | V <sub>REF+</sub> = 3.6 V | V <sub>REF+</sub> = 3.6 V | -   | ±5   |      |

|           | after calibration                         |                                                              | V <sub>REF+</sub> = 1.8 V | -                         | -   | ±7   |      |

124/149 DocID028798 Rev 2