Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                          |

| Number of I/O              | 26                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                          |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 32-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l432kcu6          |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32L432xx devices are the ultra-low-power microcontrollers based on the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L432xx devices embed high-speed memories (Flash memory up to 256 Kbyte, 64 Kbyte of SRAM), a Quad SPI flash memories interface and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L432xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer a fast 12-bit ADC (5 Msps), two comparators, one operational amplifier, two DAC channels, a low-power RTC, one general-purpose 32-bit timer, one 16-bit PWM timer dedicated to motor control, four general-purpose 16-bit timers, and two 16-bit low-power timers.

In addition, up to 3 capacitive sensing channels are available.

They also feature standard and advanced communication interfaces.

- Two I2Cs

- Two SPIs

- Two USARTs and one Low-Power UART.

- One SAI (Serial Audio Interfaces)

- One CAN

- One USB full-speed device crystal less

- One SWPMI (Single Wire Protocol Master Interface)

The STM32L432xx operates in the -40 to +85  $^{\circ}$ C (+105  $^{\circ}$ C junction), -40 to +105  $^{\circ}$ C (+125  $^{\circ}$ C junction) and -40 to +125  $^{\circ}$ C (+130  $^{\circ}$ C junction) temperature ranges from a 1.71 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMPs and comparators.

The STM32L432xx family offers a single 32-pin package.

#### Table 1. STM32L432Kx family device features and peripheral counts

| Peripheral   | STM32L432Kx |

|--------------|-------------|

| Flash memory | 256KB       |

| SRAM         | 64KB        |

| Quad SPI     | Yes         |

### 3.9.3 Voltage regulator

Two embedded linear voltage regulators supply most of the digital circuitries: the main regulator (MR) and the low-power regulator (LPR).

- The MR is used in the Run and Sleep modes and in the Stop 0 mode.

- The LPR is used in Low-Power Run, Low-Power Sleep, Stop 1 and Stop 2 modes. It is also used to supply the 16 Kbyte SRAM2 in Standby with RAM2 retention.

- Both regulators are in power-down in Standby and Shutdown modes: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The ultralow-power STM32L432xx supports dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the Main Regulator that supplies the logic (VCORE) can be adjusted according to the system's maximum operating frequency.

There are two power consumption ranges:

- Range 1 with the CPU running at up to 80 MHz.

- Range 2 with a maximum CPU frequency of 26 MHz. All peripheral clocks are also limited to 26 MHz.

The VCORE can be supplied by the low-power regulator, the main regulator being switched off. The system is then in Low-power run mode.

Low-power run mode with the CPU running at up to 2 MHz. Peripherals with independent clock can be clocked by HSI16.

#### 3.9.4 Low-power modes

The ultra-low-power STM32L432xx supports seven low-power modes to achieve the best compromise between low-power consumption, short startup time, available peripherals and available wakeup sources:

By default, the microcontroller is in Run mode after a system or a power Reset. It is up to the user to select one of the low-power modes described below:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Low-power run mode

This mode is achieved with VCORE supplied by the low-power regulator to minimize the regulator's operating current. The code can be executed from SRAM or from Flash,

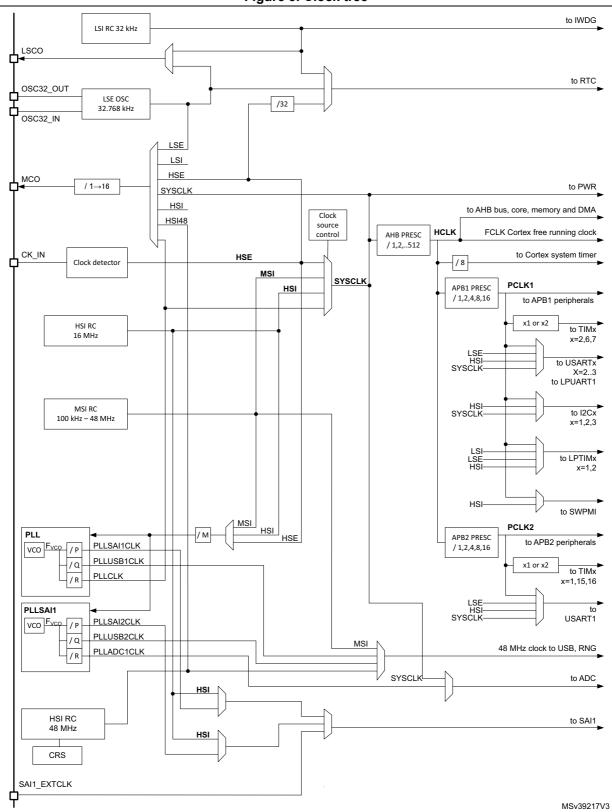

# 3.11 Clocks and startup

The clock controller (see *Figure 3*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source:** four different clock sources can be used to drive the master clock SYSCLK:

- High Speed External clock (HSE) can supply a PLL.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. In this mode the MSI can feed the USB device. The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **RC48 with clock recovery system (HSI48)**: internal RC48 MHz clock source can be used to drive the USB or the RNG peripherals. This clock can be output on the MCO.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (USB, RNG, SAI, USARTs, I2Cs, LPTimers, ADC, SWPMI) have their own independent clock whatever the system clock. Two PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the USB/RNG and the SAI.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application

- **LSCO:** low speed clock output: it outputs LSI or LSE in all low-power modes.

#### STM32L432KB STM3L432KC

Figure 3. Clock tree

| Timer type          | Timer      | Counter resolution | Counter<br>type | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |  |

|---------------------|------------|--------------------|-----------------|---------------------------------------|------------------------------|---------------------------------|--------------------------|--|

| General-<br>purpose | TIM16      | 16-bit             | Up              | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                        |  |

| Basic               | TIM6, TIM7 | 16-bit             | Up              | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                       |  |

Table 8. Timer feature comparison (continued)

# 3.21.1 Advanced-control timer (TIM1)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.21.2*) using the same architecture, so the advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

# 3.24 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L432xx devices have two embedded universal synchronous receiver transmitters (USART1 and USART2).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1 and USART2 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2) to wake up the MCU from Stop mode using baudrates up to 200 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1            | USART2 | LPUART1 |  |  |  |

|---------------------------------------|-------------------|--------|---------|--|--|--|

| Hardware flow control for modem       | Х                 | Х      | Х       |  |  |  |

| Continuous communication using DMA    | Х                 | Х      | Х       |  |  |  |

| Multiprocessor communication          | Х                 | Х      | Х       |  |  |  |

| Synchronous mode                      | Х                 | Х      | -       |  |  |  |

| Smartcard mode                        | Х                 | Х      | -       |  |  |  |

| Single-wire half-duplex communication | Х                 | Х      | Х       |  |  |  |

| IrDA SIR ENDEC block                  | Х                 | Х      | -       |  |  |  |

| LIN mode                              | Х                 | Х      | -       |  |  |  |

| Dual clock domain                     | Х                 | Х      | Х       |  |  |  |

| Wakeup from Stop 0 / Stop 1 modes     | Х                 | Х      | Х       |  |  |  |

| Wakeup from Stop 2 mode               | -                 | -      | Х       |  |  |  |

| Receiver timeout interrupt            | Х                 | Х      | -       |  |  |  |

| Modbus communication                  | Х                 | Х      | -       |  |  |  |

| Auto baud rate detection              | X (4 n            | nodes) | -       |  |  |  |

| Driver Enable                         | Х                 | Х      | Х       |  |  |  |

| LPUART/USART data length              | h 7, 8 and 9 bits |        |         |  |  |  |

#### Table 10. STM32L432xx USART/LPUART features

1. X = supported.

| Τ              |

|----------------|

| Ë              |

| ō              |

| uts            |

| an             |

| ā              |

| σ              |

| Ŀ,             |

| de             |

| S              |

| <u><u></u></u> |

| Ъ.             |

| Ē.             |

| <u>o</u>       |

|                |

|        |      |            | Table 14. Alte       | rnate function | AF0 to AF7 (fo | r AF8 to AF15 s | ee <i>Table 15</i> ) |           |                              |

|--------|------|------------|----------------------|----------------|----------------|-----------------|----------------------|-----------|------------------------------|

|        |      | AF0        | AF1                  | AF2            | AF3            | AF4             | AF5                  | AF6       | AF7                          |

| Po     | ort  | SYS_AF     | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2      | USART2         | 12C1/12C2/12C3  | SPI1/SPI2            | SPI3      | USART1/<br>USART2/<br>USART3 |

|        | PA0  | -          | TIM2_CH1             | -              | -              | -               | -                    | -         | USART2_CTS                   |

|        | PA1  | -          | TIM2_CH2             | -              | -              | I2C1_SMBA       | SPI1_SCK             | -         | USART2_RTS_<br>DE            |

|        | PA2  | -          | TIM2_CH3             | -              | -              | -               | -                    | -         | USART2_TX                    |

|        | PA3  | -          | TIM2_CH4             | -              | -              | -               | -                    | -         | USART2_RX                    |

|        | PA4  | -          | -                    | -              | -              | -               | SPI1_NSS             | SPI3_NSS  | USART2_CK                    |

|        | PA5  | -          | TIM2_CH1             | TIM2_ETR       | -              | -               | SPI1_SCK             | -         | -                            |

|        | PA6  | -          | TIM1_BKIN            | -              | -              | -               | SPI1_MISO            | COMP1_OUT | USART3_CTS                   |

|        | PA7  | -          | TIM1_CH1N            | -              | -              | I2C3_SCL        | SPI1_MOSI            | -         | -                            |

| Port A | PA8  | MCO        | TIM1_CH1             | -              | -              | -               | -                    | -         | USART1_CK                    |

|        | PA9  | -          | TIM1_CH2             | -              | -              | I2C1_SCL        | -                    | -         | USART1_TX                    |

|        | PA10 | -          | TIM1_CH3             | -              | -              | I2C1_SDA        | -                    | -         | USART1_RX                    |

|        | PA11 | -          | TIM1_CH4             | TIM1_BKIN2     | -              | -               | SPI1_MISO            | COMP1_OUT | USART1_CTS                   |

|        | PA12 | -          | TIM1_ETR             | -              | -              | -               | SPI1_MOSI            | -         | USART1_RTS_<br>DE            |

|        | PA13 | JTMS-SWDIO | IR_OUT               | -              | -              | -               | -                    | -         | -                            |

|        | PA14 | JTCK-SWCLK | LPTIM1_OUT           | -              | -              | I2C1_SMBA       | -                    | -         | -                            |

|        | PA15 | JTDI       | TIM2_CH1             | TIM2_ETR       | USART2_RX      | -               | SPI1_NSS             | SPI3_NSS  | USART3_RTS_<br>DE            |

DocID028798 Rev 2

5

50/149

| Bus  | Boundary address          | Size(bytes) | Peripheral |

|------|---------------------------|-------------|------------|

|      | 0x4001 1C00 - 0x4001 1FFF | 1 KB        | FIREWALL   |

|      | 0x4001 0800- 0x4001 1BFF  | 5 KB        | Reserved   |

| APB2 | 0x4001 0400 - 0x4001 07FF | 1 KB        | EXTI       |

| APDZ | 0x4001 0200 - 0x4001 03FF |             | COMP       |

|      | 0x4001 0030 - 0x4001 01FF | 1 KB        | Reserved   |

|      | 0x4001 0000 - 0x4001 002F |             | SYSCFG     |

|      | 0x4000 9800 - 0x4000 FFFF | 26 KB       | Reserved   |

|      | 0x4000 9400 - 0x4000 97FF | 1 KB        | LPTIM2     |

|      | 0x4000 8C00 - 0x4000 93FF | 2 KB        | Reserved   |

|      | 0x4000 8800 - 0x4000 8BFF | 1 KB        | SWPMI1     |

|      | 0x4000 8400 - 0x4000 87FF | 1 KB        | Reserved   |

|      | 0x4000 8000 - 0x4000 83FF | 1 KB        | LPUART1    |

|      | 0x4000 7C00 - 0x4000 7FFF | 1 KB        | LPTIM1     |

|      | 0x4000 7800 - 0x4000 7BFF | 1 KB        | OPAMP      |

|      | 0x4000 7400 - 0x4000 77FF | 1 KB        | DAC        |

|      | 0x4000 7000 - 0x4000 73FF | 1 KB        | PWR        |

|      | 0x4000 6C00 - 0x4000 6FFF | 1 KB        | USB SRAM   |

|      | 0x4000 6800 - 0x4000 6BFF | 1 KB        | USB FS     |

|      | 0x4000 6400 - 0x4000 67FF | 1 KB        | CAN1       |

| APB1 | 0x4000 6000 - 0x4000 63FF | 1 KB        | CRS        |

|      | 0x4000 5C00- 0x4000 5FFF  | 1 KB        | I2C3       |

|      | 0x4000 5800 - 0x4000 5BFF | 1 KB        | Reserved   |

|      | 0x4000 5400 - 0x4000 57FF | 1 KB        | I2C1       |

|      | 0x4000 4800 - 0x4000 53FF | 3 KB        | Reserved   |

|      | 0x4000 4400 - 0x4000 47FF | 1 KB        | USART2     |

|      | 0x4000 4000 - 0x4000 43FF | 1 KB        | Reserved   |

|      | 0x4000 3C00 - 0x4000 3FFF | 1 KB        | SPI3       |

|      | 0x4000 3400 - 0x4000 3BFF | 2 KB        | Reserved   |

|      | 0x4000 3000 - 0x4000 33FF | 1 KB        | IWDG       |

|      | 0x4000 2C00 - 0x4000 2FFF | 1 KB        | WWDG       |

|      | 0x4000 2800 - 0x4000 2BFF | 1 KB        | RTC        |

|      | 0x4000 1800 - 0x4000 27FF | 4 KB        | Reserved   |

|      | 0x4000 1400 - 0x4000 17FF | 1 KB        | TIM7       |

# Table 16. STM32L432xx memory map and peripheral register boundary addresses

| Bus  | Boundary address          | Size(bytes) | Peripheral |

|------|---------------------------|-------------|------------|

|      | 0x4000 1000 - 0x4000 13FF | 1 KB        | TIM6       |

| APB1 | 0x4000 0400- 0x4000 0FFF  | 3 KB        | Reserved   |

|      | 0x4000 0000 - 0x4000 03FF | 1 KB        | TIM2       |

Table 16. STM32L432xx memory map and peripheral register boundary addresses

1. The gray color is used for reserved boundary addresses.

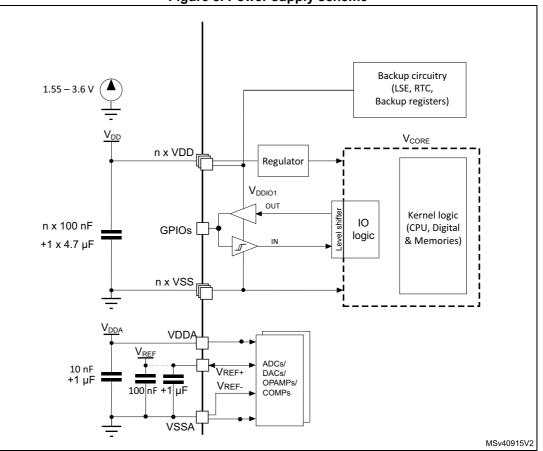

## 6.1.6 Power supply scheme

Figure 8. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

# 6.3.4 Embedded voltage reference

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

|                                           | 14,510 201 201,5044                                                 | eu internar voltage reie          |                  |       |                     |                          |

|-------------------------------------------|---------------------------------------------------------------------|-----------------------------------|------------------|-------|---------------------|--------------------------|

| Symbol                                    | Parameter                                                           | Conditions                        | Min              | Тур   | Мах                 | Unit                     |

| V <sub>REFINT</sub>                       | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +130 °C | 1.182            | 1.212 | 1.232               | V                        |

| t <sub>S_vrefint</sub> <sup>(1)</sup>     | ADC sampling time when<br>reading the internal reference<br>voltage | -                                 | 4 <sup>(2)</sup> | -     | -                   | μs                       |

| t <sub>start_vrefint</sub>                | Start time of reference voltage buffer when ADC is enable           | -                                 | -                | 8     | 12 <sup>(2)</sup>   | μs                       |

| I <sub>DD</sub> (V <sub>REFINTBUF</sub> ) | $V_{REFINT}$ buffer consumption from $V_{DD}$ when converted by ADC | -                                 | -                | 12.5  | 20 <sup>(2)</sup>   | μΑ                       |

| $\Delta V_{REFINT}$                       | Internal reference voltage spread over the temperature range        | V <sub>DD</sub> = 3 V             | -                | 5     | 7.5 <sup>(2)</sup>  | mV                       |

| T <sub>Coeff</sub>                        | Temperature coefficient                                             | –40°C < T <sub>A</sub> < +130°C   | -                | 30    | 50 <sup>(2)</sup>   | ppm/°C                   |

| A <sub>Coeff</sub>                        | Long term stability                                                 | 1000 hours, T = 25°C              | -                | -     | TBD <sup>(2)</sup>  | ppm                      |

| V <sub>DDCoeff</sub>                      | Voltage coefficient                                                 | 3.0 V < V <sub>DD</sub> < 3.6 V   | -                | 250   | 1200 <sup>(2)</sup> | ppm/V                    |

| V <sub>REFINT_DIV1</sub>                  | 1/4 reference voltage                                               |                                   | 24               | 25    | 26                  |                          |

| V <sub>REFINT_DIV2</sub>                  | 1/2 reference voltage                                               | -                                 | 49               | 50    | 51                  | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub>                  | 3/4 reference voltage                                               |                                   | 74               | 75    | 76                  |                          |

1. The shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

|                                        |                                                                              | Table 32. Cu                                                                   | rrent c  | onsum | ption i | n Stop | 2 mode | (contin | ued)  |       |                    |        |        |      |

|----------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-------|---------|--------|--------|---------|-------|-------|--------------------|--------|--------|------|

| Cumhal                                 | Parameter                                                                    | Conditions                                                                     |          |       |         | TYP    |        |         |       |       | MAX <sup>(1)</sup> |        |        | Unit |

| Symbol                                 | Parameter                                                                    | -                                                                              | $V_{DD}$ | 25 °C | 55 °C   | 85 °C  | 105 °C | 125 °C  | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | On   |

|                                        | Wakeup clock is<br>MSI = 48 MHz,<br>voltage Range 1.<br>See <sup>(3)</sup> . | 3 V                                                                            | 1.85     | -     | -       | -      | -      | -       | -     | -     | -                  | -      |        |      |

| I <sub>DD</sub> (wakeup<br>from Stop2) |                                                                              | Wakeup clock is<br>MSI = 4 MHz,<br>voltage Range 2.<br>See $^{(3)}$ .          | 3 V      | 1.52  | -       | -      | -      | -       | -     | -     | -                  | -      | -      | mA   |

|                                        |                                                                              | Wakeup clock is<br>HSI16 = 16 MHz,<br>voltage Range 1.<br>See <sup>(3)</sup> . | 3 V      | 1.54  | -       | -      | -      | -       | -     | -     | -                  | -      | -      |      |

1. Guaranteed based on test during characterization, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 38: Low-power mode wakeup timings.

DocID028798 Rev 2

Z

75/149

| Ш        |

|----------|

| e        |

| Õ        |

|          |

| <u> </u> |

| 8        |

| <u> </u> |

| 0        |

| ÷        |

| 2        |

| Ĩ        |

| a        |

| Q        |

| ጠ        |

| Ť        |

| 5        |

| Ť        |

| ō        |

| ö        |

|          |

|                                    |                           | Conditions                                                                | ions TYP |       |       |       | MAX <sup>(1)</sup> |        |       |       |       | Ur     |              |     |

|------------------------------------|---------------------------|---------------------------------------------------------------------------|----------|-------|-------|-------|--------------------|--------|-------|-------|-------|--------|--------------|-----|

| Symbol                             | Parameter                 | -                                                                         |          | 25 °C | 55 °C | 85 °C | 105 °C             | 125 °C | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C       |     |

|                                    |                           |                                                                           | 1.8 V    | 27.7  | 144   | 758   | 2 072              | 5 425  | 119   | 425   | 2866  | 7524   | 20510        | T   |

|                                    | O                         |                                                                           | 2.4 V    | 50.9  | 187   | 892   | 2 408              | 6 247  | 183   | 564   | 3383  | 8778   | 23768        |     |

|                                    | Supply current in Standby | no independent wateridog                                                  | 3 V      | 90.2  | 253   | 1 090 | 2 884              | 7 409  | 225   | 681   | 3912  | 10071  | 26976        |     |

| I <sub>DD</sub> (Standby)          | mode (backup              |                                                                           | 3.6 V    | 253   | 459   | 1 474 | 3 575              | 8 836  | 292   | 877   | 4638  | 11659  | 30758        | r   |

| DD(ctando)                         | registers<br>retained),   |                                                                           | 1.8 V    | 216   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

|                                    | RTC disabled              | with independent                                                          | 2.4 V    | 342   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

|                                    |                           | watchdog                                                                  | 3 V      | 416   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

|                                    |                           |                                                                           | 3.6 V    | 551   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

|                                    |                           |                                                                           | 1.8 V    | 287   | 407   | 989   | 2 230              | 5 396  | 585   | 944   | 3344  | 7866   | 20504        |     |

|                                    |                           | RTC clocked by LSI, no independent watchdog         upply current Standby | 2.4 V    | 386   | 526   | 1 201 | 2 638              | 6 274  | 811   | 1230  | 4007  | 9246   | 23824        |     |

|                                    |                           |                                                                           | 3 V      | 513   | 679   | 1 478 | 3 167              | 7 414  | 1022  | 1521  | 4683  | 10671  | 27124        |     |

|                                    |                           |                                                                           | 3.6 V    | 771   | 978   | 1 963 | 3 992              | 9 039  | 1284  | 1924  | 5577  | 12383  | 30954<br>(2) | n   |

|                                    |                           |                                                                           | 1.8 V    | 342   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

|                                    | Supply current            |                                                                           | 2.4 V    | 521   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

|                                    | in Standby                |                                                                           | 3 V      | 655   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

| I <sub>DD</sub> (Standby with RTC) | mode (backup<br>registers |                                                                           | 3.6 V    | 865   | -     | -     | -                  | -      | -     | -     | -     | -      | -            |     |

| with ((10)                         | retained),                |                                                                           | 1.8 V    | 142   | 126   | 865   | 2 220              | 5 650  | -     | -     | -     | -      | -            |     |

|                                    | RTC enabled               | RTC clocked by LSE                                                        | 2.4 V    | 249   | 219   | 1 090 | 2 660              | 6 600  | -     | -     | -     | -      | -            |     |

|                                    |                           | bypassed at 32768Hz                                                       | 3 V      | 404   | 364   | 1 410 | 3 260              | 7 850  | -     | -     | -     | -      | -            |     |

|                                    |                           |                                                                           | 3.6 V    | 742   | 670   | 2 000 | 4 230              | 9 700  | -     | -     | -     | -      | -            | _ r |

|                                    |                           |                                                                           | 1.8 V    | 281   | 423   | 1 046 | 2 410              | 5 700  | -     | -     | -     | -      | -            |     |

|                                    |                           | RTC clocked by LSE                                                        | 2.4 V    | 388   | 548   | 1 268 | 2 847              | 6 564  | -     | -     | -     | -      | -            |     |

|                                    |                           | quartz <sup>(3)</sup> in low drive mode                                   | 3 V      | 535   | 715   | 1 565 | 3 420              | 7 694  | -     | -     | -     | -      | -            |     |

|                                    |                           |                                                                           | 3.6 V    | 836   | 1 048 | 2 081 | 4 311              | 9 338  | -     | -     | -     | -      | -            |     |

78/149

DocID028798 Rev 2

5

| Multi-speed internal ( | (MSI) RC | oscillator |

|------------------------|----------|------------|

|------------------------|----------|------------|

| Symbol                     | Parameter                                           |                   | Conditions                     | Min      | Тур     | Мах    | Unit |   |

|----------------------------|-----------------------------------------------------|-------------------|--------------------------------|----------|---------|--------|------|---|

|                            |                                                     |                   | Range 0                        | 98.7     | 100     | 101.3  |      |   |

|                            |                                                     |                   | Range 1                        | 197.4    | 200     | 202.6  | kHz  |   |

|                            |                                                     |                   | Range 2                        | 394.8    | 400     | 405.2  |      |   |

|                            |                                                     |                   | Range 3                        | 789.6    | 800     | 810.4  |      |   |

|                            |                                                     |                   | Range 4                        | 0.987    | 1       | 1.013  |      |   |

|                            |                                                     | MSI mode          | Range 5                        | 1.974    | 2       | 2.026  |      |   |

|                            |                                                     | MSI Mode          | Range 6                        | 3.948    | 4       | 4.052  |      |   |

|                            |                                                     |                   | Range 7                        | 7.896    | 8       | 8.104  | MHz  |   |

|                            |                                                     |                   | Range 8                        | 15.79    | 16      | 16.21  |      |   |

|                            |                                                     |                   | Range 9                        | 23.69    | 24      | 24.31  |      |   |

| f <sub>MSI</sub>           | MSI frequency<br>after factory<br>calibration, done |                   | Range 10                       | 31.58    | 32      | 32.42  |      |   |

|                            |                                                     |                   | Range 11                       | 47.38    | 48      | 48.62  |      |   |

|                            | at $V_{DD}$ =3 V and $T_A$ =30 °C                   |                   | Range 0                        | -        | 98.304  | -      |      |   |

|                            |                                                     |                   | Range 1                        | -        | 196.608 | -      | kHz  |   |

|                            |                                                     |                   | Range 2                        | -        | 393.216 | -      |      |   |

|                            |                                                     |                   | Range 3                        | -        | 786.432 | -      |      |   |

|                            |                                                     |                   | Range 4                        | -        | 1.016   | -      |      |   |

|                            |                                                     | PLL mode<br>XTAL= | Range 5                        | -        | 1.999   | -      |      |   |

|                            |                                                     | 32.768 kHz        | Range 6                        | -        | 3.998   | -      |      |   |

|                            |                                                     |                   | Range 7                        | -        | 7.995   | -      | MHz  |   |

|                            |                                                     |                   | Range 8                        | -        | 15.991  | -      |      |   |

|                            |                                                     |                   | Range 9                        | -        | 23.986  | -      |      |   |

|                            |                                                     |                   | Range 10                       | Range 10 | -       | 32.014 | -    | ] |

|                            |                                                     |                   | Range 11                       | -        | 48.005  | -      |      |   |

| (2)                        | MSI oscillator                                      |                   | T <sub>A</sub> = -0 to 85 °C   | -3.5     | -       | 3      |      |   |

| $\Delta_{TEMP}(MSI)^{(2)}$ | frequency drift over temperature                    | MSI mode          | T <sub>A</sub> = -40 to 125 °C | -8       | -       | 6      | %    |   |

Table 45. MSI oscillator characteristics<sup>(1)</sup>

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                       | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |      |

|------------------|------------|--------------------------------------------------|-----------------------------|---------------------------------------------------|------|------|

|                  |            |                                                  | inequency band              | 8 MHz/ 80 MHz                                     |      |      |

|                  |            |                                                  | 0.1 MHz to 30 MHz           | 1                                                 |      |      |

|                  |            | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C, | 30 MHz to 130 MHz           | 0                                                 | dBµV |      |

| S <sub>EMI</sub> | Peak level | UFQFPN32 package compliant with IEC              |                             | 130 MHz to 1 GHz                                  | -1   | υБμν |

|                  |            | 61967-2                                          | 1 GHz to 2 GHz              | 7                                                 |      |      |

|                  |            |                                                  | EMI Level                   | 1                                                 | -    |      |

Table 52. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symb                | Ratings                                                     | Conditions                                                    | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|---------------------|-------------------------------------------------------------|---------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(H</sub>  | Electrostatic discharge<br>voltage (human body model)       | $T_A$ = +25 °C, conforming<br>to ANSI/ESDA/JEDEC<br>JS-001    | 2     | 2000                            | V    |

| V <sub>ESD(CI</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25 \degree C$ ,<br>conforming to ANSI/ESD<br>STM5.3.1 | C3    | 250                             | v    |

| Table 53. | ESD absolut | e maximum | ratings |

|-----------|-------------|-----------|---------|

|           |             |           |         |

1. Guaranteed by characterization results.

| Sym-<br>bol | Parameter             | (                                     | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit |

|-------------|-----------------------|---------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|             |                       |                                       | Single                   | Fast channel (max speed) | -    | 4    | 5   |      |

| ET          | Total                 |                                       | ended                    | Slow channel (max speed) | -    | 4    | 5   |      |

| EI          | unadjusted<br>error   |                                       | Differential             | Fast channel (max speed) | -    | 3.5  | 4.5 |      |

|             |                       |                                       | Differential             | Slow channel (max speed) | -    | 3.5  | 4.5 |      |

|             |                       |                                       | Single                   | Fast channel (max speed) | -    | 1    | 2.5 |      |

| EO          | Offset                |                                       | ended                    | Slow channel (max speed) | -    | 1    | 2.5 |      |

| EO          | error                 |                                       | Differential             | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

|             |                       |                                       | Differential             | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

|             |                       |                                       | Single                   | Fast channel (max speed) | -    | 2.5  | 4.5 |      |

| 50          | Coin orror            |                                       | ended                    | Slow channel (max speed) | -    | 2.5  | 4.5 | LSB  |

| EG          | Gain error            |                                       | Differential             | Fast channel (max speed) | -    | 2.5  | 3.5 | LOD  |

|             |                       |                                       | Differential             | Slow channel (max speed) | -    | 2.5  | 3.5 | -    |

|             |                       |                                       | Single                   | Fast channel (max speed) | -    | 1    | 1.5 |      |

| ED          | Differential          |                                       | ended                    | Slow channel (max speed) | -    | 1    | 1.5 |      |

| ED          | linearity<br>error    | rror ADC clock frequency ≤            | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |      |

|             |                       | 80 MHz,<br>Sampling rate ≤ 5.33 Msps, | Dillerential             | Slow channel (max speed) | -    | 1    | 1.2 |      |

|             |                       | $V_{DDA} = VREF + = 3 V,$             | Single                   | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

| EL          | Integral<br>linearity | TA = 25 °C                            | ended                    | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

| EL          | error                 |                                       | Differential             | Fast channel (max speed) | -    | 1    | 2   |      |

|             |                       |                                       | Differential             | Slow channel (max speed) | -    | 1    | 2   |      |

|             |                       |                                       | Single                   | Fast channel (max speed) | 10.4 | 10.5 | -   |      |

| ENOB        | Effective number of   |                                       | ended                    | Slow channel (max speed) | 10.4 | 10.5 | -   | bits |

| LINOD       | bits                  |                                       | Differential             | Fast channel (max speed) | 10.8 | 10.9 | -   | 5113 |

|             |                       |                                       | Differentia              | Slow channel (max speed) | 10.8 | 10.9 | -   |      |

|             | Signal-to-            |                                       | Single                   | Fast channel (max speed) | 64.4 | 65   | -   |      |

| SINAD       | noise and             |                                       | ended                    | Slow channel (max speed) | 64.4 | 65   | -   |      |

| OINAD       | NAD distortion ratio  |                                       | Differential             | Fast channel (max speed) | 66.8 | 67.4 | -   |      |

|             | 1410                  |                                       | Differential             | Slow channel (max speed) | 66.8 | 67.4 | -   | dB   |

|             |                       |                                       | Single                   | Fast channel (max speed) | 65   | 66   | -   | чD   |

| SNR         | Signal-to-            |                                       | ended                    | Slow channel (max speed) | 65   | 66   | -   |      |

|             | noise ratio           |                                       | Differential             | Fast channel (max speed) | 67   | 68   | -   |      |

|             |                       |                                       | Dinerential              | Slow channel (max speed) | 67   | 68   | -   |      |

# Table 63. ADC accuracy - limited test conditions $1^{(1)(2)(3)}$

| Symbol             | Parameter              | Conditions                                                   | Min | Тур  | Max  | Unit |

|--------------------|------------------------|--------------------------------------------------------------|-----|------|------|------|

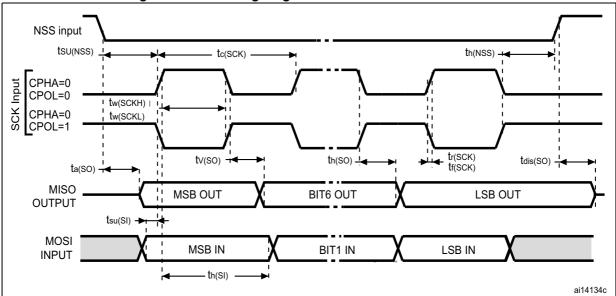

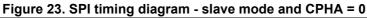

|                    |                        | Slave mode 2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  | -   | 12.5 | 13.5 |      |

| t <sub>v(SO)</sub> | Data output valid time | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 | -   | 12.5 | 24   | ns   |

|                    |                        | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 2 | -   | 12.5 | 33   |      |

| t <sub>v(MO)</sub> |                        | Master mode                                                  | -   | 4.5  | 6    |      |

| t <sub>h(SO)</sub> | Data output hold time  | Slave mode                                                   | 7   | -    | -    | - ns |

| t <sub>h(MO)</sub> |                        | Master mode                                                  | 0   | -    | -    | 115  |

## Table 76. SPI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50 %.

| Symbol               | Parameter              | Conditions                                                                   | Min                    | Тур | Max                    | Unit |

|----------------------|------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

|                      |                        | $1.71 < V_{DD} < 3.6 V$ , $C_{LOAD} = 20 pF$<br>Voltage Range 1              | -                      | -   | 40                     |      |

| F <sub>CK</sub>      | Quad SPI clock         | 2 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1    | -                      | -   | 48                     | MHz  |

| 1/t <sub>(СК)</sub>  | frequency              | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1 | -                      | -   | 48                     |      |

|                      |                        | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2  | -                      | -   | 26                     |      |

| t <sub>w(CKH)</sub>  | Quad SPI clock high    | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |      |

| t <sub>w(CKL)</sub>  | and low time           | AHBCLK - 40 MITZ, presc-0                                                    | t <sub>(CK)</sub> /2   | -   | t <sub>(CK)</sub> /2+2 |      |

|                      | Data input setup time  | Voltage Range 1                                                              | 1                      |     | _                      |      |

| t <sub>sr(IN)</sub>  | on rising edge         | Voltage Range 2                                                              | 3.5                    | -   | -                      |      |

| 4                    | Data input setup time  | Voltage Range 1                                                              | 1<br>1.5               |     |                        |      |

| t <sub>sf(IN)</sub>  | on falling edge        | Voltage Range 2                                                              |                        | -   | -                      |      |

| +                    | Data input hold time   | Voltage Range 1                                                              | 6                      |     |                        |      |

| t <sub>hr(IN)</sub>  | on rising edge         | Voltage Range 2                                                              | 6.5                    | -   | -                      |      |

|                      | Data input hold time   | Voltage Range 1                                                              | 5.5                    |     |                        |      |

| t <sub>hf(IN)</sub>  | on falling edge        | Voltage Range 2                                                              | 5.5                    | -   | -                      | ns   |

| +                    | Data output valid time | Voltage Range 1                                                              |                        | 5   | 5.5                    |      |

| t <sub>vr(OUT)</sub> | on rising edge         | Voltage Range 2                                                              | -                      | 9.5 | 14                     | Ť    |

| 1                    | Data output valid time | Voltage Range 1                                                              |                        | 5   | 8.5                    |      |

| t <sub>vf(OUT)</sub> | on falling edge        | Voltage Range 2                                                              | -                      | 15  | 19                     | †    |

| +                    | Data output hold time  | Voltage Range 1                                                              | 3.5                    | -   |                        |      |

| t <sub>hr(OUT)</sub> | on rising edge         | Voltage Range 2                                                              | 8 -                    |     | -                      |      |

| +                    | Data output hold time  | Voltage Range 1                                                              | 3.5                    | -   |                        |      |

| t <sub>hf(OUT)</sub> | on falling edge        | Voltage Range 2                                                              | 13                     | -   | _                      |      |

| Table 78. QUADSPI characteristics in DDR mode <sup>(1)</sup> |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

1. Guaranteed by characterization results.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Feb-2016 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 31-May-2016 | 2        | <ul> <li>Updated document title.</li> <li>Updated Table 1: STM32L432Kx family device features and peripheral counts.</li> <li>Updated Section 3.24: Universal synchronous/asynchronous receiver transmitter (USART).</li> <li>Updated Table 13: STM32L432xx pin definitions.</li> <li>Updated Table 15: Alternate function AF8 to AF15 (for AF0 to AF7 see Table 14).</li> <li>Updated Table 20: General operating conditions.</li> <li>Added Figure 10: VREFINT versus temperature.</li> <li>Updated Table 22: Embedded reset and power control block characteristics.</li> <li>Updated Table 24 to Table 26 and Table 30 to Table 38.</li> <li>Updated Table 45: MSI oscillator characteristics.</li> <li>Added Table 46: HSI48 oscillator characteristics.</li> <li>Added Figure 16: HSI48 frequency versus temperature.</li> <li>Updated Table 51: EMS characteristics.</li> <li>Updated Table 52: EMI characteristics.</li> <li>Updated Table 52: EMI characteristics.</li> <li>Updated Table 60: Analog switches booster characteristics.</li> <li>Updated Table 60: Analog switches booster characteristics.</li> <li>Updated Table 60: COMP characteristics.</li> <li>Updated Table 60: SWPMI characteristics.</li> <li>Updated Table 60: SWPMI characteristics.</li> </ul> |

| Table 85. Document revision history | Table 85. | Document revis | sion history |

|-------------------------------------|-----------|----------------|--------------|

|-------------------------------------|-----------|----------------|--------------|

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved