Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 16KB (5.5K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 512 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka301-e-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                | 1   |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 1/0 | Buffer            | Description                       |

| AN0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | Т   | ANA               |                                   |

| AN2      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               |                                   |

| AN3      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               |                                   |

| AN4      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ANA               |                                   |

| AN5      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I   | ANA               |                                   |

| AN6      | _                                | _                                 | _             | 25                     | 27             | _                                | _                                 | _             | 25                     | 27             | I   | ANA               |                                   |

| AN7      | _                                | _                                 | _             | 26                     | 28             | _                                | —                                 | _             | 26                     | 28             | I   | ANA               |                                   |

| AN8      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I   | ANA               |                                   |

| AN9      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ANA               |                                   |

| AN10     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA               |                                   |

| AN11     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | Т   | ANA               |                                   |

| AN12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | Т   | ANA               |                                   |

| AN13     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | Т   | ANA               |                                   |

| AN14     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ANA               |                                   |

| AN15     | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA               |                                   |

| ASCL1    | -                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | l <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | -                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | l <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                                | 25            | 17                     | 18             | 20                               | 28                                | 25            | 17                     | 18             | 1   | ANA               | A/D Supply Pins                   |

| AVss     | 19                               | 27                                | 24            | 16                     | 17             | 19                               | 27                                | 24            | 16                     | 17             | Т   | ANA               |                                   |

| C1INA    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | 1   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | 1   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 1 Input D (-)          |

| C1OUT    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | —                 | Comparator 1 Output               |

| C2INA    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ANA               | Comparator 2 Input A (+)          |

| C2INB    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 2 Input B (-)          |

| C2INC    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | I   | ANA               | Comparator 2 Input C (+)          |

| C2IND    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | I   | ANA               | Comparator 2 Input D (-)          |

| C2OUT    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 16                                | 13            | 43                     | 47             | 0   | —                 | Comparator 2 Output               |

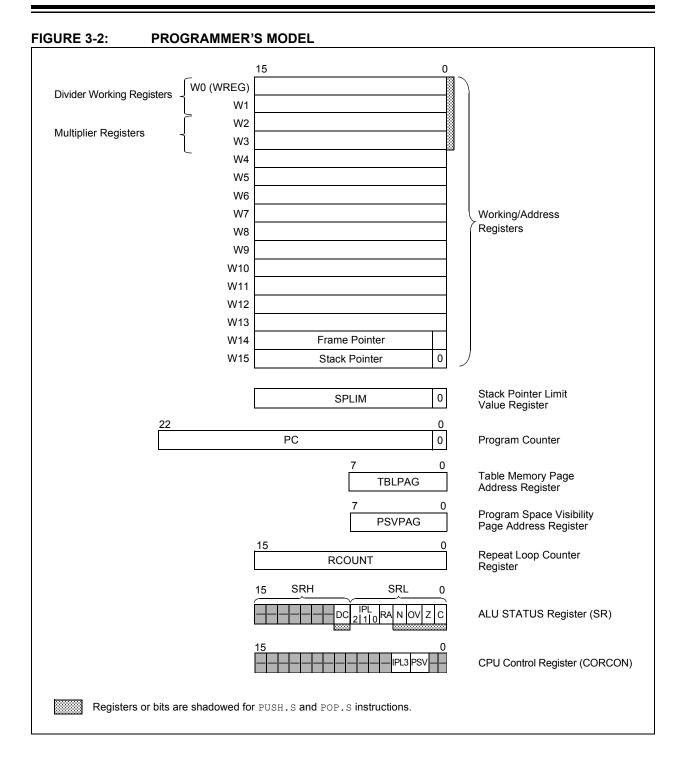

#### TABLE 4-3: CPU CORE REGISTERS MAP

| IADEE -   | т-∪.          |        | OOKE       |            |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

|-----------|---------------|--------|------------|------------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Start<br>Addr | Bit 15 | Bit 14     | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| WREG0     | 0000          |        |            |            |        |        |        |       | WF    | REG0  |       |       |       |       |       |       |       | 0000          |

| WREG1     | 0002          |        |            |            |        |        |        |       | WF    | REG1  |       |       |       |       |       |       |       | 0000          |

| WREG2     | 0004          |        |            |            |        |        |        |       | WF    | REG2  |       |       |       |       |       |       |       | 0000          |

| WREG3     | 0006          |        |            |            |        |        |        |       | WF    | REG3  |       |       |       |       |       |       |       | 0000          |

| WREG4     | 0008          |        | WREG4 00   |            |        |        |        |       |       |       |       | 0000  |       |       |       |       |       |               |

| WREG5     | 000A          |        | WREG5 0000 |            |        |        |        |       |       |       |       |       | 0000  |       |       |       |       |               |

| WREG6     | 000C          |        |            | WREG6 0000 |        |        |        |       |       |       |       |       | 0000  |       |       |       |       |               |

| WREG7     | 000E          |        |            |            |        |        |        |       | WF    | REG7  |       |       |       |       |       |       |       | 0000          |

| WREG8     | 0010          |        |            |            |        |        |        |       | WF    | REG8  |       |       |       |       |       |       |       | 0000          |

| WREG9     | 0012          |        |            |            |        |        |        |       | WF    | REG9  |       |       |       |       |       |       |       | 0000          |

| WREG10    | 0014          |        |            |            |        |        |        |       | WR    | EG10  |       |       |       |       |       |       |       | 0000          |

| WREG11    | 0016          |        |            |            |        |        |        |       | WR    | EG11  |       |       |       |       |       |       |       | 0000          |

| WREG12    | 0018          |        |            |            |        |        |        |       | WR    | EG12  |       |       |       |       |       |       |       | 0000          |

| WREG13    | 001A          |        |            |            |        |        |        |       | WR    | EG13  |       |       |       |       |       |       |       | 0000          |

| WREG14    | 001C          |        |            |            |        |        |        |       | WR    | EG14  |       |       |       |       |       |       |       | 0000          |

| WREG15    | 001E          |        |            |            |        |        |        |       | WR    | EG15  |       |       |       |       |       |       |       | 0000          |

| SPLIM     | 0020          |        |            |            |        |        |        |       | SF    | PLIM  |       |       |       |       |       |       |       | XXXX          |

| PCL       | 002E          |        |            |            |        |        |        |       | F     | PCL   |       |       |       |       |       |       |       | 0000          |

| PCH       | 0030          | _      | _          | _          | _      | _      | _      | _     | _     | _     |       |       |       | PCH   |       |       |       | 0000          |

| TBLPAG    | 0032          |        | _          |            | —      | —      |        | —     | —     |       |       |       | TBI   | _PAG  |       |       |       | 0000          |

| PSVPAG    | 0034          |        | PSVPAG 00  |            |        |        |        |       |       |       | 0000  |       |       |       |       |       |       |               |

| RCOUNT    | 0036          |        | RCOUNT     |            |        |        |        |       |       |       | XXXXX |       |       |       |       |       |       |               |

| SR        | 0042          | _      | _          |            | -      | -      |        | _     | DC    | IPL2  | IPL1  | IPL0  | RA    | Ν     | OV    | Z     | С     | 0000          |

| CORCON    | 0044          |        | _          | -          | _      | _      |        | _     | —     | —     | _     | _     | -     | IPL3  | PSV   | —     | _     | 0000          |

| DISICNT   | 0052          |        | _          |            |        |        |        |       |       | DISIC | NT    |       |       |       |       |       |       | XXXX          |

|           |               |        |            |            |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

DS39995D-page 39

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-8: OUTPUT COMPARE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                                                                                  | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6    | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|---------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|--------|--------|--------|----------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1   | 0190 |        | _                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1 | ENFLT0 | OCFLT2   | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2   | 0192 | FLTMD  | FLTOUT                                                                                                  | FLTTRIEN | OCINV   |         | DCB1    | DCB0   | OC32   | OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS     | 0194 |        | OC1RS 0000                                                                                              |          |         |         |         |        |        |        |          |        |          |          |          |          |          |               |

| OC1R      | 0196 |        |                                                                                                         |          |         |         |         |        |        | OC1R   |          |        |          |          |          |          |          | 0000          |

| OC1TMR    | 0198 |        | OC1TMR XXXX                                                                                             |          |         |         |         |        |        |        |          |        |          |          |          |          |          |               |

| OC2CON1   | 019A | _      | - OCSIDL OCTSEL2 OCTSEL1 OCTSEL0 ENFLT2 ENFLT1 ENFLT0 OCFLT2 OCFLT1 OCFLT0 TRIGMODE OCM2 OCM1 OCM0 0000 |          |         |         |         |        |        |        |          |        |          |          |          |          |          |               |

| OC2CON2   | 019C | FLTMD  | FLTOUT                                                                                                  | FLTTRIEN | OCINV   |         | DCB1    | DCB0   | OC32   | OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS     | 019E |        |                                                                                                         |          |         |         |         |        |        | OC2RS  |          |        |          |          |          |          |          | 0000          |

| OC2R      | 01A0 |        |                                                                                                         |          |         |         |         |        |        | OC2R   |          |        |          |          |          |          |          | 0000          |

| OC2TMR    | 01A2 |        |                                                                                                         |          |         |         |         |        |        | OC2TMR |          |        |          |          |          |          |          | XXXX          |

| OC3CON1   | 01A4 |        |                                                                                                         | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1 | ENFLT0 | OCFLT2   | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2   | 01A6 | FLTMD  | FLTOUT                                                                                                  | FLTTRIEN | OCINV   |         | DCB1    | DCB0   | OC32   | OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS     | 01A8 |        |                                                                                                         |          |         |         |         |        |        | OC3RS  |          |        |          |          |          |          |          | 0000          |

| OC3R      | 01AA |        |                                                                                                         |          |         |         |         |        |        | OC3R   |          |        |          |          |          |          |          | 0000          |

| OC3TMR    | 01AC |        | OC3TMR xxxx                                                                                             |          |         |         |         |        |        |        |          |        |          |          |          |          |          |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is as follows:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '011000' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

| MOV #0x4058, W0                  | ;                                       |

|----------------------------------|-----------------------------------------|

| MOV W0, NVMCON                   | ; Initialize NVMCON                     |

| Init pointer to row to be ERASED |                                         |

| MOV #tblpage(PROG_ADDR), W0      | ;                                       |

| MOV W0, TBLPAG                   | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W     | 0 ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                  | ; Set base address of erase block       |

| DISI #5                          | ; Block all interrupts                  |

|                                  | for next 5 instructions                 |

| MOV #0x55, W0                    |                                         |

| MOV W0, NVMKEY                   | ; Write the 55 key                      |

| MOV #0xAA, W1                    | ;                                       |

| MOV W1, NVMKEY                   | ; Write the AA key                      |

| BSET NVMCON, #WR                 | ; Start the erase sequence              |

| NOP                              | ; Insert two NOPs after the erase       |

| NOP                              | ; command is asserted                   |

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

#### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE Reset - GOTO Instruction 000000h Reset - GOTO Address 000002h Reserved 000004h Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000014h Interrupt Vector 1 \_ Interrupt Vector 52 00007Ch Interrupt Vector Table (IVT)<sup>(1)</sup> Decreasing Natural Order Priority Interrupt Vector 53 00007Eh Interrupt Vector 54 000080h \_ Interrupt Vector 116 0000FCh Interrupt Vector 117 0000FEh Reserved 000100h Reserved 000102h Reserved Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000114h Interrupt Vector 1 Alternate Interrupt Vector Table (AIVT)<sup>(1)</sup> 00017Ch Interrupt Vector 52 00017Eh Interrupt Vector 53 Interrupt Vector 54 000180h \_\_\_\_\_ Interrupt Vector 116 Interrupt Vector 117 0001FEh Start of Code 000200h

Note 1: See Table 8-2 for the interrupt vector list.

#### REGISTER 8-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| R/W-0, HS        | R/W-0, HS                              | R/W-0, HS                          | R/W-0, HS       | R/W-0, HS         | U-0              | R/W-0, HS        | U-0     |  |  |  |  |  |

|------------------|----------------------------------------|------------------------------------|-----------------|-------------------|------------------|------------------|---------|--|--|--|--|--|

| U2TXIF           | U2RXIF                                 | INT2IF                             | T5IF            | T4IF              | —                | OC3IF            |         |  |  |  |  |  |

| bit 15           |                                        |                                    |                 |                   |                  |                  | bit 8   |  |  |  |  |  |

|                  |                                        |                                    |                 |                   |                  |                  |         |  |  |  |  |  |

| U-0              | U-0                                    | U-0                                | R/W-0, HS       | R/W-0, HS         | R/W-0, HS        | R/W-0            | R/W-0   |  |  |  |  |  |

|                  |                                        | —                                  | INT1IF          | CNIF              | CMIF             | MI2C1IF          | SI2C1IF |  |  |  |  |  |

| bit 7            |                                        |                                    |                 |                   |                  |                  | bit 0   |  |  |  |  |  |

| Legend:          |                                        | HS = Hardwa                        | ro Sottabla bit |                   |                  |                  |         |  |  |  |  |  |

| R = Readable     | a hit                                  | W = Writable                       |                 | II = I Inimplem   | nented bit, read | 1 as 'O'         |         |  |  |  |  |  |

| -n = Value at    |                                        | '1' = Bit is set                   | on              | '0' = Bit is clea |                  | x = Bit is unkne | own     |  |  |  |  |  |

| II Value at      |                                        |                                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 15           | U2TXIF: UAR                            | RT2 Transmitter                    | Interrupt Flag  | Status bit        |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    |                 |                   |                  |                  |         |  |  |  |  |  |

|                  | 0 = Interrupt r                        | request has not                    | occurred        |                   |                  |                  |         |  |  |  |  |  |

| bit 14           | U2RXIF: UAF                            | RT2 Receiver Ir                    | terrupt Flag St | atus bit          |                  |                  |         |  |  |  |  |  |

|                  | •                                      | request has occ                    |                 |                   |                  |                  |         |  |  |  |  |  |

| h:+ 40           | -                                      | request has not                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 13           |                                        | rnal Interrupt 2                   | -               |                   |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has not                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 12           | -                                      | Interrupt Flag S                   |                 |                   |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    |                 |                   |                  |                  |         |  |  |  |  |  |

|                  | 0 = Interrupt request has not occurred |                                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 11           | T4IF: Timer4                           | Interrupt Flag S                   | Status bit      |                   |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    |                 |                   |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has not                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 10           | •                                      | ted: Read as '                     |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 9            |                                        | ut Compare Ch                      |                 | pt Flag Status b  | bit              |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    |                 |                   |                  |                  |         |  |  |  |  |  |

| h# 0 5           | -                                      | request has not                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 8-5<br>bit 4 | •                                      | ted: Read as '                     |                 |                   |                  |                  |         |  |  |  |  |  |

| DIL 4            |                                        | rnal Interrupt 1                   | -               |                   |                  |                  |         |  |  |  |  |  |

|                  | •                                      | request has not                    |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 3            | -                                      | Change Notifica                    |                 | lag Status bit    |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    | -               | U                 |                  |                  |         |  |  |  |  |  |

|                  | 0 = Interrupt r                        | request has not                    | occurred        |                   |                  |                  |         |  |  |  |  |  |

| bit 2            | -                                      | arator Interrupt                   | -               |                   |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    |                 |                   |                  |                  |         |  |  |  |  |  |

| h:+ 1            | -                                      | request has not                    |                 | Ctatua hit        |                  |                  |         |  |  |  |  |  |

| bit 1            |                                        | ster I2C1 Event                    |                 | Status bit        |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ<br>request has not |                 |                   |                  |                  |         |  |  |  |  |  |

| bit 0            | -                                      | ve I2C1 Event I                    |                 | tatus bit         |                  |                  |         |  |  |  |  |  |

|                  |                                        | request has occ                    |                 | ·····             |                  |                  |         |  |  |  |  |  |

|                  |                                        |                                    |                 |                   |                  |                  |         |  |  |  |  |  |

#### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                   | R/W-0                                | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------|-------------------------|--------------------------------------|------------------|------------------|------------------|-----------------|---------|

| _                | U1RXIP2                 | U1RXIP1                              | U1RXIP0          | _                | SPI1IP2          | SPI1IP1         | SPI1IP0 |

| bit 15           |                         |                                      |                  |                  |                  |                 | bit 8   |

| U-0              | R/W-1                   | R/W-0                                | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                | SPF1IP2                 | SPF1IP1                              | SPF1IP0          |                  | T3IP2            | T3IP1           | T3IP0   |

| bit 7            |                         | 1                                    |                  |                  |                  | 1               | bit (   |

| Legend:          |                         |                                      |                  |                  |                  |                 |         |

| R = Readat       | ole bit                 | W = Writable                         | bit              | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value a     | at POR                  | '1' = Bit is set                     |                  | '0' = Bit is cle |                  | x = Bit is unkn | iown    |

|                  |                         |                                      |                  |                  |                  |                 |         |

| bit 15           | Unimplemen              | ted: Read as '                       | )'               |                  |                  |                 |         |

| bit 14-12        | -                       | : UART1 Rece                         |                  | riority bits     |                  |                 |         |

|                  |                         | pt is Priority 7 (                   | =                | -                |                  |                 |         |

|                  | •                       |                                      | 0 . ,            | • /              |                  |                 |         |

|                  | •                       |                                      |                  |                  |                  |                 |         |

|                  | 001 = Interru           |                                      |                  |                  |                  |                 |         |

|                  | -                       | ot source is dis                     |                  |                  |                  |                 |         |

| bit 11           | -                       | ted: Read as '                       |                  |                  |                  |                 |         |

| bit 10-8         |                         | SPI1 Event Int                       | , ,              |                  |                  |                 |         |

|                  | 111 = Interru           | pt is Priority 7 (                   | highest priority | interrupt)       |                  |                 |         |

|                  | •                       |                                      |                  |                  |                  |                 |         |

|                  | •<br>001 = Interru      | pt is Priority 1                     |                  |                  |                  |                 |         |

|                  | 000 = Interru           | pt source is dis                     | abled            |                  |                  |                 |         |

| bit 7            | Unimplemen              | ted: Read as '                       | )'               |                  |                  |                 |         |

| bit 6-4          | SPF1IP<2:0>             | : SPI1 Fault Inf                     | errupt Priority  | oits             |                  |                 |         |

|                  | 111 = Interru           | pt is Priority 7 (                   | highest priority | interrupt)       |                  |                 |         |

|                  | •                       |                                      |                  |                  |                  |                 |         |

|                  | •                       |                                      |                  |                  |                  |                 |         |

|                  | 001 = Interru           | pt is Priority 1<br>pt source is dis | abled            |                  |                  |                 |         |

|                  | -                       | ted: Read as '                       |                  |                  |                  |                 |         |

| hit 3            |                         | imer3 Interrupt                      |                  |                  |                  |                 |         |

|                  |                         |                                      | •                | interrunt)       |                  |                 |         |

|                  | 111 = Interru           | nt is Priority 7 (                   |                  |                  |                  |                 |         |

|                  | 111 = Interruj<br>•     | pt is Priority 7 (                   | nignest priority | interrupt)       |                  |                 |         |

| bit 3<br>bit 2-0 | 111 = Interruj<br>•     | pt is Priority 7 (                   | nignest phonty   | interrupt)       |                  |                 |         |

|                  | •<br>•<br>001 = Interru |                                      |                  | interrupt)       |                  |                 |         |

NOTES:

#### 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FV32KA304 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals (CN0 through CN22) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the ICN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately, using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

**Note:** Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB; | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs $\$ |

|-----------------------------------|-----------------------------------------------------------------|

| NOP;                              | //Delay 1 cycle                                                 |

| BTSS PORTB, #13;                  | //Next Instruction                                              |

| Equivalent <b>`</b> C' Code       |                                                                 |

| TRISB = 0xFF00;                   | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs     |

| NOP();                            | //Delay 1 cycle                                                 |

| if(PORTBbits.RB13 == 1)           | // execute following code if PORTB pin 13 is set.               |

| {                                 |                                                                 |

| }                                 |                                                                 |

#### 18.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 18-1 provides the formula for computation of the baud rate with BRGH = 0.

### EQUATION 18-1: UARTX BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$   $UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$ Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 18-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is Fcy/16 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(16 \* 65536).

Equation 18-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 18-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

Baud Rate =  $\frac{FCY}{4 \cdot (UxBRG + 1)}$  $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

### **EXAMPLE 18-1:** BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | =   | FCY/(16 (UxBRG + 1))                                                                           |

|----------------------|-----|------------------------------------------------------------------------------------------------|

| Solving for UxBRG va | lue | :                                                                                              |

| UxBRG<br>UxBRG       | =   | ((FCY/Desired Baud Rate)/16) – 1<br>((4000000/9600)/16) – 1                                    |

| UxBRG                | =   | 25                                                                                             |

| Calculated Baud Rate |     | 4000000/(16 (25 + 1))<br>9615                                                                  |

| Error                | =   | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate<br>(9615 – 9600)/9600<br>0.16% |

| Note 1: Based on     | Fc  | Y = Fosc/2; Doze mode and PLL are disabled.                                                    |

| R/W-0         | U-0                            | R/W-0                             | U-0             | U-0                          | U-0              | U-0              | U-0            |

|---------------|--------------------------------|-----------------------------------|-----------------|------------------------------|------------------|------------------|----------------|

| HLVDEN        | _                              | HLSIDL                            |                 | —                            | —                | —                |                |

| bit 15        |                                |                                   |                 |                              |                  |                  | bit 8          |

|               |                                |                                   |                 |                              |                  |                  |                |

| R/W-0         | R/W-0                          | R/W-0                             | U-0             | R/W-0                        | R/W-0            | R/W-0            | R/W-0          |

| VDIR          | BGVST                          | IRVST                             | —               | HLVDL3                       | HLVDL2           | HLVDL1           | HLVDL0         |

| bit 7         |                                |                                   |                 |                              |                  |                  | bit C          |

| Legend:       |                                |                                   |                 |                              |                  |                  |                |

| R = Readabl   | e bit                          | W = Writable b                    | oit             | U = Unimplem                 | nented bit, read | l as '0'         |                |

| -n = Value at | POR                            | '1' = Bit is set                  |                 | '0' = Bit is clea            | ared             | x = Bit is unkn  | iown           |

|               |                                |                                   |                 |                              |                  |                  |                |

| bit 15        | HLVDEN: Hig                    | gh/Low-Voltage                    | Detect Powe     | r Enable bit                 |                  |                  |                |

|               | 1 = HLVD is                    |                                   |                 |                              |                  |                  |                |

|               | 0 = HLVD is                    |                                   |                 |                              |                  |                  |                |

| bit 14        | •                              | nted: Read as '0                  |                 |                              |                  |                  |                |

| bit 13        |                                | /D Stop in Idle N                 |                 |                              |                  |                  |                |

|               |                                | nues module op<br>es module opera |                 | device enters Id             | le mode          |                  |                |

| bit 12-8      |                                | ited: Read as '0                  |                 | ouc                          |                  |                  |                |

| bit 7         | -                              | e Change Direc                    |                 | t                            |                  |                  |                |

|               | -                              | -                                 |                 | exceeds trip poir            | nt (HLVDL<3:0>   | >)               |                |

|               |                                |                                   |                 | falls below trip po          | •                | ,                |                |

| bit 6         | BGVST: Ban                     | d Gap Voltage S                   | Stable Flag bit | t                            |                  |                  |                |

|               |                                | that the band g                   |                 |                              |                  |                  |                |

| 6.4 <i>F</i>  |                                | that the band g                   |                 |                              |                  |                  |                |

| bit 5         |                                | al Reference Vo                   |                 | riag bit<br>oltage is stable | and the high-v   | oltage detect lo | ogic generates |

|               | the inter                      | rupt flag at the s                | pecified volta  | ige range                    |                  |                  |                |

|               |                                |                                   |                 | oltage is unstab             |                  |                  |                |

|               | generate<br>enabled            | e the interrupt fi                | ag at the spe   | cified voltage ra            | nge, and the F   | ALVD Interrupt   | snould not be  |

| bit 4         |                                | ted: Read as '0                   | ,               |                              |                  |                  |                |

| bit 3-0       | -                              | High/Low-Volt                     |                 | n Limit bits                 |                  |                  |                |

|               | 1111 = Exter                   | nal analog inpu                   | -               | ut comes from th             | e HLVDIN pin)    |                  |                |

|               | 1110 <b>= Trip  </b>           | Point 1 <sup>(1)</sup>            | 、 I             |                              | . ,              |                  |                |

|               | 1101 = Trip I<br>1100 = Trip I | Point $2^{(1)}$                   |                 |                              |                  |                  |                |

|               | 1100 = 1mp i                   | onto' /                           |                 |                              |                  |                  |                |

|               | •                              |                                   |                 |                              |                  |                  |                |

|               | •                              |                                   |                 |                              |                  |                  |                |

|               | 0000 <b>= Trip I</b>           | Point 15                          |                 |                              |                  |                  |                |

#### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

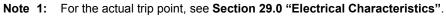

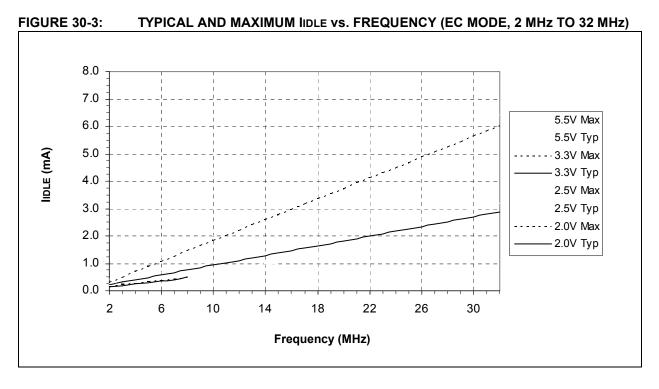

FIGURE 30-4: TYPICAL AND MAXIMUM lidle vs. FREQUENCY (EC MODE, 1.95 kHz TO 1 MHz)

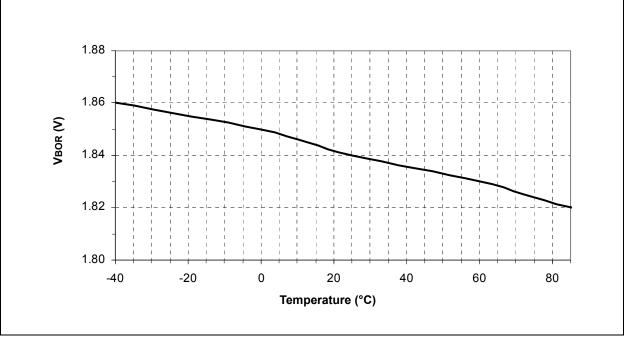

FIGURE 30-23: TYPICAL VBOR vs. TEMPERATURE (BOR TRIP POINT 3)

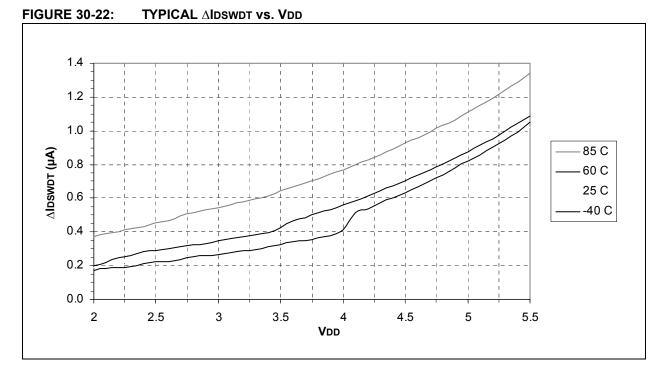

FIGURE 30-46: TYPICAL AlwDT vs. VDD

**∆IWDT (µA)**

Vdd

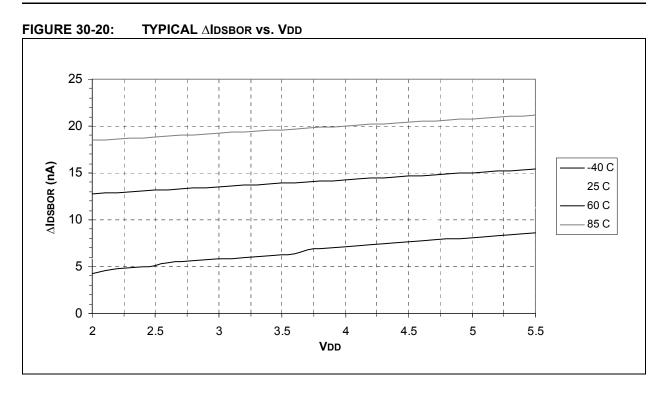

FIGURE 30-47: TYPICAL AIDSBOR vs. VDD

Aldsbor (nA)

Vdd

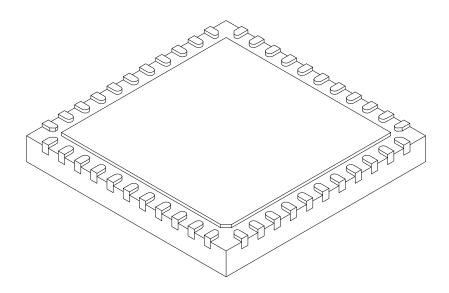

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | N    | <b>IILLIMETER</b> | S    |

|-------------------------|--------|------|-------------------|------|

| Dimension               | Limits | MIN  | NOM               | MAX  |

| Number of Pins          | N      |      | 44                |      |

| Pitch                   | е      |      | 0.65 BSC          |      |

| Overall Height          | A      | 0.80 | 0.90              | 1.00 |

| Standoff                | A1     | 0.00 | 0.02              | 0.05 |

| Terminal Thickness      | A3     |      | 0.20 REF          |      |

| Overall Width           | E      |      | 8.00 BSC          |      |

| Exposed Pad Width       | E2     | 6.25 | 6.45              | 6.60 |

| Overall Length          | D      |      | 8.00 BSC          |      |

| Exposed Pad Length      | D2     | 6.25 | 6.45              | 6.60 |

| Terminal Width          | b      | 0.20 | 0.30              | 0.35 |

| Terminal Length         | L      | 0.30 | 0.40              | 0.50 |

| Terminal-to-Exposed-Pad | K      | 0.20 | -                 | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

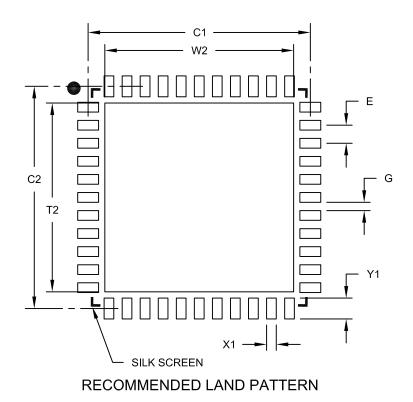

44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |      |          |      |  |  |

|----------------------------|-------|------|----------|------|--|--|

| Dimensior                  | MIN   | NOM  | MAX      |      |  |  |

| Contact Pitch              | E     |      | 0.65 BSC |      |  |  |

| Optional Center Pad Width  | W2    |      |          | 6.60 |  |  |

| Optional Center Pad Length | T2    |      |          | 6.60 |  |  |

| Contact Pad Spacing        | C1    |      | 8.00     |      |  |  |

| Contact Pad Spacing        | C2    |      | 8.00     |      |  |  |

| Contact Pad Width (X44)    | X1    |      |          | 0.35 |  |  |

| Contact Pad Length (X44)   | Y1    |      |          | 0.85 |  |  |

| Distance Between Pads      | G     | 0.25 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B