Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

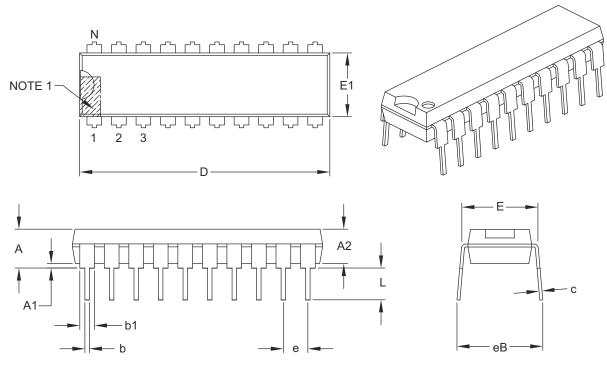

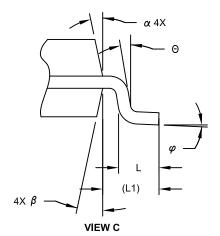

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka301-e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams**

|                          | 44-Pin TQFP/QFN <sup>(1,2,3)</sup>                                                                                    | Pir      |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|

|                          |                                                                                                                       | 1        |

|                          |                                                                                                                       |          |

|                          |                                                                                                                       | 2        |

|                          | RB RC 8 VDD 7 VDD 7 VC 8 RB RC 8 RC 8 RC 8 RC 8 RC 8 RC 8 RC                         | 3        |

|                          | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                                                | 4        |

|                          | 4 4 4 7 4 7 4 7 4 7 4 7 4 7 4 7 4 7 4 7                                                                               | 5<br>6   |

| RB                       |                                                                                                                       | 7        |

| RC                       | 7 3 31 RA3                                                                                                            | 8        |

| RC:<br>RC:               |                                                                                                                       | 9        |

| RA<br>RA6 or VCA<br>RB10 | 7 6 PIC24FXXKA304 28 VDD<br>7 PIC24FXXKA304 27 RC2                                                                    | 10       |

| RB1                      |                                                                                                                       | 11       |

| RB12<br>RB13             |                                                                                                                       | 12       |

| KD I.                    | 3 11 23 RB2                                                                                                           | 13       |

|                          | RA10<br>RA11<br>RA11<br>RB15<br>VSS<br>VSS<br>VDD<br>MCLR/RA5<br>RA1<br>RA1<br>RA1<br>RA1<br>RA1<br>RA1<br>RB1<br>RB1 | 14       |

|                          | WCI                                                                                                                   | 15       |

|                          |                                                                                                                       | 16       |

|                          |                                                                                                                       | 17       |

|                          |                                                                                                                       | 18       |

|                          |                                                                                                                       | 19       |

|                          |                                                                                                                       | 20       |

|                          |                                                                                                                       | 21       |

|                          |                                                                                                                       | 22       |

|                          |                                                                                                                       | 23       |

|                          |                                                                                                                       | 24       |

|                          |                                                                                                                       | 25       |

|                          |                                                                                                                       | 26       |

|                          |                                                                                                                       | 27       |

|                          |                                                                                                                       | 28       |

|                          |                                                                                                                       | 29       |

|                          |                                                                                                                       | 30       |

|                          |                                                                                                                       | 31       |

|                          |                                                                                                                       | 32<br>33 |

|                          |                                                                                                                       | 33       |

| Legend:                  | Pin numbers in <b>bold</b> indicate pin                                                                               | 34       |

|                          | function differences between<br>PIC24FV and PIC24F devices.                                                           | 35       |

| Note 1:                  | Exposed pad on underside of devices.                                                                                  | 30       |

| NOLE 1.                  | is connected to Vss.                                                                                                  | 38       |

| 2:                       | Alternative multiplexing for SDA1                                                                                     | 39       |

|                          | (ASDA1) and SCL1 (ASCL1) when                                                                                         | 40       |

|                          | the I2CSEL Configuration bit is set.                                                                                  | 41       |

| 3:                       | PIC24F32KA304 device pins have a                                                                                      | 42       |

|                          | maximum voltage of 3.6V and are not 5V tolerant.                                                                      | 43       |

|                          |                                                                                                                       | 44       |

| Pin | Pin F                                                         | eatures                                                       |

|-----|---------------------------------------------------------------|---------------------------------------------------------------|

| Pin | PIC24FVXXKA304                                                | PIC24FXXKA304                                                 |

| 1   | SDA1/T1CK/U1RTS/CTED4/CN21/<br>RB9                            | SDA1/T1CK/U1RTS/CTED4/CN21/<br>RB9                            |

| 2   | U1RX/CN18/RC6                                                 | U1RX/CN18/RC6                                                 |

| 3   | U1TX/CN17/RC7                                                 | U1TX/CN17/RC7                                                 |

| 4   | OC2/CN20/RC8                                                  | OC2/CN20/RC8                                                  |

| 5   | IC2/CTED7/CN19/RC9                                            | IC2/CTED7/CN19/RC9                                            |

| 6   | IC1/CTED3/CN9/RA7                                             | IC1/CTED3/CN9/RA7                                             |

| 7   | VCAP                                                          | C2OUT/OC1/CTED1/INT2/CN8/RAG                                  |

| 8   | PGED2/SDI1/CTED11/CN16/RB10                                   | PGED2/SDI1/CTED11/CN16/RB10                                   |

| 9   | PGEC2/SCK1/CTED9/CN15/RB11                                    | PGEC2/SCK1/CTED9/CN15/RB11                                    |

| 10  | AN12/HLVDIN/CTED2/INT2/CN14/<br>RB12                          | AN12/HLVDIN/CTED2/CN14/RB12                                   |

| 11  | AN11/SDO1/CTPLS/CN13/RB13                                     | AN11/SDO1/CTPLS/CN13/RB13                                     |

| 12  | OC3/CN35/RA10                                                 | OC3/CN35/RA10                                                 |

| 13  | IC3/CTED8/CN36/RA11                                           | IC3/CTED8/CN36/RA11                                           |

| 14  | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |

| 15  | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15              | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15              |

| 16  | Vss/AVss                                                      | Vss/AVss                                                      |

| 17  | Vdd/AVdd                                                      | Vdd/AVdd                                                      |

| 18  | MCLR/Vpp/RA5                                                  | MCLR/VPP/RA5                                                  |

| 19  | VREF+/CVREF+/AN0/C3INC/<br>CTED1/CN2/RA0                      | VREF+/CVREF+/AN0/C3INC/CN2/<br>RA0                            |

| 20  | CVREF-/VREF-/AN1/CN3/RA1                                      | CVREF-/VREF-/AN1/CN3/RA1                                      |

| 21  | PGED1/AN2/ULPWU/CTCMP/<br>C1IND/C2INB/C3IND/U2TX/CN4/RB0      | PGED1/AN2/ULPWU/CTCMP/C1IND<br>C2INB/C3IND/U2TX/CN4/RB0       |

| 22  | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1                 | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1                 |

| 23  | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2             | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2             |

| 24  | AN5/C1INA/C2INC/SCL2/CN7/<br>RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RB3                                  |

| 25  | AN6/CN32/RC0                                                  | AN6/CN32/RC0                                                  |

| 26  | AN7/CN31/RC1                                                  | AN7/CN31/RC1                                                  |

| 27  | AN8/CN10/RC2                                                  | AN8/CN10/RC2                                                  |

| 28  | VDD                                                           | VDD                                                           |

| 29  | Vss                                                           | Vss                                                           |

| 30  | OSCI/AN13/CLKI/CN30/RA2                                       | OSCI/AN13/CLKI/CN30/RA2                                       |

| 31  | OSCO/AN14/CLKO/CN29/RA3                                       | OSCO/AN14/CLKO/CN29/RA3                                       |

| 32  | OCFB/CN33/RA8                                                 | OCFB/CN33/RA8                                                 |

| 33  | SOSCI/AN15/U2RTS/CN1/RB4                                      | SOSCI/AN15/U2RTS/CN1/RB4                                      |

| 34  | SOSCO/SCLKI/U2CTS/CN0/RA4                                     | SOSCO/SCLKI/U2CTS/CN0/RA4                                     |

| 35  | SS2/CN34/RA9                                                  | SS2/CN34/RA9                                                  |

| 36  | SDI2/CN28/RC3                                                 | SDI2/CN28/RC3                                                 |

| 37  | SDO2/CN25/RC4                                                 | SDO2/CN25/RC4                                                 |

| 38  | SCK2/CN26/RC5                                                 | SCK2/CN26/RC5                                                 |

| 39  | Vss                                                           | Vss                                                           |

| 40  | VDD                                                           | VDD                                                           |

| 41  | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                          | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                          |

| 42  | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                          | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                          |

| 43  | C2OUT/OC1/INT0/CN23/RB7                                       | INT0/CN23/RB7                                                 |

| 44  | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                          | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                          |

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all the devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex.

## 1.2 Other Special Features

- Communications: The PIC24FV32KA304 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an I<sup>2</sup>C<sup>™</sup> module that supports both the Master and Slave modes of operation. It also comprises UARTs with built-in IrDA<sup>®</sup> encoders/decoders and an SPI module.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- **12-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV32KA304 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation.

## 1.3 Details on Individual Family Members

Devices in the PIC24FV32KA304 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are different from each other in four ways:

- Flash program memory (16 Kbytes for PIC24FV16KA devices, 32 Kbytes for PIC24FV32KA devices).

- Available I/O pins and ports (18 pins on two ports for 20-pin devices, 22 pins on two ports for 28-pin devices and 38 pins on three ports for 44/48-pin devices).

- 3. Alternate SCLx and SDAx pins are available only in 28-pin, 44-pin and 48-pin devices and not in 20-pin devices.

- 4. Members of the PIC24FV32KA301 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV32KA304), accommodate an operating VDD range of 2.0V to 5.5V, and have an on-board Voltage Regulator that powers the core. Peripherals operate at VDD. Standard devices, designated by "F" (such as PIC24F32KA304), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

All other features for devices in this family are identical; these are summarized in Table 1-1.

A list of the pin features available on the PIC24FV32KA304 family devices, sorted by function, is provided in Table 1-3.

Note: Table 1-1 provides the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams on pages 3, 4, 5, 6 and 7 of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

## TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  | Pin Number                        |               |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CN23     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs                  |

| CN24     |                                  | 15                                | 12            | 42                     | 46             | -                                | 15                                | 12            | 42                     | 46             | 1   | ST     |                                             |

| CN25     |                                  | _                                 | _             | 37                     | 40             | -                                |                                   |               | 37                     | 40             | 1   | ST     |                                             |

| CN26     |                                  | _                                 | _             | 38                     | 41             |                                  |                                   |               | 38                     | 41             | I   | ST     |                                             |

| CN27     |                                  | 14                                | 11            | 41                     | 45             |                                  | 14                                | 11            | 41                     | 45             | I   | ST     |                                             |

| CN28     |                                  | _                                 | _             | 36                     | 39             |                                  |                                   |               | 36                     | 39             | I   | ST     |                                             |

| CN29     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ST     |                                             |

| CN30     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ST     |                                             |

| CN31     |                                  | _                                 | _             | 26                     | 28             | —                                | _                                 | —             | 26                     | 28             | I   | ST     |                                             |

| CN32     |                                  | _                                 | —             | 25                     | 27             | —                                | —                                 | —             | 25                     | 27             | 1   | ST     |                                             |

| CN33     |                                  | _                                 | —             | 32                     | 35             | —                                | —                                 | —             | 32                     | 35             | 1   | ST     |                                             |

| CN34     |                                  | _                                 | —             | 35                     | 38             | —                                | —                                 | —             | 35                     | 38             | I   | ST     |                                             |

| CN35     |                                  | _                                 | _             | 12                     | 13             | —                                | _                                 | —             | 12                     | 13             | I   | ST     |                                             |

| CN36     |                                  | _                                 | _             | 13                     | 14             | —                                | _                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CVREF    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA    | Comparator Reference Positive Input Voltage |

| CVREF-   | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA    | Comparator Reference Negative Input Voltage |

| CTCMP    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input                       |

| CTED1    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 2                                 | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     |                                             |

| CTED3    | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I   | ST     |                                             |

| CTED4    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 1   | ST     |                                             |

| CTED5    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ST     |                                             |

| CTED6    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     |                                             |

| CTED7    | _                                | _                                 | _             | 5                      | 5              | _                                | —                                 | _             | 5                      | 5              | I   | ST     |                                             |

| CTED8    | _                                | _                                 | —             | 13                     | 14             | —                                | —                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CTED9    | _                                | 22                                | 19            | 9                      | 10             | —                                | 22                                | 19            | 9                      | 10             | I   | ST     |                                             |

| CTED10   | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I   | ST     | ]                                           |

| CTED11   | _                                | 21                                | 18            | 8                      | 9              | —                                | 21                                | 18            | 8                      | 9              | I   | ST     | ]                                           |

| CTED12   | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | ]                                           |

| CTED13   | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | 1   | ST     | 1                                           |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     |     | IPL3 <sup>(1)</sup> | PSV   | —   | _     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/0 | HSC = Hardware Settable/Clearable bit |                    |  |  |  |  |

|-------------------|---------------------------|---------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'    |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in data space                                                                                    |

|          | 0 = Program space is not visible in data space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

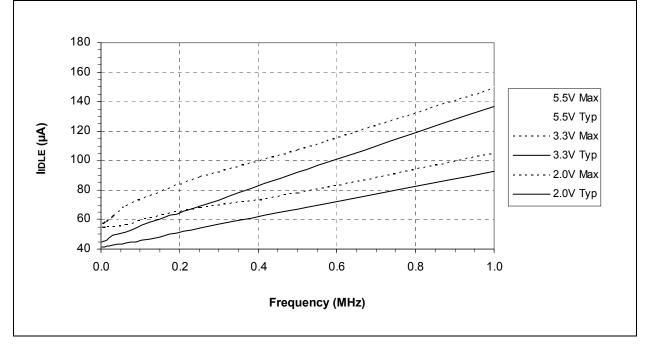

### 10.2.2 IDLE MODE

Idle mode has these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.4 DEEP SLEEP MODE

In PIC24FV32KA304 family devices, Deep Sleep mode is intended to provide the lowest levels of power consumption available without requiring the use of external switches to completely remove all power from the device. Entry into Deep Sleep mode is completely under software control. Exit from Deep Sleep mode can be triggered from any of the following events:

- · POR Event

- MCLR Event

- RTCC Alarm (if the RTCC is present)

- External Interrupt 0

- Deep Sleep Watchdog Timer (DSWDT) Time-out

- Ultra Low-Power Wake-up (ULPWU) Event

In Deep Sleep mode, it is possible to keep the device Real-Time Clock and Calendar (RTCC) running without the loss of clock cycles.

The device has a dedicated Deep Sleep Brown-out Reset (DSBOR) and a Deep Sleep Watchdog Timer Reset (DSWDT) for monitoring voltage and time-out events. The DSBOR and DSWDT are independent of the standard BOR and WDT used with other power-managed modes (Sleep, Idle and Doze).

### 10.2.4.1 Entering Deep Sleep Mode

Deep Sleep mode is entered by setting the DSEN bit in the DSCON register and then executing a Sleep command (PWRSAV #SLEEP\_MODE). An unlock sequence is required to set the DSEN bit. Once the DSEN bit has been set, there is no time limit before the SLEEP command can be executed. The DSEN bit is automatically cleared when exiting the Deep Sleep mode.

| Note: | To re-enter Deep Sleep after a Deep Sleep |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | wake-up, allow a delay of at least 3 TcY  |  |  |  |  |  |  |

|       | after clearing the RELEASE bit.           |  |  |  |  |  |  |

The sequence to enter Deep Sleep mode is:

- If the application requires the Deep Sleep WDT, enable it and configure its clock source. For more information on Deep Sleep WDT, see Section 10.2.4.5 "Deep Sleep WDT".

- 2. If the application requires Deep Sleep BOR, enable it by programming the DSLPBOR Configuration bit (FDS<6>).

- 3. If the application requires wake-up from Deep Sleep on RTCC alarm, enable and configure the RTCC module For more information on RTCC, see Section 19.0 "Real-Time Clock and Calendar (RTCC)".

- If needed, save any critical application context data by writing it to the DSGPR0 and DSGPR1 registers (optional).

- 5. Enable Deep Sleep mode by setting the DSEN bit (DSCON<15>).

Note: An unlock sequence is required to set the DSEN bit.

Any time the DSEN bit is set, all bits in the DSWAKE register will be automatically cleared.

To set the DSEN bit, the unlock sequence in Example 10-2 is required:

#### EXAMPLE 10-2: THE UNLOCK SEQUENCE

| //Disa | able Interrupts For 5 instructions |

|--------|------------------------------------|

| asm    | <pre>volatile("disi #5");</pre>    |

| //Issu | le Unlock Sequence                 |

| asm    | volatile                           |

| mov    | #0x55, W0;                         |

| mov    | W0, NVMKEY;                        |

| mov    | #0xAA, W1;                         |

| mov    | W1, NVMKEY;                        |

| bset   | DSCON, #DSEN                       |

|        |                                    |

Enter Deep Sleep mode by issuing a PWRSAV #0 instruction.

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O Ports, refer to the "PIC24F Family Reference Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24FV32KA304 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

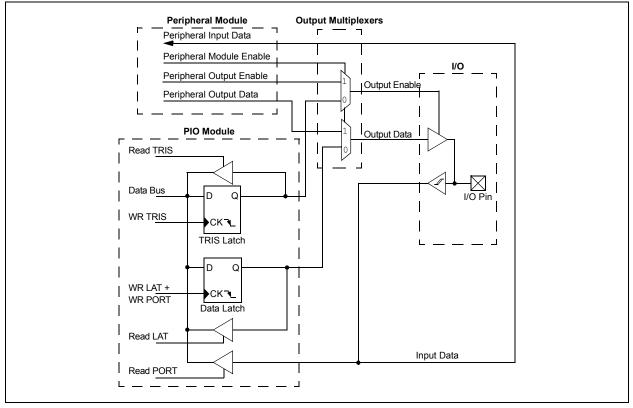

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LAT), read the latch. Writes to the latch, write the latch. Reads from the port (PORT), read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

## 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 34. "Input Capture with Dedicated Timer" (DS39722).

All devices in the PIC24FV32KA304 family feature three independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events, and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 20 user-selectable Sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

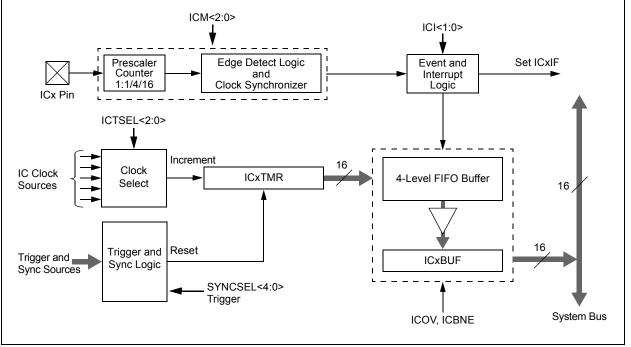

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

## 14.1 General Operating Modes

#### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the input capture module operates in a Free-Running mode. The internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected Sync source, the internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSELx bits to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the Sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

## EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

## TABLE 16-1: SAMPLE SCKx FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               | Secondary Prescaler Settings |         |      |      |      |      |  |

|----------------------------|------------------------------|---------|------|------|------|------|--|

|                            | 1:1                          | 2:1     | 4:1  | 6:1  | 8:1  |      |  |

| Primary Prescaler Settings | 1:1                          | Invalid | 8000 | 4000 | 2667 | 2000 |  |

|                            | 4:1                          | 4000    | 2000 | 1000 | 667  | 500  |  |

|                            | 16:1                         | 1000    | 500  | 250  | 167  | 125  |  |

|                            | 64:1                         | 250     | 125  | 63   | 42   | 31   |  |

| Fcy <b>= 5 MHz</b>         |                              |         |      |      |      |      |  |

| Primary Prescaler Settings | 1:1                          | 5000    | 2500 | 1250 | 833  | 625  |  |

|                            | 4:1                          | 1250    | 625  | 313  | 208  | 156  |  |

|                            | 16:1                         | 313     | 156  | 78   | 52   | 39   |  |

|                            | 64:1                         | 78      | 39   | 20   | 13   | 10   |  |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: SCKx frequencies are indicated in kHz.

#### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   |     | —   | —   | —   | AMSK9 | AMSK8 |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enables masking for bit x of an incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

#### REGISTER 17-4: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| U-0         | U-0 | R/W-0     | R/W-0     | U-0 | U-0 | U-0 | U-0 |  |

|-------------|-----|-----------|-----------|-----|-----|-----|-----|--|

| _           | —   | SMBUSDEL2 | SMBUSDEL1 |     | —   | —   | —   |  |

| bit 7 bit 0 |     |           |           |     |     |     |     |  |

| Legend:           |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

| bit 5   | SMBUSDEL2: SMBus SDA2 Input Delay Select bit                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The I2C2 module is configured for a longer SMBus input delay (nominal 300 ns delay)</li> <li>0 = The I2C2 module is configured for a legacy input delay (nominal 150 ns delay)</li> </ul> |

| bit 4   | SMBUSDEL1: SMBus SDA1 Input Delay Select bit                                                                                                                                                           |

|         | <ul> <li>1 = The I2C1 module is configured for a longer SMBus input delay (nominal 300 ns delay)</li> <li>0 = The I2C1 module is configured for a legacy input delay (nominal 150 ns delay)</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                             |

#### 19.2.6 ALRMVAL REGISTER MAPPINGS

### **REGISTER 19-8:** ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

|              |                            |                    | -                |                      |                                    |                    |         |  |  |  |

|--------------|----------------------------|--------------------|------------------|----------------------|------------------------------------|--------------------|---------|--|--|--|

| U-0          | U-0                        | U-0                | R/W-x            | R/W-x                | R/W-x                              | R/W-x              | R/W-x   |  |  |  |

| _            | —                          | —                  | MTHTEN0          | MTHONE3              | MTHONE2                            | MTHONE1            | MTHONE0 |  |  |  |

| bit 15       |                            |                    | •                |                      |                                    |                    | bit 8   |  |  |  |

| 11.0         |                            | D () ()            | DAA              | D () ()              | D////                              |                    | DAV     |  |  |  |

| U-0          | U-0                        | R/W-x              | R/W-x            | R/W-x                | R/W-x                              | R/W-x              | R/W-x   |  |  |  |

|              |                            | DAYTEN1            | DAYTEN0          | DAYONE3              | DAYONE2                            | DAYONE1            | DAYONE0 |  |  |  |

| bit 7        |                            |                    |                  |                      |                                    |                    | bit 0   |  |  |  |

|              |                            |                    |                  |                      |                                    |                    |         |  |  |  |

| Legend:      |                            |                    |                  |                      |                                    |                    |         |  |  |  |

| R = Readab   | le bit                     | W = Writable       | W = Writable bit |                      | U = Unimplemented bit, read as '0' |                    |         |  |  |  |

| -n = Value a | It POR                     | '1' = Bit is set   |                  | '0' = Bit is cleared |                                    | x = Bit is unknown |         |  |  |  |

| h# 45 40     |                            |                    | 9                |                      |                                    |                    |         |  |  |  |

| bit 15-13    | -                          | ted: Read as '0'   |                  |                      |                                    |                    |         |  |  |  |

| bit 12       | MTHTEN0: B                 | inary Coded Do     | ecimal Value o   | f Month's Tens       | Digit bit                          |                    |         |  |  |  |

|              | Contains a va              | lue of '0' or '1'. |                  |                      |                                    |                    |         |  |  |  |

| bit 11-8     | MTHONE<3:                  | 0>: Binary Cod     | ed Decimal Va    | lue of Month's       | Ones Digit bits                    |                    |         |  |  |  |

|              | Contains a va              | lue from 0 to 9    |                  |                      | -                                  |                    |         |  |  |  |

| bit 7-6      | Unimplemented: Read as '0' |                    |                  |                      |                                    |                    |         |  |  |  |

| h:+ C 4      |                            |                    |                  |                      |                                    |                    |         |  |  |  |

| bit 5-4 | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits |

|---------|------------------------------------------------------------------|

|         | Contains a value from 0 to 3.                                    |

| bit 3-0 | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits |

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 19-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0    | U-0    | U-0    | R/W-x  | R/W-x  | R/W-x  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | —      | —      | —      | WDAY2  | WDAY1  | WDAY0  |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|        |     |        |        |        |        |        |        |

| —      |     | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 15-11<br>bit 10-8 | <b>Unimplemented:</b> Read as '0'<br><b>WDAY&lt;2:0&gt;:</b> Binary Coded Decimal Value of Weekday Digit bits<br>Contains a value from 0 to 6. |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6               | Unimplemented: Read as '0'                                                                                                                     |

| bit 5-4               | <b>HRTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2.                                    |

| bit 3-0               | <b>HRONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

| U-0          | R/W-x         | R/W-x            | R/W-x          | R/W-x            | R/W-x                | R/W-x    | R/W-x              |  |

|--------------|---------------|------------------|----------------|------------------|----------------------|----------|--------------------|--|

|              | MINTEN2       | MINTEN1          | MINTEN0        | MINONE3          | MINONE2              | MINONE1  | MINONE0            |  |

| bit 15       |               |                  |                |                  |                      |          | bit 8              |  |

|              |               |                  |                |                  |                      |          |                    |  |

| U-0          | R/W-x         | R/W-x            | R/W-x          | R/W-x            | R/W-x                | R/W-x    | R/W-x              |  |

| —            | SECTEN2       | SECTEN1          | SECTEN0        | SECONE3          | SECONE2              | SECONE1  | SECONE0            |  |

| bit 7        |               |                  |                |                  |                      |          | bit 0              |  |

|              |               |                  |                |                  |                      |          |                    |  |

| Legend:      |               |                  |                |                  |                      |          |                    |  |

| R = Readab   | le bit        | W = Writable bit |                | U = Unimplem     | nented bit, read     | l as '0' |                    |  |

| -n = Value a | t POR         | '1' = Bit is set | = Bit is set   |                  | '0' = Bit is cleared |          | x = Bit is unknown |  |

|              |               |                  |                |                  |                      |          |                    |  |

| bit 15       | Unimplement   | ted: Read as '0  | ,              |                  |                      |          |                    |  |

| bit 14-12    | MINTEN<2:0    | >: Binary Code   | d Decimal Valu | ue of Minute's T | ens Digit bits       |          |                    |  |

|              | Contains a va | lue from 0 to 5  |                |                  |                      |          |                    |  |

| bit 11-8     | MINONE<3:0    | >: Binary Code   | d Decimal Val  | ue of Minute's 0 | Ones Digit bits      |          |                    |  |

|              | Contains a va | lue from 0 to 9  |                |                  |                      |          |                    |  |

| bit 7        | Unimplemen    | ted: Read as '   | o'             |                  |                      |          |                    |  |

| bit 6-4      | SECTEN<2:0    | >: Binary Code   | ed Decimal Val | ue of Second's   | Tens Digit bits      |          |                    |  |

|              | Contains a va | lue from 0 to 5  |                |                  |                      |          |                    |  |

| bit 3-0      | SECONE<3:0    | >: Binary Code   | ed Decimal Va  | lue of Second's  | Ones Digit bits      | 6        |                    |  |

|              | Contains a va | lue from 0 to 9  |                |                  |                      |          |                    |  |

|              |               |                  |                |                  |                      |          |                    |  |

### REGISTER 19-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

NOTES:

| U-0                       | U-0                                                                                                                                                                                   | U-0                                                                                                                                                                                         | U-0                                                                                                                          | U-0                                | U-0    | U-0                | U-0    |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------|--------------------|--------|--|

| _                         | _                                                                                                                                                                                     |                                                                                                                                                                                             |                                                                                                                              | _                                  | _      | _                  | _      |  |

| bit 23                    |                                                                                                                                                                                       |                                                                                                                                                                                             | •                                                                                                                            |                                    |        | •                  | bit 16 |  |

|                           |                                                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                                              |                                    |        |                    |        |  |

| R                         | R                                                                                                                                                                                     | R                                                                                                                                                                                           | R                                                                                                                            | R                                  | R      | R                  | R      |  |

| FAMID7                    | FAMID6                                                                                                                                                                                | FAMID5                                                                                                                                                                                      | FAMID4                                                                                                                       | FAMID3                             | FAMID2 | FAMID1             | FAMID0 |  |

| bit 15                    |                                                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                                              |                                    |        |                    | bit 8  |  |

| R                         | R                                                                                                                                                                                     | R                                                                                                                                                                                           | R                                                                                                                            | R                                  | R      | R                  | R      |  |

| DEV7                      | DEV6                                                                                                                                                                                  | DEV5                                                                                                                                                                                        | DEV4                                                                                                                         | DEV3                               | DEV2   | DEV1               | DEV0   |  |

| bit 7                     | DLVU                                                                                                                                                                                  | DEVS                                                                                                                                                                                        | DEV4                                                                                                                         | DLVJ                               | DLVZ   | DEVI               | bit 0  |  |

|                           |                                                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                                              |                                    |        |                    | bit 0  |  |

| Legend:                   |                                                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                                              |                                    |        |                    |        |  |

| R = Readable bit          |                                                                                                                                                                                       | W = Writable bit                                                                                                                                                                            |                                                                                                                              | U = Unimplemented bit, read as '0' |        |                    |        |  |

| -n = Value at POR         |                                                                                                                                                                                       | '1' = Bit is set                                                                                                                                                                            |                                                                                                                              | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |

| -n = Value a              | t POR                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                            |                                                                                                                              | '0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| -n = Value a              | t POR                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                            |                                                                                                                              | '0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| -n = Value a<br>bit 23-16 |                                                                                                                                                                                       | <ul><li>'1' = Bit is set</li><li>ted: Read as '0</li></ul>                                                                                                                                  |                                                                                                                              | '0' = Bit is clea                  | ared   | x = Bit is unkr    | lown   |  |

|                           | Unimplemen                                                                                                                                                                            |                                                                                                                                                                                             | 0'                                                                                                                           | '0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16                 | Unimplemen<br>FAMID<7:0>:                                                                                                                                                             | ted: Read as '                                                                                                                                                                              | 0'<br>V Identifier bits                                                                                                      | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16                 | Unimplemen<br>FAMID<7:0>:<br>01000101 =                                                                                                                                               | <b>ted:</b> Read as '<br>Device Family                                                                                                                                                      | 0'<br>/ Identifier bits<br>304 family                                                                                        | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16<br>bit 15-8     | Unimplemen<br>FAMID<7:0>:<br>01000101 =<br>DEV<7:0>: In<br>00010111 =                                                                                                                 | ted: Read as '<br>Device Family<br>PIC24FV32KA<br>dividual Device<br>PIC24FV32KA                                                                                                            | 0'<br>Identifier bits<br>304 family<br>e Identifier bits<br>304                                                              | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16<br>bit 15-8     | Unimplemen<br>FAMID<7:0>:<br>01000101 =<br>DEV<7:0>: In<br>00010111 =<br>00000111 =                                                                                                   | ted: Read as '<br>Device Family<br>PIC24FV32KA<br>dividual Device<br>PIC24FV32KA<br>PIC24FV16KA                                                                                             | 0'<br>1 Identifier bits<br>304 family<br>e Identifier bits<br>304<br>304                                                     | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16<br>bit 15-8     | Unimplemen<br>FAMID<7:0>:<br>01000101 =<br>DEV<7:0>: In<br>00010111 =<br>00000111 =<br>00010011 =                                                                                     | ted: Read as '<br>Device Family<br>PIC24FV32KA<br>dividual Device<br>PIC24FV32KA<br>PIC24FV16KA<br>PIC24FV32KA                                                                              | 0'<br>Identifier bits<br>304 family<br>e Identifier bits<br>304<br>304<br>302                                                | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16<br>bit 15-8     | Unimplemen<br>FAMID<7:0>:<br>01000101 =<br>DEV<7:0>: In<br>00010111 =<br>00000111 =<br>00010011 =<br>00010011 =                                                                       | ted: Read as '<br>Device Family<br>PIC24FV32KA<br>dividual Device<br>PIC24FV32KA<br>PIC24FV16KA<br>PIC24FV32KA<br>PIC24FV32KA                                                               | 0'<br>Identifier bits<br>304 family<br>e Identifier bits<br>304<br>304<br>302<br>302                                         | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16<br>bit 15-8     | Unimplemen<br>FAMID<7:0>:<br>01000101 =<br>DEV<7:0>: In<br>00010111 =<br>00010011 =<br>00010011 =<br>00010011 =                                                                       | ted: Read as '<br>Device Family<br>PIC24FV32KA<br>dividual Device<br>PIC24FV32KA<br>PIC24FV16KA<br>PIC24FV32KA<br>PIC24FV16KA<br>PIC24FV32KA                                                | 0'<br>Identifier bits<br>304 family<br>e Identifier bits<br>304<br>304<br>302<br>302<br>302                                  | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |

| bit 23-16<br>bit 15-8     | Unimplemen<br>FAMID<7:0>:<br>01000101 =<br>DEV<7:0>: In<br>00010111 =<br>00000111 =<br>00010011 =<br>00010011 =<br>00011001 =                                                         | ted: Read as '<br>Device Family<br>PIC24FV32KA<br>dividual Device<br>PIC24FV32KA<br>PIC24FV16KA<br>PIC24FV32KA<br>PIC24FV16KA<br>PIC24FV32KA<br>PIC24FV16KA                                 | 0'<br>Identifier bits<br>304 family<br>e Identifier bits<br>304<br>304<br>302<br>302<br>301<br>301                           | ʻ0' = Bit is clea                  | ared   | x = Bit is unkr    | iown   |  |