#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 16KB (5.5K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 512 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka301-i-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|       | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearable bit        |                  |

|----------------------|------------------------|------------------------------------|------------------|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit                   | W = Writable bit |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, read as '0' |                  |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once the operation is complete.</li> <li>0 = Program or erase operation is complete and inactive</li> </ul>               |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                                                     |

|          | <ul><li>1 = Enables Flash program/erase operations</li><li>0 = Inhibits Flash program/erase operations</li></ul>                                                                                                                                           |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                                                       |

|          | <ul> <li>1 = An improper program or erase sequence attempt, or termination, has occurred (bit is set automatically on any set attempt of the WR bit)</li> <li>0 = The program or erase operation completed normally</li> </ul>                             |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                                                            |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                 |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                                                            |

|          | <ul> <li>1 = Performs the erase operation specified by NVMOP&lt;5:0&gt; on the next WR command</li> <li>0 = Performs the program operation specified by NVMOP&lt;5:0&gt; on the next WR command</li> </ul>                                                 |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                                                         |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                                                  |

|          | 1010xx = Erases entire boot block (including code-protected boot block) <sup>(2)</sup><br>1001xx = Erases entire memory (including boot block, configuration block, general block) <sup>(2)</sup><br>011010 = Erases 4 rows of Flash memory <sup>(3)</sup> |

|          | 011001 = Erases 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                                                      |

|          | 011000 = Erases 1 row of Flash memory <sup>(3)</sup>                                                                                                                                                                                                       |

|          | 0101xx = Erases entire configuration block (except code protection bits)                                                                                                                                                                                   |

|          | 0100xx = Erases entire data EEPROM <sup>(4)</sup><br>0011xx = Erases entire general memory block programming operations                                                                                                                                    |

|          | 0011xx = Erases entire general memory block programming operations<br>$0001xx = \text{Writes 1 row of Flash memory (when ERASE bit is '0')^{(3)}$                                                                                                          |

| Note 1:  | All other combinations of NVMOP<5:0> are no operation.                                                                                                                                                                                                     |

| 2:       | These values are available in ICSP <sup>™</sup> mode only. Refer to the device programming specification.                                                                                                                                                  |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM.

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

#### TABLE 8-1:TRAP VECTOR DETAILS

#### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

| la farmar f O anna a           |               |             | AIVT    | Interrupt Bit Locations |          |              |  |

|--------------------------------|---------------|-------------|---------|-------------------------|----------|--------------|--|

| Interrupt Source               | Vector Number | IVT Address | Address | Flag                    | Enable   | Priority     |  |

| ADC1 Conversion Done           | 13            | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |

| Comparator Event               | 18            | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |

| CRC Generator                  | 67            | 00009Ah     | 00019Ah | IFS4<3>                 | IEC4<3>  | IPC16<14:12> |  |

| СТМИ                           | 77            | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |

| External Interrupt 0           | 0             | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |

| External Interrupt 1           | 20            | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |

| External Interrupt 2           | 29            | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |

| I2C1 Master Event              | 17            | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |

| I2C1 Slave Event               | 16            | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |

| I2C2 Master Event              | 50            | 000078h     | 000178h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |

| I2C2 Slave Event               | 49            | 000076h     | 000176h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |

| Input Capture 1                | 1             | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |

| Input Capture 2                | 5             | 00001Eh     | 00011Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |

| Input Capture 3                | 37            | 00005Eh     | 00015Eh | IFS2<5>                 | IEC2<5>  | IPC9<6:4>    |  |

| Input Change Notification      | 19            | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |

| HLVD (High/Low-Voltage Detect) | 72            | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC17<2:0>   |  |

| NVM – NVM Write Complete       | 15            | 000032h     | 000132h | IFS0<15>                | IEC0<15> | IPC3<14:12>  |  |

| Output Compare 1               | 2             | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>   |  |

| Output Compare 2               | 6             | 000020h     | 000120h | IFS0<6>                 | IEC0<6>  | IPC1<10:8>   |  |

| Output Compare 3               | 25            | 000046h     | 000146h | IFS1<9>                 | IEC1<9>  | IPC6<6:4>    |  |

| Real-Time Clock/Calendar       | 62            | 000090h     | 000190h | IFS3<14>                | IEC3<14> | IPC15<10:8>  |  |

| SPI1 Error                     | 9             | 000026h     | 000126h | IFS0<9>                 | IEC0<9>  | IPC2<6:4>    |  |

| SPI1 Event                     | 10            | 000028h     | 000128h | IFS0<10>                | IEC0<10> | IPC2<10:8>   |  |

| SPI2 Error                     | 32            | 000054h     | 000154h | IFS2<0>                 | IEC2<2>  | IPC8<2:0>    |  |

| SPI2 Event                     | 33            | 000056h     | 000156h | IFS2<1>                 | IEC2<1>  | IPC8<6:4>    |  |

| Timer1                         | 3             | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |  |

| Timer2                         | 7             | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |  |

| Timer3                         | 8             | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |  |

| Timer4                         | 27            | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |  |

| Timer5                         | 28            | 00004Ch     | 00015Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |  |

| UART1 Error                    | 65            | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |  |

| UART1 Receiver                 | 11            | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |  |

| UART1 Transmitter              | 12            | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |  |

| UART2 Error                    | 66            | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |  |

| UART2 Receiver                 | 30            | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |  |

| UART2 Transmitter              | 31            | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |  |

| Ultra Low-Power Wake-up        | 80            | 0000B4h     | 0001B4h | IFS5<0>                 | IEC5<0>  | IPC20<2:0>   |  |

| U-0              | U-0                                                                 | U-0                                                          | U-0                                | U-0                                | R/W-1    | R/W-0              | R/W-0    |  |  |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|------------------------------------|----------|--------------------|----------|--|--|

| —                |                                                                     |                                                              | —                                  |                                    | MI2C2IP2 | MI2C2IP1           | MI2C2IP0 |  |  |

| bit 15           |                                                                     |                                                              |                                    |                                    |          |                    | bit 8    |  |  |

| U-0              | R/W-1                                                               | R/W-0                                                        | R/W-0                              | U-0                                | U-0      | U-0                | U-0      |  |  |

|                  | SI2C2IP2                                                            | SI2C2IP1                                                     | SI2C2IP0                           |                                    |          |                    | <u> </u> |  |  |

| bit 7            |                                                                     |                                                              |                                    |                                    |          |                    | bit 0    |  |  |

|                  |                                                                     |                                                              |                                    |                                    |          |                    |          |  |  |

| Legend:          |                                                                     |                                                              |                                    |                                    |          |                    |          |  |  |

| R = Readable     |                                                                     | W = Writable                                                 | bit                                | U = Unimplemented bit, read as '0' |          |                    |          |  |  |

| -n = Value at I  | POR                                                                 | '1' = Bit is set                                             |                                    | '0' = Bit is cleared               |          | x = Bit is unknown |          |  |  |

| bit 15-11        | Unimplemen                                                          | ted: Read as '                                               | )'                                 |                                    |          |                    |          |  |  |

| bit 10-8         | MI2C2IP <2:0                                                        | >: Master I2C2                                               | Event Interru                      | pt Priority bits                   |          |                    |          |  |  |

|                  | •<br>•<br>001 = Interrup                                            | ot is Priority 7 (l<br>ot is Priority 1<br>ot source is disa |                                    | r interrupt)                       |          |                    |          |  |  |

|                  | 000 = Interru                                                       |                                                              | Unimplemented: Read as '0'         |                                    |          |                    |          |  |  |

| bit 7            | •                                                                   | ted: Read as '                                               | )'                                 |                                    |          |                    |          |  |  |

| bit 7<br>bit 6-4 | Unimplemen                                                          | ted: Read as 'd<br>>: Slave I2C2 E                           |                                    | Priority bits                      |          |                    |          |  |  |

|                  | Unimplement<br>SI2C2IP<2:0><br>111 = Interrup<br><br>001 = Interrup | •: Slave I2C2 E<br>ot is Priority 7 (I                       | vent Interrupt<br>nighest priority |                                    |          |                    |          |  |  |

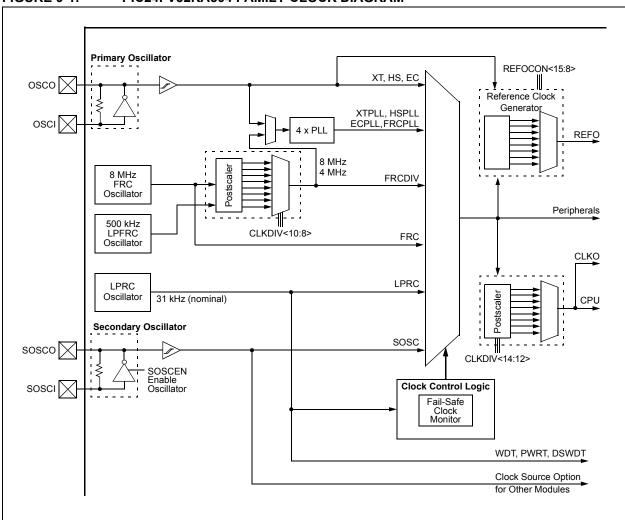

### 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Oscillator Configuration, refer to the "PIC24F Family Reference Manual", Section 38. "Oscillator with 500 kHz Low-Power FRC" (DS39726).

The oscillator system for the PIC24FV32KA304 family of devices has the following features:

- A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for EC mode. When using an external clock source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24FV32KA304 FAMILY CLOCK DIAGRAM

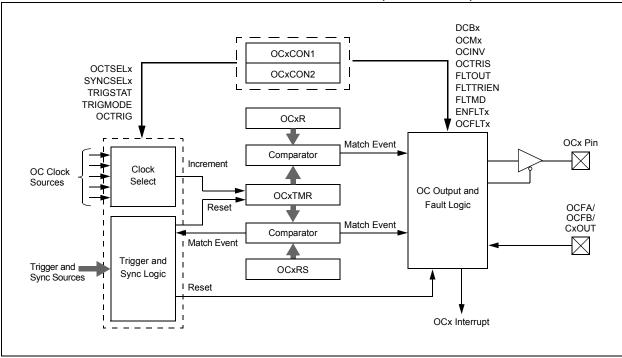

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

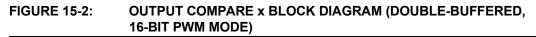

#### 15.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are double-buffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for edge-aligned PWM operation:

- 1. Calculate the desired ON time and load it into the OCxR register.

- 2. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the synchronization source by writing 0x1F to SYNCSEL<4:0> (OCxCON2<4:0>) and '0' to OCTRIG (OCxCON2<7>).

- 4. Select a clock source by writing the OCTSEL2<2:0> (OCxCON<12:10>) bits.

- 5. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- 6. Select the desired PWM mode in the OCM<2:0> (OCxCON1<2:0>) bits.

- If a timer is selected as a clock source, set the TMRy prescale value and enable the time base by setting the TON (TxCON<15>) bit.

|                                    | CSS30 | CSS29          | CSS28                | CSS27                              | CSS26              | —     |       |

|------------------------------------|-------|----------------|----------------------|------------------------------------|--------------------|-------|-------|

| bit 15                             |       |                |                      |                                    |                    |       | bit 8 |

| U-0                                | U-0   | U-0            | U-0                  | U-0                                | U-0                | R/W-0 | R/W-0 |

| —                                  | —     | —              | _                    | —                                  | —                  | CSS17 | CSS16 |

| bit 7                              |       |                |                      |                                    |                    |       | bit   |

| Legend:                            |       |                |                      |                                    |                    |       |       |

| R = Readable                       | e bit | W = Writable I | oit                  | U = Unimplemented bit, read as '0' |                    |       |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared |                                    | x = Bit is unknown |       |       |

- bit 14-10CSS<30:26>: A/D Input Scan Selection bits<br/>1 = Includes corresponding channel for input scan<br/>0 = Skips channel for input scanbit 9-2Unimplemented: Read as '0'bit 1-0CSS<17:16>: A/D Input Scan Selection bits

- 1 = Includes corresponding channel for input scan

- 0 = Skips channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

#### REGISTER 22-9: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0 | R/W-0          | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                                            |

|-------|----------------|----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSS14 | CSS13          | CSS12                      | CSS11                                  | CSS10                                                                                                     | CSS9                                                                                                                                  | CSS8                                                                                                                                                             |

|       |                |                            |                                        | •                                                                                                         |                                                                                                                                       | bit 8                                                                                                                                                            |

|       |                |                            |                                        |                                                                                                           |                                                                                                                                       |                                                                                                                                                                  |

| R/W-0 | R/W-0          | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                                            |

| CSS6  | CSS5           | CSS4                       | CSS3                                   | CSS2                                                                                                      | CSS1                                                                                                                                  | CSS0                                                                                                                                                             |

|       |                |                            |                                        |                                                                                                           |                                                                                                                                       | bit (                                                                                                                                                            |

|       | CSS14<br>R/W-0 | CSS14 CSS13<br>R/W-0 R/W-0 | CSS14 CSS13 CSS12<br>R/W-0 R/W-0 R/W-0 | CSS14         CSS13         CSS12         CSS11           R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10         CSS9           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 C

CSS<15:0>: A/D Input Scan Selection bits

- 1 = Includes corresponding ANx input for scan

- 0 = Skips channel for input scan

**Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

NOTES:

| U-0          | U-0   | U-0           | U-0   | U-0          | U-0             | R/C-1    | R/C-1 |

|--------------|-------|---------------|-------|--------------|-----------------|----------|-------|

| —            |       | —             | _     | —            |                 | GSS0     | GWRP  |

| bit 7        | •     |               | •     |              |                 |          | bit 0 |

|              |       |               |       |              |                 |          |       |

| Legend:      |       |               |       |              |                 |          |       |

| R = Readable | hit   | C = Clearable | hit   | U = Unimplem | onted hit read  | 1 26 '0' |       |

| R = Readable | , DIL |               | , DIL |              | chica bit, icac |          |       |

| bit 7-2 | Unimplemented: Read as '0'                                                                          |

|---------|-----------------------------------------------------------------------------------------------------|

| bit 1   | GSS0: General Segment Code Flash Code Protection bit                                                |

|         | <ul><li>1 = No protection</li><li>0 = Standard security is enabled</li></ul>                        |

| bit 0   | GWRP: General Segment Code Flash Write Protection bit                                               |

|         | <ul><li>1 = General segment may be written</li><li>0 = General segment is write-protected</li></ul> |

**REGISTER 26-2: FGS: GENERAL SEGMENT CONFIGURATION REGISTER**

#### **REGISTER 26-3:** FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| R/P-1 | R/P-1   | R/P-1   | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  |

|-------|---------|---------|-----|-----|--------|--------|--------|

| IESO  | LPRCSEL | SOSCSRC | —   | —   | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7 |         |         |     |     |        |        | bit 0  |

| Legend:    |            |                                                                    |                          |                    |

|------------|------------|--------------------------------------------------------------------|--------------------------|--------------------|

| R = Reada  | ble bit    | P = Programmable bit                                               | U = Unimplemented bit    | , read as '0'      |

| -n = Value | at POR     | '1' = Bit is set                                                   | '0' = Bit is cleared     | x = Bit is unknown |

|            |            |                                                                    |                          |                    |

| bit 7      | IESO: Inte | ernal External Switchover bit                                      |                          |                    |

|            |            | al External Switchover mode is<br>al External Switchover mode is   | · · ·                    | ,                  |

| bit 6      | LPRCSEL    | .: Internal LPRC Oscillator Pov                                    | wer Select bit           |                    |

|            | 0          | Power/High-Accuracy mode<br>Power/Low-Accuracy mode                |                          |                    |

| bit 5      | SOSCSR     | C: Secondary Oscillator Clock                                      | Source Configuration bit |                    |

|            |            | analog crystal function is ava<br>crystal is disabled; digital SCI |                          | 1                  |

| bit 4-3    | Unimplen   | nented: Read as '0'                                                |                          |                    |

| bit 2-0    | FNOSC<2    | 2:0>: Oscillator Selection bits                                    |                          |                    |

|            |            | at RC Oscillator (FRC)<br>at RC Oscillator with Divide-by-         | N with PLL module (FRCD  | V+PLL)             |

|            |            |                                                                    |                          | •                  |

- 010 = Primary Oscillator (XT, HS, EC)

- 011 = Primary Oscillator with PLL module (HS+PLL, EC+PLL)

- 100 = Secondary Oscillator (SOSC)

- 101 = Low-Power RC Oscillator (LPRC)

- 110 = 500 kHz Low-Power FRC Oscillator with Divide-by-N (LPFRCDIV)

- 111 = 8 MHz FRC Oscillator with Divide-by-N (FRCDIV)

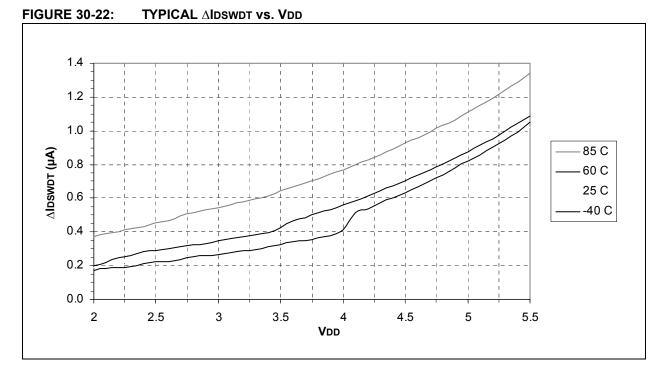

#### 26.4 Deep Sleep Watchdog Timer (DSWDT)

In PIC24FV32KA304 family devices, in addition to the WDT module, a DSWDT module is present which runs while the device is in Deep Sleep, if enabled. It is driven by either the SOSC or LPRC oscillator. The clock source is selected by the Configuration bit, DSWDTOSC (FDS<4>).

The DSWDT can be configured to generate a time-out, at 2.1 ms to 25.7 days, by selecting the respective postscaler. The postscaler can be selected by the Configuration bits, DSWDTPS<3:0> (FDS<3:0>). When the DSWDT is enabled, the clock source is also enabled.

DSWDT is one of the sources that can wake-up the device from Deep Sleep mode.

### 26.5 Program Verification and Code Protection

For all devices in the PIC24FV32KA304 family, code protection for the boot segment is controlled by the Configuration bit, BSS0, and the general segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the boot segment and bit, GWRP, for the general segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

### 26.6 In-Circuit Serial Programming

PIC24FV32KA304 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 26.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

#### 27.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 27.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 27.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 27.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 27.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

#### 27.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 27.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 27.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 27.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

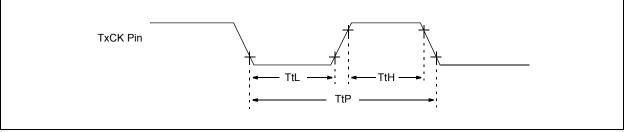

#### FIGURE 29-8: TIMER1/2/3/4/5 EXTERNAL CLOCK INPUT TIMING

#### TABLE 29-27: TIMER1/2/3/4/5 EXTERNAL CLOCK INPUT REQUIREMENTS

| Param.<br>No. | Symbol | Chara                | Min               | Max                                              | Units | Conditions |                    |

|---------------|--------|----------------------|-------------------|--------------------------------------------------|-------|------------|--------------------|

|               | TtH    | TxCK High Pulse      | Sync w/Prescaler  | Tcy + 20                                         | _     | ns         | Must also meet     |

|               |        | Time                 | Async w/Prescaler | 10                                               | _     | ns         | Parameter Ttp      |

|               |        |                      | Async Counter     | 20                                               | _     | ns         |                    |

|               | TtL    | TxCK Low Pulse       | Sync w/Prescaler  | Tcy + 20                                         | _     | ns         | Must also meet     |

|               |        | Time                 | Async w/Prescaler | 10                                               | _     | ns         | Parameter Ttp      |

|               |        |                      | Async Counter     | 20                                               | _     | ns         |                    |

|               | TtP    | TxCK External Input  | Sync w/Prescaler  | 2 * Tcy + 40                                     | _     | ns         | N = Prescale Value |

|               |        | Period               | Async w/Prescaler | Greater of:<br>20 or<br><u>2 * Tcy + 40</u><br>N | —     | ns         | (1, 4, 8, 16)      |

|               |        |                      | Async Counter     | 40                                               |       | ns         |                    |

|               |        | Delay for Input Edge | Synchronous       | 1                                                | 2     | TCY        |                    |

|               |        | to Timer Increment   | Asynchronous      | —                                                | 20    | ns         |                    |

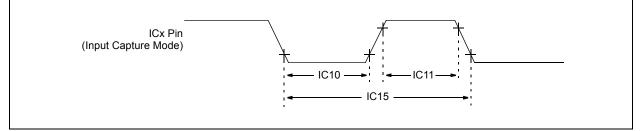

#### FIGURE 29-9: INPUT CAPTURE x TIMINGS

#### TABLE 29-28: INPUT CAPTURE x REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic           |                | Min                      | Мах | Units | Conditions                       |

|---------------|--------|--------------------------|----------------|--------------------------|-----|-------|----------------------------------|

| IC10          | TccL   | ICx Input Low Time –     | No Prescaler   | Tcy + 20                 | —   | ns    | Must also meet                   |

|               |        | Synchronous Timer        | With Prescaler | 20                       | —   | ns    | Parameter IC15                   |

| IC11          | ТссН   | ICx Input Low Time –     | No Prescaler   | Tcy + 20                 | —   | ns    | Must also meet                   |

|               |        | Synchronous Timer        | With Prescaler | 20                       | —   | ns    | Parameter IC15                   |

| IC15          | TccP   | ICx Input Period – Syncl | nronous Timer  | <u>2 * Tcy + 40</u><br>N | —   | ns    | N = prescale value<br>(1, 4, 16) |

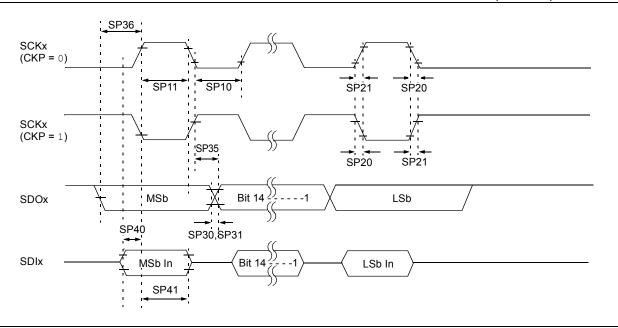

#### FIGURE 29-19: SPIX MODULE MASTER MODE TIMING CHARACTERISTICS (CKE = 1)

#### TABLE 29-37: SPIX MODULE MASTER MODE TIMING REQUIREMENTS (CKE = 1)

| АС СНА       | RACTERIST             | TICS                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |            |  |

|--------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|

| Param<br>No. | Symbol                | Characteristic                               | Min                                                                                                                                                                                                                                                                                     | Typ <sup>(1)</sup> | Мах | Units | Conditions |  |

| SP10         | TscL                  | SCKx Output Low Time <sup>(2)</sup>          | Tcy/2                                                                                                                                                                                                                                                                                   | —                  | _   | ns    |            |  |

| SP11         | TscH                  | SCKx Output High Time <sup>(2)</sup>         | Tcy/2                                                                                                                                                                                                                                                                                   |                    | _   | ns    |            |  |

| SP20         | TscF                  | SCKx Output Fall Time <sup>(3)</sup>         | _                                                                                                                                                                                                                                                                                       | 10                 | 25  | ns    |            |  |

| SP21         | TscR                  | SCKx Output Rise Time <sup>(3)</sup>         | —                                                                                                                                                                                                                                                                                       | 10                 | 25  | ns    |            |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                       | 10                 | 25  | ns    |            |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                       | 10                 | 25  | ns    |            |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                       | —                  | 30  | ns    |            |  |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                      |                    | —   | ns    |            |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 20                                                                                                                                                                                                                                                                                      | —                  | —   | ns    |            |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 20                                                                                                                                                                                                                                                                                      | —                  | —   | ns    |            |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** The minimum clock period for SCKx is 100 ns; therefore, the clock generated in Master mode must not violate this specification.

3: This assumes a 50 pF load on all SPIx pins.

#### TABLE 29-40: A/D MODULE SPECIFICATIONS

|              |           |                                                      | Standard Opera                  | ting C |                                                              |        |                                                |

|--------------|-----------|------------------------------------------------------|---------------------------------|--------|--------------------------------------------------------------|--------|------------------------------------------------|

| AC CHA       | ARACTERI  | STICS                                                | Operating tempe                 | rature | 2.0V<br>-40°C $\leq$ TA $\leq$ +<br>-40°C $\leq$ TA $\leq$ + | 85°C f |                                                |

| Param<br>No. | Symbol    | Characteristic                                       | Min.                            | Тур    | Max.                                                         | Units  | Conditions                                     |

|              |           |                                                      | Device S                        | upply  |                                                              |        |                                                |

| AD01         | AVDD      | Module VDD Supply                                    | Greater of:<br>VDD – 0.3 or 1.8 |        | Lesser of:<br>VDD + 0.3 or 3.6                               | V      | PIC24FXXKA30X devices                          |

|              |           |                                                      | Greater of:<br>VDD – 0.3 or 2.0 |        | Lesser of:<br>VDD + 0.3 or 5.5                               | V      | PIC24FVXXKA30X<br>devices                      |

| AD02         | AVss      | Module Vss Supply                                    | Vss-0.3                         |        | Vss + 0.3                                                    | V      |                                                |

|              |           |                                                      | Reference                       | Inputs | 3                                                            |        | -                                              |

| AD05         | VREFH     | Reference Voltage High                               | AVss + 1.7                      | _      | AVDD                                                         | V      |                                                |

| AD06         | VREFL     | Reference Voltage Low                                | AVss                            | _      | AVDD – 1.7                                                   | V      |                                                |

| AD07         | Vref      | Absolute Reference<br>Voltage                        | AVss – 0.3                      | —      | AVDD + 0.3                                                   | V      |                                                |

| AD08         | IVREF     | Reference Voltage Input<br>Current                   | _                               | 1.25   | —                                                            | mA     |                                                |

| AD09         | ZVREF     | Reference Input<br>Impedance                         | _                               | 10k    | _                                                            | Ω      |                                                |

|              |           |                                                      | Analog                          | nput   | 1                                                            |        |                                                |

| AD10         | VINH-VINL | Full-Scale Input Span                                | VREFL                           | —      | VREFH                                                        | V      | (Note 2)                                       |

| AD11         | VIN       | Absolute Input Voltage                               | AVss - 0.3                      |        | AVDD + 0.3                                                   | V      |                                                |

| AD12         | VINL      | Absolute VINL Input<br>Voltage                       | AVss – 0.3                      |        | AVDD/2                                                       | V      |                                                |

| AD17         | RIN       | Recommended<br>Impedance of Analog<br>Voltage Source | —                               | _      | 1k                                                           | Ω      | 12-bit                                         |

|              |           |                                                      | A/D Acc                         | uracy  |                                                              |        |                                                |

| AD20b        | NR        | Resolution                                           | —                               | 12     | —                                                            | bits   |                                                |

| AD21b        | INL       | Integral Nonlinearity                                | _                               | ±1     | ±9                                                           | LSb    | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |

| AD22b        | DNL       | Differential Nonlinearity                            | —                               | ±1     | ±5                                                           | LSb    | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |

| AD23b        | Gerr      | Gain Error                                           | —                               | ±1     | ±9                                                           | LSb    | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |

| AD24b        | EOFF      | Offset Error                                         | _                               | ±1     | ±5                                                           | LSb    | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |

| AD25b        |           | Monotonicity <sup>(1)</sup>                          |                                 | _      | _                                                            | _      | Guaranteed                                     |

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage.

2: Measurements are taken with external VREF+ and VREF- used as the A/D voltage reference.

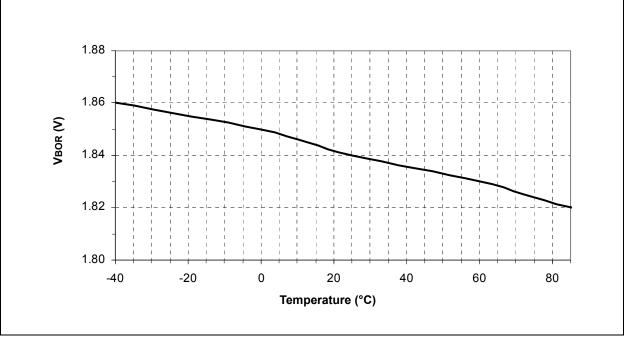

FIGURE 30-23: TYPICAL VBOR vs. TEMPERATURE (BOR TRIP POINT 3)

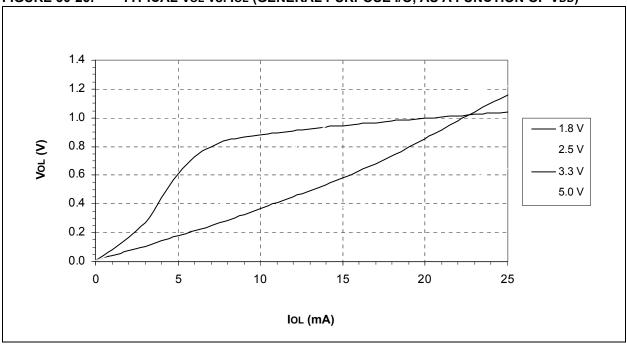

FIGURE 30-26: TYPICAL Vol vs. IoL (GENERAL PURPOSE I/O, AS A FUNCTION OF VDD)

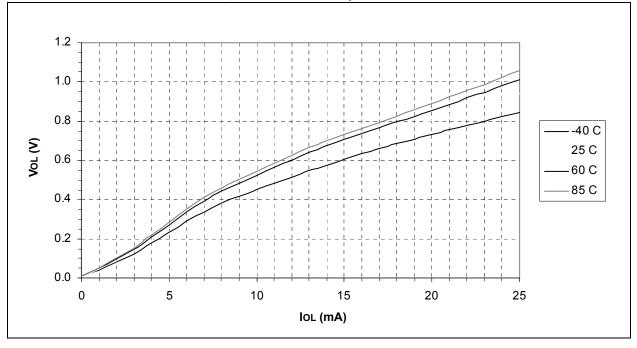

FIGURE 30-27: TYPICAL Vol vs. Iol (GENERAL PURPOSE I/O, AS A FUNCTION OF TEMPERATURE,  $2.0V \le Vdd \le 5.5V$ )

### 30.2 Characteristics for Extended Temperature Devices (-40°C to +125°C)

Note: Data for VDD levels greater than 3.3V are applicable to PIC24FV32KA304 family devices only.

FIGURE 30-40: TYPICAL AND MAXIMUM lidle vs. Vdd (FRC MODE)

| libLE (mA) |  |     |  |  |

|------------|--|-----|--|--|

|            |  | VDD |  |  |

#### FIGURE 30-41: TYPICAL AND MAXIMUM lidle vs. TEMPERATURE (FRC MODE)

| liple (mA) |                  |

|------------|------------------|

|            | Temperature (°C) |

FIGURE 30-49: TYPICAL Vol vs. Iol (GENERAL I/O,  $2.0V \le VDD \le 5.5V$ )

0 Γοι (MA)

## FIGURE 30-50: TYPICAL VOH vs. IOH (GENERAL I/O, AS A FUNCTION OF TEMPERATURE, $2.0V \le V \text{DD} \le 5.5 \text{V})$

| (л) нол | - | -<br>-  | - | _ | - |

|---------|---|---------|---|---|---|

|         |   | Юн (mA) | ) |   |   |

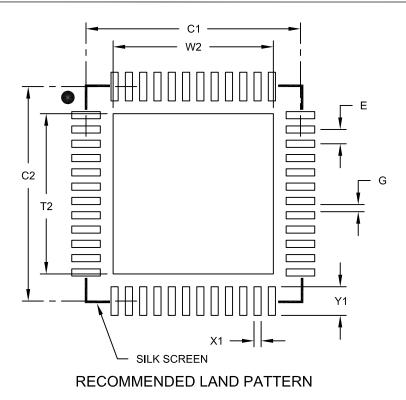

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

|                            | Units    |          |      |      |  |

|----------------------------|----------|----------|------|------|--|

| Dimensio                   | n Limits | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E        | 0.40 BSC |      |      |  |

| Optional Center Pad Width  | W2       |          |      | 4.45 |  |

| Optional Center Pad Length | T2       |          |      | 4.45 |  |

| Contact Pad Spacing        | C1       |          | 6.00 |      |  |

| Contact Pad Spacing        | C2       |          | 6.00 |      |  |

| Contact Pad Width (X28)    | X1       |          |      | 0.20 |  |

| Contact Pad Length (X28)   | Y1       |          |      | 0.80 |  |

| Distance Between Pads      | G        | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A