Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka302-e-sp |

TABLE 1-2: DEVICE FEATURES FOR THE PIC24F32KA304 FAMILY

|                                                  | KES I OK IIII                                                                                                                                 | - 1 102 11 021 |                    |                                            | ı                              |               |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|--------------------------------------------|--------------------------------|---------------|--|--|

| Features                                         | PIC24F16KA301                                                                                                                                 | PIC24F32KA301  | PIC24F16KA302      | PIC24F32KA302                              | PIC16F16KA304                  | PIC24F32KA304 |  |  |

| Operating Frequency                              |                                                                                                                                               |                | DC - 32 ľ          | MHz                                        |                                |               |  |  |

| Program Memory (bytes)                           | 16K                                                                                                                                           | 32K            | 16K                | 32K                                        | 16K                            | 32K           |  |  |

| Program Memory (instructions)                    | 5632                                                                                                                                          | 11264          | 5632               | 11264                                      | 5632                           | 11264         |  |  |

| Data Memory (bytes)                              |                                                                                                                                               |                | 2048               |                                            |                                |               |  |  |

| Data EEPROM Memory (bytes)                       |                                                                                                                                               |                | 512                |                                            |                                |               |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)   |                                                                                                                                               |                | 30 (26/            | 4)                                         |                                |               |  |  |

| I/O Ports                                        | PORTA<br>PORTB<15:12                                                                                                                          | PORTA<br>PORTB | •                  | PORTA<11:0>,<br>PORTB<15:0>,<br>PORTC<9:0> |                                |               |  |  |

| Total I/O Pins                                   | 18                                                                                                                                            | 3              | 24                 | 4                                          | 3                              | 9             |  |  |

| Timers: Total Number (16-bit)                    |                                                                                                                                               |                | 5                  |                                            |                                |               |  |  |

| 32-Bit (from paired 16-bit timers)               |                                                                                                                                               |                | 2                  |                                            |                                |               |  |  |

| Input Capture Channels                           |                                                                                                                                               |                | 3                  |                                            |                                |               |  |  |

| Output Compare/PWM Channels                      |                                                                                                                                               |                | 3                  |                                            |                                |               |  |  |

| Input Change Notification Interrupt              | 17                                                                                                                                            | 7              | 23                 | 3                                          | 3                              | 8             |  |  |

| Serial Communications: UART SPI (3-wire/4-wire)  |                                                                                                                                               |                | 2                  |                                            |                                |               |  |  |

| I <sup>2</sup> C <sup>TM</sup>                   |                                                                                                                                               |                | 2                  |                                            |                                |               |  |  |

| 12-Bit Analog-to-Digital Module (input channels) | 12                                                                                                                                            | 2              | 1:                 | 3                                          | 1                              | 6             |  |  |

| Analog Comparators                               |                                                                                                                                               |                | 3                  |                                            |                                |               |  |  |

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode, REPEAT Instruction, Hardware Traps, Configuration Word Mismatch (PWRT, OST, PLL Lock) |                |                    |                                            |                                |               |  |  |

| Instruction Set                                  | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                     |                |                    |                                            |                                |               |  |  |

| Packages                                         | 20-F<br>PDIP/SSC                                                                                                                              |                | 28-I<br>SPDIP/SSOF |                                            | 44-Pin QFN/TQFP<br>48-Pin UQFN |               |  |  |

TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer            | Description                       |

| AN0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA               |                                   |

| AN2      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               |                                   |

| AN3      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ANA               |                                   |

| AN4      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ANA               |                                   |

| AN5      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I   | ANA               |                                   |

| AN6      | _                                | _                                 | _             | 25                     | 27             | _                                | _                                 | _             | 25                     | 27             | ı   | ANA               |                                   |

| AN7      | _                                | _                                 | _             | 26                     | 28             | _                                | _                                 | _             | 26                     | 28             | ı   | ANA               |                                   |

| AN8      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I   | ANA               |                                   |

| AN9      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ANA               |                                   |

| AN10     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA               |                                   |

| AN11     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | I   | ANA               |                                   |

| AN12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ANA               |                                   |

| AN13     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ANA               |                                   |

| AN14     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ANA               |                                   |

| AN15     | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA               |                                   |

| ASCL1    | _                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | I <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | _                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | I <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                                | 25            | 17                     | 18             | 20                               | 28                                | 25            | 17                     | 18             | I   | ANA               | A/D Supply Pins                   |

| AVss     | 19                               | 27                                | 24            | 16                     | 17             | 19                               | 27                                | 24            | 16                     | 17             | I   | ANA               |                                   |

| C1INA    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | I   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | ı   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | ı   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | ı   | ANA               | Comparator 1 Input D (-)          |

| C1OUT    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | _                 | Comparator 1 Output               |

| C2INA    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ANA               | Comparator 2 Input A (+)          |

| C2INB    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 2 Input B (-)          |

| C2INC    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | I   | ANA               | Comparator 2 Input C (+)          |

| C2IND    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | I   | ANA               | Comparator 2 Input D (-)          |

| C2OUT    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 16                                | 13            | 43                     | 47             | 0   | _                 | Comparator 2 Output               |

TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  |                                   | Pin Number    |                        |                | Pin Number                       |                                   |               |                        |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| CTPLS    | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | 0   | _      | CTMU Pulse Output                              |

| HLVDIN   | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     | High/Low-Voltage Detect Input                  |

| IC1      | 14                               | 19                                | 16            | 6                      | 6              | 11                               | 19                                | 16            | 6                      | 6              | I   | ST     | Input Capture 1 Input                          |

| IC2      | 13                               | 18                                | 15            | 5                      | 5              | 13                               | 18                                | 15            | 5                      | 5              | - 1 | ST     | Input Capture 2 Input                          |

| IC3      | 15                               | 23                                | 20            | 13                     | 14             | 15                               | 23                                | 20            | 13                     | 14             | - 1 | ST     | Input Capture 3 Input                          |

| INT0     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | - 1 | ST     | Interrupt 0 Input                              |

| INT1     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | - 1 | ST     | Interrupt 1 Input                              |

| INT2     | 14                               | 20                                | 17            | 7                      | 7              | 15                               | 23                                | 20            | 10                     | 11             | - 1 | ST     | Interrupt 2 Input                              |

| MCLR     | 1                                | 1                                 | 26            | 18                     | 19             | 1                                | 1                                 | 26            | 18                     | 19             | 1   | ST     | Master Clear (Device Reset) Input (active-low) |

| OC1      | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 16                                | 13            | 43                     | 47             | 0   | _      | Output Compare/PWM1 Output                     |

| OC2      | 4                                | 22                                | 19            | 4                      | 4              | 4                                | 22                                | 19            | 4                      | 4              | 0   | _      | Output Compare/PWM2 Output                     |

| OC3      | 5                                | 21                                | 18            | 12                     | 13             | 5                                | 21                                | 18            | 12                     | 13             | 0   | _      | Output Compare/PWM3 Output                     |

| OCFA     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | _      | Output Compare Fault A                         |

| OFCB     | 16                               | 24                                | 21            | 32                     | 35             | 16                               | 24                                | 21            | 32                     | 35             | 0   | _      | Output Compare Fault B                         |

| OSCI     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | -1  | ANA    | Main Oscillator Input                          |

| OSCO     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | 0   | ANA    | Main Oscillator Output                         |

| PGEC1    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I/O | ST     | ICSP™ Clock 1                                  |

| PCED1    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I/O | ST     | ICSP Data 1                                    |

| PGEC2    | 2                                | 22                                | 19            | 19                     | 10             | 2                                | 22                                | 19            | 19                     | 10             | I/O | ST     | ICSP Clock 2                                   |

| PGED2    | 3                                | 21                                | 18            | 8                      | 9              | 3                                | 21                                | 18            | 8                      | 9              | I/O | ST     | ICSP Data 2                                    |

| PGEC3    | 10                               | 15                                | 12            | 42                     | 46             | 10                               | 15                                | 12            | 42                     | 46             | I/O | ST     | ICSP Clock 3                                   |

| PGED3    | 9                                | 14                                | 11            | 41                     | 45             | 9                                | 14                                | 11            | 41                     | 45             | I/O | ST     | ICSP Data 3                                    |

TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                   | Bit 14  | Bit 13  | Bit 12                   | Bit 11                 | Bit 10                   | Bit 9                    | Bit 8                  | Bit 7                 | Bit 6   | Bit 5   | Bit 4                    | Bit 3                    | Bit 2                    | Bit 1                    | Bit 0                    | All<br>Resets |

|--------------|------|--------------------------|---------|---------|--------------------------|------------------------|--------------------------|--------------------------|------------------------|-----------------------|---------|---------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|---------------|

| CNPD1        | 0056 | CN15PDE <sup>(1)</sup>   | CN14PDE | CN13PDE | CN12PDE                  | CN11PDE                | CN10PDE <sup>(1,2)</sup> | CN9PDE <sup>(1)</sup>    | CN8PDE <sup>(3)</sup>  | CN7PDE <sup>(1)</sup> | CN6PDE  | CN5PDE  | CN4PDE                   | CN3PDE                   | CN2PDE                   | CN1PDE                   | CN0PDE                   | 0000          |

| CNPD2        | 0058 | CN31PDE <sup>(1,2)</sup> | CN30PDE | CN29PDE | CN28PDE <sup>(1,2)</sup> | CN27PDE <sup>(1)</sup> | CN26PDE <sup>(1,2)</sup> | CN25PDE <sup>(1,2)</sup> | CN24PDE <sup>(1)</sup> | CN23PDE               | CN22PDE | CN21PDE | CN20PDE <sup>(1,2)</sup> | CN19PDE <sup>(1,2)</sup> | CN18PDE <sup>(1,2)</sup> | CN17PDE <sup>(1,2)</sup> | CN16PDE <sup>(1)</sup>   | 0000          |

| CNPD3        | 005A | _                        | -       | _       | _                        | -                      | _                        | _                        | _                      | 1                     | -       | _       | CN36PDE <sup>(1,2)</sup> | CN35PDE <sup>(1,2)</sup> | CN34PDE <sup>(1,2)</sup> | CN33PDE <sup>(1,2)</sup> | CN32PDE <sup>(1,2)</sup> | 0000          |

| CNEN1        | 0062 | CN15IE <sup>(1)</sup>    | CN14IE  | CN13IE  | CN12IE                   | CN11IE                 | CN10IE <sup>(1,2)</sup>  | CN9IE <sup>(1)</sup>     | CN8IE(3)               | CN7IE <sup>(1)</sup>  | CN6IE   | CN5IE   | CN4IE                    | CN3IE                    | CN2IE                    | CN1IE                    | CN0IE                    | 0000          |

| CNEN2        | 0064 | CN31IE <sup>(1,2)</sup>  | CN30IE  | CN29IE  | CN28IE <sup>(1,2)</sup>  | CN27IE <sup>(1)</sup>  | CN26IE <sup>(1,2)</sup>  | CN25IE <sup>(1,2)</sup>  | CN24IE <sup>(1)</sup>  | CN23IE                | CN22IE  | CN21IE  | CN20IE <sup>(1,2)</sup>  | CN19IE <sup>(1,2)</sup>  | CN18IE <sup>(1,2)</sup>  | CN17IE <sup>(1,2)</sup>  | CN16IE <sup>(1)</sup>    | 0000          |

| CNEN3        | 0066 | -                        | -       | 1       | _                        | ı                      | -                        | _                        | 1                      | -                     | _       | -       | CN36IE <sup>(1,2)</sup>  | CN35IE <sup>(1,2)</sup>  | CN34IE <sup>(1,2)</sup>  | CN33IE <sup>(1,2)</sup>  | CN32IE <sup>(1,2)</sup>  | 0000          |

| CNPU1        | 006E | CN15PUE <sup>(1)</sup>   | CN14PUE | CN13PUE | CN12PUE                  | CN11PUE                | CN10PUE <sup>(1,2)</sup> | CN9PUE <sup>(1)</sup>    | CN8PUE <sup>(3)</sup>  | CN7PUE <sup>(1)</sup> | CN6PUE  | CN5PUE  | CN4PUE                   | CN3PUE                   | CN2PUE                   | CN1PUE                   | CN0PUE                   | 0000          |

| CNPU2        | 0070 | CN31PUE <sup>(1,2)</sup> | CN30PUE | CN29PUE | CN28PUE <sup>(1,2)</sup> | CN27PUE <sup>(1)</sup> | CN26PUE <sup>(1,2)</sup> | CN25PUE <sup>(1,2)</sup> | CN24PUE <sup>(1)</sup> | CN23PUE               | CN22PUE | CN21PUE | CN20PUE <sup>(1,2)</sup> | CN19PUE <sup>(1,2)</sup> | CN18PUE <sup>(1,2)</sup> | CN17PUE <sup>(1,2)</sup> | CN16PUE <sup>(1)</sup>   | 0000          |

| CNPU3        | 0072 | _                        | _       | _       | _                        | _                      | _                        | _                        | _                      | _                     | _       | _       | CN36PUE <sup>(1,2)</sup> | CN35PUE <sup>(1,2)</sup> | CN34PUE <sup>(1,2)</sup> | CN33PUE <sup>(1,2)</sup> | CN32PUE <sup>(1,2)</sup> | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

3: These bits are not implemented in FV devices.

# 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is as follows:

- Read a row of program memory (32 instructions) and store in data RAM.

- Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '011000' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

```

; Set up NVMCON for row erase operation

MOV

#0x4058, W0

; Initialize NVMCON

MOV

W0, NVMCON

; Init pointer to row to be ERASED

MOV

#tblpage(PROG ADDR), W0

MOV

WO, TBLPAG

; Initialize PM Page Boundary SFR

#tbloffset(PROG ADDR), W0

MOV

; Initialize in-page EA[15:0] pointer

TBLWTL WO, [WO]

; Set base address of erase block

#5

; Block all interrupts

DISI

for next 5 instructions

MOV

#0x55, W0

WO, NVMKEY

VOM

; Write the 55 key

#0xAA, W1

MOV

; Write the AA key

MOV

W1, NVMKEY

NVMCON, #WR

; Start the erase sequence

BSET

NOP

; Insert two NOPs after the erase

NOP

; command is asserted

```

The following code sequence for a clock switch is recommended:

- Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON

in two back-to-back instructions.

- Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

# EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

```

;Place the new oscillator selection in WO

;OSCCONH (high byte) Unlock Sequence

#OSCCONH, w1

MOV

#0x78, w2

MOV

#0x9A, w3

MOV.b

w2, [w1]

MOV.b

w3, [w1]

;Set new oscillator selection

MOV.b

WREG, OSCCONH

;OSCCONL (low byte) unlock sequence

#OSCCONL, w1

MOV

MOV

#0x46, w2

#0x57, w3

MOV

MOV.b

w2, [w1]

MOV.b

w3, [w1]

;Start oscillator switch operation

OSCCON, #0

```

#### 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FV32KA304 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

#### 10.2.4.5 Deep Sleep WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (FDS<7>). The device Watchdog Timer (WDT) need not be enabled for the DSWDT to function. Entry into Deep Sleep mode automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (FDS<4>). The post-scaler options are programmed by the DSWDTPS<3:0> Configuration bits (FDS<3:0>). The minimum time-out period that can be achieved is 2.1 ms and the maximum is 25.7 days. For more details on the FDS Configuration register and DSWDT configuration options, refer to **Section 26.0 "Special Features"**.

#### 10.2.4.6 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If a more accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCOSC Configuration bit (FDS<5>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention; however, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

# 10.2.4.7 Checking and Clearing the Status of Deep Sleep

Upon entry into Deep Sleep mode, the status bit, DPSLP (RCON<10>), becomes set and must be cleared by the software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set; this

is a normal POR.

- Both the DPSLP and POR bits are set. This

means that Deep Sleep mode was entered, the

device was powered down and Deep Sleep mode

was exited.

#### 10.2.4.8 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep functionally looks like a POR, the technique described in **Section 10.2.4.7** "Checking and Clearing the Status of Deep Sleep" should be used to distinguish between Deep Sleep and a true POR event.

When a true POR occurs, the entire device, including all Deep Sleep logic (Deep Sleep registers: RTCC, DSWDT, etc.) is reset.

#### 10.2.4.9 Summary of Deep Sleep Sequence

To review, these are the necessary steps involved in invoking and exiting Deep Sleep mode:

- The device exits Reset and begins to execute its application code.

- If DSWDT functionality is required, program the appropriate Configuration bit.

- Select the appropriate clock(s) for the DSWDT and RTCC (optional).

- 4. Enable and configure the DSWDT (optional).

- 5. Enable and configure the RTCC (optional).

- Write context data to the DSGPRx registers (optional).

- 7. Enable the INT0 interrupt (optional).

- 8. Set the DSEN bit in the DSCON register.

- 9. Enter Deep Sleep by issuing a PWRSV #SLEEP\_MODE command.

- 10. The device exits Deep Sleep when a wake-up event occurs.

- 11. The DSEN bit is automatically cleared.

- Read and clear the DPSLP status bit in RCON, and the DSWAKE status bits.

- 13. Read the DSGPRx registers (optional).

- Once all state related configurations are complete, clear the RELEASE bit.

- 15. The application resumes normal operation.

#### REGISTER 13-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | _   | TSIDL <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0              | U-0   |

|-------|----------------------|-----------------------|-----------------------|-----|-----|--------------------|-------|

| _     | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> | _   | _   | TCS <sup>(1)</sup> | _     |

| bit 7 |                      |                       |                       |     |     |                    | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timery On bit<sup>(1)</sup>

1 = Starts 16-bit Timery

0 = Stops 16-bit Timery

bit 14 Unimplemented: Read as '0'

bit 13 **TSIDL:** Timery Stop in Idle Mode bit<sup>(1)</sup>

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 **TGATE:** Timery Gated Time Accumulation Enable bit<sup>(1)</sup>

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timery Input Clock Prescale Select bits<sup>(1)</sup>

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timery Clock Source Select bit<sup>(1)</sup>

1 = External clock is from the T3CK pin (on the rising edge)

0 = Internal clock (Fosc/2)

bit 0 Unimplemented: Read as '0'

**Note 1:** When 32-bit operation is enabled (TxCON<3> = 1), these bits have no effect on Timery operation. All timer functions are set through the TxCON register.

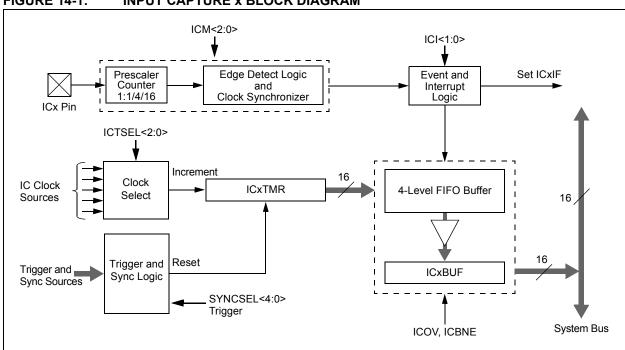

# 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 34. "Input Capture with Dedicated Timer" (DS39722).

All devices in the PIC24FV32KA304 family feature three independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events, and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 20 user-selectable Sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

#### 14.1 General Operating Modes

# 14.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the input capture module operates in a Free-Running mode. The internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected Sync source, the internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSELx bits to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the Sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

FIGURE 14-1: INPUT CAPTURE x BLOCK DIAGRAM

#### 15.4 Subcycle Resolution

The DCBx bits (OCxCON2<10:9>) provide for resolution better than one instruction cycle. When used, they delay the falling edge generated from a match event by a portion of an instruction cycle.

For example, setting DCB<1:0> = 10 causes the falling edge to occur halfway through the instruction cycle in which the match event occurs, instead of at the beginning. These bits cannot be used when OCM<2:0> = 001. When operating the module in PWM mode (OCM<2:0> = 110 or 111), the DCBx bits will be double-buffered.

The DCBx bits are intended for use with a clock source identical to the system clock. When an OCx module with enabled prescaler is used, the falling edge delay caused by the DCBx bits will be referenced to the system clock period, rather than the OCx module's period.

TABLE 15-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (FcY = 4 MHz)<sup>(1)</sup>

| PWM Frequency     | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-------------------|--------|-------|--------|--------|---------|----------|---------|

| Prescaler Ratio   | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Value      | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits) | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

#### TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (FcY = 16 MHz)<sup>(1)</sup>

| PWM Frequency     | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-------------------|---------|--------|--------|---------|----------|---------|---------|

| Prescaler Ratio   | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Value      | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits) | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

#### 19.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- · RTCC Value Registers

- · Alarm Value Registers

#### 19.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value Register Window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 19-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 19-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |  |  |  |

|-------------|----------------------------|-------------|--|--|--|--|--|--|

| KICPIK 1.02 | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |  |  |

| 0.0         | MINUTES                    | SECONDS     |  |  |  |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |  |  |  |

| 11          |                            | YEAR        |  |  |  |  |  |  |

The Alarm Value Register Window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 19-2).

By writing the ALRMVALH byte, the Alarm Pointer value (ALRMPTR<1:0> bits) decrements by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL, until the pointer value is manually changed.

TABLE 19-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |  |  |

|---------|-----------------------------|--------------|--|--|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |  |  |

| 0.0     | ALRMMIN                     | ALRMSEC      |  |  |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |  |  |

| 11      | PWCSTAB                     | PWCSAMP      |  |  |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

#### 19.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RTCPWC<13>) must be set (see Example 19-1).

| Note: | To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only one instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN. Therefore, it is recommended that code |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | follow the procedure in Example 19-1.                                                                                                                                                                                                                                                                                |

#### 19.2.3 SELECTING RTCC CLOCK SOURCE

There are four reference source clock options that can be selected for the RTCC using the RTCCSEL<1:0> bits: 00 = Secondary Oscillator, 01 = LPRC, 10 = 50 Hz External Clock and 11 = 60 Hz External Clock.

#### **EXAMPLE 19-1: SETTING THE RTCWREN BIT**

```

asm

volatile

("push w7");

volatile

("push w8");

asm

asm volatile

("disi #5");

asm volatile

("mov #0x55, w7");

asm volatile

("mov w7, NVMKEY");

asm volatile

("mov #0xAA, w8");

volatile

("mov w8, NVMKEY");

asm

("bset RCFGCAL, #13");

//set the RTCWREN bit

asm

volatile

volatile

("pop w8");

asm

asm

volatile

("pop w7");

```

### REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

bit 7-0 CAL<7:0>: RTC Drift Calibration bits

01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute

.

. 00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute 00000000 = No adjustment

11111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute

.

10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute

**Note 1:** The RCFGCAL register is only affected by a POR.

2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

#### REGISTER 22-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)(1)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      |     |     | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | CHH17 | CHH16 |

| bit 7 |     |     |     |     |     |       | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-2 Unimplemented: Read as '0'.

bit 1-0 CHH<17:16>: A/D Compare Hit bits

If CM<1:0> = 11:

1 = A/D Result Buffer x has been written with data or a match has occurred

0 = A/D Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

1 = A match has occurred on A/D Result Channel x

0 = No match has occurred on A/D Result Channel x

**Note 1:** Unimplemented channels are read as '0'.

#### REGISTER 22-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)(1)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| CHH15  | CHH14 | CHH13 | CHH12 | CHH11 | CHH10 | CHH9  | CHH8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CHH7  | CHH6  | CHH5  | CHH4  | CHH3  | CHH2  | CHH1  | CHH0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 CHH<15:0>: A/D Compare Hit bits

#### If CM<1:0> = 11:

1 = A/D Result Buffer x has been written with data or a match has occurred

0 = A/D Result Buffer x has not been written with data

#### For all other values of CM<1:0>:

1 = A match has occurred on A/D Result Channel x

0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

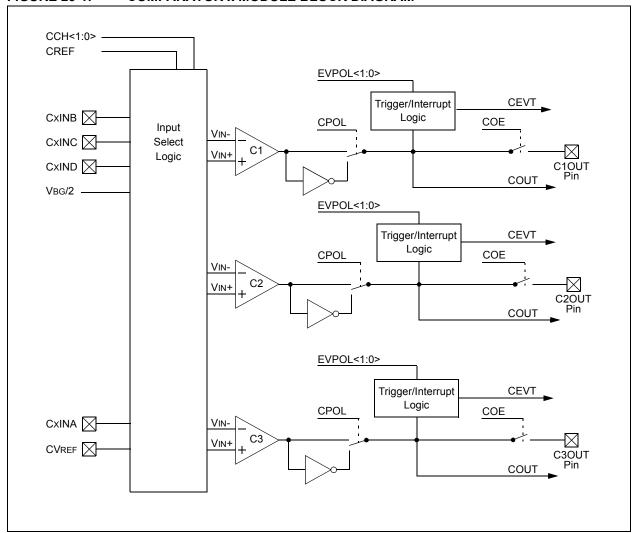

#### 23.0 COMPARATOR MODULE

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator module, refer to the "PIC24F Family Reference Manual", Section 46. "Scalable Comparator Module" (DS39734).

The comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as a voltage reference input from either the internal band gap reference, divided by 2 (VBG/2), or the comparator voltage reference generator.

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is shown in Figure 23-1. Diagrams of the possible individual comparator configurations are shown in Figure 23-2.

Each comparator has its own control register, CMxCON (Register 23-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 23-2).

FIGURE 23-1: COMPARATOR x MODULE BLOCK DIAGRAM

# 27.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit™ 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 27.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

#### 27.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoQ® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta A/D, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

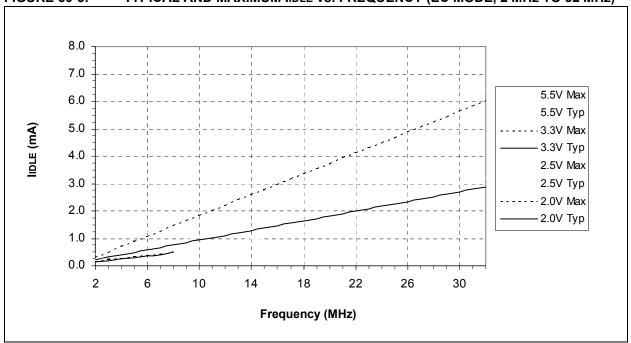

FIGURE 30-3: TYPICAL AND MAXIMUM lidle vs. FREQUENCY (EC MODE, 2 MHz TO 32 MHz)

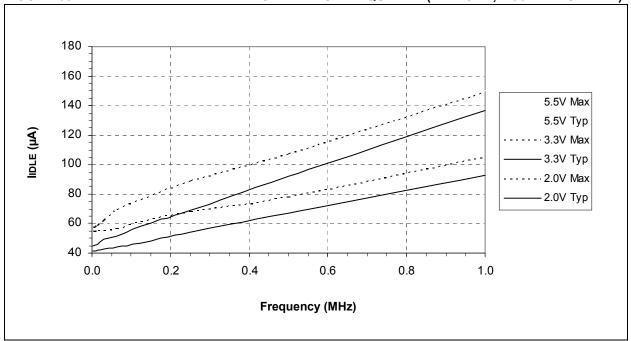

FIGURE 30-4: TYPICAL AND MAXIMUM lidle vs. FREQUENCY (EC MODE, 1.95 kHz TO 1 MHz)

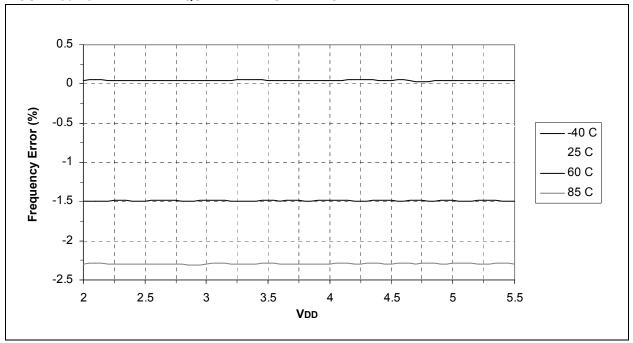

FIGURE 30-10: FRC FREQUENCY ACCURACY vs. VDD

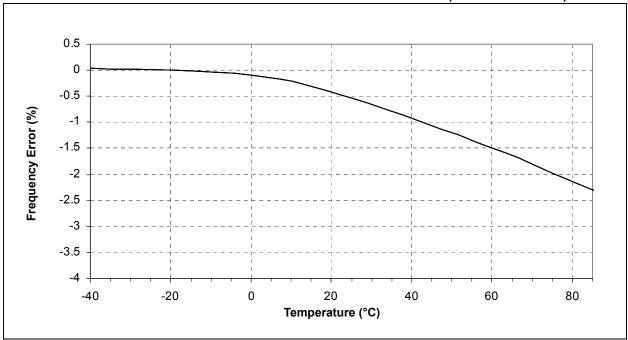

FIGURE 30-11: FRC FREQUENCY ACCURACY vs. TEMPERATURE ( $2.0V \le VDD \le 5.5V$ )

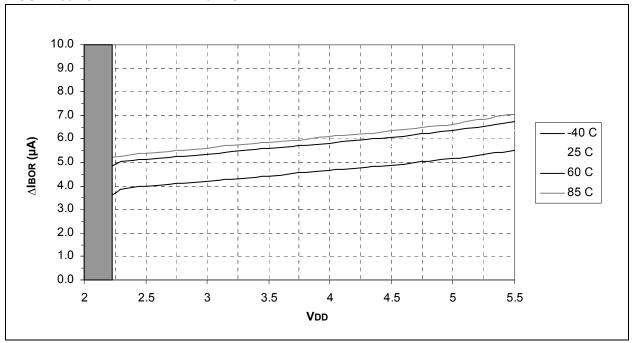

FIGURE 30-18: TYPICAL ∆IBOR vs. VDD

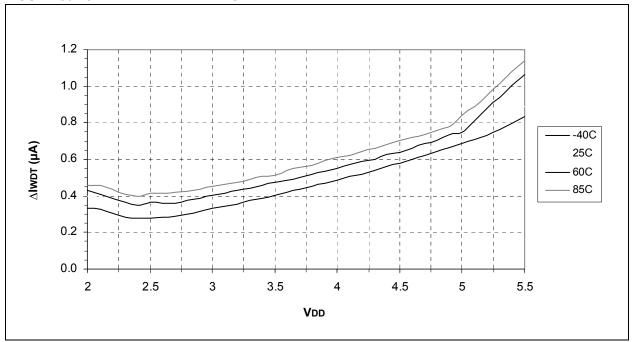

FIGURE 30-19: TYPICAL AlWDT vs. VDD

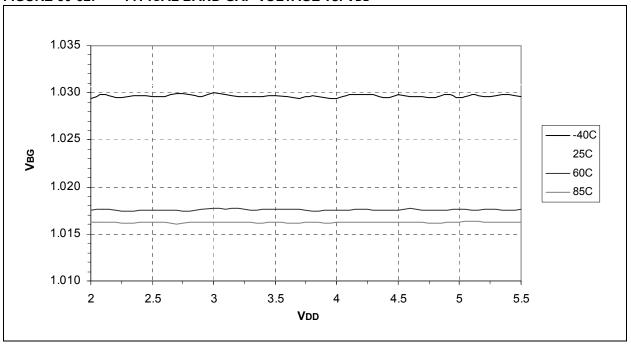

FIGURE 30-32: TYPICAL BAND GAP VOLTAGE vs. VDD

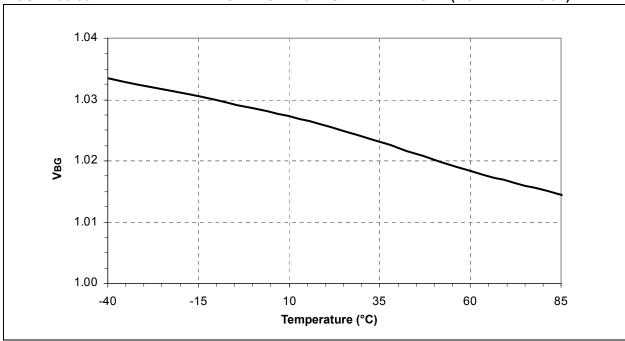

FIGURE 30-33: TYPICAL BAND GAP VOLTAGE vs. TEMPERATURE (2.0V ≤ VDD ≤ 5.5V)

| FIGURE 30-55:        | TYPICAL BAND GAP VOLTAGE vs. TEMPERATURE (2.0V $\leq$ VDD $\leq$ 5.5V) |

|----------------------|------------------------------------------------------------------------|

|                      |                                                                        |

| VBG (V)              |                                                                        |

|                      | Temperature (°C)                                                       |

| FIGURE 30-56:        | TYPICAL VOLTAGE REGULATOR OUTPUT vs. TEMPERATURE                       |

| Regulator Output (V) |                                                                        |

|                      | Temperature (°C)                                                       |