#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Betuns                     |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka302-e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

# 1.1.4 EASY MIGRATION

Regardless of the memory size, all the devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex.

# 1.2 Other Special Features

- Communications: The PIC24FV32KA304 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an I<sup>2</sup>C<sup>™</sup> module that supports both the Master and Slave modes of operation. It also comprises UARTs with built-in IrDA<sup>®</sup> encoders/decoders and an SPI module.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- **12-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV32KA304 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation.

# 1.3 Details on Individual Family Members

Devices in the PIC24FV32KA304 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are different from each other in four ways:

- Flash program memory (16 Kbytes for PIC24FV16KA devices, 32 Kbytes for PIC24FV32KA devices).

- Available I/O pins and ports (18 pins on two ports for 20-pin devices, 22 pins on two ports for 28-pin devices and 38 pins on three ports for 44/48-pin devices).

- 3. Alternate SCLx and SDAx pins are available only in 28-pin, 44-pin and 48-pin devices and not in 20-pin devices.

- 4. Members of the PIC24FV32KA301 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV32KA304), accommodate an operating VDD range of 2.0V to 5.5V, and have an on-board Voltage Regulator that powers the core. Peripherals operate at VDD. Standard devices, designated by "F" (such as PIC24F32KA304), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

All other features for devices in this family are identical; these are summarized in Table 1-1.

A list of the pin features available on the PIC24FV32KA304 family devices, sorted by function, is provided in Table 1-3.

Note: Table 1-1 provides the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams on pages 3, 4, 5, 6 and 7 of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

# TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 1/0 | Buffer            | Description                       |

| AN0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | Т   | ANA               |                                   |

| AN2      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               |                                   |

| AN3      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               |                                   |

| AN4      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ANA               |                                   |

| AN5      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I   | ANA               |                                   |

| AN6      | _                                | _                                 | _             | 25                     | 27             | _                                | _                                 | _             | 25                     | 27             | I   | ANA               |                                   |

| AN7      | _                                | _                                 | _             | 26                     | 28             | _                                | —                                 | —             | 26                     | 28             | I   | ANA               |                                   |

| AN8      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I   | ANA               |                                   |

| AN9      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ANA               |                                   |

| AN10     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA               |                                   |

| AN11     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | I   | ANA               |                                   |

| AN12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | Т   | ANA               |                                   |

| AN13     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | Т   | ANA               |                                   |

| AN14     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ANA               |                                   |

| AN15     | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA               |                                   |

| ASCL1    | _                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | I <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | _                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | l <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                                | 25            | 17                     | 18             | 20                               | 28                                | 25            | 17                     | 18             | 1   | ANA               | A/D Supply Pins                   |

| AVss     | 19                               | 27                                | 24            | 16                     | 17             | 19                               | 27                                | 24            | 16                     | 17             | Т   | ANA               |                                   |

| C1INA    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | 1   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | 1   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 1 Input D (-)          |

| C1OUT    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | —                 | Comparator 1 Output               |

| C2INA    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ANA               | Comparator 2 Input A (+)          |

| C2INB    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 2 Input B (-)          |

| C2INC    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | I   | ANA               | Comparator 2 Input C (+)          |

| C2IND    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | I   | ANA               | Comparator 2 Input D (-)          |

| C2OUT    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 16                                | 13            | 43                     | 47             | 0   | _                 | Comparator 2 Output               |

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

# 2.1 Basic Connection Requirements

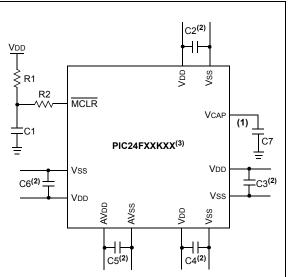

Getting started with the PIC24FV32KA304 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED

#### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

**<sup>3:</sup>** Some PIC24F K parts do not have a regulator.

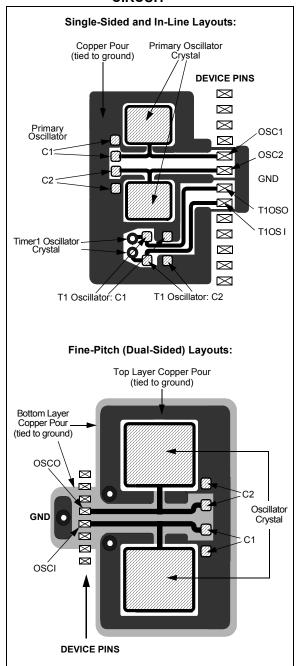

# 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

# FIGURE 2-5: SUGGESTED PLACEMENT

#### OF THE OSCILLATOR CIRCUIT

# 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Data EEPROM, refer to the *"PIC24F Family Reference Manual"*, Section 5. "Data EEPROM" (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFFh. The size of the data EEPROM is 256 words in the PIC24FV32KA304 family devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

## 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

| //Disable Interr | upts For 5 instruc | ctions |

|------------------|--------------------|--------|

| asm volatile (   | "disi #5");        |        |

| //Issue Unlock S | equence            |        |

| asm volatile (   | "mov #0x55, W0     | \n"    |

| "                | mov W0, NVMKEY     | \n"    |

| "                | mov #0xAA, W1      | \n"    |

| "                | mov W1, NVMKEY     | \n");  |

| // Perform Write | /Erase operations  |        |

| asm volatile (   | "bset NVMCON, #WR  | \n"    |

| "                | nop                | \n"    |

| "                | nop                | \n");  |

|                  |                    |        |

#### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the table read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and table read procedures (builtin\_tblrdl) from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

#### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

```

int attribute ((space(eedata))) eeData = 0x1234;

// Data read from EEPROM

int data;

/*_____

_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the read

_____

*/

unsigned int offset;

\ensuremath{//} Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData);

// Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

data = __builtin_tblrdl(offset);

// Initizlize lower word of address

// Write EEPROM data to write latch

```

#### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the Flash Configuration Word (FOSCSEL<2:0>); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

# 7.4 Deep Sleep BOR (DSBOR)

Deep Sleep BOR is a very low-power BOR circuitry, used when the device is in Deep Sleep mode. Due to low current consumption, accuracy may vary.

The DSBOR trip point is around 2.0V. DSBOR is enabled by configuring DSLPBOR (FDS<6>) = 1. DSLPBOR will re-arm the POR to ensure the device will reset if VDD drops below the POR threshold.

# 7.5 Brown-out Reset (BOR)

The PIC24FV32KA304 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

# 7.5.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the Brown-out Reset voltage level is still set by the BORV<1:0> Configuration bits; it cannot be changed in software.

# PIC24FV32KA304 FAMILY

#### REGISTER 8-29: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

|                    | R/W-1                                                                                                                                                              | R/W-0                                                                                                                                                                        | R/W-0                                                                                           | U-0               | R/W-1            | R/W-0           | R/W-0   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|

| _                  | CRCIP2                                                                                                                                                             | CRCIP1                                                                                                                                                                       | CRCIP0                                                                                          |                   | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| pit 15             |                                                                                                                                                                    |                                                                                                                                                                              |                                                                                                 |                   | •                | •               | bit     |

| U-0                | R/W-1                                                                                                                                                              | R/W-0                                                                                                                                                                        | R/W-0                                                                                           | U-0               | U-0              | U-0             | U-0     |

| 0-0                | U1ERIP2                                                                                                                                                            | U1ERIP1                                                                                                                                                                      | U1ERIP0                                                                                         | 0-0               | 0-0              | 0-0             | 0-0     |

| bit 7              |                                                                                                                                                                    | OTEINIT                                                                                                                                                                      | OTEINIO                                                                                         |                   |                  |                 | bit     |

| Legend:            |                                                                                                                                                                    |                                                                                                                                                                              |                                                                                                 |                   |                  |                 |         |

| R = Readabl        | le bit                                                                                                                                                             | W = Writable                                                                                                                                                                 | bit                                                                                             | U = Unimplem      | nented bit, read | l as '0'        |         |

| -n = Value at      | t POR                                                                                                                                                              | '1' = Bit is set                                                                                                                                                             |                                                                                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|                    | •                                                                                                                                                                  | pt is Priority 7(                                                                                                                                                            | inglicat phoney                                                                                 | interrupt)        |                  |                 |         |

|                    |                                                                                                                                                                    | pt is Priority 1<br>pt source is dis                                                                                                                                         | abled                                                                                           |                   |                  |                 |         |

| bit 11             | 000 <b>= Interru</b>                                                                                                                                               |                                                                                                                                                                              |                                                                                                 |                   |                  |                 |         |

| bit 11<br>bit 10-8 | 000 = Interru<br>Unimplemen<br>U2ERIP<2:0><br>111 = Interru                                                                                                        | ot source is dis<br>ted: Read as '<br>UART2 Error<br>ot is Priority 7 (                                                                                                      | <sup>0'</sup><br>r Interrupt Prior<br>highest priority                                          | -                 |                  |                 |         |

|                    | 000 = Interrup<br>Unimplemen<br>U2ERIP<2:0><br>111 = Interrup                                                                                                      | ot source is dis<br>ted: Read as f<br>UART2 Error<br>ot is Priority 7 (<br>ot is Priority 1                                                                                  | <sup>0'</sup><br>Interrupt Prior<br>highest priority<br>abled                                   | -                 |                  |                 |         |

| bit 10-8           | 000 = Interrup<br>Unimplemen<br>U2ERIP<2:0><br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interrup<br>001 = Interrup | et source is dis<br>ted: Read as (<br>): UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as (<br>): UART1 Error<br>pt is Priority 7 ( | 0'<br>Interrupt Prior<br>highest priority<br>abled<br>0'<br>Interrupt Prior<br>highest priority | interrupt)        |                  |                 |         |

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The maximum open-drain voltage allowed is the same as the maximum  $V_{\text{IH}}$  specification.

# 11.2 Configuring Analog Port Pins

The use of the ANS and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 ANALOG SELECTION REGISTERS

I/O pins with shared analog functionality, such as A/D inputs and comparator inputs, must have their digital inputs shut off when analog functionality is used. Note that analog functionality includes an analog voltage being applied to the pin externally.

To allow for analog control, the ANSx registers are provided. There is one ANS register for each port (ANSA, ANSB and ANSC). Within each ANSx register, there is a bit for each pin that shares analog functionality with the digital I/O functionality.

If a particular pin does not have an analog function, that bit is unimplemented. See Register 11-1 to Register 11-3 for implementation.

# REGISTER 11-1: ANSA: ANALOG SELECTION (PORTA)

| U-0           | U-0   | U-0              | U-0 | U-0                                     | U-0   | U-0   | U-0   |  |

|---------------|-------|------------------|-----|-----------------------------------------|-------|-------|-------|--|

| —             | —     | —                | —   | —                                       | —     | —     | —     |  |

| bit 15        |       |                  |     |                                         |       |       | bit 8 |  |

|               |       |                  |     |                                         |       |       |       |  |

| U-0           | U-0   | U-0              | U-0 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |  |

|               | —     | —                | —   | ANSA3                                   | ANSA2 | ANSA1 | ANSA0 |  |

| bit 7         |       |                  |     |                                         |       |       | bit 0 |  |

|               |       |                  |     |                                         |       |       |       |  |

| Legend:       |       |                  |     |                                         |       |       |       |  |

| R = Readable  | e bit | W = Writable I   | bit | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-4 Unimplemented: Read as '0'

bit 3-0 ANSA<3:0>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

# PIC24FV32KA304 FAMILY

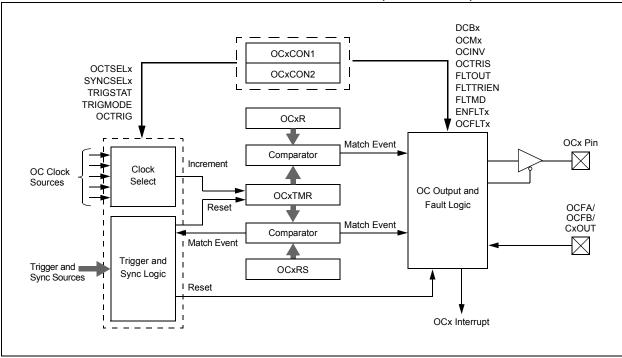

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

### 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse, based on the desired pulse width and the time to the rising edge of the pulse.

- 2. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure the trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no Sync/trigger source).

- 5. Select the time base source with the OCTSEL<2:0> bits. If the desired clock source is running, set the OCTSEL<2:0> bits before the output compare module is enabled for proper synchronization with the desired clock source. If necessary, set the TON bit for the selected timer which enables the compare time base to count. Synchronous mode operation starts as soon as the synchronization source is enabled; Trigger mode operation starts after a trigger source event occurs.

- 6. Set the OCM<2:0> bits for the appropriate compare operation ('0xx').

For 32-bit cascaded operation, these steps are also necessary:

- Set the OC32 bits for both registers (OCyCON2<8> and (OCxCON2<8>). Enable the even numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2), so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCy.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGSTAT (OCxCON2<6>) and SYNCSELx (OCxCON2<4:0>) bits.

- Configure the desired Compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx.

Depending on the output mode selected, the module holds the OCx pin in its default state and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes and after each OCxRS match in Double Compare modes.

Single-shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Serial Peripheral Interface, refer to the *"PIC24F Family Reference Manual"*, Section 23. *"Serial Peripheral Interface (SPI)"* (DS39699).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial data EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

**Note:** Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPI1BUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- SDI1: Serial Data Input

- SDO1: Serial Data Output

- · SCK1: Shift Clock Input or Output

- SS1: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SS1}$  is not used. In the 2-pin mode, both SDO1 and  $\overline{SS1}$  are not used.

Block diagrams of the module, in Standard and Enhanced Buffer modes, are shown in Figure 16-1 and Figure 16-2.

The devices of the PIC24FV32KA304 family offer two SPI modules on a device.

Note: In this section, the SPI modules are referred to as SPIx. Special Function Registers (SFRs) will follow a similar notation. For example, SPI1CON1 or SPI1CON2 refers to the control register for the SPI1 module. To set up the SPI1 module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 1.

- 3. Clear the SPIROV bit (SPI1STAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

- 5. Write the data to be transmitted to the SPI1BUF register. Transmission (and reception) will start as soon as data is written to the SPI1BUF register.

To set up the SPI1 module for the Standard Slave mode of operation:

- 1. Clear the SPI1BUF register.

- 2. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit (SPI1CON1<7>) must be set to enable the SS1 pin.

- 6. Clear the SPIROV bit (SPI1STAT<6>).

- 7. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

# 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

# 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 18.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 18.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

# 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month         | Day | Hours | Minutes  | Seconds |

|-------------------------------------------------|-----------------------|---------------|-----|-------|----------|---------|

| 0000 - Every half second<br>0001 - Every second |                       |               |     |       | •        | •       |

| 0010 - Every 10 seconds                         |                       |               |     |       | •        | s       |

| 0011 - Every minute                             |                       |               |     |       |          | s s     |

| 0100 - Every 10 minutes                         |                       |               |     |       | <b>m</b> | ss      |

| 0101 - Every hour                               |                       |               |     |       | mm       | ss      |

| 0110 - Every day                                |                       |               |     | hh    | mm       | ss      |

| 0111 - Every week                               | d                     |               |     | hh    | mm       | ss      |

| 1000 - Every month                              |                       |               | d d | hh    | mm       | ss      |

| 1001 - Every year <sup>(1)</sup>                |                       | <b>m m</b> /  | d d | hh    | mm       | ss      |

| Note 1: Annually, except whe                    | n configured fo       | r February 29 |     |       |          |         |

# 19.5 POWER CONTROL

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current low-power mode (Sleep, Deep Sleep, etc.).

To enable this feature, the RTCC must be enabled (RTCEN = 1), the PWCEN register bit must be set and the RTCC pin must be driving the PWC control signal (RTCOE = 1 and RTCOUT<1:0> = 11).

The polarity of the PWC control signal may be chosen using the PWCPOL register bit. Active-low or active-high may be used with the appropriate external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin. This setting is able to drive the GND pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity. To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs and/or select band gap reference inputs (ANS<12:10>, ANS<5:0>).

- b) Select voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select the interrupt rate (AD1CON2<6:2>).

- g) Turn on the A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

To perform an A/D sample and conversion using Threshold Detect scanning:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs (ANS<12:10>, ANS<5,0>).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4>, AD1CON3<12:8>).

- Select how the conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select the interrupt rate (AD1CON2<6:2>).

- 2. Configure the threshold compare channels:

- a) Enable auto-scan ASEN bit (AD1CON5<15>).

- b) Select the Compare mode, "Greater Than, Less Than or Windowed" – CMx bits (AD1CON5<1:0>).

- c) Select the threshold compare channels to be scanned (ADCSSH, ADCSSL).

- d) If the CTMU is required as a current source for a threshold compare channel, enable the corresponding CTMU channel (ADCCTMUENH, ADCCTMUENL).

- e) Write the threshold values into the corresponding ADC1BUFn registers.

- f) Turn on the A/D module (AD1CON1<15>).

Note: If performing an A/D sample and conversion using Threshold Detect in Sleep Mode, the RC A/D clock source must be selected before entering into Sleep mode.

- 3. Configure the A/D interrupt (OPTIONAL):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

# 27.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 27.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 27.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 27.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# PIC24FV32KA304 FAMILY

| DC CHARAG                                         | CTERISTICS     | Standard O             | 4F32KA3XX<br>4FV32KA3XX<br>strial<br>ended |       |        |            |                              |  |  |  |

|---------------------------------------------------|----------------|------------------------|--------------------------------------------|-------|--------|------------|------------------------------|--|--|--|

| Parameter<br>No.                                  | Device         | Typical <sup>(1)</sup> | Max                                        | Units |        | Conditions |                              |  |  |  |

| Module Differential Current (∆IPD) <sup>(3)</sup> |                |                        |                                            |       |        |            |                              |  |  |  |

| DC71                                              | PIC24FV32KA3XX | 0.50                   |                                            | μA    | -40°C  | 2.0V       |                              |  |  |  |

|                                                   |                | 0.70                   | 1.5                                        | μA    | +85°C  | 5.0V       |                              |  |  |  |

|                                                   |                | —                      | 1.5                                        | μA    | +125°C | 5.0V       | Watchdog Timer<br>Current:   |  |  |  |

|                                                   | PIC24F32KA3XX  | 0.50                   |                                            | μA    | -40°C  | 1.8V       | ∆lwDT <sup>(4)</sup>         |  |  |  |

|                                                   |                | 0.70                   | 1.5                                        | μA    | +85°C  | 3.3V       |                              |  |  |  |

|                                                   |                | —                      | 1.5                                        | μA    | +125°C | 3.3V       |                              |  |  |  |

| DC72                                              | PIC24FV32KA3XX | 0.80                   |                                            | μA    | -40°C  | 2.0V       |                              |  |  |  |

|                                                   |                | 1.50                   | 2.0                                        | μA    | +85°C  | 5.0V       | 32 kHz Crystal with RTCC,    |  |  |  |

|                                                   |                | —                      | 2.0                                        | μA    | +125°C | 5.0V       | DSWDT or Timer1:             |  |  |  |

|                                                   | PIC24F32KA3XX  | 0.70                   | —                                          | μA    | -40°C  | 1.8V       | ∆lsosc                       |  |  |  |

|                                                   |                | 1.0                    | 1.5                                        | μA    | +85°C  | 3.3V       | (SOSCSEL = 0) <sup>(5)</sup> |  |  |  |

|                                                   |                | —                      | 1.5                                        | μA    | +125°C | 3.3V       |                              |  |  |  |

| DC75                                              | PIC24FV32KA3XX | 5.4                    | —                                          | μA    | -40°C  | 2.0V       |                              |  |  |  |

|                                                   |                | 8.1                    | 14.0                                       | μA    | +85°C  | 5.0V       |                              |  |  |  |

|                                                   |                | —                      | 14.0                                       | μA    | +125°C | 5.0V       | ∆IHLVD <sup>(4)</sup>        |  |  |  |

|                                                   | PIC24F32KA3XX  | 4.9                    | _                                          | μA    | -40°C  | 1.8V       |                              |  |  |  |

|                                                   |                | 7.5                    | 14.0                                       | μA    | +85°C  | 3.3V       |                              |  |  |  |

|                                                   |                | _                      | 14.0                                       | μA    | +125°C | 3.3V       |                              |  |  |  |

| DC76                                              | PIC24FV32KA3XX | 5.6                    | _                                          | μA    | -40°C  | 2.0V       |                              |  |  |  |

|                                                   |                | 6.5                    | 11.2                                       | μA    | -40°C  | 5.0V       |                              |  |  |  |

|                                                   |                | —                      | 11.2                                       | μA    | +125°C | 5.0V       | ∆lbor <sup>(4)</sup>         |  |  |  |

|                                                   | PIC24F32KA3XX  | 5.6                    | —                                          | μA    | -40°C  | 1.8V       | ΔΙΒΟΚ' '                     |  |  |  |

|                                                   |                | 6.0                    | 11.2                                       | μA    | +85°C  | 3.3V       |                              |  |  |  |

|                                                   |                | —                      | 11.2                                       | μA    | +125°C | 3.3V       |                              |  |  |  |

#### TABLE 29-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

Legend: Unshaded rows represent PIC24F32KA3XX devices and shaded rows represent PIC24FV32KA3XX devices.

Note 1: Data in the Typical column is at 3.3V, +25°C (PIC24F32KA3XX) or 5.0V, +25°C (PIC24FV32KA3XX) unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and set low, PMSLP is set to '0' and WDT, etc., are all switched off.

3: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

4: This current applies to Sleep only.

5: This current applies to Sleep and Deep Sleep.

6: This current applies to Deep Sleep only.

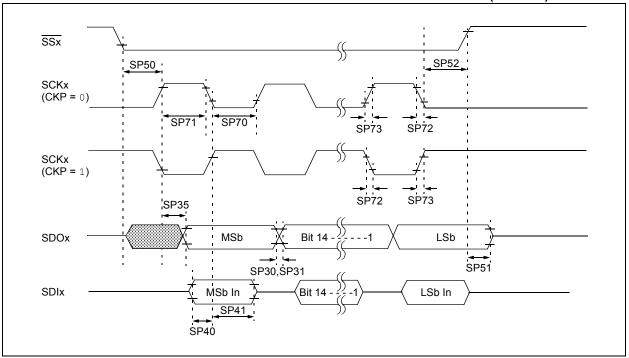

### FIGURE 29-20: SPIX MODULE SLAVE MODE TIMING CHARACTERISTICS (CKE = 0)

#### TABLE 29-38: SPIX MODULE SLAVE MODE TIMING REQUIREMENTS (CKE = 0)

| АС СН        | ARACTERIS             | TICS                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     | C for Industrial |            |

|--------------|-----------------------|----------------------------------------------------|-------------------------------------------------------|--------------------|-----|------------------|------------|

| Param<br>No. | Symbol                | Characteristic                                     | Min                                                   | Typ <sup>(1)</sup> | Мах | Units            | Conditions |

| SP70         | TscL                  | SCKx Input Low Time                                | 30                                                    |                    | _   | ns               |            |

| SP71         | TscH                  | SCKx Input High Time                               | 30                                                    | _                  | _   | ns               |            |

| SP72         | TscF                  | SCKx Input Fall Time <sup>(2)</sup>                |                                                       | 10                 | 25  | ns               |            |

| SP73         | TscR                  | SCKx Input Rise Time <sup>(2)</sup>                |                                                       | 10                 | 25  | ns               |            |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(2)</sup>          |                                                       | 10                 | 25  | ns               |            |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(2)</sup>          |                                                       | 10                 | 25  | ns               |            |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge          | —                                                     | —                  | 30  | ns               |            |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input<br>to SCKx Edge      | 20                                                    | —                  | —   | ns               |            |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge       | 20                                                    | _                  | _   | ns               |            |

| SP50         | TssL2scH,<br>TssL2scL | SSx to SCKx ↑ or SCKx Input                        | 120                                                   | —                  | _   | ns               |            |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output High-Impedance <sup>(3)</sup> | 10                                                    | —                  | 50  | ns               |            |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                | 1.5 Tcy + 40                                          | —                  | —   | ns               |            |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The minimum clock period for SCKx is 100 ns; therefore, the clock generated in Master mode must not violate this specification.

3: This assumes a 50 pF load on all SPIx pins.

# PIC24FV32KA304 FAMILY

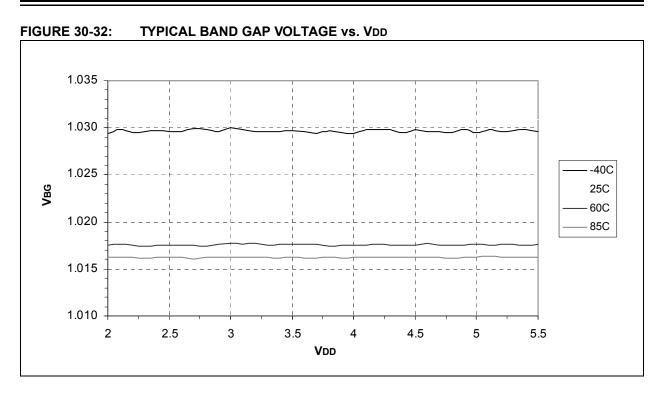

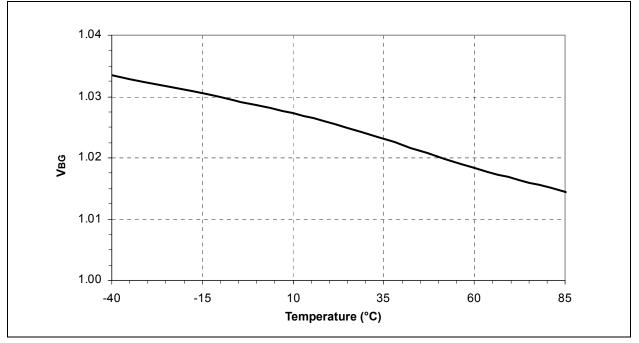

FIGURE 30-33: TYPICAL BAND GAP VOLTAGE vs. TEMPERATURE ( $2.0V \le VDD \le 5.5V$ )

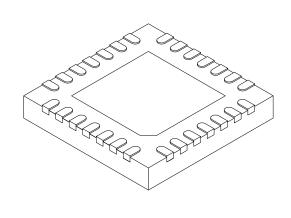

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units MILLIMETERS |      |          |      |  |

|-------------------------|-------------------|------|----------|------|--|

| Dimension               | Limits            | MIN  | NOM      | MAX  |  |

| Number of Pins          | N                 |      | 28       |      |  |

| Pitch                   | е                 |      | 0.65 BSC |      |  |

| Overall Height          | A                 | 0.80 | 0.90     | 1.00 |  |

| Standoff                | A1                | 0.00 | 0.02     | 0.05 |  |

| Terminal Thickness      | A3                |      | 0.20 REF |      |  |

| Overall Width           | E                 |      | 6.00 BSC |      |  |

| Exposed Pad Width       | E2                | 3.65 | 3.70     | 4.20 |  |

| Overall Length          | D                 |      | 6.00 BSC |      |  |

| Exposed Pad Length      | D2                | 3.65 | 3.70     | 4.20 |  |

| Terminal Width          | b                 | 0.23 | 0.30     | 0.35 |  |

| Terminal Length         | L                 | 0.50 | 0.55     | 0.70 |  |

| Terminal-to-Exposed Pad | K                 | 0.20 | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2