#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 39                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka304-e-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 23  |

| 3.0   | СРИ                                                         |     |

| 4.0   | Memory Organization                                         | 35  |

| 5.0   | Flash Program Memory                                        | 57  |

| 6.0   | Data EEPROM Memory                                          | 63  |

| 7.0   | Resets                                                      | 69  |

| 8.0   | Interrupt Controller                                        |     |

| 9.0   | Oscillator Configuration                                    | 115 |

| 10.0  | Power-Saving Features                                       | 125 |

| 11.0  | I/O Ports                                                   | 135 |

| 12.0  | Timer1                                                      | 139 |

| 13.0  | Timer2/3 and Timer4/5                                       | 141 |

| 14.0  | Input Capture with Dedicated Timers                         | 147 |

| 15.0  | Output Compare with Dedicated Timers                        | 151 |

| 16.0  | Serial Peripheral Interface (SPI)                           |     |

| 17.0  |                                                             |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)          | 177 |

| 19.0  | Real-Time Clock and Calendar (RTCC)                         |     |

| 20.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator | 199 |

| 21.0  | High/Low-Voltage Detect (HLVD)                              | 205 |

| 22.0  | 12-Bit A/D Converter with Threshold Detect                  |     |

| 23.0  | Comparator Module                                           | 225 |

| 24.0  | Comparator Voltage Reference                                | 229 |

| 25.0  | Charge Time Measurement Unit (CTMU)                         |     |

| 26.0  | Special Features                                            | 239 |

| 27.0  | Development Support                                         | 251 |

|       | Instruction Set Summary                                     |     |

|       | Electrical Characteristics                                  |     |

| 30.0  | DC and AC Characteristics Graphs and Tables                 | 295 |

| 31.0  | Packaging Information                                       | 325 |

| Appe  | endix A: Revision History                                   | 351 |

| Index | κ                                                           | 353 |

| The I | Microchip Web Site                                          | 359 |

|       | omer Change Notification Service                            |     |

| Cust  | omer Support                                                | 359 |

| Read  | der Response                                                | 360 |

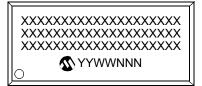

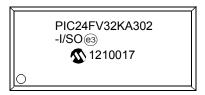

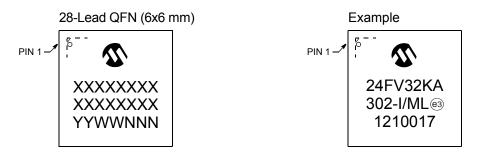

| Prod  | uct Identification System                                   |     |

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

#### 1.1.4 EASY MIGRATION

Regardless of the memory size, all the devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex.

### 1.2 Other Special Features

- Communications: The PIC24FV32KA304 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an I<sup>2</sup>C<sup>™</sup> module that supports both the Master and Slave modes of operation. It also comprises UARTs with built-in IrDA<sup>®</sup> encoders/decoders and an SPI module.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- **12-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV32KA304 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation.

#### 1.3 Details on Individual Family Members

Devices in the PIC24FV32KA304 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are different from each other in four ways:

- Flash program memory (16 Kbytes for PIC24FV16KA devices, 32 Kbytes for PIC24FV32KA devices).

- Available I/O pins and ports (18 pins on two ports for 20-pin devices, 22 pins on two ports for 28-pin devices and 38 pins on three ports for 44/48-pin devices).

- 3. Alternate SCLx and SDAx pins are available only in 28-pin, 44-pin and 48-pin devices and not in 20-pin devices.

- 4. Members of the PIC24FV32KA301 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV32KA304), accommodate an operating VDD range of 2.0V to 5.5V, and have an on-board Voltage Regulator that powers the core. Peripherals operate at VDD. Standard devices, designated by "F" (such as PIC24F32KA304), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

All other features for devices in this family are identical; these are summarized in Table 1-1.

A list of the pin features available on the PIC24FV32KA304 family devices, sorted by function, is provided in Table 1-3.

Note: Table 1-1 provides the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams on pages 3, 4, 5, 6 and 7 of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

#### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                            |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    | •                      |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| C3INA    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | Ι   | ANA    | Comparator 3 Input A (+)   |

| C3INB    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator 3 Input B (-)   |

| C3INC    | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | 1   | ANA    | Comparator 3 Input C (+)   |

| C3IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | 1   | ANA    | Comparator 3 Input D (-)   |

| C3OUT    | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | 0   | —      | Comparator 3 Output        |

| CLK I    | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ANA    | Main Clock Input           |

| CLKO     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | 0   | _      | System Clock Output        |

| CN0      | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I   | ST     | Interrupt-on-Change Inputs |

| CN1      | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ST     |                            |

| CN2      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ST     |                            |

| CN3      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ST     |                            |

| CN4      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ST     |                            |

| CN5      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     |                            |

| CN6      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ST     |                            |

| CN7      | _                                | 7                                 | 4             | 24                     | 26             |                                  | 7                                 | 4             | 24                     | 26             | I   | ST     |                            |

| CN8      | 14                               | 20                                | 17            | 7                      | 7              |                                  |                                   |               | _                      |                | I   | ST     |                            |

| CN9      |                                  | 19                                | 16            | 6                      | 6              |                                  | 19                                | 16            | 6                      | 6              | I   | ST     |                            |

| CN10     |                                  | —                                 | —             | 27                     | 29             |                                  |                                   |               | 27                     | 29             | I   | ST     |                            |

| CN11     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 1   | ST     |                            |

| CN12     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 1   | ST     |                            |

| CN13     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | 1   | ST     |                            |

| CN14     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | 1   | ST     |                            |

| CN15     |                                  | 22                                | 19            | 9                      | 10             |                                  | 22                                | 19            | 9                      | 10             | Ι   | ST     | ]                          |

| CN16     |                                  | 21                                | 18            | 8                      | 9              |                                  | 21                                | 18            | 8                      | 9              | Ι   | ST     |                            |

| CN17     |                                  | —                                 | —             | 3                      | 3              |                                  | _                                 | _             | 3                      | 3              | 1   | ST     |                            |

| CN18     | _                                | _                                 | _             | 2                      | 2              | —                                | _                                 | _             | 2                      | 2              | Ι   | ST     | ]                          |

| CN19     |                                  | _                                 | _             | 5                      | 5              | —                                | _                                 |               | 5                      | 5              | 1   | ST     | ]                          |

| CN20     |                                  | _                                 | —             | 4                      | 4              | _                                |                                   |               | 4                      | 4              | I   | ST     |                            |

| CN21     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I   | ST     | ]                          |

| CN22     | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | 1   | ST     |                            |

#### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CN23     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs                  |

| CN24     |                                  | 15                                | 12            | 42                     | 46             | -                                | 15                                | 12            | 42                     | 46             | 1   | ST     |                                             |

| CN25     |                                  | _                                 | _             | 37                     | 40             | -                                |                                   |               | 37                     | 40             | 1   | ST     |                                             |

| CN26     |                                  | _                                 | _             | 38                     | 41             |                                  |                                   |               | 38                     | 41             | I   | ST     |                                             |

| CN27     |                                  | 14                                | 11            | 41                     | 45             |                                  | 14                                | 11            | 41                     | 45             | I   | ST     |                                             |

| CN28     |                                  | _                                 | _             | 36                     | 39             |                                  |                                   |               | 36                     | 39             | I   | ST     |                                             |

| CN29     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ST     |                                             |

| CN30     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ST     |                                             |

| CN31     |                                  | _                                 | _             | 26                     | 28             | —                                | _                                 | —             | 26                     | 28             | I   | ST     |                                             |

| CN32     |                                  | _                                 | —             | 25                     | 27             | —                                | —                                 | —             | 25                     | 27             | 1   | ST     |                                             |

| CN33     |                                  | _                                 | —             | 32                     | 35             | —                                | —                                 | —             | 32                     | 35             | 1   | ST     |                                             |

| CN34     |                                  | _                                 | —             | 35                     | 38             | —                                | —                                 | —             | 35                     | 38             | I   | ST     |                                             |

| CN35     |                                  | _                                 | _             | 12                     | 13             | —                                | _                                 | —             | 12                     | 13             | I   | ST     |                                             |

| CN36     |                                  | _                                 | _             | 13                     | 14             | —                                | _                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CVREF    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA    | Comparator Reference Positive Input Voltage |

| CVREF-   | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA    | Comparator Reference Negative Input Voltage |

| CTCMP    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input                       |

| CTED1    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 2                                 | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     |                                             |

| CTED3    | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I   | ST     |                                             |

| CTED4    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 1   | ST     |                                             |

| CTED5    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ST     |                                             |

| CTED6    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     |                                             |

| CTED7    | _                                | _                                 | _             | 5                      | 5              | _                                | —                                 | _             | 5                      | 5              | I   | ST     |                                             |

| CTED8    | _                                | _                                 | —             | 13                     | 14             | —                                | —                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CTED9    | _                                | 22                                | 19            | 9                      | 10             | —                                | 22                                | 19            | 9                      | 10             | I   | ST     |                                             |

| CTED10   | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I   | ST     | ]                                           |

| CTED11   | _                                | 21                                | 18            | 8                      | 9              | —                                | 21                                | 18            | 8                      | 9              | I   | ST     | ]                                           |

| CTED12   | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | ]                                           |

| CTED13   | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | 1   | ST     | 1                                           |

#### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                  |                                 |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|------------------|---------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |                  |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer           | Description                     |

| RC0      | _                                | _                                 | _             | 25                     | 27             | _                                | —                                 | _             | 25                     | 27             | I/O | ST               | PORTC Pins                      |

| RC1      | _                                | _                                 | _             | 26                     | 28             | _                                | _                                 | _             | 26                     | 28             | I/O | ST               |                                 |

| RC2      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I/O | ST               |                                 |

| RC3      | _                                | _                                 |               | 36                     | 39             |                                  | _                                 |               | 36                     | 39             | I/O | ST               |                                 |

| RC4      | _                                | _                                 | _             | 37                     | 40             | _                                | _                                 | _             | 37                     | 40             | I/O | ST               |                                 |

| RC5      | _                                | _                                 | _             | 38                     | 41             | _                                | _                                 | _             | 38                     | 41             | I/O | ST               |                                 |

| RC6      | _                                | _                                 | _             | 2                      | 2              | _                                | _                                 | _             | 2                      | 2              | I/O | ST               |                                 |

| RC7      | _                                | _                                 | _             | 3                      | 3              | _                                | _                                 | _             | 3                      | 3              | I/O | ST               |                                 |

| RC8      | _                                | _                                 | _             | 4                      | 4              | _                                | _                                 | _             | 4                      | 4              | I/O | ST               |                                 |

| RC9      | _                                | _                                 | _             | 5                      | 5              | _                                | _                                 | _             | 5                      | 5              | I/O | ST               |                                 |

| REFO     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 0   | _                | Reference Clock Output          |

| RTCC     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | _                | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                                | 19            | 9                      | 10             | 15                               | 22                                | 19            | 9                      | 10             | I/O | ST               | SPI1 Serial Input/Output Clock  |

| SCK2     | 2                                | 14                                | 11            | 38                     | 41             | 2                                | 14                                | 11            | 38                     | 41             | I/O | ST               | SPI2 Serial Input/Output Clock  |

| SCL1     | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I/O | l <sup>2</sup> C | I2C1 Clock Input/Output         |

| SCL2     | 18                               | 7                                 | 4             | 24                     | 26             | 18                               | 7                                 | 4             | 24                     | 26             | I/O | l <sup>2</sup> C | I2C2 Clock Input/Output         |

| SCLKI    | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I   | ST               | Digital Secondary Clock Input   |

| SDA1     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I/O | l <sup>2</sup> C | I2C1 Data Input/Output          |

| SDA2     | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I/O | l <sup>2</sup> C | I2C2 Data Input/Output          |

| SDI1     | 17                               | 21                                | 18            | 8                      | 9              | 17                               | 21                                | 18            | 8                      | 9              | I   | ST               | SPI1 Serial Data Input          |

| SDI2     | 4                                | 19                                | 16            | 36                     | 39             | 4                                | 19                                | 16            | 36                     | 39             | I   | ST               | SPI2 Serial Data Input          |

| SDO1     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | 0   | _                | SPI1 Serial Data Output         |

| SDO2     | 3                                | 15                                | 12            | 37                     | 40             | 3                                | 15                                | 12            | 37                     | 40             | 0   | —                | SPI2 Serial Data Output         |

| SOSCI    | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA              | Secondary Oscillator Input      |

| SOSCO    | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | 0   | ANA              | Secondary Oscillator Output     |

| SS1      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 0   | _                | SPI1 Slave Select               |

| SS2      | 15                               | 23                                | 20            | 35                     | 38             | 15                               | 23                                | 20            | 35                     | 38             | 0   | _                | SPI2 Slave Select               |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     |     | IPL3 <sup>(1)</sup> | PSV   | —   | _     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/0 | Clearable bit                      |                    |  |  |  |  |  |

|-------------------|---------------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in data space                                                                                    |

|          | 0 = Program space is not visible in data space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### TABLE 4-3: CPU CORE REGISTERS MAP

| IADEE -   | т-∪.          |        |        |          |         |        |        |       |       |       |       |       |       |       |       |       |       |               |

|-----------|---------------|--------|--------|----------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Start<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| WREG0     | 0000          |        |        |          |         |        |        |       | WF    | REG0  |       |       |       |       |       |       |       | 0000          |

| WREG1     | 0002          |        |        |          |         |        |        |       | WF    | REG1  |       |       |       |       |       |       |       | 0000          |

| WREG2     | 0004          |        |        |          |         |        |        |       | WF    | REG2  |       |       |       |       |       |       |       | 0000          |

| WREG3     | 0006          |        |        |          |         |        |        |       | WF    | REG3  |       |       |       |       |       |       |       | 0000          |

| WREG4     | 0008          |        |        |          |         |        |        |       | WF    | REG4  |       |       |       |       |       |       |       | 0000          |

| WREG5     | 000A          |        |        |          |         |        |        |       | WF    | REG5  |       |       |       |       |       |       |       | 0000          |

| WREG6     | 000C          |        |        |          |         |        |        |       | WF    | REG6  |       |       |       |       |       |       |       | 0000          |

| WREG7     | 000E          |        |        |          |         |        |        |       | WF    | REG7  |       |       |       |       |       |       |       | 0000          |

| WREG8     | 0010          |        |        |          |         |        |        |       | WF    | REG8  |       |       |       |       |       |       |       | 0000          |

| WREG9     | 0012          |        |        |          | WREG9 C |        |        |       |       |       |       |       |       |       |       | 0000  |       |               |

| WREG10    | 0014          |        |        |          |         |        |        |       |       |       |       |       |       |       |       |       | 0000  |               |

| WREG11    | 0016          |        |        |          |         |        |        |       | WR    | EG11  |       |       |       |       |       |       |       | 0000          |

| WREG12    | 0018          |        |        |          |         |        |        |       | WR    | EG12  |       |       |       |       |       |       |       | 0000          |

| WREG13    | 001A          |        |        |          |         |        |        |       | WR    | EG13  |       |       |       |       |       |       |       | 0000          |

| WREG14    | 001C          |        |        |          |         |        |        |       | WR    | EG14  |       |       |       |       |       |       |       | 0000          |

| WREG15    | 001E          |        |        |          |         |        |        |       | WR    | EG15  |       |       |       |       |       |       |       | 0000          |

| SPLIM     | 0020          |        |        |          |         |        |        |       | SF    | PLIM  |       |       |       |       |       |       |       | XXXX          |

| PCL       | 002E          |        |        |          |         |        |        |       | F     | PCL   |       |       |       |       |       |       |       | 0000          |

| PCH       | 0030          | _      | _      | _        | _       | _      | _      | _     | _     | _     |       |       |       | PCH   |       |       |       | 0000          |

| TBLPAG    | 0032          |        | _      |          | —       | —      |        | —     | —     |       |       |       | TBI   | _PAG  |       |       |       | 0000          |

| PSVPAG    | 0034          |        |        | PSVPAG   |         |        |        |       |       |       |       |       |       |       |       | 0000  |       |               |

| RCOUNT    | 0036          |        |        | RCOUNT x |         |        |        |       |       |       |       |       |       |       |       |       | XXXXX |               |

| SR        | 0042          | _      | _      |          | -       | -      |        | _     | DC    | IPL2  | IPL1  | IPL0  | RA    | Ν     | OV    | Z     | С     | 0000          |

| CORCON    | 0044          |        | _      | -        | _       | _      |        | _     | —     | —     | _     | _     | -     | IPL3  | PSV   | —     | _     | 0000          |

| DISICNT   | 0052          |        | _      |          |         |        |        |       |       | DISIC | NT    |       |       |       |       |       |       | XXXX          |

|           |               |        |        |          |         |        |        |       |       |       |       |       |       |       |       |       |       |               |

DS39995D-page 39

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-21: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|----------|--------|---------|---------|---------|---------|---------|--------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1      | 0640 | CRCEN  | —        | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0  | CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | —     | —     | —     | 0000          |

| CRCCON2      | 0642 | _      | _        | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0 | _      | _      | —       | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL      | 0644 | X15    | X14      | X13    | X12     | X11     | X10     | X9      | X8      | X7     | X6     | X5      | X4    | X3      | X2    | X1    | _     | 0000          |

| CRCXORH      | 0646 | X31    | X30      | X29    | X28     | X27     | X26     | X25     | X24     | X23    | X22    | X21     | X20   | X19     | X18   | X17   | X16   | 0000          |

| CRCDATL      | 0648 |        |          |        |         |         |         |         | CRCDA   | TL     |        |         |       |         |       |       |       | XXXX          |

| CRCDATH      | 064A |        |          |        |         |         |         |         | CRCDA   | ГН     |        |         |       |         |       |       |       | XXXX          |

| CRCWDATL     | 064C |        | CRCWDATL |        |         |         |         |         |         |        |        |         |       |         | XXXX  |       |       |               |

| CRCWDATH     | 064E |        | CRCWDATH |        |         |         |         |         |         |        |        |         |       |         |       | XXXX  |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: CLOCK CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | RETEN  | —      | DPSLP  | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3140          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   | _      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | _      | HLSIDL | _      | _      | _      | _      | -      | VDIR    | BGVST | IRVST  | —     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses and by type of Reset.

#### TABLE 4-23: DEEP SLEEP REGISTER MAP

| File Name             | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1 | Bit 0   | All<br>Resets |

|-----------------------|------|--------|-----------|--------|--------|--------|--------|-------|----------|--------|-------|-------|-------|--------|---------|-------|---------|---------------|

| DSCON                 | 0758 | DSEN   | _         | —      | —      | _      | _      | _     | RTCCWDIS | _      | —     | —     |       | —      | ULPWDIS | DSBOR | RELEASE | 0000          |

| DSWAKE                | 075A | _      | _         | _      | _      | -      | -      | _     | DSINT0   | DSFLT  | _     | _     | DSWDT | DSRTCC | DSMCLR  | _     | DSPOR   | 0000          |

| DSGPR0 <sup>(1)</sup> | 075C |        | DSGPR0 00 |        |        |        |        |       | 0000     |        |       |       |       |        |         |       |         |               |

| DSGPR1 <sup>(1)</sup> | 075E |        |           |        |        |        |        |       |          | DSGPR1 |       |       |       |        |         |       |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Deep Sleep registers, DSGPR0 and DSGPR1, are only reset on a VDD POR event.

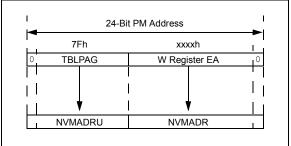

#### 6.3 NVM Address Register

As with Flash program memory, the NVM Address registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space. Instead, they directly capture the EA<23:0> of the last table write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", are unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

#### 6.4 Data EEPROM Operations

The EEPROM block is accessed using table read and write operations similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

Note 1: Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.

2: The C30 C compiler includes library procedures to automatically perform the table read and table write operations, manage the Table Pointer and write buffers, and unlock and initiate memory write sequences. This eliminates the need to create assembler macros or time critical routines in C for each application.

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

| R/W-0          | R/W-0                                 | R/W-0                                    | R/W-0          | R/W-0             | U-0              | R/W-0           | U-0     |  |  |

|----------------|---------------------------------------|------------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|

| U2TXIE         | U2RXIE                                | INT2IE                                   | T5IE           | T4IE              |                  | OC3IE           |         |  |  |

| bit 15         | 1                                     |                                          |                |                   |                  |                 | bit 8   |  |  |

|                |                                       |                                          |                |                   |                  |                 |         |  |  |

| U-0            | U-0                                   | U-0                                      | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |

| _              | —                                     |                                          | INT1IE         | CNIE              | CMIE             | MI2C1IE         | SI2C1IE |  |  |

| bit 7          |                                       |                                          |                |                   |                  |                 | bit (   |  |  |

| Legend:        |                                       |                                          |                |                   |                  |                 |         |  |  |

| R = Readable   | e bit                                 | W = Writable                             | bit            | U = Unimplem      | nented bit, read | d as '0'        |         |  |  |

| -n = Value at  | POR                                   | '1' = Bit is set                         |                | '0' = Bit is clea |                  | x = Bit is unkn | own     |  |  |

|                |                                       |                                          |                |                   |                  |                 |         |  |  |

| bit 15         | U2TXIE: UAR                           | RT2 Transmitter                          | Interrupt Ena  | ble bit           |                  |                 |         |  |  |

|                |                                       | equest is enab                           |                |                   |                  |                 |         |  |  |

|                | •                                     | equest is not e                          |                |                   |                  |                 |         |  |  |

| bit 14         |                                       | RT2 Receiver Ir                          | •              | e bit             |                  |                 |         |  |  |

|                | •                                     | equest is enab                           |                |                   |                  |                 |         |  |  |

| <b>h</b> it 40 |                                       | equest is not e                          |                |                   |                  |                 |         |  |  |

| bit 13         |                                       | nal Interrupt 2<br>equest is enab        |                |                   |                  |                 |         |  |  |

|                |                                       | equest is enab                           |                |                   |                  |                 |         |  |  |

| bit 12         |                                       | Interrupt Enabl                          |                |                   |                  |                 |         |  |  |

|                |                                       | equest is enab                           |                |                   |                  |                 |         |  |  |

|                |                                       | equest is not e                          |                |                   |                  |                 |         |  |  |

| bit 11         | T4IE: Timer4                          | Interrupt Enabl                          | e bit          |                   |                  |                 |         |  |  |

|                | •                                     | equest is enab                           |                |                   |                  |                 |         |  |  |

|                | -                                     | equest is not e                          |                |                   |                  |                 |         |  |  |

| bit 10         | -                                     | ted: Read as '                           |                |                   |                  |                 |         |  |  |

| bit 9          | -                                     | ut Compare 3 Ii                          | -              | e bit             |                  |                 |         |  |  |

|                |                                       | equest is enab                           |                |                   |                  |                 |         |  |  |

| bit 8-5        | -                                     | equest is not e<br><b>ted:</b> Read as ' |                |                   |                  |                 |         |  |  |

| bit 4          | -                                     | nal Interrupt 1                          |                |                   |                  |                 |         |  |  |

|                |                                       | request is enab                          |                |                   |                  |                 |         |  |  |

|                |                                       | request is not e                         |                |                   |                  |                 |         |  |  |

| bit 3          | CNIE: Input C                         | Change Notifica                          | tion Interrupt | Enable bit        |                  |                 |         |  |  |

|                | -                                     | equest is enab                           | =              |                   |                  |                 |         |  |  |

|                | 0 = Interrupt r                       | equest is not e                          | nabled         |                   |                  |                 |         |  |  |

| bit 2          | CMIE: Comparator Interrupt Enable bit |                                          |                |                   |                  |                 |         |  |  |

|                | •                                     | equest is enab                           |                |                   |                  |                 |         |  |  |

|                |                                       | equest is not e                          |                |                   |                  |                 |         |  |  |

| bit 1          |                                       | ster I2C1 Even                           | -              | able bit          |                  |                 |         |  |  |

|                | •                                     | equest is enab                           |                |                   |                  |                 |         |  |  |

| hit 0          |                                       | equest is not e                          |                | lo hit            |                  |                 |         |  |  |

| bit 0          |                                       | ve I2C1 Event I                          |                |                   |                  |                 |         |  |  |

|                | ⊥ – menupt r                          | equest is enab                           | nabled         |                   |                  |                 |         |  |  |

#### REGISTER 8-12: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

#### REGISTER 8-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| U-0                               | U-0             | U-0                              | U-0              | U-0               | U-0  | U-0             | U-0    |  |  |  |

|-----------------------------------|-----------------|----------------------------------|------------------|-------------------|------|-----------------|--------|--|--|--|

| —                                 | —               | —                                | —                | —                 |      |                 | —      |  |  |  |

| bit 15                            |                 |                                  |                  |                   |      |                 | bit 8  |  |  |  |

|                                   |                 |                                  |                  |                   |      |                 |        |  |  |  |

| U-0                               | U-0             | R/W-0                            | U-0              | U-0               | U-0  | R/W-0           | R/W-0  |  |  |  |

|                                   |                 | IC3IE                            |                  |                   |      | SPI2IE          | SPF2IE |  |  |  |

| bit 7                             |                 |                                  |                  |                   |      |                 | bit 0  |  |  |  |

|                                   |                 |                                  |                  |                   |      |                 |        |  |  |  |

| Legend:                           |                 |                                  |                  |                   |      |                 |        |  |  |  |

| R = Readable bit W = Writable bit |                 | U = Unimplen                     | nented bit, read | l as '0'          |      |                 |        |  |  |  |

| -n = Value a                      | at POR          | '1' = Bit is set                 |                  | '0' = Bit is clea | ared | x = Bit is unkr | nown   |  |  |  |

|                                   |                 |                                  |                  |                   |      |                 |        |  |  |  |

| bit 15-6                          | Unimplemen      | ted: Read as '                   | o'               |                   |      |                 |        |  |  |  |

| bit 5                             | IC3IE: Input C  | Capture Channe                   | el 3 Interrupt E | nable bit         |      |                 |        |  |  |  |

|                                   | 1 = Interrupt r | request is enab                  | led              |                   |      |                 |        |  |  |  |

|                                   | 0 = Interrupt r | request is not e                 | nabled           |                   |      |                 |        |  |  |  |

| bit 4-2                           | Unimplemen      | ted: Read as '                   | D'               |                   |      |                 |        |  |  |  |

| bit 1                             | SPI2IE: SPI2    | Event Interrup                   | t Enable bit     |                   |      |                 |        |  |  |  |

|                                   | 1 = Interrupt r | 1 = Interrupt request is enabled |                  |                   |      |                 |        |  |  |  |

|                                   | 0 = Interrupt r | request is not e                 | nabled           |                   |      |                 |        |  |  |  |

| bit 0                             | SPF2IE: SPI2    | 2 Fault Interrup                 | t Enable bit     |                   |      |                 |        |  |  |  |

|                                   | 1 = Interrupt r | request is enab                  | led              |                   |      |                 |        |  |  |  |

|                                   | ∩ = Interrupt r | request is not e                 | nahled           |                   |      |                 |        |  |  |  |

0 = Interrupt request is not enabled

### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

**Note:** The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 26.0 "Special Features"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

### 22.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", Section 51. "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (Internal and External)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU and a configurable results buffer. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 22-1.

### 22.1 A/D Control Registers