Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 39                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8×8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka304-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                   | Bit 14  | Bit 13  | Bit 12                   | Bit 11                 | Bit 10                   | Bit 9                    | Bit 8                  | Bit 7                 | Bit 6   | Bit 5   | Bit 4                    | Bit 3                    | Bit 2                    | Bit 1                    | Bit 0                    | All<br>Resets |

|--------------|------|--------------------------|---------|---------|--------------------------|------------------------|--------------------------|--------------------------|------------------------|-----------------------|---------|---------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|---------------|

| CNPD1        | 0056 | CN15PDE <sup>(1)</sup>   | CN14PDE | CN13PDE | CN12PDE                  | CN11PDE                | CN10PDE <sup>(1,2)</sup> | CN9PDE <sup>(1)</sup>    | CN8PDE <sup>(3)</sup>  | CN7PDE <sup>(1)</sup> | CN6PDE  | CN5PDE  | CN4PDE                   | CN3PDE                   | CN2PDE                   | CN1PDE                   | CNOPDE                   | 0000          |

| CNPD2        | 0058 | CN31PDE <sup>(1,2)</sup> | CN30PDE | CN29PDE | CN28PDE <sup>(1,2)</sup> | CN27PDE <sup>(1)</sup> | CN26PDE <sup>(1,2)</sup> | CN25PDE <sup>(1,2)</sup> | CN24PDE <sup>(1)</sup> | CN23PDE               | CN22PDE | CN21PDE | CN20PDE <sup>(1,2)</sup> | CN19PDE <sup>(1,2)</sup> | CN18PDE <sup>(1,2)</sup> | CN17PDE <sup>(1,2)</sup> | CN16PDE <sup>(1)</sup>   | 0000          |

| CNPD3        | 005A | _                        |         | _       | _                        | -                      | _                        | _                        | -                      | _                     | _       | _       | CN36PDE <sup>(1,2)</sup> | CN35PDE <sup>(1,2)</sup> | CN34PDE <sup>(1,2)</sup> | CN33PDE <sup>(1,2)</sup> | CN32PDE <sup>(1,2)</sup> | 0000          |

| CNEN1        | 0062 | CN15IE <sup>(1)</sup>    | CN14IE  | CN13IE  | CN12IE                   | CN11IE                 | CN10IE <sup>(1,2)</sup>  | CN9IE <sup>(1)</sup>     | CN8IE <sup>(3)</sup>   | CN7IE <sup>(1)</sup>  | CN6IE   | CN5IE   | CN4IE                    | CN3IE                    | CN2IE                    | CN1IE                    | CN0IE                    | 0000          |

| CNEN2        | 0064 | CN31IE <sup>(1,2)</sup>  | CN30IE  | CN29IE  | CN28IE <sup>(1,2)</sup>  | CN27IE <sup>(1)</sup>  | CN26IE <sup>(1,2)</sup>  | CN25IE <sup>(1,2)</sup>  | CN24IE <sup>(1)</sup>  | CN23IE                | CN22IE  | CN21IE  | CN20IE <sup>(1,2)</sup>  | CN19IE <sup>(1,2)</sup>  | CN18IE <sup>(1,2)</sup>  | CN17IE <sup>(1,2)</sup>  | CN16IE <sup>(1)</sup>    | 0000          |

| CNEN3        | 0066 | _                        |         | _       | _                        | _                      | _                        | _                        | -                      | _                     | _       | _       | CN36IE <sup>(1,2)</sup>  | CN35IE <sup>(1,2)</sup>  | CN34IE <sup>(1,2)</sup>  | CN33IE <sup>(1,2)</sup>  | CN32IE <sup>(1,2)</sup>  | 0000          |

| CNPU1        | 006E | CN15PUE <sup>(1)</sup>   | CN14PUE | CN13PUE | CN12PUE                  | CN11PUE                | CN10PUE <sup>(1,2)</sup> | CN9PUE <sup>(1)</sup>    | CN8PUE <sup>(3)</sup>  | CN7PUE <sup>(1)</sup> | CN6PUE  | CN5PUE  | CN4PUE                   | <b>CN3PUE</b>            | CN2PUE                   | CN1PUE                   | CNOPUE                   | 0000          |

| CNPU2        | 0070 | CN31PUE <sup>(1,2)</sup> | CN30PUE | CN29PUE | CN28PUE <sup>(1,2)</sup> | CN27PUE <sup>(1)</sup> | CN26PUE <sup>(1,2)</sup> | CN25PUE <sup>(1,2)</sup> | CN24PUE <sup>(1)</sup> | CN23PUE               | CN22PUE | CN21PUE | CN20PUE <sup>(1,2)</sup> | CN19PUE <sup>(1,2)</sup> | CN18PUE <sup>(1,2)</sup> | CN17PUE <sup>(1,2)</sup> | CN16PUE <sup>(1)</sup>   | 0000          |

| CNPU3        | 0072 | _                        | _       | —       | _                        | _                      | _                        | _                        | _                      |                       | —       | _       | CN36PUE <sup>(1,2)</sup> | CN35PUE <sup>(1,2)</sup> | CN34PUE <sup>(1,2)</sup> | CN33PUE <sup>(1,2)</sup> | CN32PUE <sup>(1,2)</sup> | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

3: These bits are not implemented in FV devices.

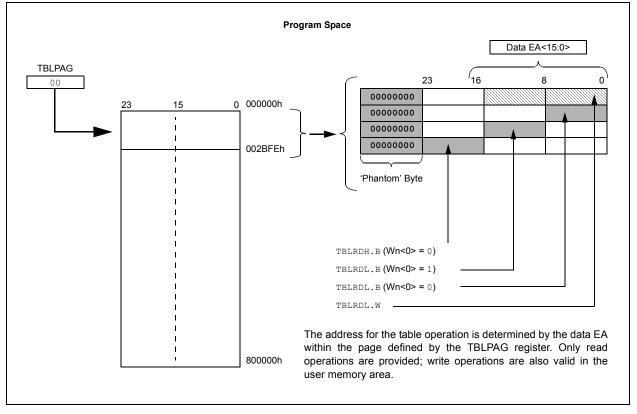

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

### FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the table read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and table read procedures (builtin\_tblrdl) from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

```

int attribute ((space(eedata))) eeData = 0x1234;

// Data read from EEPROM

int data;

/*_____

_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the read

_____

*/

unsigned int offset;

\ensuremath{//} Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData);

// Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

data = __builtin_tblrdl(offset);

// Initizlize lower word of address

// Write EEPROM data to write latch

```

| REGISTER      | 8-4: INTC                                                           | ON2: INTERR                             | UPT CONTE                  | ROL REGIST       | ER2              |                 |        |  |  |

|---------------|---------------------------------------------------------------------|-----------------------------------------|----------------------------|------------------|------------------|-----------------|--------|--|--|

| R/W-0         | R-0, HSC                                                            | U-0                                     | U-0                        | U-0              | U-0              | U-0             | U-0    |  |  |

| ALTIVT        | DISI                                                                | —                                       | _                          | _                | —                | —               | —      |  |  |

| bit 15        |                                                                     |                                         |                            |                  |                  |                 | bit 8  |  |  |

|               |                                                                     |                                         |                            |                  |                  |                 |        |  |  |

| U-0           | U-0                                                                 | U-0                                     | U-0                        | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |

| —             |                                                                     | —                                       |                            | —                | INT2EP           | INT1EP          | INT0EP |  |  |

| bit 7         |                                                                     |                                         |                            |                  |                  |                 | bit 0  |  |  |

|               |                                                                     |                                         |                            |                  |                  |                 |        |  |  |

| Legend:       |                                                                     | HSC = Hardwa                            | are Settable/C             |                  |                  |                 |        |  |  |

| R = Readabl   | le bit                                                              | W = Writable b                          | oit                        | U = Unimpler     | mented bit, read | d as '0'        |        |  |  |

| -n = Value at | t POR                                                               | '1' = Bit is set                        |                            | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |

|               |                                                                     |                                         |                            |                  |                  |                 |        |  |  |

| bit 15        | ALTIVT: Enat                                                        | ole Alternate Inte                      | errupt Vector <sup>-</sup> | lable bit        |                  |                 |        |  |  |

|               |                                                                     | rnate Interrupt \<br>ndard (default) Ir | · ·                        | ,                |                  |                 |        |  |  |

| bit 14        | DISI: DISI In                                                       | struction Status                        | bit                        |                  |                  |                 |        |  |  |

|               |                                                                     | ruction is active                       |                            |                  |                  |                 |        |  |  |

|               | 0 = DISI inst                                                       | ruction is not ac                       | tive                       |                  |                  |                 |        |  |  |

| bit 13-3      | Unimplemen                                                          | ted: Read as '0                         | 3                          |                  |                  |                 |        |  |  |

| bit 2         | INT2EP: Exte                                                        | ernal Interrupt 2                       | Edge Detect F              | Polarity Select  | bit              |                 |        |  |  |

|               |                                                                     | s on the negatives on the positive      | 0                          |                  |                  |                 |        |  |  |

| bit 1         | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit |                                         |                            |                  |                  |                 |        |  |  |

|               | 1 = Interrupt i                                                     | s on the negativ                        | e edge                     |                  |                  |                 |        |  |  |

|               | 0 = Interrupt i                                                     | s on the positive                       | e edge                     |                  |                  |                 |        |  |  |

| bit 0         | INTOEP: Exte                                                        | ernal Interrupt 0                       | Edge Detect F              | Polarity Select  | bit              |                 |        |  |  |

|               |                                                                     | s on the negativ                        |                            |                  |                  |                 |        |  |  |

|               | 0 = Interrupt i                                                     | s on the positive                       | e edge                     |                  |                  |                 |        |  |  |

### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

### REGISTER 8-30: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|--------|-----|-----|-----|-----|---------|---------|---------|

| —      | —   | —   | —   | —   | _       |         | —       |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _      | _   | _   | _   | _   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7 |

|-------|

|       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

### REGISTER 8-31: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CTMUIP2 | CTMUIP1 | CTMUIP0 | —   | —   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-4 **CTMUIP<2:0>:** CTMU Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

•

bit 0

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

|                                           |

### 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FV32KA304 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

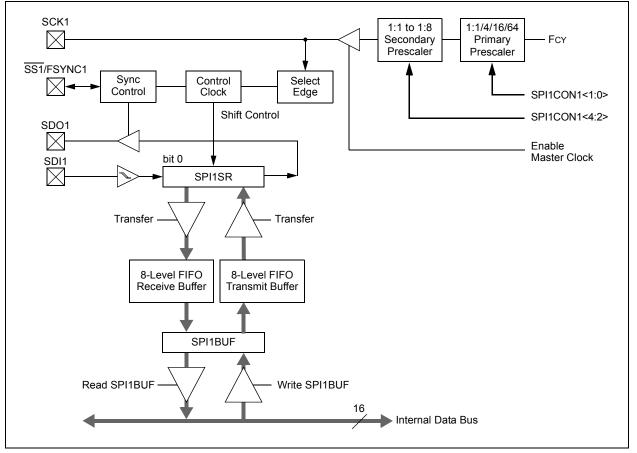

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches. To set up the SPI1 module for the Enhanced Buffer Master (EBM) mode of operation:

- 1. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 1.

- 3. Clear the SPIROV bit (SPI1STAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPI1CON2<0>).

- 5. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

- 6. Write the data to be transmitted to the SPI1BUF register. Transmission (and reception) will start as soon as data is written to the SPI1BUF register.

To set up the SPI1 module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPI1BUF register.

- 2. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SS1 pin.

- 6. Clear the SPIROV bit (SPI1STAT<6>).

- Select Enhanced Buffer mode by setting the SPIBEN bit (SPI1CON2<0>).

- Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

### FIGURE 16-2: SPI1 MODULE BLOCK DIAGRAM (ENHANCED BUFFER MODE)

REGISTER 16-1:

#### R/W-0 U-0 R/W-0 U-0 U-0 R-0, HSC R-0, HSC R-0, HSC SPIEN SPIBEC0 SPISIDL SPIBEC2 SPIBEC1 bit 15 bit 8 R-0, HSC R/C-0, HS R/W-0, HSC R/W-0 R/W-0 R/W-0 R-0, HSC R-0, HSC SPIROV SPIRBF SRMPT SRXMPT SISEL2 SISEL1 SISEL0 SPITBF bit 7 bit 0 HS = Hardware Settable bit HSC = Hardware Settable/Clearable bit Legend: C = Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set -n = Value at POR '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPI transfers pending. Slave mode: Number of SPI transfers unread. bit 7 SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) 1 = SPIx Shift register is empty and ready to send or receive 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit 1 = A new byte/word is completely received and discarded (the user software has not read the previous data in the SPI1BUF register) 0 = No overflow has occurred bit 5 **SRXMPT:** SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode) 1 = Receive FIFO is empty 0 = Receive FIFO is not empty bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode) 111 = Interrupt when SPIx transmit buffer is full (SPITBF bit is set) 110 = Interrupt when last bit is shifted into SPIxSR; as a result, the TX FIFO is empty 101 = Interrupt when the last bit is shifted out of SPIxSR; now the transmit is complete 100 = Interrupt when one data byte is shifted into the SPIxSR: as a result, the TX FIFO has one open spot 011 = Interrupt when SPIx receive buffer is full (SPIRBF bit is set) 010 = Interrupt when SPIx receive buffer is 3/4 or more full 001 = Interrupt when data is available in receive buffer (SRMPT bit is set) 000 = Interrupt when the last data in the receive buffer is read; as a result, the buffer is empty (SRXMPT bit is set)

SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                               | R/W-1, HC         | R/W-0                         | R/W-0                     | R/W-0             | R/W-0          |

|--------------|------------------------------|-------------------------------------|-------------------|-------------------------------|---------------------------|-------------------|----------------|

| I2CEN        |                              | I2CSIDL                             | SCLREL            | IPMIEN                        | A10M                      | DISSLW            | SMEN           |

| bit 15       |                              | -                                   | •                 |                               | ·                         |                   | bit 8          |

| R/W-0        | R/W-0                        | R/W-0                               | R/W-0, HC         | R/W-0, HC                     | R/W-0, HC                 | R/W-0, HC         | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                               | ACKEN             | RCEN                          | PEN                       | RSEN              | SEN            |

| bit 7        |                              |                                     |                   |                               |                           |                   | bit C          |

| Legend:      |                              | HC = Hardwa                         | re Clearable bit  |                               |                           |                   |                |

| R = Readat   | le hit                       | W = Writable                        |                   |                               | nented bit, read          | as '0'            |                |

| -n = Value a |                              | 1' = Bit is set                     | JIL               | '0' = Bit is clea             |                           | x = Bit is unkn   |                |

|              | al FUR                       | I - DILIS SEL                       |                   |                               | aleu                      |                   | OWIT           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                          |                   |                               |                           |                   |                |

|              |                              | he I2Cx module                      |                   |                               |                           |                   | 3              |

| bit 14       |                              | ited: Read as '0                    |                   | are controlled                | by port functio           | 10                |                |

| bit 13       | -                            | x Stop in Idle M                    |                   |                               |                           |                   |                |

|              |                              | ues module ope                      |                   | e device enters               | an Idle mode              |                   |                |

|              |                              | s module opera                      |                   |                               |                           |                   |                |

| bit 12       | SCLREL: SC                   | Lx Release Co                       | ntrol bit (when c | operating as I <sup>2</sup> 0 | C slave)                  |                   |                |

|              | 1 = Releases<br>0 = Holds SC | SCLx clock                          | ock stretch)      |                               |                           |                   |                |

|              | If STREN = 1                 |                                     |                   |                               |                           |                   |                |

|              |                              | V (i.e., software                   |                   |                               |                           |                   |                |

|              | lf STREN = 0                 | eginning of the                     | slave transmiss   | ion. Hardware                 | is clear at the e         | end of slave rec  | eption.        |

|              |                              | <u>.</u><br>6 (i.e., software       | may only write    | '1' to release                | clock). Hardwa            | re is clear at th | e beainnina o  |

|              | slave transmi                |                                     |                   |                               |                           |                   | 5              |

| bit 11       | IPMIEN: Intel                | lligent Periphera                   | al Management     | Interface (IPM                | I) Enable bit             |                   |                |

|              |                              | port mode is en<br>port mode is dis |                   | esses are Ackn                | owledged                  |                   |                |

| bit 10       | A10M: 10-Bit                 | Slave Address                       | ing bit           |                               |                           |                   |                |

|              | -                            | is a 10-bit slav                    |                   |                               |                           |                   |                |

|              | 0 = I2CxADD                  | is a 7-bit slave                    | address           |                               |                           |                   |                |

| bit 9        |                              | able Slew Rate                      |                   |                               |                           |                   |                |

|              |                              | control is disab                    |                   |                               |                           |                   |                |

| bit 8        | SMEN: SMBI                   | us Input Levels                     | bit               |                               |                           |                   |                |

|              |                              | /O pin threshold                    |                   | h the SMBus s                 | pecification              |                   |                |

|              |                              | the SMBus inpu                      |                   | _                             |                           |                   |                |

| bit 7        |                              | ral Call Enable                     | · ·               | •                             | ,                         |                   |                |

|              |                              | interrupt when                      | a general call a  | address is rece               | ived in the I2C           | xRSR (module      | is enabled for |

|              | 0 = General                  | i)<br>call address is o             | disabled          |                               |                           |                   |                |

| bit 6        |                              | x Clock Stretch                     |                   | en operating as               | s I <sup>2</sup> C slave) |                   |                |

|              |                              | Inction with the                    | -                 | on operating at               |                           |                   |                |

|              | 1 = Enables s                | software or rece                    | ives clock strete | •                             |                           |                   |                |

|              |                              | -                                   | eives clock stret |                               |                           |                   |                |

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC     | R-0, HSC         | U-0                                           | U-0             | U-0                           | R/C-0, HS        | R-0, HSC                         | R-0, HSC               |

|--------------|------------------|-----------------------------------------------|-----------------|-------------------------------|------------------|----------------------------------|------------------------|

| ACKSTAT      | TRSTAT           | —                                             |                 | —                             | BCL              | GCSTAT                           | ADD10                  |

| bit 15       |                  |                                               |                 |                               |                  |                                  | bit 8                  |

|              |                  |                                               |                 |                               |                  |                                  |                        |

| R/C-0, HS    | R/C-0, HS        | R-0, HSC                                      | R/C-0, HSC      | R/C-0, HSC                    | R-0, HSC         | R-0, HSC                         | R-0, HSC               |

| IWCOL        | I2COV            | D/A                                           | Р               | S                             | R/W              | RBF                              | TBF                    |

| bit 7        |                  |                                               |                 |                               |                  |                                  | bit C                  |

| Legend:      |                  | C = Clearabl                                  | e hit           | HS = Hardwar                  | e Settable bit   | HSC = Hardware S                 | Settable/Clearable bit |

| R = Readat   | ole hit          | W = Writable                                  |                 | U = Unimplem                  |                  |                                  |                        |

| -n = Value a |                  | '1' = Bit is se                               |                 | '0' = Bit is clear            |                  | x = Bit is unknown               |                        |

|              |                  | 1 - Dit 13 30                                 |                 |                               |                  |                                  |                        |

| bit 15       | ACKSTAT:         | Acknowledge                                   | e Status bit    |                               |                  |                                  |                        |

|              |                  | was detected                                  |                 |                               |                  |                                  |                        |

|              |                  | as detected la                                |                 |                               |                  |                                  |                        |

|              |                  |                                               |                 | Acknowledge.                  |                  |                                  |                        |

| bit 14       |                  | ransmit Statu<br>rating as I <sup>2</sup> C I |                 | cable to master               | transmit oner    | ration)                          |                        |

|              |                  | transmit is in                                |                 |                               | transmit oper    |                                  |                        |

|              |                  | transmit is no                                |                 | ,                             |                  |                                  |                        |

|              | Hardware is      | s set at the beg                              | inning of the r | master transmis               | sion; hardware   | is clear at the end of           | slave Acknowledge      |

| bit 13-11    | Unimplem         | ented: Read                                   | <b>as</b> '0'   |                               |                  |                                  |                        |

| bit 10       | BCL: Mast        | er Bus Collisi                                | on Detect bit   |                               |                  |                                  |                        |

|              |                  |                                               | een detected    | d during a mast               | er operation     |                                  |                        |

|              | 0 = No coll      | ision<br>s set at the d                       | otoption of a   | hua colligion                 |                  |                                  |                        |

| bit 9        |                  | Seneral Call S                                |                 |                               |                  |                                  |                        |

| DIL 9        |                  | al call address                               |                 | h                             |                  |                                  |                        |

|              |                  | al call address                               |                 |                               |                  |                                  |                        |

|              | Hardware i       | s set when a                                  | n address ma    | atches the gene               | eral call addres | s; hardware is clea              | ar at Stop detection.  |

| bit 8        | <b>ADD10:</b> 10 | -Bit Address                                  | Status bit      |                               |                  |                                  |                        |

|              |                  | address was r                                 |                 |                               |                  |                                  |                        |

|              |                  | address was r                                 |                 | uto of the motok              | ad 10 bit addr   | ana hardwara ia ala              | ar at Stop detection   |

| bit 7        |                  | Cx Write Coll                                 |                 | •                             |                  | ess, naioware is cle             | ar at Stop detection   |

|              |                  |                                               |                 |                               | d because the    | e I <sup>2</sup> C module is bus | M                      |

|              | 0 = No coll      |                                               |                 | in register falle             |                  |                                  | y                      |

|              |                  |                                               | currence of a   | a write to I2CxT              | RN while bus     | y (cleared by softwa             | are).                  |

| bit 6        | 12COV: 12C       | Cx Receive O                                  | verflow Flag    | bit                           |                  |                                  |                        |

|              | -                |                                               | while the I20   | CxRCV register                | is still holding | the previous byte                |                        |

|              | 0 = No ove       |                                               | lomat to tran   |                               |                  | laarad by aaffwara)              |                        |

| bit 5        |                  |                                               |                 | ng as I <sup>2</sup> C slave  |                  | leared by software)              |                        |

| bit 5        |                  | es that the las                               |                 |                               | )                |                                  |                        |

|              |                  |                                               |                 | ed was data<br>ed was the dev | vice address     |                                  |                        |

|              |                  |                                               |                 |                               |                  | a write to I2CxTRN               | or by reception of a   |

|              | slave byte.      |                                               |                 |                               |                  |                                  |                        |

| U-0          | R/W-x                                                               | R/W-x            | R/W-x          | R/W-x             | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

|--------------|---------------------------------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|---------|--|--|--|--|

|              | MINTEN2                                                             | MINTEN1          | MINTEN0        | MINONE3           | MINONE2          | MINONE1         | MINONE0 |  |  |  |  |

| bit 15       |                                                                     |                  |                |                   |                  |                 | bit 8   |  |  |  |  |

|              |                                                                     |                  |                |                   |                  |                 |         |  |  |  |  |

| U-0          | R/W-x                                                               | R/W-x            | R/W-x          | R/W-x             |                  |                 |         |  |  |  |  |

| —            | SECTEN2                                                             | SECTEN1          | SECTEN0        | SECONE3           | SECONE2          | SECONE1         | SECONE0 |  |  |  |  |

| bit 7        |                                                                     |                  |                |                   |                  |                 | bit 0   |  |  |  |  |

|              |                                                                     |                  |                |                   |                  |                 |         |  |  |  |  |

| Legend:      |                                                                     |                  |                |                   |                  |                 |         |  |  |  |  |

| R = Readab   | le bit                                                              | W = Writable     | bit            | U = Unimplem      | nented bit, read | 1 as '0'        |         |  |  |  |  |

| -n = Value a | t POR                                                               | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                                     |                  |                |                   |                  |                 |         |  |  |  |  |

| bit 15       | Unimplement                                                         | ted: Read as '0  | ,              |                   |                  |                 |         |  |  |  |  |

| bit 14-12    | MINTEN<2:0                                                          | >: Binary Code   | d Decimal Valu | ue of Minute's T  | ens Digit bits   |                 |         |  |  |  |  |

|              | Contains a va                                                       | lue from 0 to 5  |                |                   |                  |                 |         |  |  |  |  |

| bit 11-8     | MINONE<3:0                                                          | >: Binary Code   | d Decimal Val  | ue of Minute's 0  | Ones Digit bits  |                 |         |  |  |  |  |

|              | Contains a va                                                       | lue from 0 to 9  |                |                   |                  |                 |         |  |  |  |  |

| bit 7        | Unimplemen                                                          | ted: Read as '   | o'             |                   |                  |                 |         |  |  |  |  |

| bit 6-4      | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |                  |                |                   |                  |                 |         |  |  |  |  |

|              | Contains a value from 0 to 5.                                       |                  |                |                   |                  |                 |         |  |  |  |  |

| bit 3-0      | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |                  |                |                   |                  |                 |         |  |  |  |  |

|              | Contains a va                                                       | lue from 0 to 9  |                |                   |                  |                 |         |  |  |  |  |

|              |                                                                     |                  |                |                   |                  |                 |         |  |  |  |  |

### REGISTER 19-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

### REGISTER 22-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   | U-0   |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   | —   | —   | —   | _   |       | —     |

| bit 15 |     |     |     |     |     |       | bit 8 |

|        |     |     |     |     |     |       |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|        |     | —   | —   | —   |     | CHH17 | CHH16 |

| bit 7  |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'.

bit 1-0 CHH<17:16>: A/D Compare Hit bits

If CM<1:0> = 11:

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For All Other Values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

### REGISTER 22-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| CHH15  | CHH14 | CHH13 | CHH12 | CHH11 | CHH10 | CHH9  | CHH8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CHH7   | CHH6  | CHH5  | CHH4  | CHH3  | CHH2  | CHH1  | CHH0  |

| bit 7  | •     | •     | •     |       | •     | •     | bit 0 |

|        |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CHH<15:0>: A/D Compare Hit bits

<u>If CM<1:0> = 11:</u>

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For all other values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

### TABLE 22-2:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>12-BIT FRACTIONAL FORMATS

| VIN/VREF   | 12-Bit<br>Output Code | 16-Bit Fractional Format/<br>Equivalent Decimal Value |       | 16-Bit Signed Fractional Fo<br>Equivalent Decimal Val |        |

|------------|-----------------------|-------------------------------------------------------|-------|-------------------------------------------------------|--------|

| +4095/4096 | 0 1111 1111 1111      | 1111 1111 1111 0000                                   | 0.999 | 0111 1111 1111 1000                                   | 0.999  |

| +4094/4096 | 0 1111 1111 1110      | 1111 1111 1110 0000                                   | 0.998 | 0111 1111 1110 1000                                   | 0.998  |

|            |                       | •••                                                   |       |                                                       |        |

| +1/4096    | 0 0000 0000 0001      | 0000 0000 0001 0000                                   | 0.001 | 0000 0000 0000 1000                                   | 0.001  |

| 0/4096     | 0 0000 0000 0000      | 0000 0000 0000 0000                                   | 0.000 | 0000 0000 0000 0000                                   | 0.000  |

| -1/4096    | 1 0111 1111 1111      | 0000 0000 0000 0000                                   | 0.000 | 1111 1111 1111 1000                                   | -0.001 |

|            |                       | •••                                                   |       |                                                       |        |

| -4095/4096 | 1 0000 0000 0001      | 0000 0000 0000 0000                                   | 0.000 | 1000 0000 0000 1000                                   | -0.999 |

| -4096/4096 | 1 0000 0000 0000      | 0000 0000 0000 0000                                   | 0.000 | 1000 0000 0000 0000                                   | -1.000 |

### FIGURE 22-5: A/D OUTPUT DATA FORMATS (10-BIT)

|     |           |               |                                                                |                                                                                       |                                                                                                              | d09                                                                                                                                 | d08                                                                                                                                                                                                                                   | d07                                                                                                                                                                                                                                                                       | d06                                                                                                                                                                                                                                                                                                                      | d05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | d04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | d03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | d02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------|---------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |           |               |                                                                |                                                                                       |                                                                                                              |                                                                                                                                     |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |