Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 39                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

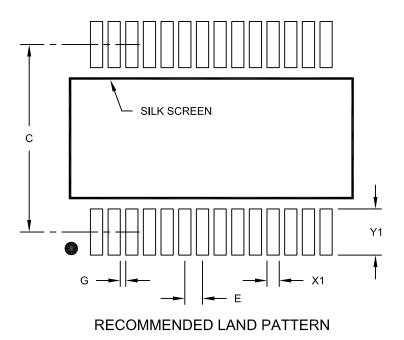

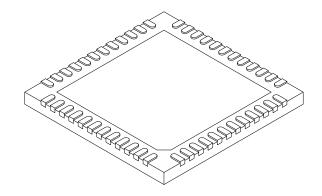

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka304t-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F32KA304 FAMILY

| Features                                            | PIC24F16KA301                            | PIC24F32KA301                         | PIC24F16KA302              | PIC24F32KA302 | PIC16F16KA304                              | PIC24F32KA304 |  |

|-----------------------------------------------------|------------------------------------------|---------------------------------------|----------------------------|---------------|--------------------------------------------|---------------|--|

| Operating Frequency                                 |                                          |                                       | DC – 32 I                  | MHz           |                                            |               |  |

| Program Memory (bytes)                              | 16K                                      | 32K                                   | 16K                        | 32K           | 16K                                        | 32K           |  |

| Program Memory (instructions)                       | 5632                                     | 11264                                 | 5632                       | 11264         | 5632                                       | 11264         |  |

| Data Memory (bytes)                                 |                                          |                                       | 2048                       |               |                                            |               |  |

| Data EEPROM Memory (bytes)                          |                                          |                                       | 512                        |               |                                            |               |  |

| Interrupt Sources (soft vectors/<br>NMI traps)      |                                          |                                       | 30 (26/-                   | 4)            |                                            |               |  |

| I/O Ports                                           | PORTA<6:0>,<br>PORTB<15:12, 9:7, 4, 2:0> |                                       | PORTA<7:0>,<br>PORTB<15:0> |               | PORTA<11:0>,<br>PORTB<15:0>,<br>PORTC<9:0> |               |  |

| Total I/O Pins                                      | 18                                       |                                       | 24                         |               | 39                                         |               |  |

| Timers: Total Number (16-bit)                       |                                          |                                       | 5                          |               |                                            |               |  |

| 32-Bit (from paired 16-bit timers)                  | 2                                        |                                       |                            |               |                                            |               |  |

| Input Capture Channels                              |                                          | 3                                     |                            |               |                                            |               |  |

| Output Compare/PWM Channels                         |                                          |                                       | 3                          |               |                                            |               |  |

| Input Change Notification Interrupt                 | 17                                       | 7                                     | 23                         |               | 38                                         |               |  |

| Serial Communications: UART<br>SPI (3-wire/4-wire)  |                                          |                                       | 2                          |               |                                            |               |  |

| I <sup>2</sup> C™                                   |                                          |                                       | 2                          |               |                                            |               |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 12                                       | 2                                     | 1:                         | 3             | 1                                          | 6             |  |

| Analog Comparators                                  |                                          |                                       | 3                          |               |                                            |               |  |

| Resets (and delays)                                 |                                          | , BOR, RESET<br>Instruction, Ha<br>(F |                            | , Configurati |                                            |               |  |

| Instruction Set                                     | 76 E                                     | Base Instruction                      | ns, Multiple A             | ddressing M   | ode Variation                              | S             |  |

| Packages                                            | 20-F<br>PDIP/SSC                         |                                       | 28-1<br>SPDIP/SSOF         |               | 44-Pin QI<br>48-Pin                        |               |  |

## 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                       | U-0                                                                                          | U-0                                 | U-0             | U-0              | U-0                                   | U-0              | R/W-0, HSC    |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|---------------------------------------|------------------|---------------|--|--|--|--|

| _                         | _                                                                                            | _                                   | —               | —                | —                                     | —                | DC            |  |  |  |  |

| bit 15                    |                                                                                              |                                     |                 |                  |                                       |                  | bit 8         |  |  |  |  |

|                           |                                                                                              |                                     |                 |                  |                                       |                  |               |  |  |  |  |

| R/W-0, HSC <sup>(1)</sup> |                                                                                              | R/W-0, HSC <sup>(1)</sup>           | R-0, HSC        | R/W-0, HSC       | R/W-0, HSC                            | R/W-0, HSC       | R/W-0, HSC    |  |  |  |  |

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>                                                                          | IPL0 <sup>(2)</sup>                 | RA              | Ν                | OV                                    | Z                | С             |  |  |  |  |

| bit 7                     |                                                                                              |                                     |                 |                  |                                       |                  | bit (         |  |  |  |  |

| Lagandi                   |                                                                                              | HSC = Hardwa                        | ra Cattabla/    | Nooroblo hit     |                                       |                  |               |  |  |  |  |

| Legend:<br>R = Readable   | hit                                                                                          | W = Writable bi                     |                 |                  | mented bit, rea                       | ad as 'O'        |               |  |  |  |  |

| -n = Value at P           |                                                                                              | '1' = Bit is set                    | ι               | '0' = Bit is cle |                                       | x = Bit is unk   | nown          |  |  |  |  |

|                           | on                                                                                           |                                     |                 |                  | arca                                  |                  |               |  |  |  |  |

| bit 15-9                  | Unimplemente                                                                                 | d: Read as '0'                      |                 |                  |                                       |                  |               |  |  |  |  |

| bit 8                     | DC: ALU Half C                                                                               |                                     |                 |                  |                                       |                  |               |  |  |  |  |

|                           |                                                                                              | from the 4 <sup>th</sup> low-       | -order bit (foi | byte-sized da    | ta) or 8 <sup>th</sup> Iow-o          | rder bit (for wo | rd-sized data |  |  |  |  |

|                           | of the resul                                                                                 |                                     | oth .           |                  |                                       |                  |               |  |  |  |  |

|                           | -                                                                                            | ut from the 4 <sup>th</sup> or      |                 |                  | sult has occurr                       | ed               |               |  |  |  |  |

| bit 7-5                   |                                                                                              | Interrupt Priority                  |                 |                  |                                       |                  |               |  |  |  |  |

|                           | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                   |                                     |                 |                  |                                       |                  |               |  |  |  |  |

|                           | 110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13) |                                     |                 |                  |                                       |                  |               |  |  |  |  |

|                           | 101 = CPU Interrupt Priority Level is 3 (13)<br>100 = CPU Interrupt Priority Level is 4 (12) |                                     |                 |                  |                                       |                  |               |  |  |  |  |

|                           |                                                                                              | errupt Priority Lev                 |                 |                  |                                       |                  |               |  |  |  |  |

|                           |                                                                                              | errupt Priority Lev                 |                 |                  |                                       |                  |               |  |  |  |  |

|                           |                                                                                              | errupt Priority Lev                 |                 |                  |                                       |                  |               |  |  |  |  |

| bit 4                     | RA: REPEAT LC                                                                                | errupt Priority Lev                 |                 |                  |                                       |                  |               |  |  |  |  |

| bit 4                     | $1 = \text{REPEAT} \log 1$                                                                   | -                                   |                 |                  |                                       |                  |               |  |  |  |  |

|                           |                                                                                              | p not in progress                   | S               |                  |                                       |                  |               |  |  |  |  |

| bit 3                     | N: ALU Negativ                                                                               | e bit                               |                 |                  |                                       |                  |               |  |  |  |  |

|                           | 1 = Result was                                                                               | •                                   |                 |                  |                                       |                  |               |  |  |  |  |

|                           |                                                                                              | non-negative (ze                    | ero or positiv  | ve)              |                                       |                  |               |  |  |  |  |

| bit 2                     | OV: ALU Overfl                                                                               |                                     |                 |                  |                                       |                  |               |  |  |  |  |

|                           | 1 = Overflow or<br>0 = No overflow                                                           | curred for signe                    | d (2's compl    | ement) arithme   | etic in this arith                    | nmetic operatio  | on            |  |  |  |  |

| bit 1                     | <b>Z:</b> ALU Zero bit                                                                       |                                     |                 |                  |                                       |                  |               |  |  |  |  |

|                           | 1 = An operatio                                                                              | n, which effects                    |                 |                  |                                       |                  | esult)        |  |  |  |  |

| bit 0                     | <b>C:</b> ALU Carry/B                                                                        |                                     |                 |                  | , , , , , , , , , , , , , , , , , , , | ,                | ,             |  |  |  |  |

|                           | 1 = A carry-out                                                                              | from the Most S<br>at from the Most |                 |                  |                                       |                  |               |  |  |  |  |

| Note 1: The               | IPLx Status bits                                                                             | are read-onlv wh                    | en NSTDIS       | (INTCON1<1       | 5>) = 1.                              |                  |               |  |  |  |  |

|                           | IPL<2:0> Status                                                                              | •                                   |                 |                  |                                       | o form the CPL   | J Interrupt   |  |  |  |  |

|                           | rity I aval (IPI ) T                                                                         |                                     |                 |                  |                                       |                  |               |  |  |  |  |

Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

### 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | intended to be a comprehensive reference                                           |  |  |  |  |  |  |

|       | source. For more information on Flash pro-                                         |  |  |  |  |  |  |

|       | gramming, refer to the "PIC24F Family                                              |  |  |  |  |  |  |

|       | Reference Manual", Section 4. "Program                                             |  |  |  |  |  |  |

|       | Memory" (DS39715).                                                                 |  |  |  |  |  |  |

The PIC24FV32KA304 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FV32KA304 device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program mode Entry voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

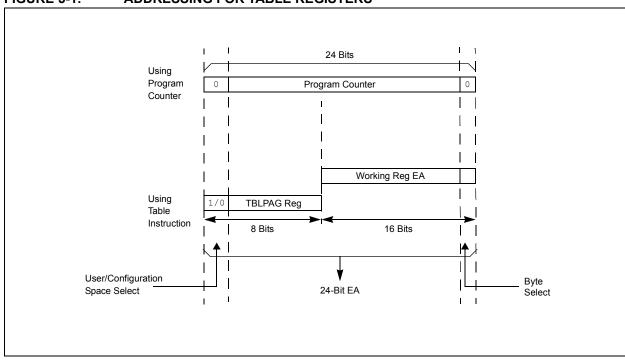

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, Flash memory programming is done with the table read and write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is as follows:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '011000' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

| MOV #0x4058, W0                  | ;                                       |

|----------------------------------|-----------------------------------------|

| MOV W0, NVMCON                   | ; Initialize NVMCON                     |

| Init pointer to row to be ERASED |                                         |

| MOV #tblpage(PROG_ADDR), W0      | ;                                       |

| MOV W0, TBLPAG                   | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W     | 0 ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                  | ; Set base address of erase block       |

| DISI #5                          | ; Block all interrupts                  |

|                                  | for next 5 instructions                 |

| MOV #0x55, W0                    |                                         |

| MOV W0, NVMKEY                   | ; Write the 55 key                      |

| MOV #0xAA, W1                    | ;                                       |

| MOV W1, NVMKEY                   | ; Write the AA key                      |

| BSET NVMCON, #WR                 | ; Start the erase sequence              |

| NOP                              | ; Insert two NOPs after the erase       |

| NOP                              | ; command is asserted                   |

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

#### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the table read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and table read procedures (builtin\_tblrdl) from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

#### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

```

int attribute ((space(eedata))) eeData = 0x1234;

// Data read from EEPROM

int data;

/*_____

_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the read

_____

*/

unsigned int offset;

\ensuremath{//} Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData);

// Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

data = __builtin_tblrdl(offset);

// Initizlize lower word of address

// Write EEPROM data to write latch

```

#### 8.3 Interrupt Control and Status Registers

The PIC24FV32KA304 family of devices implements a total of 23 registers for the interrupt controller:

- INTCON1

- INTCON2

- · IFS0, IFS1, IFS3 and IFS4

- · IEC0, IEC1, IEC3 and IEC4

- IPC0 through IPC5, IPC7 and IPC15 through IPC19

- INTTREG

Global Interrupt Enable (GIE) control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIVT.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU Interrupt Priority Level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All Interrupt registers are described in Register 8-1 through Register 8-33, in the following sections.

#### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | —   | —   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-9 Unimplemented: Read as '0'

| bit 7 5 | IPL<2:0>: CPU Interrupt Priority Level              | Status hits (2,3) |

|---------|-----------------------------------------------------|-------------------|

| bit 7-5 | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level | Status Dits       |

- 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- **3:** The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

#### REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0           | U-0               | U-0                                  | U-0               | U-0                                   | U-0                | U-0              | U-0                |  |

|---------------|-------------------|--------------------------------------|-------------------|---------------------------------------|--------------------|------------------|--------------------|--|

| —             | —                 | —                                    | —                 | —                                     | —                  | —                | —                  |  |

| bit 15        |                   |                                      |                   |                                       |                    |                  | bit 8              |  |

|               |                   |                                      |                   |                                       |                    |                  |                    |  |

| U-0           | U-0               | U-0                                  | U-0               | R/C-0, HSC                            | R/W-0              | U-0              | U-0                |  |

| _             | —                 | —                                    | —                 | IPL3 <sup>(2)</sup>                   | PSV <sup>(1)</sup> | —                | —                  |  |

| bit 7         |                   |                                      |                   |                                       |                    |                  | bit 0              |  |

|               |                   |                                      |                   |                                       |                    |                  |                    |  |

| Legend:       |                   | C = Clearable                        | bit               | HSC = Hardware Settable/Clearable bit |                    |                  |                    |  |

| R = Readabl   | e bit             | W = Writable                         | bit               | U = Unimplemented bit, read as '0'    |                    |                  |                    |  |

| -n = Value at | POR               | '1' = Bit is set                     |                   | '0' = Bit is clea                     | ared               | x = Bit is unkr  | c = Bit is unknown |  |

|               |                   |                                      |                   |                                       |                    |                  |                    |  |

| bit 15-4      | Unimplemen        | ted: Read as '                       | )'                |                                       |                    |                  |                    |  |

| bit 3         | IPL3: CPU In      | terrupt Priority                     | Level Status bi   | t <sup>(2)</sup>                      |                    |                  |                    |  |

|               |                   | rupt Priority Le<br>rupt Priority Le |                   |                                       |                    |                  |                    |  |

| bit 1-0       | Unimplemen        | ted: Read as '                       | )'                |                                       |                    |                  |                    |  |

| Note 1: Se    | ee Register 3-2   | for the descript                     | ion of this hit v | which is not der                      | dicated to inter   | runt control fun | ctions             |  |

|               | ne IPL3 bit is co | -                                    |                   |                                       |                    | -                |                    |  |

|               |                   |                                      |                   |                                       |                    |                  | 2                  |  |

|               |                   |                                      |                   |                                       |                    |                  |                    |  |

Note: Bit 2 is described in Section 3.0 "CPU".

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0           | U-0    | U-0              | U-0 | U-0                                     | U-0              | U-0      | U-0     |

|---------------|--------|------------------|-----|-----------------------------------------|------------------|----------|---------|

| _             | —      | —                | _   | —                                       |                  | _        | —       |

| bit 15        |        |                  |     |                                         |                  |          | bit 8   |

|               |        |                  |     |                                         |                  |          |         |

| U-0           | U-0    | U-0              | U-0 | U-0                                     | U-0              | U-0      | R/W-0   |

| —             | —      | —                | —   | —                                       | —                | —        | ULPWUIE |

| bit 7         |        |                  |     |                                         |                  |          | bit 0   |

|               |        |                  |     |                                         |                  |          |         |

| Legend:       |        |                  |     |                                         |                  |          |         |

| R = Readabl   | le bit | W = Writable I   | oit | U = Unimplen                            | nented bit, read | l as '0' |         |

| -n = Value at | POR    | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |          | nown    |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                   | R/W-0                                | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------|-------------------------|--------------------------------------|-------------------|------------------|------------------|-----------------|---------|

| _                | U1RXIP2                 | U1RXIP1                              | U1RXIP0           | _                | SPI1IP2          | SPI1IP1         | SPI1IP0 |

| bit 15           |                         |                                      |                   |                  |                  |                 | bit 8   |

| U-0              | R/W-1                   | R/W-0                                | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                | SPF1IP2                 | SPF1IP1                              | SPF1IP0           |                  | T3IP2            | T3IP1           | T3IP0   |

| bit 7            |                         | 1                                    |                   |                  |                  | 1               | bit (   |

| Legend:          |                         |                                      |                   |                  |                  |                 |         |

| R = Readat       | ole bit                 | W = Writable                         | bit               | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value a     | at POR                  | '1' = Bit is set                     |                   | '0' = Bit is cle |                  | x = Bit is unkn | iown    |

|                  |                         |                                      |                   |                  |                  |                 |         |

| bit 15           | Unimplemen              | ted: Read as '                       | )'                |                  |                  |                 |         |

| bit 14-12        | -                       | : UART1 Rece                         |                   | riority bits     |                  |                 |         |

|                  |                         | pt is Priority 7 (                   | =                 | -                |                  |                 |         |

|                  | •                       |                                      | 0 . ,             | • /              |                  |                 |         |

|                  | •                       |                                      |                   |                  |                  |                 |         |

|                  | 001 = Interru           |                                      |                   |                  |                  |                 |         |

|                  | -                       | ot source is dis                     |                   |                  |                  |                 |         |

| bit 11           | -                       | ted: Read as '                       |                   |                  |                  |                 |         |

| bit 10-8         |                         | SPI1 Event Int                       | , ,               |                  |                  |                 |         |

|                  | 111 = Interru           | pt is Priority 7 (                   | highest priority  | interrupt)       |                  |                 |         |

|                  | •                       |                                      |                   |                  |                  |                 |         |

|                  | •<br>001 = Interru      | pt is Priority 1                     |                   |                  |                  |                 |         |

|                  | 000 = Interru           | pt source is dis                     | abled             |                  |                  |                 |         |

| bit 7            | Unimplemen              | ted: Read as '                       | )'                |                  |                  |                 |         |

| bit 6-4          | SPF1IP<2:0>             | : SPI1 Fault Inf                     | errupt Priority I | oits             |                  |                 |         |

|                  | 111 = Interru           | pt is Priority 7 (                   | highest priority  | interrupt)       |                  |                 |         |

|                  | •                       |                                      |                   |                  |                  |                 |         |

|                  | •                       |                                      |                   |                  |                  |                 |         |

|                  | 001 = Interru           | pt is Priority 1<br>pt source is dis | abled             |                  |                  |                 |         |

|                  | -                       | ted: Read as '                       |                   |                  |                  |                 |         |

| hit 3            |                         | imer3 Interrupt                      |                   |                  |                  |                 |         |

|                  |                         |                                      | •                 | interrunt)       |                  |                 |         |

|                  | 111 = Interru           | nt is Priority 7 (                   |                   |                  |                  |                 |         |

|                  | 111 = Interruj<br>•     | pt is Priority 7 (                   | nignest priority  | interrupt)       |                  |                 |         |

| bit 3<br>bit 2-0 | 111 = Interruj<br>•     | pt is Priority 7 (                   | nignest priority  | interrupt)       |                  |                 |         |

|                  | •<br>•<br>001 = Interru |                                      |                   | interrupt)       |                  |                 |         |

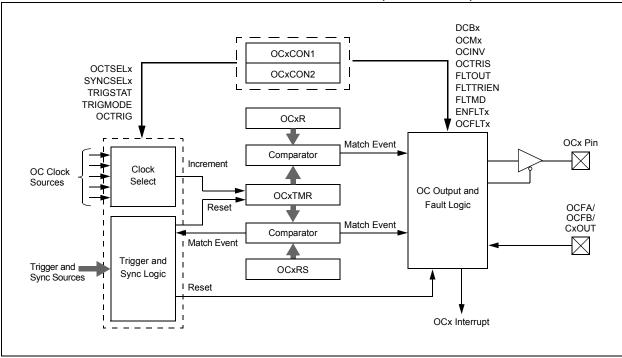

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

### 15.4 Subcycle Resolution

The DCBx bits (OCxCON2<10:9>) provide for resolution better than one instruction cycle. When used, they delay the falling edge generated from a match event by a portion of an instruction cycle.

For example, setting DCB<1:0> = 10 causes the falling edge to occur halfway through the instruction cycle in which the match event occurs, instead of at the beginning. These bits cannot be used when OCM<2:0> = 001. When operating the module in PWM mode (OCM<2:0> = 110 or 111), the DCBx bits will be double-buffered. The DCBx bits are intended for use with a clock source identical to the system clock. When an OCx module with enabled prescaler is used, the falling edge delay caused by the DCBx bits will be referenced to the system clock period, rather than the OCx module's period.

| PWM Frequency     | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-------------------|--------|-------|--------|--------|---------|----------|---------|

| Prescaler Ratio   | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Value      | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits) | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

| TADLE 13-2. EXAMPLE PWW FREQUENCIES AND RESULUTIONS AT 10 MIPS (FCY = 10 MID) | <b>TABLE 15-2</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz) <sup>(1)</sup> |

|-------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------|

| PWM Frequency     | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-------------------|---------|--------|--------|---------|----------|---------|---------|

| Prescaler Ratio   | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Value      | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits) | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

#### **REGISTER 15-1:** OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)

#### bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: Initialize OCx pin low; toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize OCx pin low; toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- **Note 1:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

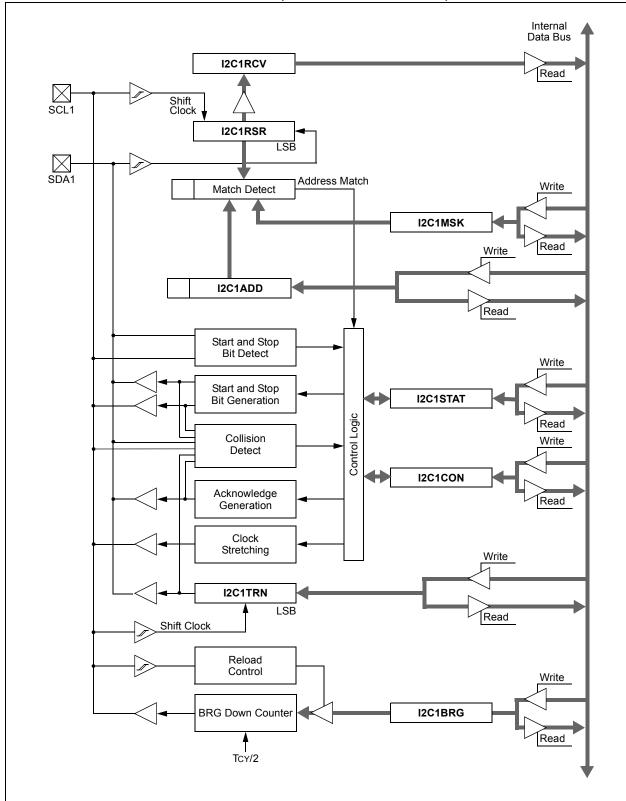

### FIGURE 17-1: I<sup>2</sup>C<sup>™</sup> BLOCK DIAGRAM (I2C1 MODULE IS SHOWN)

| R/W-0               | R/W-0                                                          | R/W-0                                                                                                                      | R/W-0                                            | r-0                                                    | U-0                     | R/W-0            | R/W-0          |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|-------------------------|------------------|----------------|

| ASEN <sup>(1)</sup> | LPEN                                                           | CTMREQ                                                                                                                     | BGREQ                                            | r                                                      | —                       | ASINT1           | ASINT0         |

| bit 15              |                                                                |                                                                                                                            |                                                  |                                                        |                         |                  | bit            |

| U-0                 | U-0                                                            | U-0                                                                                                                        | U-0                                              | R/W-0                                                  | R/W-0                   | R/W-0            | R/W-0          |

| _                   | —                                                              | —                                                                                                                          |                                                  | WM1                                                    | WM0                     | CM1              | CM0            |

| bit 7               |                                                                |                                                                                                                            |                                                  |                                                        |                         |                  | bit            |

| Legend:             |                                                                | r = Reserved                                                                                                               | bit                                              |                                                        |                         |                  |                |

| R = Readabl         | e bit                                                          | W = Writable                                                                                                               | oit                                              | U = Unimplem                                           | nented bit, read        | d as '0'         |                |

| -n = Value at       | POR                                                            | '1' = Bit is set                                                                                                           |                                                  | '0' = Bit is clea                                      | ared                    | x = Bit is unkr  | nown           |

| bit 15              | <b>ASEN:</b> Auto-<br>1 = Auto-sca<br>0 = Auto-sca             |                                                                                                                            | <sub>(</sub> (1)                                 |                                                        |                         |                  |                |

| bit 14              | 1 = Returns                                                    | Power Enable bi<br>to Low-Power n<br>s in Full-Power r                                                                     | node after sca                                   |                                                        |                         |                  |                |

| bit 13              | 1 = CTMU is                                                    | TMU Request b<br>s enabled when<br>s not enabled by                                                                        | the A/D is ena                                   | abled and active                                       |                         |                  |                |

| bit 12              | 1 = Band ga                                                    | nd Gap Requesi<br>p is enabled wh<br>p is not enabled                                                                      | en the A/D is                                    | enabled and act                                        | live                    |                  |                |

| bit 11              | Reserved: N                                                    | <b>laintain as</b> '0'                                                                                                     |                                                  |                                                        |                         |                  |                |

| bit 10              | Unimplemer                                                     | nted: Read as '                                                                                                            | )'                                               |                                                        |                         |                  |                |

| bit 9-8             | ASINT<1:0>                                                     | : Auto-Scan (Th                                                                                                            | reshold Detec                                    | t) Interrupt Mod                                       | e bits                  |                  |                |

|                     | 10 = Interru                                                   | pt after a Thresh<br>pt after a valid c<br>pt after a Thresh<br>errupt                                                     | ompare has o                                     | ccurred                                                |                         | compare has o    | occurred       |

| bit 7-4             | Unimplemer                                                     | nted: Read as '                                                                                                            | )'                                               |                                                        |                         |                  |                |

| bit 3-2             | 11 = Reserv<br>10 = Auto-co<br>match,<br>01 = Conver<br>when a | Vrite Mode bits<br>ved<br>ompare only (co<br>as defined by th<br>rt and save (cor<br>a match, as defin<br>v operation (con | ne CMx and A<br>oversion result<br>ned by the CM | SINTx bits, occu<br>s are saved to<br>lx bits, occurs) | urs)<br>locations as de | etermined by th  | ne register bi |

| bit 1-0             | CM<1:0>: Co                                                    | ompare Mode bi                                                                                                             | ts                                               |                                                        |                         |                  |                |

|                     | by the of<br>10 = Inside V<br>corresp<br>01 = Greate           | Window mode<br>corresponding bu<br>Window mode (v<br>ponding buffer pa<br>r Than mode (va<br>egister)                      | uffer pair)<br>alid match occ<br>ir)             | urs if the convers                                     | sion result is ins      | side the window  | defined by th  |

|                     |                                                                | han mode (valid                                                                                                            | match occurs                                     | if the result is le                                    | ss than the val         | ue in the corres | ponding buff   |

#### Note 1: When using auto-scan with Threshold Detect (ASEN = 1), do not configure the sample clock source to Auto-Convert mode (SSRCx = 7). Any other available SSRCx selection is valid. To use auto-convert as the sample clock source (SSRCx = 7), make sure ASEN is cleared.

| R/W-0                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                            | R/W-0                                                                                            | R/W-0                              | R/W-0           | R/W-0         |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|-----------------|---------------|

| CH0NB2                         | CH0NB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CH0NB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CH0SB4                                                                                                                                                                                           | CH0SB3                                                                                           | CH0SB2                             | CH0SB1          | CH0SB0        |

| bit 15                         | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |                                                                                                  | ·                                  |                 | bit           |

| R/W-0                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                            | R/W-0                                                                                            | R/W-0                              | R/W-0           | R/W-0         |