Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 39                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

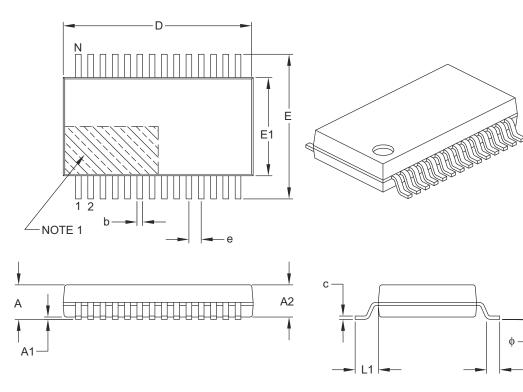

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka304t-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                       | U-0                                                                                                                                                            | U-0                                        | U-0             | U-0              | U-0                          | U-0              | R/W-0, HSC    |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|------------------|------------------------------|------------------|---------------|--|--|--|

| _                         | _                                                                                                                                                              | _                                          | —               | —                | —                            | —                | DC            |  |  |  |

| bit 15                    |                                                                                                                                                                |                                            |                 |                  |                              |                  | bit 8         |  |  |  |

|                           |                                                                                                                                                                |                                            |                 |                  |                              |                  |               |  |  |  |

| R/W-0, HSC <sup>(1)</sup> |                                                                                                                                                                | R/W-0, HSC <sup>(1)</sup>                  | R-0, HSC        | R/W-0, HSC       | R/W-0, HSC                   | R/W-0, HSC       | R/W-0, HSC    |  |  |  |

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>                                                                                                                                            | IPL0 <sup>(2)</sup>                        | RA              | Ν                | OV                           | Z                | С             |  |  |  |

| bit 7                     |                                                                                                                                                                |                                            |                 |                  |                              |                  | bit (         |  |  |  |

| Lagandi                   |                                                                                                                                                                | HSC = Hardwa                               | ra Cattabla/    | Nooroblo hit     |                              |                  |               |  |  |  |

| Legend:<br>R = Readable   | hit                                                                                                                                                            | W = Writable bi                            |                 |                  | mented bit, rea              | ad as 'O'        |               |  |  |  |

| -n = Value at P           |                                                                                                                                                                | '1' = Bit is set                           | ι               | '0' = Bit is cle |                              | x = Bit is unk   | nown          |  |  |  |

|                           | on                                                                                                                                                             |                                            |                 |                  | arca                         |                  |               |  |  |  |

| bit 15-9                  | Unimplemente                                                                                                                                                   | d: Read as '0'                             |                 |                  |                              |                  |               |  |  |  |

| bit 8                     | DC: ALU Half C                                                                                                                                                 |                                            |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | from the 4 <sup>th</sup> low-              | -order bit (foi | byte-sized da    | ta) or 8 <sup>th</sup> Iow-o | rder bit (for wo | rd-sized data |  |  |  |

|                           | of the resul                                                                                                                                                   |                                            | oth .           |                  |                              |                  |               |  |  |  |

|                           | -                                                                                                                                                              | ut from the 4 <sup>th</sup> or             |                 |                  | sult has occurr              | ed               |               |  |  |  |

| bit 7-5                   | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |                                            |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | errupt Priority Lev<br>errupt Priority Lev |                 | user interrupts  | s are disabled               |                  |               |  |  |  |

|                           |                                                                                                                                                                | errupt Priority Lev                        |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | errupt Priority Lev                        |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | errupt Priority Lev                        |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | errupt Priority Lev                        |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | errupt Priority Lev                        |                 |                  |                              |                  |               |  |  |  |

| bit 4                     | RA: REPEAT LC                                                                                                                                                  | errupt Priority Lev                        |                 |                  |                              |                  |               |  |  |  |

| bit 4                     | $1 = \text{REPEAT} \log 1$                                                                                                                                     | -                                          |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | p not in progress                          | S               |                  |                              |                  |               |  |  |  |

| bit 3                     | N: ALU Negativ                                                                                                                                                 | e bit                                      |                 |                  |                              |                  |               |  |  |  |

|                           | 1 = Result was                                                                                                                                                 | •                                          |                 |                  |                              |                  |               |  |  |  |

|                           |                                                                                                                                                                | non-negative (ze                           | ero or positiv  | ve)              |                              |                  |               |  |  |  |

| bit 2                     | OV: ALU Overfl                                                                                                                                                 |                                            |                 |                  |                              |                  |               |  |  |  |

|                           | 1 = Overflow or<br>0 = No overflow                                                                                                                             | curred for signe                           | d (2's compl    | ement) arithme   | etic in this arith           | nmetic operatio  | on            |  |  |  |

| bit 1                     | <b>Z:</b> ALU Zero bit                                                                                                                                         |                                            |                 |                  |                              |                  |               |  |  |  |

|                           | 1 = An operatio                                                                                                                                                | n, which effects                           |                 |                  |                              |                  | esult)        |  |  |  |

| bit 0                     | <b>C:</b> ALU Carry/B                                                                                                                                          |                                            |                 |                  | × ×                          | ,                | ,             |  |  |  |

|                           | 1 = A carry-out                                                                                                                                                | from the Most S<br>at from the Most        |                 |                  |                              |                  |               |  |  |  |

| Note 1: The               | IPLx Status bits                                                                                                                                               | are read-onlv wh                           | en NSTDIS       | (INTCON1<1       | 5>) = 1.                     |                  |               |  |  |  |

|                           | IPL<2:0> Status                                                                                                                                                | •                                          |                 |                  |                              | o form the CPL   | J Interrupt   |  |  |  |

|                           | rity I aval (IPI ) T                                                                                                                                           |                                            |                 |                  |                              |                  |               |  |  |  |

Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| IADLL        | <del>4</del> -J. |        |         |         |         |        | JULK     |          |          |       |          |          |          |         |          |          |          |               |

|--------------|------------------|--------|---------|---------|---------|--------|----------|----------|----------|-------|----------|----------|----------|---------|----------|----------|----------|---------------|

| File<br>Name | Addr             | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| INTCON1      | 0080             | NSTDIS | _       | —       | —       | —      | _        | —        | —        | —     | —        | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082             | ALTIVT | DISI    | -       | _       | _      |          | _        | _        | _     | _        |          | _        | _       | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084             | NVMIF  | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF   | SPF1IF   | T3IF     | T2IF  | OC2IF    | IC2IF    | —        | T1IF    | OC1IF    | IC1IF    | INT0IF   | 0000          |

| IFS1         | 0086             | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | _        | OC3IF    | _        | _     | _        | _        | INT1IF   | CNIF    | CMIF     | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 8800             | _      | _       | _       | _       | _      | _        | _        | _        | -     | _        | IC3IF    | _        | _       | _        | SPI2IF   | SPF2IF   | 0000          |

| IFS3         | 008A             | _      | RTCIF   | _       | _       | _      | _        | _        | _        | -     | _        | _        | _        | _       | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C             | -      | _       | CTMUIF  | —       | —      |          | —        | HLVDIF   |       | —        | _        | _        | CRCIF   | U2ERIF   | U1ERIF   |          | 0000          |

| IFS5         | 008E             |        | —       |         | _       | _      |          | —        | —        |       | —        |          | _        | —       |          | —        | ULPWUIF  | 0000          |

| IEC0         | 0094             | NVMIE  | _       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE   | SPF1IE   | T3IE     | T2IE  | OC2IE    | IC2IE    | _        | T1IE    | OC1IE    | IC1IE    | INT0IE   | 0000          |

| IEC1         | 0096             | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | _        | OC3IE    | _        | -     | _        | _        | INT1IE   | CNIE    | CMIE     | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098             | _      | _       | _       | _       | _      | _        | _        | _        | -     | _        | IC3IE    | _        | _       | _        | SPI2IE   | SPF2IE   | 0000          |

| IEC3         | 009A             | _      | RTCIE   | _       | _       | _      | _        | _        | _        | -     | _        | _        | _        | _       | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C             |        | —       | CTMUIE  | _       | _      |          | —        | HLVDIE   |       | —        |          | _        | CRCIE   | U2ERIE   | U1ERIE   |          | 0000          |

| IEC5         | 009E             | _      | _       | _       | _       | _      | _        | _        | _        | -     | _        | _        | _        | _       | _        | _        | ULPWUIE  | 0000          |

| IPC0         | 00A4             |        | T1IP2   | T1IP1   | T1IP0   | _      | OC1IP2   | OC1IP1   | OC1IP0   |       | IC1IP2   | IC1IP1   | IC1IP0   | —       | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6             |        | T2IP2   | T2IP1   | T2IP0   | _      | OC2IP2   | OC2IP1   | OC2IP0   |       | IC2IP2   | IC2IP1   | IC2IP0   | —       |          | —        |          | 4444          |

| IPC2         | 00A8             |        | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2  | SPI1IP1  | SPI1IP0  |       | SPF1IP2  | SPF1IP1  | SPF1IP0  | —       | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA             |        | NVMIP2  | NVMIP1  | NVMIP0  | _      |          | —        | —        |       | AD1IP2   | AD1IP1   | AD1IP0   | —       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 4044          |

| IPC4         | 00AC             |        | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2    | CMIP1    | CMIP0    |       | MI2C1P2  | MI2C1P1  | MI2C1P0  | —       | SI2C1P2  | SI2C1P1  | SI2C1P0  | 4444          |

| IPC5         | 00AE             |        | _       |         | _       | _      |          | —        | —        |       | —        |          | _        | —       | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0             |        | T4IP2   | T4IP1   | T4IP0   | _      |          | —        | —        |       | OC3IP2   | OC3IP1   | OC3IP0   | —       |          | —        |          | 4040          |

| IPC7         | 00B2             |        | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2  | U2RXIP1  | U2RXIP0  |       | INT2IP2  | INT2IP1  | INT2IP0  | —       | T5IP2    | T5IP1    | T5IP0    | 4440          |

| IPC8         | 00B4             |        | _       |         | _       | _      |          | —        | —        |       | SPI2IP2  | SPI2IP1  | SPI2IP0  | —       | SPF2IP2  | SPF2IP1  | SPF2IP0  | 0044          |

| IPC9         | 00B6             |        | _       |         | _       | _      |          | —        | —        |       | IC3IP2   | IC3IP1   | IC3IP0   | —       |          | —        |          | 0040          |

| IPC12        | 00BC             | -      | _       |         | —       | —      | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 |       | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | —       |          | —        |          | 0440          |

| IPC15        | 00C2             | _      | _       | _       | _       | _      | RTCIP2   | RTCIP1   | RTCIP0   | -     | _        | _        | _        | _       | _        | _        | _        | 0400          |

| IPC16        | 00C4             | _      | CRCIP2  | CRCIP1  | CRCIP0  | _      | U2ERIP2  | U2ERIP1  | U2ERIP0  | -     | U1ERIP2  | U1ERIP1  | U1ERIP0  | _       | _        | _        | _        | 4440          |

| IPC18        | 00C8             | -      |         |         | —       | —      |          | _        | _        | _     | —        |          | _        | _       | HLVDIP2  | HLVDIP1  | HLVDIP0  | 0004          |

| IPC19        | 00CA             | -      |         |         | —       | —      |          | _        | _        | _     | CTMUIP2  | CTMUIP1  | CTMUIP0  | _       | _        | —        | _        | 0040          |

| IPC20        | 00CC             | _      | _       |         | _       |        |          | _        |          | —     |          |          |          |         | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 | 0000          |

| INTTREG      | 00E0             | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

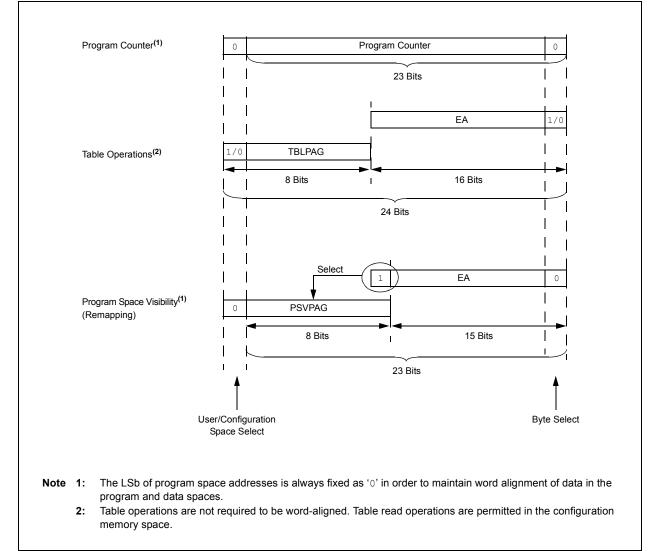

|                                       | Access        | Program Space Address |                         |                                                 |                                                                                           |     |  |  |  |

|---------------------------------------|---------------|-----------------------|-------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|-----|--|--|--|

| Access Type                           | Space         | <23>                  | <22:16>                 | <15>                                            | <14:1><br>xxxx xxx0<br>Data EA<15:0><br>xxxx xxxx xx<br>Data EA<15:0><br>xxxx xxxx xxxx x | <0> |  |  |  |

| Instruction Access                    | User          | 0                     |                         | PC<22:1>                                        |                                                                                           | 0   |  |  |  |

| (Code Execution)                      |               |                       | 0xx xxxx xxxx xxxx xxx0 |                                                 |                                                                                           |     |  |  |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TBL                   | _PAG<7:0>               | Data EA<15:0>                                   |                                                                                           |     |  |  |  |

|                                       |               | 0 x                   | XXX XXXX                | XXXX XXXX XXXX XXXX                             |                                                                                           |     |  |  |  |

|                                       | Configuration | TBL                   | TBLPAG<7:0>             |                                                 | Data EA<15:0>                                                                             |     |  |  |  |

|                                       |               | 1x                    | XXX XXXX                | XXXX XXXX XXXX XXXX                             |                                                                                           |     |  |  |  |

| Program Space Visibility              | User          | 0                     | PSVPAG<7                | :0> <sup>(2)</sup> Data EA<14:0> <sup>(1)</sup> |                                                                                           |     |  |  |  |

| (Block Remap/Read)                    |               | 0                     | XXXX XX                 | XXX                                             | x xxx xxxx xxxx xxxx                                                                      |     |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) in the PIC24FV32KA304 family.

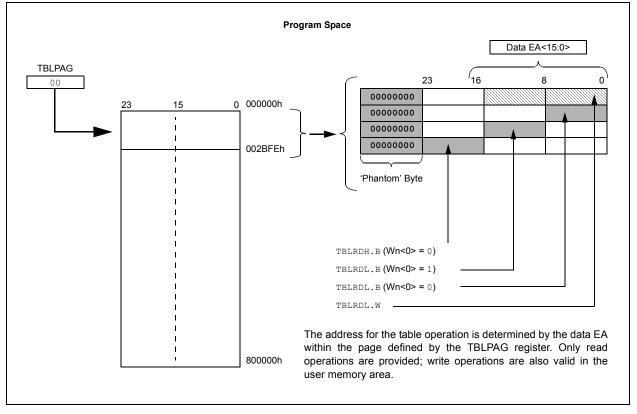

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

#### FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | —   | —   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/0 | Clearable bit              |                    |

|-------------------|---------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

| bit 7 5 | IPL<2:0>: CPU Interrupt Priority Level              | Status hits (2,3) |

|---------|-----------------------------------------------------|-------------------|

| bit 7-5 | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level | Status Dits       |

- 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- **3:** The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

| U-0                               | R/W-1                                                                                                                     | R/W-0                                 | R/W-0            | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

|                                   | NVMIP2                                                                                                                    | NVMIP1                                | NVMIP0           |                   |                  |                 |         |  |  |  |  |  |

| bit 15                            |                                                                                                                           |                                       |                  |                   |                  |                 | bit     |  |  |  |  |  |

|                                   |                                                                                                                           |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

| U-0                               | R/W-1                                                                                                                     | R/W-0                                 | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|                                   | AD1IP2                                                                                                                    | AD1IP1                                | AD1IP0           | —                 | U1TXIP2          | U1TXIP1         | U1TXIP0 |  |  |  |  |  |

| bit 7                             |                                                                                                                           |                                       |                  |                   |                  |                 | bit     |  |  |  |  |  |

| Legend:                           |                                                                                                                           |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                           |                                       | bit              | U = Unimplei      | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a                      | at POR                                                                                                                    | '1' = Bit is set                      |                  | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |  |  |  |  |  |

|                                   |                                                                                                                           |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 15                            | -                                                                                                                         | ted: Read as '                        |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12                         |                                                                                                                           | : NVM Interrup                        |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   | 111 = Interru                                                                                                             | pt is Priority 7 (                    | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

|                                   | •                                                                                                                         |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   | •<br>001 = Interru                                                                                                        | pt is Priority 1                      |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   |                                                                                                                           | pt source is dis                      | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 11-7                          |                                                                                                                           | ,<br>ited: Read as '                  |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4                           | AD1IP<2:0>:                                                                                                               | A/D Conversio                         | n Complete In    | nterrupt Priority | bits             |                 |         |  |  |  |  |  |

|                                   | AD1IP<2:0>: A/D Conversion Complete Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   | •                                                                                                                         |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   | •                                                                                                                         |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   | 001 = Interrupt is Priority 1                                                                                             |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|                                   |                                                                                                                           | pt source is dis                      |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 3                             | Unimplemen                                                                                                                | ted: Read as '                        | 0'               |                   |                  |                 |         |  |  |  |  |  |

|                                   |                                                                                                                           | : UART1 Trans                         |                  | •                 |                  |                 |         |  |  |  |  |  |

| bit 2-0                           |                                                                                                                           |                                       |                  | (intermed)        |                  |                 |         |  |  |  |  |  |

| bit 2-0                           | 111 = Interru                                                                                                             | pt is Priority 7 (                    | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

| bit 2-0                           | 111 = Interru<br>•                                                                                                        | pt is Priority 7(                     | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

| bit 2-0                           |                                                                                                                           | pt is Priority 7(<br>pt is Priority 1 | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-20: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0                               | U-0                                                                 | U-0                                                          | U-0                                | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |

|-----------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|-------------------|------------------|-----------------|----------|--|--|

| —                                 |                                                                     |                                                              | —                                  |                   | MI2C2IP2         | MI2C2IP1        | MI2C2IP0 |  |  |

| bit 15                            |                                                                     |                                                              |                                    |                   |                  |                 | bit 8    |  |  |

| U-0                               | R/W-1                                                               | R/W-0                                                        | R/W-0                              | U-0               | U-0              | U-0             | U-0      |  |  |

|                                   | SI2C2IP2                                                            | SI2C2IP1                                                     | SI2C2IP0                           |                   |                  |                 | <u> </u> |  |  |

| bit 7                             |                                                                     |                                                              |                                    |                   |                  |                 | bit 0    |  |  |

|                                   |                                                                     |                                                              |                                    |                   |                  |                 |          |  |  |

| Legend:                           |                                                                     |                                                              |                                    |                   |                  |                 |          |  |  |

| R = Readable bit W = Writable bit |                                                                     |                                                              | bit                                | •                 | nented bit, read |                 |          |  |  |

| -n = Value at POR '1' = E         |                                                                     | '1' = Bit is set                                             |                                    | '0' = Bit is clea | ared             | x = Bit is unkn | iown     |  |  |

| bit 15-11                         | Unimplemen                                                          | ted: Read as '                                               | )'                                 |                   |                  |                 |          |  |  |

| bit 10-8                          | MI2C2IP <2:0                                                        | >: Master I2C2                                               | Event Interru                      | pt Priority bits  |                  |                 |          |  |  |

|                                   | •<br>•<br>001 = Interrup                                            | ot is Priority 7 (l<br>ot is Priority 1<br>ot source is disa |                                    | r interrupt)      |                  |                 |          |  |  |

|                                   | 000 = Interru                                                       | Unimplemented: Read as '0'                                   |                                    |                   |                  |                 |          |  |  |

| bit 7                             | •                                                                   | ted: Read as '                                               | )'                                 |                   |                  |                 |          |  |  |

| bit 7<br>bit 6-4                  | Unimplemen                                                          | ted: Read as 'd<br>>: Slave I2C2 E                           |                                    | Priority bits     |                  |                 |          |  |  |

|                                   | Unimplement<br>SI2C2IP<2:0><br>111 = Interrup<br><br>001 = Interrup | •: Slave I2C2 E<br>ot is Priority 7 (I                       | vent Interrupt<br>nighest priority |                   |                  |                 |          |  |  |

#### 10.3 Ultra Low-Power Wake-up

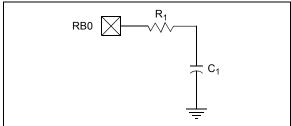

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source. See Example 10-3 for initializing the ULPWU module.

A series resistor, between RB0 and the external capacitor, provides overcurrent protection for the RB0/AN0/ULPWU pin and enables software calibration of the time-out (see Figure 10-1).

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

#### EXAMPLE 10-3: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//*******************************

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1:

for(i = 0; i < 10000; i++) Nop();</pre>

//*******

//2. Stop Charging the capacitor

// on RBO

//********************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

TEC5bits.ULPWUTE = 1:

IPC21bits.ULPWUIP = 0x7;

//********

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//********

//5. Enter Sleep Mode

//********************************

Sleep();

//for sleep, execution will

//resume here

```

| R/W-0              | U-0                                                                                                                         | R/W-0                                                                  | U-0                   | U-0               | U-0             | U-0                  | U-0         |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|-------------------|-----------------|----------------------|-------------|--|--|--|--|--|--|

| TON <sup>(1)</sup> | 0-0                                                                                                                         | TSIDL <sup>(1)</sup>                                                   | 0-0                   | 0-0               | 0-0             | 0-0                  | 0-0         |  |  |  |  |  |  |

| bit 15             |                                                                                                                             | TSIDL                                                                  |                       | _                 |                 |                      | <br>bit 8   |  |  |  |  |  |  |

|                    |                                                                                                                             |                                                                        |                       |                   |                 |                      | bit c       |  |  |  |  |  |  |

| U-0                | R/W-0                                                                                                                       | R/W-0                                                                  | R/W-0                 | U-0               | U-0             | R/W-0                | U-0         |  |  |  |  |  |  |

| _                  | TGATE <sup>(1)</sup>                                                                                                        | TCKPS1 <sup>(1)</sup>                                                  | TCKPS0 <sup>(1)</sup> |                   | _               | TCS <sup>(1)</sup>   |             |  |  |  |  |  |  |

| bit 7              |                                                                                                                             |                                                                        |                       |                   |                 |                      | bit 0       |  |  |  |  |  |  |

|                    |                                                                                                                             |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

| Legend:            |                                                                                                                             |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

| R = Reada          |                                                                                                                             | W = Writable                                                           | bit                   | -                 | nented bit, rea |                      |             |  |  |  |  |  |  |

| -n = Value         | at POR                                                                                                                      | '1' = Bit is set                                                       |                       | '0' = Bit is clea | ared            | x = Bit is unknow    | <u>ו</u>    |  |  |  |  |  |  |

| 1.11.45            |                                                                                                                             | o                                                                      |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 15             | TON: Timery                                                                                                                 |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    |                                                                                                                             | 1 = Starts 16-bit Timery<br>0 = Stops 16-bit Timery                    |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 14             | -                                                                                                                           | Unimplemented: Read as '0'                                             |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 13             | -                                                                                                                           |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | <b>TSIDL:</b> Timery Stop in Idle Mode bit <sup>(1)</sup><br>1 = Discontinues module operation when device enters Idle mode |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    |                                                                                                                             | 0 = Continues module operation in Idle mode                            |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 12-7           | Unimplemen                                                                                                                  | ted: Read as '0                                                        | )'                    |                   |                 |                      |             |  |  |  |  |  |  |

| bit 6              | TGATE: Time                                                                                                                 | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup> |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | When TCS = 1:                                                                                                               |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | This bit is ignored.                                                                                                        |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | <u>When TCS = 0:</u><br>1 = $Cated time conversion is enabled.$                                                             |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | <ul> <li>1 = Gated time accumulation is enabled</li> <li>0 = Gated time accumulation is disabled</li> </ul>                 |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 5-4            |                                                                                                                             | : Timery Input (                                                       |                       | Select hits(1)    |                 |                      |             |  |  |  |  |  |  |

| bit 0 4            | 11 = 1:256                                                                                                                  | . Thirdy input (                                                       |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | 10 = 1:64                                                                                                                   |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | 01 <b>= 1:8</b>                                                                                                             |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    | 00 = 1:1                                                                                                                    |                                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 3-2            | •                                                                                                                           | ted: Read as '0                                                        |                       |                   |                 |                      |             |  |  |  |  |  |  |

| bit 1              |                                                                                                                             | Clock Source S                                                         |                       |                   |                 |                      |             |  |  |  |  |  |  |

|                    |                                                                                                                             | clock is from th<br>clock (Fosc/2)                                     | e T3CK pin (o         | n the rising edg  | le)             |                      |             |  |  |  |  |  |  |

| bit 0              | Unimplemen                                                                                                                  | ted: Read as '                                                         | )'                    |                   |                 |                      |             |  |  |  |  |  |  |

| Note 1:            | When 22 hit ener                                                                                                            | ation is anabled                                                       |                       | - 1) those hite l | have no affact  | on Timon ( operation | - All timer |  |  |  |  |  |  |

#### REGISTER 13-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER

**Note 1:** When 32-bit operation is enabled (TxCON<3> = 1), these bits have no effect on Timery operation. All timer functions are set through the TxCON register.

### 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even numbered module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bit (ICxCON2<8>) for both modules.

### 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. If Synchronous mode is to be used, disable the Sync source before proceeding.

- 2. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 3. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired Sync/trigger source.

- Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSELx bits before the input capture module is enabled, for proper synchronization with the desired clock source.

- 5. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- 6. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 7. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 8. Enable the selected Sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same Sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bit settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the Sync source as the last step. Both input capture modules are held in Reset until the Sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the Sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

| R/W-0         | U-0                        | R/W-0                                          | R-0              | R-0               | R-0             | R-0             | R-0           |

|---------------|----------------------------|------------------------------------------------|------------------|-------------------|-----------------|-----------------|---------------|

| CRCEN         | <u> </u>                   | CSIDL                                          | VWORD4           | VWORD3            | VWORD2          | VWORD1          | VWORD0        |

| bit 15        |                            | COIDE                                          |                  |                   | VVV01102        |                 | bit 8         |

| bit 10        |                            |                                                |                  |                   |                 |                 | bit 0         |

| R-0, HSC      | R-1, HSC                   | R/W-0                                          | R/W-0, HC        | R/W-0             | U-0             | U-0             | U-0           |

| CRCFUL        | CRCMPT                     | CRCISEL                                        | CRCGO            | LENDIAN           | —               | —               | —             |

| bit 7         |                            |                                                | •                |                   |                 |                 | bit 0         |

|               |                            |                                                |                  |                   |                 |                 |               |

| Legend:       |                            | HC = Hardware                                  | Clearable bit    | HSC = Hardw       | are Settable/C  | Clearable bit   |               |

| R = Readabl   | e bit                      | W = Writable bit                               |                  | U = Unimplen      | nented bit, rea | ad as '0'       |               |

| -n = Value at | POR                        | '1' = Bit is set                               |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown          |

|               |                            |                                                |                  |                   |                 |                 |               |

| bit 15        | CRCEN: CR                  | C Enable bit                                   |                  |                   |                 |                 |               |

|               | 1 = Module<br>0 = Module   |                                                |                  |                   |                 |                 |               |

|               |                            | chines, pointers a                             | nd CRCWDAT/      | CRCDAT regist     | ers are reset:  | other SERs an   | e NOT reset.  |

| bit 14        |                            | nted: Read as '0'                              |                  |                   |                 |                 |               |

| bit 13        | -                          | C Stop in Idle Mod                             | e bit            |                   |                 |                 |               |

|               |                            | inues module ope                               |                  | vice enters Idle  | mode            |                 |               |

|               | 0 = Continu                | es module operat                               | ion in Idle mode | 9                 |                 |                 |               |

| bit 12-8      | VWORD<4:0                  | 0>: Pointer Value                              | bits             |                   |                 |                 |               |

|               |                            | e number of valid v<br>PLEN<4:0> $\leq$ 7.     | vords in the FIF | O, which has a    | maximum val     | ue of 8 when P  | PLEN<4:0> > 7 |

| bit 7         | CRCFUL: C                  | RC FIFO Full bit                               |                  |                   |                 |                 |               |

|               | 1 = FIFO is<br>0 = FIFO is |                                                |                  |                   |                 |                 |               |

| bit 6         | CRCMPT: C                  | RC FIFO Empty E                                | Bit              |                   |                 |                 |               |

|               | 1 = FIFO is                |                                                |                  |                   |                 |                 |               |

|               | 0 = FIFO is                |                                                |                  |                   |                 |                 |               |

| bit 5         |                            | CRC interrupt Sele                             |                  |                   |                 |                 |               |

|               | •                          | t on FIFO is empt<br>t on shift is compl       | •                |                   |                 |                 |               |

| bit 4         | CRCGO: Sta                 | -                                              |                  | DATTCSULTSTC      | auy             |                 |               |

|               |                            | RC serial shifter                              |                  |                   |                 |                 |               |

|               |                            | rial shifter is turne                          | ed off           |                   |                 |                 |               |

| bit 3         | LENDIAN: D                 | Data Shift Directio                            | n Select bit     |                   |                 |                 |               |

|               |                            | ord is shifted into t<br>ord is shifted into t |                  |                   |                 |                 |               |

| bit 2-0       | Unimplemer                 | nted: Read as '0'                              |                  |                   |                 |                 |               |

|               |                            |                                                |                  |                   |                 |                 |               |

#### REGISTER 20-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0         | U-0                                                                                                                                                                               | R/W-0                             | U-0             | U-0                 | U-0              | U-0              | U-0            |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|---------------------|------------------|------------------|----------------|--|--|--|

| HLVDEN        | _                                                                                                                                                                                 | HLSIDL                            |                 | —                   | —                | —                |                |  |  |  |

| bit 15        |                                                                                                                                                                                   |                                   |                 |                     |                  |                  | bit 8          |  |  |  |

|               |                                                                                                                                                                                   |                                   |                 |                     |                  |                  |                |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                             | R/W-0                             | U-0             | R/W-0               | R/W-0            | R/W-0            | R/W-0          |  |  |  |

| VDIR          | BGVST                                                                                                                                                                             | IRVST                             | —               | HLVDL3              | HLVDL2           | HLVDL1           | HLVDL0         |  |  |  |

| bit 7         |                                                                                                                                                                                   |                                   |                 |                     |                  |                  | bit C          |  |  |  |

| Legend:       |                                                                                                                                                                                   |                                   |                 |                     |                  |                  |                |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                             | W = Writable b                    | oit             | U = Unimplem        | nented bit, read | l as '0'         |                |  |  |  |

| -n = Value at | POR                                                                                                                                                                               | '1' = Bit is set                  |                 | '0' = Bit is clea   | ared             | x = Bit is unkn  | iown           |  |  |  |

|               |                                                                                                                                                                                   |                                   |                 |                     |                  |                  |                |  |  |  |

| bit 15        | HLVDEN: Hig                                                                                                                                                                       | gh/Low-Voltage                    | Detect Powe     | r Enable bit        |                  |                  |                |  |  |  |

|               | 1 = HLVD is                                                                                                                                                                       |                                   |                 |                     |                  |                  |                |  |  |  |

|               | 0 = HLVD is                                                                                                                                                                       |                                   |                 |                     |                  |                  |                |  |  |  |

| bit 14        | •                                                                                                                                                                                 | nted: Read as '0                  |                 |                     |                  |                  |                |  |  |  |

| bit 13        |                                                                                                                                                                                   | /D Stop in Idle N                 |                 |                     |                  |                  |                |  |  |  |

|               |                                                                                                                                                                                   | nues module op<br>es module opera |                 | device enters Id    | le mode          |                  |                |  |  |  |

| bit 12-8      |                                                                                                                                                                                   | ited: Read as '0                  |                 | ouc                 |                  |                  |                |  |  |  |

| bit 7         | -                                                                                                                                                                                 | e Change Direc                    |                 | t                   |                  |                  |                |  |  |  |

|               | -                                                                                                                                                                                 | -                                 |                 | exceeds trip poir   | nt (HLVDL<3:0>   | >)               |                |  |  |  |

|               |                                                                                                                                                                                   |                                   |                 | falls below trip po | •                | ,                |                |  |  |  |