#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka301-e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 3-1: CPU CORE | REGISTERS |

|---------------------|-----------|

|---------------------|-----------|

| Register(s) Name | Description                                    |  |  |  |  |

|------------------|------------------------------------------------|--|--|--|--|

| W0 through W15   | Working Register Array                         |  |  |  |  |

| PC               | 23-Bit Program Counter                         |  |  |  |  |

| SR               | ALU STATUS Register                            |  |  |  |  |

| SPLIM            | Stack Pointer Limit Value Register             |  |  |  |  |

| TBLPAG           | Table Memory Page Address Register             |  |  |  |  |

| PSVPAG           | Program Space Visibility Page Address Register |  |  |  |  |

| RCOUNT           | Repeat Loop Counter Register                   |  |  |  |  |

| CORCON           | CPU Control Register                           |  |  |  |  |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     |     | IPL3 <sup>(1)</sup> | PSV   | —   | _     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                                   |                    |  |  |

|-------------------|---------------------------------------|---------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared                              | x = Bit is unknown |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in data space                                                                                    |

|          | 0 = Program space is not visible in data space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

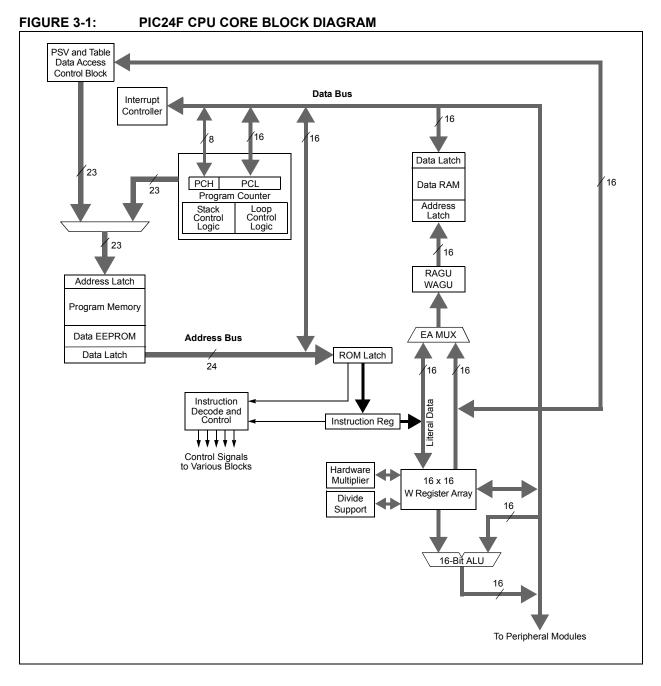

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Programming Executive (PE), to manage the programming process. Using an SPI data frame format, the Programming Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

## 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

## 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a program or erase operation, the processor stalls (Waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

|        | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | MI2C2IF   | SI2C2IF   | —     |

| bit 7 |     |     |     |     | •         |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | <b>Unimplemented:</b> Read as '0'                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | <b>RTCIF:</b> Real-Time Clock and Calendar Interrupt Flag Status bit                                                                       |

|          | <ol> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ol>                                     |

| bit 13-3 | Unimplemented: Read as '0'                                                                                                                 |

| bit 2    | MI2C2IF: Master I2C2 Event Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred       |

| bit 1    | <b>SI2C2IF:</b> Slave I2C2 Event Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |

| bit 0    | Unimplemented: Read as '0'                                                                                                                 |

## 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FV32KA304 family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High Accuracy mode

- Low-Power/Low Accuracy mode

The primary oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the primary oscillator.

## 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 26.1 "Configuration Bits"). The Primary Oscillator Configuration POSCMD<1:0> bits, (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The secondary oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

#### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSMx Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                   | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|---------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)     | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler (LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                    | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)              | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)   | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)   | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                           | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                           | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                           | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)     | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                        | Internal          | 11          | 000        | 1     |

TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 15.3.1 PWM PERIOD

In Edge-Aligned PWM mode, the period is specified by the value of the OCxRS register. In Center-Aligned PWM mode, the period of the synchronization source, such as the Timers' PRy, specifies the period. The period in both cases can be calculated using Equation 15-1.

## EQUATION 15-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period = [Value + 1] x TCY x (Prescaler Value)

Where:

Value = OCxRS in Edge-Aligned PWM mode and can be PRy in Center-Aligned PWM mode (if TMRy is the Sync source).

**Note 1:** Based on Tcy = Tosc \* 2; Doze mode and PLL are disabled.

## 15.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS and OCxR registers. The OCxRS and OCxR registers can be written to at any time, but the duty cycle value is not latched until a period is complete. This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation.

Some important boundary parameters of the PWM duty cycle include:

- Edge-Aligned PWM:

- If OCxR and OCxRS are loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than OCxR, the pin will remain high (100% duty cycle).

- Center-Aligned PWM (with TMRy as the Sync source):

- If OCxR, OCxRS and PRy are all loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than PRy, the pin will go high (100% duty cycle).

See Example 15-3 for PWM mode timing details. Table 15-1 and Table 15-2 show example PWM frequencies and resolutions for a device operating at 4 MIPS and 10 MIPS, respectively.

#### EQUATION 15-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

Maximum PWM Resolution (bits) =

$$\frac{\log_{10} \left( \frac{F_{CY}}{F_{PWM} \cdot (Prescale Value)} \right)}{\log_{10}(2)}$$

bits

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

#### EQUATION 15-3: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

Find the OCxRS register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a prescaler setting of 1:1 using Edge-Aligned PWM mode:

TCY = 2 • Tosc = 62.5 ns

PWM Period = 1/PWM Frequency = 1/52.08 kHz = 19.2 μs

PWM Period = (OCxRS + 1) • TCY • (OCx Prescale Value)

19.2 μs = (OCxRS + 1) • 62.5 ns • 1

OCxRS = 306

OCxRS = 306

Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution = log<sub>10</sub>(FCY/FPWM)/log<sub>10</sub>2) bits

= (log<sub>10</sub>(16 MHz/52.08 kHz)/log<sub>10</sub>2) bits

= 8.3 bits

= 8.3 bits

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

= 1/2

**Note 1:** Based on TCY = 2 \* TOSC; Doze mode and PLL are disabled.

## REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                 |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                          |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                         |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                     |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                    |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                               |

|       | 1 = Receive buffer has overflowed                                                                                                                                             |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the RSR to the empty state)    |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                    |

|       | <ul> <li>1 = Receive buffer has data; at least one more characters can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                |

© 2011-2013 Microchip Technology Inc.

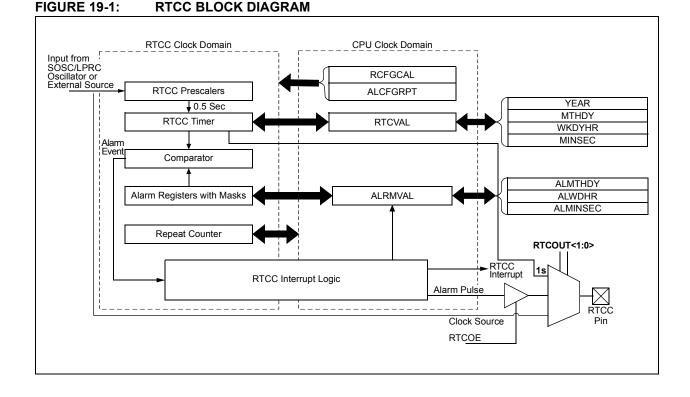

## 19.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", Section 29. "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- Operates in Deep Sleep mode

- Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- · Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long-term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long-term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

## 19.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

## © 2011-2013 Microchip Technology Inc.

| R/W-0         | U-0                                                                                                                                     | R/W-0                                                                                                                                                                               | R-0              | R-0               | R-0             | R-0             | R-0           |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------|---------------|--|--|--|

| CRCEN         | <u> </u>                                                                                                                                | CSIDL                                                                                                                                                                               | VWORD4           | VWORD3            | VWORD2          | VWORD1          | VWORD0        |  |  |  |

| bit 15        |                                                                                                                                         | COIDE                                                                                                                                                                               |                  |                   | V V U U U U     |                 | bit 8         |  |  |  |

| bit 10        |                                                                                                                                         |                                                                                                                                                                                     |                  |                   |                 |                 | bit o         |  |  |  |

| R-0, HSC      | R-1, HSC                                                                                                                                | R/W-0                                                                                                                                                                               | R/W-0, HC        | R/W-0             | U-0             | U-0             | U-0           |  |  |  |

| CRCFUL        | CRCMPT                                                                                                                                  | CRCISEL                                                                                                                                                                             | CRCGO            | LENDIAN           | —               | —               | —             |  |  |  |

| bit 7         | pit 7 bit                                                                                                                               |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

|               |                                                                                                                                         |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

| Legend:       |                                                                                                                                         | HC = Hardware                                                                                                                                                                       | Clearable bit    | HSC = Hardw       | are Settable/C  | Clearable bit   |               |  |  |  |

| R = Readabl   | e bit                                                                                                                                   | W = Writable bit                                                                                                                                                                    |                  | U = Unimplen      | nented bit, rea | ad as '0'       |               |  |  |  |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set                                                                                                                                                                    |                  | '0' = Bit is clea | ared            | x = Bit is unkr | iown          |  |  |  |

|               |                                                                                                                                         |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

| bit 15        | CRCEN: CR                                                                                                                               | C Enable bit                                                                                                                                                                        |                  |                   |                 |                 |               |  |  |  |

|               | 1 = Module                                                                                                                              |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

|               | 0 = Module                                                                                                                              | is enabled<br>chines, pointers a                                                                                                                                                    |                  |                   | ore aro rosot.  | other SERs ar   | o NOT reset   |  |  |  |

| bit 14        |                                                                                                                                         | nted: Read as '0'                                                                                                                                                                   |                  | SILEDAI TEGISI    |                 |                 | e nor reset.  |  |  |  |

| bit 13        | -                                                                                                                                       | C Stop in Idle Mod                                                                                                                                                                  | e hit            |                   |                 |                 |               |  |  |  |

| DIL 15        |                                                                                                                                         | •                                                                                                                                                                                   |                  | vice enters Idle  | mode            |                 |               |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

| bit 12-8      | VWORD<4:0                                                                                                                               | 0>: Pointer Value                                                                                                                                                                   | bits             |                   |                 |                 |               |  |  |  |

|               |                                                                                                                                         | number of valid v<br>PLEN<4:0> $\leq$ 7.                                                                                                                                            | vords in the FIF | O, which has a    | maximum val     | ue of 8 when F  | 2LEN<4:0> > 7 |  |  |  |

| bit 7         | CRCFUL: C                                                                                                                               | RC FIFO Full bit                                                                                                                                                                    |                  |                   |                 |                 |               |  |  |  |

|               |                                                                                                                                         | 1 = FIFO is full<br>0 = FIFO is not full                                                                                                                                            |                  |                   |                 |                 |               |  |  |  |

| bit 6         | CRCMPT: C                                                                                                                               | RC FIFO Empty E                                                                                                                                                                     | Bit              |                   |                 |                 |               |  |  |  |

|               | 1 = FIFO is empty                                                                                                                       |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

|               | 0 = FIFO is not empty                                                                                                                   |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

| bit 5         |                                                                                                                                         | CRC interrupt Sele                                                                                                                                                                  |                  |                   |                 |                 |               |  |  |  |

|               | •                                                                                                                                       | t on FIFO is empt                                                                                                                                                                   | •                |                   |                 |                 |               |  |  |  |

| bit 4         | 0 = Interrupt on shift is complete and CRCWDAT result is ready                                                                          |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

| Dit 4         | CRCGO: Start CRC bit<br>1 = Starts CRC serial shifter                                                                                   |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

|               | 0 = CRC serial shifter is turned off                                                                                                    |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

| bit 3         | LENDIAN: Data Shift Direction Select bit                                                                                                |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

|               |                                                                                                                                         | <ul> <li>1 = Data word is shifted into the CRC, starting with the LSb (little endian)</li> <li>0 = Data word is shifted into the CRC, starting with the MSb (big endian)</li> </ul> |                  |                   |                 |                 |               |  |  |  |

| bit 2-0       | Unimplemer                                                                                                                              | nted: Read as '0'                                                                                                                                                                   |                  |                   |                 |                 |               |  |  |  |

|               |                                                                                                                                         |                                                                                                                                                                                     |                  |                   |                 |                 |               |  |  |  |

## REGISTER 20-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                        | R/W-0                                                                                    | R/W-0                                                                                                                                                                                                                                                                     | R/W-0                  | R/W-0                                    | R/W-0          | U-0                 | U-0         |  |

|------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------|----------------|---------------------|-------------|--|

| PVCFG1                       | PVCFG0                                                                                   | NVCFG0                                                                                                                                                                                                                                                                    | OFFCAL                 | BUFREGEN                                 | CSCNA          | —                   | _           |  |

| bit 15                       |                                                                                          |                                                                                                                                                                                                                                                                           |                        |                                          |                |                     | bit 8       |  |

|                              |                                                                                          | DAALO                                                                                                                                                                                                                                                                     |                        |                                          | DAVA           | DANO                |             |  |

| R/W-0                        | R/W-0                                                                                    | R/W-0                                                                                                                                                                                                                                                                     | R/W-0                  | R/W-0                                    | R/W-0          | R/W-0               | R/W-0       |  |

| BUFS <sup>(1)</sup><br>bit 7 | SMPI4                                                                                    | SMPI3                                                                                                                                                                                                                                                                     | SMPI2                  | SMPI1                                    | SMPI0          | BUFM <sup>(1)</sup> | ALTS<br>bit |  |

|                              |                                                                                          |                                                                                                                                                                                                                                                                           |                        |                                          |                |                     |             |  |

| Legend:                      |                                                                                          |                                                                                                                                                                                                                                                                           |                        |                                          |                |                     |             |  |

| R = Reada                    | ble bit                                                                                  | W = Writable                                                                                                                                                                                                                                                              | bit                    | U = Unimplem                             | ented bit, rea | d as '0'            |             |  |

| -n = Value                   | at POR                                                                                   | '1' = Bit is set                                                                                                                                                                                                                                                          |                        | '0' = Bit is clea                        | red            | x = Bit is unkno    | own         |  |

| bit 15-14                    | <b>PVCFG&lt;1:0&gt;</b><br>11 = 4 * Inter<br>10 = 2 * Inter<br>01 = Externa<br>00 = AVDD | mal VBG <sup>(2)</sup><br>mal VBG <sup>(3)</sup>                                                                                                                                                                                                                          | sitive Voltage         | Reference Confi                          | guration bits  |                     |             |  |

| bit 13                       |                                                                                          | <b>NVCFG0:</b> Converter Negative Voltage Reference Configuration bits<br>1 = External VREF-                                                                                                                                                                              |                        |                                          |                |                     |             |  |

| bit 12                       | 1 = Inverting                                                                            | <ul> <li>OFFCAL: Offset Calibration Mode Select bit</li> <li>1 = Inverting and non-inverting inputs of channel Sample-and-Hold are connected to AVss</li> <li>0 = Inverting and non-inverting inputs of channel Sample-and-Hold are connected to normal inputs</li> </ul> |                        |                                          |                |                     |             |  |

| bit 11                       | 1 = Conversi                                                                             | <ul> <li>BUFREGEN: A/D Buffer Register Enable bit</li> <li>1 = Conversion result is loaded into a buffer location determined by the converted channel</li> <li>0 = A/D result buffer is treated as a FIFO</li> </ul>                                                      |                        |                                          |                |                     |             |  |

| bit 10                       | CSCNA: Sca<br>1 = Scans in<br>0 = Does not                                               | puts                                                                                                                                                                                                                                                                      | ons for CH0+           | S/H Input for MU                         | X A Setting b  | it                  |             |  |

| bit 9-8                      |                                                                                          | ted: Read as '                                                                                                                                                                                                                                                            | ר <b>י</b>             |                                          |                |                     |             |  |

| bit 7                        | •                                                                                        | Fill Status bit <sup>(1</sup>                                                                                                                                                                                                                                             |                        |                                          |                |                     |             |  |

|                              | 1 = A/D is fill                                                                          | ing the upper h                                                                                                                                                                                                                                                           | alf of the buff        | er; user should ac<br>er; user should ac |                |                     |             |  |

| bit 6-2                      |                                                                                          | Sample Rate In                                                                                                                                                                                                                                                            | •                      |                                          |                |                     |             |  |

|                              |                                                                                          |                                                                                                                                                                                                                                                                           |                        | ne conversion for<br>ne conversion for   |                |                     |             |  |

|                              |                                                                                          |                                                                                                                                                                                                                                                                           |                        | ne conversion for<br>ne conversion for   |                |                     |             |  |

| bit 1                        | BUFM: Buffe                                                                              | r Fill Mode Sele                                                                                                                                                                                                                                                          | ect bit <sup>(1)</sup> |                                          |                |                     |             |  |

|                              | interrupt<br>0 = Starts fil                                                              | (Split Buffer mo                                                                                                                                                                                                                                                          | ode)                   | 01BUF0, on the fi<br>ADCBUF0, and        |                |                     |             |  |

|                              | This is only applicused when BUFN                                                        |                                                                                                                                                                                                                                                                           | buffer is used         | l in FIFO mode (E                        | BUFREGEN =     | = 0). In addition,  | BUFS is onl |  |

| 2:                           | The voltage refer                                                                        | ence setting wi                                                                                                                                                                                                                                                           | ll not be withir       | n the specificatior                      | n with VDD be  | low 4.5V.           |             |  |

|                              |                                                                                          |                                                                                                                                                                                                                                                                           |                        |                                          |                |                     |             |  |

#### REGISTER 22-2: AD1CON2: A/D CONTROL REGISTER 2

3: The voltage reference setting will not be within the specification with VDD below 2.3V.

NOTES:

## 27.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 27.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 27.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta A/D, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 28.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |  |  |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |  |  |  |  |  |

|       | reference source.                          |  |  |  |  |  |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| DC CHARAG        | CTERISTICS             | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |        |            |                              |  |  |

|------------------|------------------------|-------------------------------------------------------|------|-------|--------|------------|------------------------------|--|--|

| Parameter<br>No. | Device                 | Typical <sup>(1)</sup>                                | Max  | Units |        | Conditions |                              |  |  |

| Module Diffe     | erential Current (AlPD | ) <sup>(3)</sup>                                      |      |       |        |            |                              |  |  |

| DC71             | PIC24FV32KA3XX         | 0.50                                                  |      | μA    | -40°C  | 2.0V       |                              |  |  |

|                  |                        | 0.70                                                  | 1.5  | μA    | +85°C  | 5.0V       |                              |  |  |

|                  |                        | —                                                     | 1.5  | μA    | +125°C | 5.0V       | Watchdog Timer<br>Current:   |  |  |

|                  | PIC24F32KA3XX          | 0.50                                                  |      | μA    | -40°C  | 1.8V       | ∆lwDT <sup>(4)</sup>         |  |  |

|                  |                        | 0.70                                                  | 1.5  | μA    | +85°C  | 3.3V       |                              |  |  |

|                  |                        | —                                                     | 1.5  | μA    | +125°C | 3.3V       |                              |  |  |

| DC72             | PIC24FV32KA3XX         | 0.80                                                  |      | μA    | -40°C  | 2.0V       |                              |  |  |

|                  |                        | 1.50                                                  | 2.0  | μA    | +85°C  | 5.0V       | 32 kHz Crystal with RTCC,    |  |  |

|                  |                        | —                                                     | 2.0  | μA    | +125°C | 5.0V       | DSWDT or Timer1:             |  |  |

|                  | PIC24F32KA3XX          | 0.70                                                  | —    | μA    | -40°C  | 1.8V       | ∆lsosc                       |  |  |

|                  |                        | 1.0                                                   | 1.5  | μA    | +85°C  | 3.3V       | (SOSCSEL = 0) <sup>(5)</sup> |  |  |

|                  |                        | —                                                     | 1.5  | μA    | +125°C | 3.3V       |                              |  |  |

| DC75             | PIC24FV32KA3XX         | 5.4                                                   | —    | μA    | -40°C  | 2.0V       |                              |  |  |

|                  |                        | 8.1                                                   | 14.0 | μA    | +85°C  | 5.0V       |                              |  |  |

|                  |                        | —                                                     | 14.0 | μA    | +125°C | 5.0V       | ∆IHLVD <sup>(4)</sup>        |  |  |

|                  | PIC24F32KA3XX          | 4.9                                                   | _    | μA    | -40°C  | 1.8V       |                              |  |  |

|                  |                        | 7.5                                                   | 14.0 | μA    | +85°C  | 3.3V       |                              |  |  |

|                  |                        | _                                                     | 14.0 | μA    | +125°C | 3.3V       |                              |  |  |

| DC76             | PIC24FV32KA3XX         | 5.6                                                   | _    | μA    | -40°C  | 2.0V       |                              |  |  |

|                  |                        | 6.5                                                   | 11.2 | μA    | -40°C  | 5.0V       |                              |  |  |

|                  |                        | —                                                     | 11.2 | μA    | +125°C | 5.0V       | ∆lbor <sup>(4)</sup>         |  |  |

|                  | PIC24F32KA3XX          | 5.6                                                   | —    | μA    | -40°C  | 1.8V       | ΔΙΒΟΚ' '                     |  |  |

|                  |                        | 6.0                                                   | 11.2 | μA    | +85°C  | 3.3V       |                              |  |  |

|                  |                        | —                                                     | 11.2 | μA    | +125°C | 3.3V       |                              |  |  |

#### TABLE 29-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

Legend: Unshaded rows represent PIC24F32KA3XX devices and shaded rows represent PIC24FV32KA3XX devices.

Note 1: Data in the Typical column is at 3.3V, +25°C (PIC24F32KA3XX) or 5.0V, +25°C (PIC24FV32KA3XX) unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and set low, PMSLP is set to '0' and WDT, etc., are all switched off.

3: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

4: This current applies to Sleep only.

5: This current applies to Sleep and Deep Sleep.

6: This current applies to Deep Sleep only.

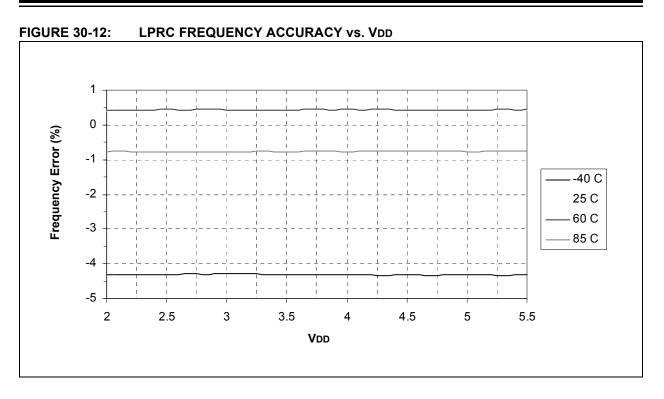

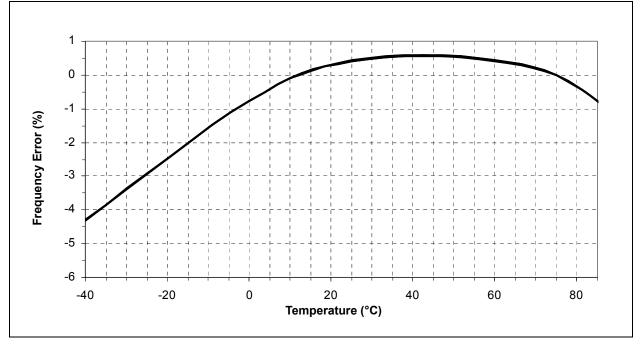

FIGURE 30-13: LPRC FREQUENCY ACCURACY vs. TEMPERATURE ( $2.0V \le VDD \le 5.5V$ )

FIGURE 30-48: TYPICAL AIHLVD VS. VDD

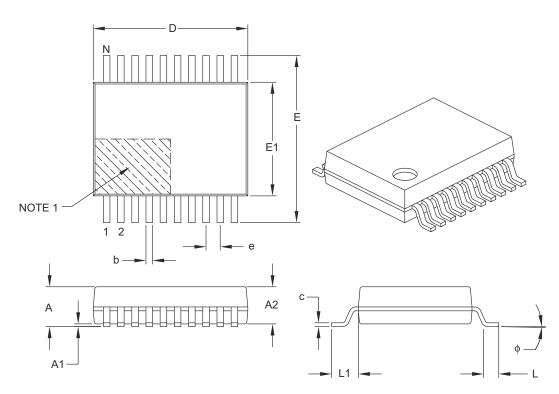

## 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      | 5    |  |

|--------------------------|------------------|----------|------|------|--|

| Dimer                    | Dimension Limits |          |      | MAX  |  |

| Number of Pins           | Ν                |          | 20   |      |  |

| Pitch                    | е                | 0.65 BSC |      |      |  |

| Overall Height           | А                | -        | -    | 2.00 |  |

| Molded Package Thickness | A2               | 1.65     | 1.75 | 1.85 |  |

| Standoff                 | A1               | 0.05     | -    | -    |  |

| Overall Width            | E                | 7.40     | 7.80 | 8.20 |  |

| Molded Package Width     | E1               | 5.00     | 5.30 | 5.60 |  |

| Overall Length           | D                | 6.90     | 7.20 | 7.50 |  |

| Foot Length              | L                | 0.55     | 0.75 | 0.95 |  |

| Footprint                | L1               | 1.25 REF |      |      |  |

| Lead Thickness           | С                | 0.09     | -    | 0.25 |  |

| Foot Angle               | φ                | 0°       | 4°   | 8°   |  |

| Lead Width b             |                  | 0.22     | _    | 0.38 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

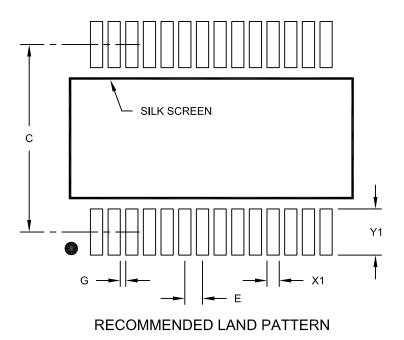

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |      |      |  |

|--------------------------|------------------|----------|------|------|--|

| Dimension                | Dimension Limits |          |      | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1               |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1               |          |      | 1.75 |  |

| Distance Between Pads    | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

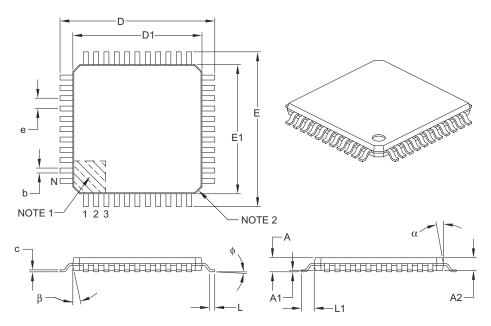

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |             |           | MILLIMETERS |  |  |  |

|--------------------------|------------------|-------------|-----------|-------------|--|--|--|

| Dime                     | Dimension Limits |             |           | MAX         |  |  |  |

| Number of Leads          | N                | 44          |           |             |  |  |  |

| Lead Pitch               | е                |             | 0.80 BSC  |             |  |  |  |

| Overall Height           | А                | -           | -         | 1.20        |  |  |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05        |  |  |  |

| Standoff                 | A1               | 0.05        | -         | 0.15        |  |  |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75        |  |  |  |

| Footprint                | L1               | 1.00 REF    |           |             |  |  |  |

| Foot Angle               | φ                | 0° 3.5° 7°  |           |             |  |  |  |

| Overall Width            | E                |             | 12.00 BSC |             |  |  |  |

| Overall Length           | D                |             | 12.00 BSC |             |  |  |  |

| Molded Package Width     | E1               |             | 10.00 BSC |             |  |  |  |

| Molded Package Length    | D1               | 10.00 BSC   |           |             |  |  |  |

| Lead Thickness           | С                | 0.09        | -         | 0.20        |  |  |  |

| Lead Width               | b                | 0.30        | 0.37      | 0.45        |  |  |  |

| Mold Draft Angle Top     | α                | 11°         | 12°       | 13°         |  |  |  |

| Mold Draft Angle Bottom  | β                | 11° 12° 13° |           |             |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support