#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

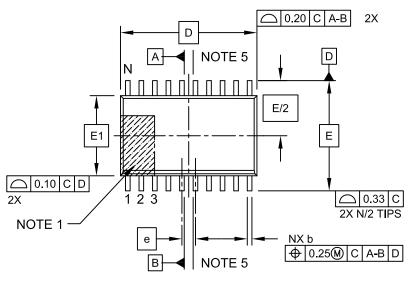

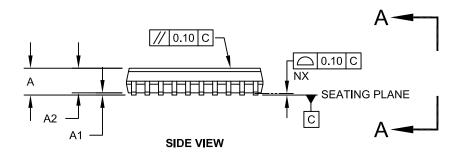

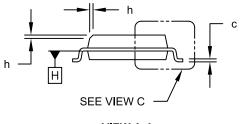

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 20-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka301-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CN23     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs                  |

| CN24     |                                  | 15                                | 12            | 42                     | 46             | -                                | 15                                | 12            | 42                     | 46             | 1   | ST     |                                             |

| CN25     |                                  | _                                 | _             | 37                     | 40             | -                                |                                   |               | 37                     | 40             | 1   | ST     |                                             |

| CN26     |                                  | _                                 | _             | 38                     | 41             |                                  |                                   |               | 38                     | 41             | I   | ST     |                                             |

| CN27     |                                  | 14                                | 11            | 41                     | 45             |                                  | 14                                | 11            | 41                     | 45             | I   | ST     |                                             |

| CN28     |                                  | _                                 | _             | 36                     | 39             |                                  |                                   |               | 36                     | 39             | I   | ST     |                                             |

| CN29     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ST     |                                             |

| CN30     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ST     |                                             |

| CN31     |                                  | _                                 | _             | 26                     | 28             | —                                | _                                 | —             | 26                     | 28             | I   | ST     |                                             |

| CN32     |                                  | _                                 | —             | 25                     | 27             | —                                | —                                 | —             | 25                     | 27             | 1   | ST     |                                             |

| CN33     |                                  | _                                 | —             | 32                     | 35             | —                                | —                                 | —             | 32                     | 35             | 1   | ST     |                                             |

| CN34     |                                  | _                                 | —             | 35                     | 38             | —                                | —                                 | —             | 35                     | 38             | I   | ST     |                                             |

| CN35     |                                  | _                                 | _             | 12                     | 13             | —                                | _                                 | —             | 12                     | 13             | I   | ST     |                                             |

| CN36     |                                  | _                                 | _             | 13                     | 14             | —                                | _                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CVREF    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA    | Comparator Reference Positive Input Voltage |

| CVREF-   | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA    | Comparator Reference Negative Input Voltage |

| CTCMP    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input                       |

| CTED1    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 2                                 | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     |                                             |

| CTED3    | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I   | ST     |                                             |

| CTED4    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 1   | ST     |                                             |

| CTED5    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ST     |                                             |

| CTED6    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     |                                             |

| CTED7    | _                                | _                                 | _             | 5                      | 5              | _                                | —                                 | _             | 5                      | 5              | I   | ST     |                                             |

| CTED8    | _                                | _                                 | —             | 13                     | 14             | —                                | —                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CTED9    | _                                | 22                                | 19            | 9                      | 10             | —                                | 22                                | 19            | 9                      | 10             | I   | ST     |                                             |

| CTED10   | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I   | ST     | ]                                           |

| CTED11   | _                                | 21                                | 18            | 8                      | 9              | —                                | 21                                | 18            | 8                      | 9              | I   | ST     | ]                                           |

| CTED12   | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | ]                                           |

| CTED13   | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | 1   | ST     | 1                                           |

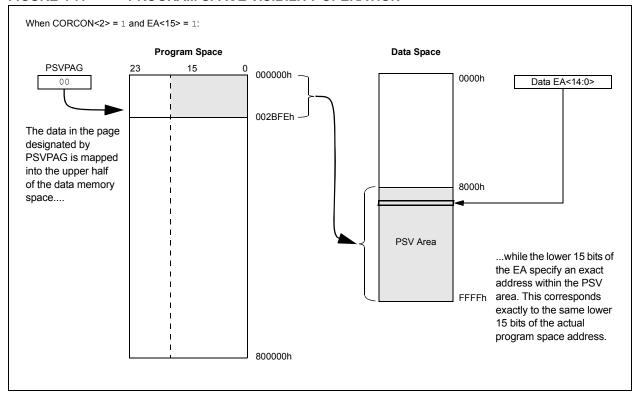

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into a 16K word page (in PIC24FV16KA3XX devices) and a 32K word page (in PIC24FV32KA3XX devices) of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space EA is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

# FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

# 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Data EEPROM, refer to the *"PIC24F Family Reference Manual"*, Section 5. "Data EEPROM" (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFFh. The size of the data EEPROM is 256 words in the PIC24FV32KA304 family devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

# 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

## 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

| //Disable Interr | upts For 5 instruc | ctions |

|------------------|--------------------|--------|

| asm volatile (   | "disi #5");        |        |

| //Issue Unlock S | equence            |        |

| asm volatile (   | "mov #0x55, W0     | \n"    |

| "                | mov W0, NVMKEY     | \n"    |

| "                | mov #0xAA, W1      | \n"    |

| "                | mov W1, NVMKEY     | \n");  |

| // Perform Write | /Erase operations  |        |

| asm volatile (   | "bset NVMCON, #WR  | \n"    |

| "                | nop                | \n"    |

| "                | nop                | \n");  |

|                  |                    |        |

#### REGISTER 8-21: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | R/W-1                                                                                                                             | R/W-0                                                                                                                                   | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| _            | CNIP2                                                                                                                             | CNIP1                                                                                                                                   | CNIP0             | _                | CMIP2            | CMIP1           | CMIP0   |  |  |  |  |  |  |

| bit 15       |                                                                                                                                   |                                                                                                                                         |                   |                  |                  |                 | bit 8   |  |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                             | R/W-0                                                                                                                                   | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

| —            | MI2C1P2                                                                                                                           | MI2C1P1                                                                                                                                 | MI2C1P0           | —                | SI2C1P2          | SI2C1P1         | SI2C1P0 |  |  |  |  |  |  |

| bit 7        |                                                                                                                                   |                                                                                                                                         |                   |                  |                  |                 | bit C   |  |  |  |  |  |  |

| Legend:      |                                                                                                                                   |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

| R = Readat   | ole bit                                                                                                                           | W = Writable                                                                                                                            | bit               | U = Unimple      | mented bit, read | d as '0'        |         |  |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                            | '1' = Bit is set                                                                                                                        |                   | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |  |  |  |  |  |  |

| -:. 4 C      |                                                                                                                                   | tad. Daad aa (                                                                                                                          | <u>.</u>          |                  |                  |                 |         |  |  |  |  |  |  |

| bit 15       | -                                                                                                                                 | ited: Read as '                                                                                                                         |                   | rupt Drigrity b  | ita              |                 |         |  |  |  |  |  |  |

| bit 14-12    |                                                                                                                                   | <b>CNIP&lt;2:0&gt;:</b> Input Change Notification Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | • •                                                                                                                               | puis Phonty 7 (                                                                                                                         | ingriest priority | mterrupt)        |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                                                                     |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | 000 = Interru                                                                                                                     | pt source is dis                                                                                                                        | abled             |                  |                  |                 |         |  |  |  |  |  |  |

| bit 11       | Unimplemen                                                                                                                        | ted: Read as '                                                                                                                          | 0'                |                  |                  |                 |         |  |  |  |  |  |  |

| bit 10-8     | CMIP<2:0>: Comparator Interrupt Priority bits                                                                                     |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | 111 = Interru                                                                                                                     | pt is Priority 7 (                                                                                                                      | highest priority  | interrupt)       |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 | untin Duinuity (                                                                                                                        |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                                   | pt is Priority 1<br>pt source is dis                                                                                                    | abled             |                  |                  |                 |         |  |  |  |  |  |  |

| bit 7        |                                                                                                                                   | ited: Read as '                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

| bit 6-4      | -                                                                                                                                 |                                                                                                                                         |                   | Priority hits    |                  |                 |         |  |  |  |  |  |  |

|              | <b>MI2C1P&lt;2:0&gt;:</b> Master I2C1 Event Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         | ingricor priority | interrupt)       |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                                   | pt is Priority 1<br>pt source is dis                                                                                                    | abled             |                  |                  |                 |         |  |  |  |  |  |  |

| bit 3        | Unimplemen                                                                                                                        | ted: Read as '                                                                                                                          | 0'                |                  |                  |                 |         |  |  |  |  |  |  |

| bit 2-0      | -                                                                                                                                 |                                                                                                                                         | vent Interrupt F  | riority bits     |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                                   |                                                                                                                                         | highest priority  | -                |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         | - · ·             | • •              |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                                 |                                                                                                                                         |                   |                  |                  |                 |         |  |  |  |  |  |  |

|              |                                                                                                                                   | pt is Priority 1<br>pt source is dis                                                                                                    |                   |                  |                  |                 |         |  |  |  |  |  |  |

| U-0           | U-0           | U-0                | U-0              | U-0               | U-0              | U-0      | U-0   |

|---------------|---------------|--------------------|------------------|-------------------|------------------|----------|-------|

| _             | —             | —                  | _                | —                 | —                | —        | —     |

| bit 15        |               |                    |                  |                   |                  |          | bit 8 |

|               |               |                    |                  |                   |                  |          |       |

| U-0           | R/W-1         | R/W-0              | R/W-0            | U-0               | U-0              | U-0      | U-0   |

| —             | IC3IP2        | IC3IP1             | IC3IP0           | —                 | —                | —        | —     |

| bit 7         |               |                    | •                |                   |                  | •        | bit 0 |

|               |               |                    |                  |                   |                  |          |       |

| Legend:       |               |                    |                  |                   |                  |          |       |

| R = Readable  | e bit         | W = Writable       | bit              | U = Unimplen      | nented bit, read | l as '0' |       |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea | x = Bit is unkn  | own      |       |

| bit 15-7      | Unimplemen    | ted: Read as '     | )'               |                   |                  |          |       |

| bit 6-4       | -             |                    |                  | nt Interrupt Prio | rity bite        |          |       |

| DIL 0-4       |               |                    |                  | -                 | They bits        |          |       |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | (interrupt)       |                  |          |       |

|               | •             |                    |                  |                   |                  |          |       |

|               | •             |                    |                  |                   |                  |          |       |

|               | 001 = Interru |                    |                  |                   |                  |          |       |

|               | 000 = Interru | pt source is dis   | abled            |                   |                  |          |       |

|               |               |                    |                  |                   |                  |          |       |

#### REGISTER 8-26: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

bit 3-0 Unimplemented: Read as '0'

## 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine tune the FRC oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC oscillator by a fixed amount.

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     |     | LOCK                    |     | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|----------------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit             |                    |  |  |  |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 15 Unimplemented: Read as '0'

#### bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 **NOSC<2:0>:** New Oscillator Selection bits<sup>(1)</sup>

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

#### **Note 1:** Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

|                                           |

# 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FV32KA304 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

# 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even numbered module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bit (ICxCON2<8>) for both modules.

# 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. If Synchronous mode is to be used, disable the Sync source before proceeding.

- 2. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 3. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired Sync/trigger source.

- Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSELx bits before the input capture module is enabled, for proper synchronization with the desired clock source.

- 5. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- 6. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 7. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 8. Enable the selected Sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same Sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bit settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the Sync source as the last step. Both input capture modules are held in Reset until the Sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the Sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

| R/W-0         | U-0                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0            | U-0               | U-0              | U-0              | U-0            |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|------------------|----------------|--|--|--|--|--|

| HLVDEN        | _                                                                                                                                                             | HLSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | _                 | —                |                  | —              |  |  |  |  |  |

| bit 15        |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  | bit 8          |  |  |  |  |  |

|               |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  |                |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0            | R/W-0             | R/W-0            | R/W-0            | R/W-0          |  |  |  |  |  |

| VDIR          | BGVST                                                                                                                                                         | IRVST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | HLVDL3            | HLVDL2           | HLVDL1           | HLVDL0         |  |  |  |  |  |

| bit 7         |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  | bit (          |  |  |  |  |  |

| Legend:       |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  |                |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                                         | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | oit            | U = Unimplerr     | nented bit, read | l as '0'         |                |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | '0' = Bit is clea | ared             | x = Bit is unkn  | iown           |  |  |  |  |  |

|               |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  |                |  |  |  |  |  |

| bit 15        | HLVDEN: Hi                                                                                                                                                    | gh/Low-Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Detect Powe    | r Enable bit      |                  |                  |                |  |  |  |  |  |

|               | 1 = HLVD is                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  |                |  |  |  |  |  |

|               | 0 = HLVD is                                                                                                                                                   | disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                   |                  |                  |                |  |  |  |  |  |

| bit 14        | Unimpleme                                                                                                                                                     | nted: Read as 'o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )'             |                   |                  |                  |                |  |  |  |  |  |

| bit 13        | HLSIDL: HL                                                                                                                                                    | VD Stop in Idle N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /lode bit      |                   |                  |                  |                |  |  |  |  |  |

|               | 1 = Disconti                                                                                                                                                  | nues module op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | eration when   | device enters Id  | le mode          |                  |                |  |  |  |  |  |

|               | 0 = Continue                                                                                                                                                  | es module opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tion in Idle m | ode               |                  |                  |                |  |  |  |  |  |

| bit 12-8      | Unimpleme                                                                                                                                                     | nted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )'             |                   |                  |                  |                |  |  |  |  |  |

| bit 7         | VDIR: Voltage Change Direction Select bit                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  |                |  |  |  |  |  |

|               |                                                                                                                                                               | curs when voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                   | •                | ·                |                |  |  |  |  |  |

| bit 6         |                                                                                                                                                               | nd Gap Voltage S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                   | ·                | ,                |                |  |  |  |  |  |

|               | 1 = Indicates                                                                                                                                                 | s that the band g<br>s that the band g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ap voltage is  | stable            |                  |                  |                |  |  |  |  |  |

| bit 5         | IRVST: Inter                                                                                                                                                  | nal Reference Vo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | oltage Stable  | Flag bit          |                  |                  |                |  |  |  |  |  |

|               |                                                                                                                                                               | s that the interna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                   | and the high-v   | oltage detect lo | ogic generates |  |  |  |  |  |

|               | the interrupt flag at the specified voltage range<br>0 = Indicates that the internal reference voltage is unstable and the high-voltage detect logic will not |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                   |                  |                  |                |  |  |  |  |  |

|               |                                                                                                                                                               | s that the internate the internate the interrupt flate the second s |                |                   |                  |                  |                |  |  |  |  |  |

|               | enabled                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ay at the spe  | cilled voltage la | nge, and the r   |                  |                |  |  |  |  |  |