#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 20-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka301t-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE I-I. DEVICE FEATO                            |                                      |                               |                             |                |                                              |                |

|----------------------------------------------------|--------------------------------------|-------------------------------|-----------------------------|----------------|----------------------------------------------|----------------|

| Features                                           | PIC24FV16KA301                       | PIC24FV32KA301                | PIC24FV16KA302              | PIC24FV32KA302 | PIC24FV16KA304                               | PIC24FV32KA304 |

| Operating Frequency                                |                                      |                               | DC – 32 I                   | MHz            |                                              |                |

| Program Memory (bytes)                             | 16K                                  | 32K                           | 16K                         | 32K            | 16K                                          | 32K            |

| Program Memory (instructions)                      | 5632                                 | 11264                         | 5632                        | 11264          | 5632                                         | 11264          |

| Data Memory (bytes)                                |                                      |                               | 2048                        |                |                                              |                |

| Data EEPROM Memory (bytes)                         |                                      |                               | 512                         |                |                                              |                |

| Interrupt Sources (soft vectors/<br>NMI traps)     |                                      |                               | 30 (26/                     | 4)             |                                              |                |

| I/O Ports                                          | PORTA<5:0><br>PORTB<15:12,9:7,4,2:0> |                               | PORTA<7,5:0><br>PORTB<15:0> |                | PORTA<11:7,5:0><br>PORTB<15:0><br>PORTC<9:0> |                |

| Total I/O Pins                                     | 17                                   | 7                             | 23                          |                | 3                                            | 8              |

| Timers: Total Number (16-bit)                      |                                      |                               | 5                           |                |                                              |                |

| 32-Bit (from paired 16-bit timers)                 |                                      |                               | 2                           |                |                                              |                |

| Input Capture Channels                             |                                      |                               | 3                           |                |                                              |                |

| Output Compare/PWM Channels                        |                                      |                               | 3                           |                |                                              |                |

| Input Change Notification Interrupt                | 16                                   | 6                             | 2                           | 2              | 3                                            | 7              |

| Serial Communications: UART<br>SPI (3-wire/4-wire) |                                      |                               | 2                           |                |                                              |                |

| I <sup>2</sup> C™                                  |                                      |                               | 2                           |                |                                              |                |

| 12-Bit Analog-to-Digital Module (input channels)   | 12                                   | 2                             | 1:                          | 3              | 1                                            | 6              |

| Analog Comparators                                 |                                      |                               | 3                           |                |                                              |                |

| Resets (and delays)                                |                                      | BOR, RESET<br>Instruction, Ha |                             | , Configurati  |                                              |                |

| Instruction Set                                    | 76 B                                 | ase Instructio                | ns, Multiple A              | ddressing M    | ode Variation                                | s              |

| Packages                                           | 20-F<br>PDIP/SSC                     |                               | 28-<br>SPDIP/SSOF           |                | 44-Pin QI<br>48-Pin                          |                |

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  | F                                 |               |                        |                |                                  | FV                                |               |                        |                |     |        |                                 |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|

|          | Pin Number                       |                                   |               |                        | Pin Number     |                                  |                                   |               |                        |                |     |        |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |

| T1CK     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | Т   | ST     | Timer1 Clock                    |

| T2CK     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | Ι   | ST     | Timer2 Clock                    |

| ТЗСК     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     | Timer3 Clock                    |

| T4CK     | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ST     | Timer4 Clock                    |

| T5CK     | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | Ι   | ST     | Timer5 Clock                    |

| U1CTS    | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-to-Send Input       |

| U1RTS    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 0   | _      | UART1 Request-to-Send Output    |

| U1RX     | 6                                | 6                                 | 3             | 2                      | 2              | 6                                | 6                                 | 3             | 2                      | 2              | I   | ST     | UART1 Receive                   |

| U1TX     | 11                               | 16                                | 13            | 3                      | 3              | 11                               | 16                                | 13            | 3                      | 3              | 0   | —      | UART1 Transmit                  |

| U2CTS    | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | Ι   | ST     | UART2 Clear-to-Send Input       |

| U2RTS    | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | 0   | _      | UART2 Request-to-Send Output    |

| U2RX     | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | UART2 Receive                   |

| U2TX     | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                  |

| ULPWU    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | Ultra Low-Power Wake-up Input   |

| VCAP     | _                                | —                                 | _             | —                      | _              | 14                               | 20                                | 17            | 7                      | 7              | Р   | —      | Core Power                      |

| Vdd      | 20                               | 28,13                             | 25,10         | 17,28,40               | 18,30,43       | 20                               | 28,13                             | 25,10         | 17,28,40               | 18,30,43       | Р   | —      | Device Digital Supply Voltage   |

| VREF+    | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | Ι   | ANA    | A/D Reference Voltage Input (+) |

| VREF-    | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Input (-) |

| Vss      | 19                               | 27,8                              | 24,5          | 16,29,39               | 17,31,42       | 19                               | 27,8                              | 24,5          | 16,29,39               | 17,31,42       | Р   | _      | Device Digital Ground Return    |

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC24FV32KA304 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

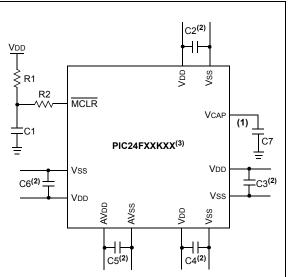

The minimum mandatory connections are shown in Figure 2-1.

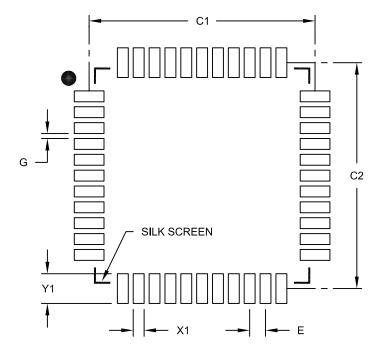

### FIGURE 2-1: RECOMMENDED

### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

**<sup>3:</sup>** Some PIC24F K parts do not have a regulator.

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal Voltage Regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal Voltage Regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE **CHARACTERISTICS** Change (%) 0 -10 16V Capacitor -20 -30 Capacitance -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 2 8 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the internal Voltage Regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 27.0 "Development Support"**.

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

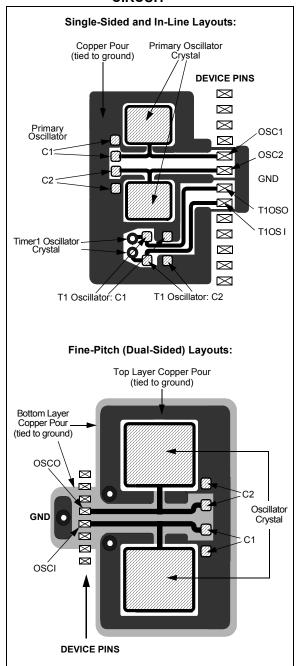

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

### FIGURE 2-5: SUGGESTED PLACEMENT

#### OF THE OSCILLATOR CIRCUIT

### 3.2 CPU Control Registers

### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                       | U-0                                                                                                                                                                                                                                                                                       | U-0                                 | U-0             | U-0              | U-0                          | U-0              | R/W-0, HSC    |  |  |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|------------------------------|------------------|---------------|--|--|--|--|--|--|

| _                         | _                                                                                                                                                                                                                                                                                         | _                                   | —               | —                | —                            | —                | DC            |  |  |  |  |  |  |

| bit 15                    |                                                                                                                                                                                                                                                                                           |                                     |                 |                  |                              |                  | bit 8         |  |  |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                           |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

| R/W-0, HSC <sup>(1)</sup> |                                                                                                                                                                                                                                                                                           | R/W-0, HSC <sup>(1)</sup>           | R-0, HSC        | R/W-0, HSC       | R/W-0, HSC                   | R/W-0, HSC       | R/W-0, HSC    |  |  |  |  |  |  |

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>                                                                                                                                                                                                                                                                       | IPL0 <sup>(2)</sup>                 | RA              | Ν                | OV                           | Z                | С             |  |  |  |  |  |  |

| bit 7                     |                                                                                                                                                                                                                                                                                           |                                     |                 |                  |                              |                  | bit (         |  |  |  |  |  |  |

| Lagandi                   |                                                                                                                                                                                                                                                                                           | HSC = Hardwa                        | ra Cattabla/    | Nooroblo hit     |                              |                  |               |  |  |  |  |  |  |

| Legend:<br>R = Readable   | hit                                                                                                                                                                                                                                                                                       | W = Writable bi                     |                 |                  | mented bit, rea              | ad as 'O'        |               |  |  |  |  |  |  |

| -n = Value at P           |                                                                                                                                                                                                                                                                                           | '1' = Bit is set                    | ι               | '0' = Bit is cle |                              | x = Bit is unk   | nown          |  |  |  |  |  |  |

|                           | on                                                                                                                                                                                                                                                                                        |                                     |                 |                  | arca                         |                  |               |  |  |  |  |  |  |

| bit 15-9                  | Unimplemente                                                                                                                                                                                                                                                                              | d: Read as '0'                      |                 |                  |                              |                  |               |  |  |  |  |  |  |

| bit 8                     | DC: ALU Half C                                                                                                                                                                                                                                                                            |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                           | -                                   | -order bit (foi | byte-sized da    | ta) or 8 <sup>th</sup> Iow-o | rder bit (for wo | rd-sized data |  |  |  |  |  |  |

|                           | <ul> <li>1 = A carry-out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-sized data) of the result occurred</li> <li>0 = No carry-out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> </ul> |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | -                                                                                                                                                                                                                                                                                         |                                     |                 |                  | sult has occurr              | ed               |               |  |  |  |  |  |  |

| bit 7-5                   | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                       |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                                                                                                                                                                                                                |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)                                                                                                                                                                                              |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 100 = CPU Interrupt Priority Level is 4 (12)                                                                                                                                                                                                                                              |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 011 = CPU Interrupt Priority Level is 3 (11)                                                                                                                                                                                                                                              |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 010 = CPU Interrupt Priority Level is 2 (10)                                                                                                                                                                                                                                              |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8)                                                                                                                                                                                                |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

| bit 4                     | RA: REPEAT LC                                                                                                                                                                                                                                                                             |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

| bit 4                     |                                                                                                                                                                                                                                                                                           | -                                   |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                            |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

| bit 3                     | N: ALU Negativ                                                                                                                                                                                                                                                                            | e bit                               |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 1 = Result was negative                                                                                                                                                                                                                                                                   |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                           | non-negative (ze                    | ero or positiv  | ve)              |                              |                  |               |  |  |  |  |  |  |

| bit 2                     | OV: ALU Overflow bit                                                                                                                                                                                                                                                                      |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | <ul> <li>1 = Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation</li> <li>0 = No overflow has occurred</li> </ul>                                                                                                                                       |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

| bit 1                     | <b>Z:</b> ALU Zero bit                                                                                                                                                                                                                                                                    |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

|                           | 1 = An operatio                                                                                                                                                                                                                                                                           | n, which effects                    |                 |                  |                              |                  | esult)        |  |  |  |  |  |  |

| bit 0                     | <b>C:</b> ALU Carry/B                                                                                                                                                                                                                                                                     |                                     |                 |                  | × ×                          | ,                | ,             |  |  |  |  |  |  |

|                           | 1 = A carry-out                                                                                                                                                                                                                                                                           | from the Most S<br>at from the Most |                 |                  |                              |                  |               |  |  |  |  |  |  |

| Note 1: The               | IPLx Status bits                                                                                                                                                                                                                                                                          | are read-onlv wh                    | en NSTDIS       | (INTCON1<1       | 5>) = 1.                     |                  |               |  |  |  |  |  |  |

|                           | IPL<2:0> Status                                                                                                                                                                                                                                                                           | •                                   |                 |                  |                              | o form the CPL   | J Interrupt   |  |  |  |  |  |  |

|                           | rity I aval (IPI ) T                                                                                                                                                                                                                                                                      |                                     |                 |                  |                              |                  |               |  |  |  |  |  |  |

Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

| R/W-0, HS   | S R/W-0, HS                       | R/W-0                                   | R/W-0                        | U-0               | R/C-0, HS          | R/W-0             | R/W-0          |

|-------------|-----------------------------------|-----------------------------------------|------------------------------|-------------------|--------------------|-------------------|----------------|

| TRAPR       | IOPUWR                            | SBOREN                                  | RETEN <sup>(3)</sup>         | —                 | DPSLP              | CM                | PMSLP          |

| bit 15      |                                   |                                         |                              |                   |                    |                   | bit 8          |

| R/W-0, H    | S R/W-0, HS                       | R/W-0, HS                               | R/W-0, HS                    | R/W-0, HS         | R/W-0, HS          | R/W-1, HS         | R/W-1, HS      |

| EXTR        | SWR                               | SWDTEN <sup>(2)</sup>                   | WDTO                         | SLEEP             | IDLE               | BOR               | POR            |

| bit 7       |                                   |                                         |                              |                   |                    |                   | bit 0          |

| <del></del> |                                   | <u> </u>                                |                              |                   |                    |                   |                |

| Legend:     |                                   | C = Clearable                           |                              |                   | re Settable bit    |                   |                |

| R = Reada   |                                   | W = Writable b                          | bit                          | •                 | nented bit, read   | as '0'            |                |

| -n = Value  | at POR                            | '1' = Bit is set                        |                              | '0' = Bit is cle  | ared               | x = Bit is unkn   | iown           |

| bit 15      | TRAPR: Tran                       | Reset Flag bit                          |                              |                   |                    |                   |                |

|             | =                                 | onflict Reset has                       | occurred                     |                   |                    |                   |                |

|             |                                   | onflict Reset has                       |                              |                   |                    |                   |                |

| bit 14      | IOPUWR: Ille                      | gal Opcode or l                         | Jninitialized W              | Access Reset      | Flag bit           |                   |                |

|             | 1 = An illegal<br>Pointer c       | l opcode detecti<br>aused a Reset       | on, an illegal a             | ddress mode o     | or Uninitialized V | V register used   | as an Address  |

|             | 0 = An illegal                    | I opcode or Unir                        | nitialized W Re              | set has not oc    | curred             |                   |                |

| bit 13      | SBOREN: So                        | oftware Enable/E                        | Disable of BOF               | R bit             |                    |                   |                |

|             |                                   | irned on in softw<br>irned off in softw |                              |                   |                    |                   |                |

| bit 12      | RETEN: Rete                       | ention Sleep Mo                         | de control bit <sup>(3</sup> | 6)                |                    |                   |                |

|             |                                   | d voltage supply<br>d voltage supply    |                              |                   |                    |                   |                |

| bit 11      | Unimplemen                        | ted: Read as '0                         | 3                            |                   |                    |                   |                |

| bit 10      | DPSLP: Deep                       | p Sleep Mode F                          | lag bit                      |                   |                    |                   |                |

|             | •                                 | ep has occurred<br>ep has not occu      |                              |                   |                    |                   |                |

| bit 9       | CM: Configur                      | ation Word Misr                         | natch Reset F                | lag bit           |                    |                   |                |

|             | Ų                                 | uration Word Mis<br>uration Word Mis    |                              |                   | ed                 |                   |                |

| bit 8       | PMSLP: Proc                       | gram Memory Po                          | ower During S                | leep bit          |                    |                   |                |

|             |                                   | memory bias vo<br>memory bias v<br>mode |                              |                   |                    | the Voltage Re    | gulator enters |

| bit 7       | -                                 | nal Reset (MCLF                         | R) Pin bit                   |                   |                    |                   |                |

| Sit 7       | 1 = A Master                      | Clear (pin) Reso<br>Clear (pin) Reso    | et has occurre               |                   |                    |                   |                |

| bit 6       |                                   | ire Reset (Instru                       |                              |                   |                    |                   |                |

|             | 1 <b>= A</b> reset                | instruction has I<br>instruction has I  | peen executed                |                   |                    |                   |                |

| Note 1:     | All of the Reset a cause a device |                                         | be set or clear              | ed in software.   | Setting one of the | nese bits in soft | ware does not  |

| 2:          | If the FWDTEN SWDTEN bit se       | x Configuration I                       | bit is '1' (unpro            | ogrammed), the    | e WDT is always    | enabled regar     | dless of the   |

| 3:          | This is implement                 | -                                       | V32KA3XX pa                  | arts only; not us | sed on PIC24F3     | 2KA3XX device     | es.            |

|             |                                   |                                         |                              |                   |                    |                   |                |

### REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

### REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0                                                                                                                           | U-0               | U-0              | U-0               | U-0                                   | U-0                | U-0              | U-0                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|---------------------------------------|--------------------|------------------|--------------------|--|--|

| —                                                                                                                             | —                 | —                | —                 | —                                     | —                  | —                | —                  |  |  |

| bit 15                                                                                                                        |                   |                  |                   |                                       |                    |                  | bit 8              |  |  |

|                                                                                                                               |                   |                  |                   |                                       |                    |                  |                    |  |  |

| U-0                                                                                                                           | U-0               | U-0              | U-0               | R/C-0, HSC                            | R/W-0              | U-0              | U-0                |  |  |

| _                                                                                                                             | —                 | —                | —                 | IPL3 <sup>(2)</sup>                   | PSV <sup>(1)</sup> | —                | —                  |  |  |

| bit 7                                                                                                                         |                   |                  |                   |                                       |                    |                  | bit 0              |  |  |

|                                                                                                                               |                   |                  |                   |                                       |                    |                  |                    |  |  |

| Legend:                                                                                                                       |                   | C = Clearable    | bit               | HSC = Hardware Settable/Clearable bit |                    |                  |                    |  |  |

| R = Readabl                                                                                                                   | e bit             | W = Writable     | bit               | U = Unimplemented bit, read as '0'    |                    |                  |                    |  |  |

| -n = Value at                                                                                                                 | POR               | '1' = Bit is set |                   | '0' = Bit is clea                     | ared               | x = Bit is unkr  | x = Bit is unknown |  |  |

|                                                                                                                               |                   |                  |                   |                                       |                    |                  |                    |  |  |

| bit 15-4                                                                                                                      | Unimplemen        | ted: Read as '   | )'                |                                       |                    |                  |                    |  |  |

| bit 3                                                                                                                         | IPL3: CPU In      | terrupt Priority | Level Status bi   | t <sup>(2)</sup>                      |                    |                  |                    |  |  |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |                   |                  |                   |                                       |                    |                  |                    |  |  |

| bit 1-0                                                                                                                       | Unimplemen        | ted: Read as '   | )'                |                                       |                    |                  |                    |  |  |

| Note 1: Se                                                                                                                    | ee Register 3-2   | for the descript | ion of this hit v | which is not der                      | dicated to inter   | runt control fun | ctions             |  |  |

|                                                                                                                               | ne IPL3 bit is co | -                |                   |                                       |                    | -                |                    |  |  |

|                                                                                                                               |                   |                  |                   |                                       |                    |                  | 2                  |  |  |

|                                                                                                                               |                   |                  |                   |                                       |                    |                  |                    |  |  |

Note: Bit 2 is described in Section 3.0 "CPU".

### 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FV32KA304 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals (CN0 through CN22) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the ICN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately, using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

**Note:** Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB; | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs $\$ |

|-----------------------------------|-----------------------------------------------------------------|

| NOP;                              | //Delay 1 cycle                                                 |

| BTSS PORTB, #13;                  | //Next Instruction                                              |

| Equivalent <b>`</b> C' Code       |                                                                 |

| TRISB = 0xFF00;                   | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs     |

| NOP();                            | //Delay 1 cycle                                                 |

| if(PORTBbits.RB13 == 1)           | // execute following code if PORTB pin 13 is set.               |

| {                                 |                                                                 |

| }                                 |                                                                 |

### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

|--------|-----|--------|---------|---------|---------|--------|--------|

| —      | —   | OCSIDL | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1 |

| bit 15 |     |        |         |         |         |        | bit 8  |

| R/W-0  | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0    | R/W-0               | R/W-0               | R/W-0               |

|--------|------------|------------|------------|----------|---------------------|---------------------|---------------------|

| ENFLT0 | OCFLT2     | OCFLT1     | OCFLT0     | TRIGMODE | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup> | OCM0 <sup>(1)</sup> |

| bit 7  |            |            |            |          |                     |                     | bit 0               |

| Legend:           | HSC = Hardware Settable/Clearable bit |                             |                    |  |  |

|-------------------|---------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared        | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Output Compare x Stop in Idle Mode Control bit                                                                                         |

|           | 1 = Output Compare x halts in CPU Idle mode                                                                                                    |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                                                                                     |

| bit 12-10 | OCTSEL<2:0>: Output Compare x Timer Select bits                                                                                                |

|           | 111 = System clock                                                                                                                             |

|           | 110 = Reserved                                                                                                                                 |

|           | 101 = Reserved<br>100 = Timer1                                                                                                                 |

|           | 011 = Timer5                                                                                                                                   |

|           | 010 = Timer4                                                                                                                                   |

|           | 001 <b>= Timer3</b>                                                                                                                            |

|           | 000 <b>= Timer2</b>                                                                                                                            |

| bit 9     | ENFLT2: Comparator Fault Input Enable bit                                                                                                      |

|           | 1 = Comparator Fault input is enabled                                                                                                          |

|           | 0 = Comparator Fault input is disabled                                                                                                         |

| bit 8     | ENFLT1: OCFB Fault Input Enable bit                                                                                                            |

|           | 1 = OCFB Fault input is enabled                                                                                                                |

|           | 0 = OCFB Fault input is disabled                                                                                                               |

| bit 7     | ENFLT0: OCFA Fault Input Enable bit                                                                                                            |

|           | <ul> <li>1 = OCFA Fault input is enabled</li> <li>0 = OCFA Fault input is disabled</li> </ul>                                                  |

| bit 6     |                                                                                                                                                |

| DILO      | <b>OCFLT2:</b> PWM Comparator Fault Condition Status bit<br>1 = PWM comparator Fault condition has occurred (this is cleared in hardware only) |

|           | 0 = PWM comparator Fault condition has not occurred (this bit is used only when OCM<2:0> = 111)                                                |

| bit 5     | OCFLT1: PWM OCFB Fault Input Enable bit                                                                                                        |

| Dit 0     | 1 = PWM OCFB Fault condition has occurred (this is cleared in hardware only)                                                                   |

|           | 0 = PWM OCFB Fault condition has not occurred (this bit is used only when OCM<2:0> = 111)                                                      |

| bit 4     | OCFLT0: PWM OCFA Fault Condition Status bit                                                                                                    |

|           | 1 = PWM OCFA Fault condition has occurred (this is cleared in hardware only)                                                                   |

|           | 0 = PWM OCFA Fault condition has not occurred (this bit is used only when OCM<2:0> = 111)                                                      |

| bit 3     | TRIGMODE: Trigger Status Mode Select bit                                                                                                       |

|           | 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software                                                                        |

|           | 0 = TRIGSTAT is only cleared by software                                                                                                       |

| Note 1:   | The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use                                                         |

### **Note 1:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This output compare module<sup>(1)</sup>

- 11110 = **Reserved** 11101 = Reserved 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 100xx = Reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1

- 01010 = Input Capture 5<sup>(2)</sup>

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Output Compare 5<sup>(1)</sup>

- 00100 = Output Compare 4<sup>(1)</sup>

- 00011 = Output Compare 3<sup>(1)</sup>

- 00010 = Output Compare 2<sup>(1)</sup>

- 00001 = Output Compare 1<sup>(1)</sup>

- 00000 = Not synchronized to any other module

- Note 1: Do not use an output compare module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as trigger sources only and never as Sync sources.

- 3: These bits affect the rising edge when OCINV = 1. The bits have no effect when the OCMx bits (OCxCON1<2:0>) = 001.

### REGISTER 18-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x                               | U-x  | U-x              | U-x                                | U-x                                     | U-x  | U-x  | W-x   |

|-----------------------------------|------|------------------|------------------------------------|-----------------------------------------|------|------|-------|

| —                                 | _    | —                | —                                  | —                                       | —    | —    | UTX8  |

| bit 15                            |      |                  |                                    | •                                       |      |      | bit 8 |

| W-x                               | W-x  | W-x              | W-x                                | W-x                                     | W-x  | W-x  | W-x   |

| UTX7                              | UTX6 | UTX5             | UTX4                               | UTX3                                    | UTX2 | UTX1 | UTX0  |

| bit 7                             |      |                  |                                    |                                         |      |      | bit 0 |

| •                                 |      |                  |                                    |                                         |      |      |       |

| Legend:                           |      |                  |                                    |                                         |      |      |       |

| R = Readable bit W = Writable bit |      |                  | U = Unimplemented bit, read as '0' |                                         |      |      |       |

| -n = Value at                     | POR  | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |      |      | nown  |

bit 15-9 Unimplemented: Read as '0'

bit 8 UTX8: UARTx Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: UARTx Data of the Transmitted Character bits

### **REGISTER 18-4: UXRXREG: UARTX RECEIVE REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|----------|

|        | —   | —   | —   | —   | —   | —   | URX8     |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R-0, HSC |

|----------|----------|----------|----------|----------|----------|----------|----------|

| URX7     | URX6     | URX5     | URX4     | URX3     | URX2     | URX1     | URX0     |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                            |                    |  |  |

|-------------------|---------------------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, rea | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared       | x = Bit is unknown |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: UARTx Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: UARTx Data of the Received Character bits

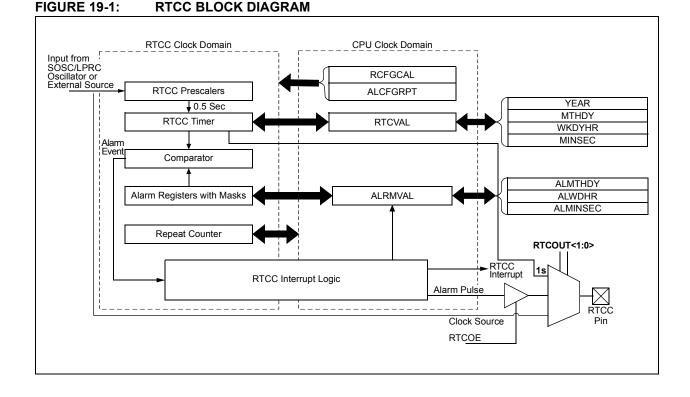

### 19.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", Section 29. "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Deep Sleep mode

- Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- · Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long-term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long-term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

### 19.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

### © 2011-2013 Microchip Technology Inc.

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month         | Day | Hours | Minutes  | Seconds |

|-------------------------------------------------|-----------------------|---------------|-----|-------|----------|---------|

| 0000 - Every half second<br>0001 - Every second |                       |               |     |       | :        | •       |

| 0010 - Every 10 seconds                         |                       |               |     |       | •        | s       |

| 0011 - Every minute                             |                       |               |     |       | :        | s s     |

| 0100 - Every 10 minutes                         |                       |               |     |       | <b>m</b> | ss      |

| 0101 - Every hour                               |                       |               |     |       | mm       | ss      |

| 0110 - Every day                                |                       |               |     | hh    | mm       | ss      |

| 0111 - Every week                               | d                     |               |     | hh    | mm       | ss      |

| 1000 - Every month                              |                       |               | d d | hh    | mm       | ss      |

| 1001 - Every year <sup>(1)</sup>                |                       | <b>m m</b> /  | d d | hh    | mm       | ss      |

| Note 1: Annually, except whe                    | n configured fo       | r February 29 |     |       |          |         |

### 19.5 POWER CONTROL

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current low-power mode (Sleep, Deep Sleep, etc.).

To enable this feature, the RTCC must be enabled (RTCEN = 1), the PWCEN register bit must be set and the RTCC pin must be driving the PWC control signal (RTCOE = 1 and RTCOUT<1:0> = 11).

The polarity of the PWC control signal may be chosen using the PWCPOL register bit. Active-low or active-high may be used with the appropriate external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin. This setting is able to drive the GND pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity.

### REGISTER 25-2: CTMUCON2: CTMU CONTROL REGISTER 2 (CONTINUED)

- bit 6 EDG2POL: Edge 2 Polarity Select bit 1 = Edge 2 is programmed for a positive edge 0 = Edge 2 is programmed for a negative edge bit 5-2 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = Edge 2 source is Comparator 3 output 1110 = Edge 2 source is Comparator 2 output 1101 = Edge 2 source is Comparator 1 output 1100 = Unimplemented; do not use 1011 = Edge 2 source is IC3 1010 = Edge 2 source is IC2 1001 = Edge 2 source is IC1 1000 = Edge 2 source is CTED13<sup>(2)</sup> 0111 = Edge 2 source is CTED12<sup>(1,2)</sup> 0110 = Edge 2 source is CTED11<sup>(1,2)</sup> 0101 = Edge 2 source is CTED10 0100 = Edge 2 source is CTED9 0011 = Edge 2 source is CTED1 0010 = Edge 2 source is CTED2 0001 = Edge 2 source is OC1 0000 = Edge 2 source is Timer1

- bit 1-0 Unimplemented: Read as '0'

- Note 1: Edge sources, CTED11 and CTED12, are not available on PIC24FV32KA302 devices.

- 2: Edge sources, CTED3, CTED11, CTED12 and CTED13, are not available on PIC24FV32KA301 devices.