#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka302-e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                  |      | N                           | lemory          |                    |                  |                  | MN                    |                              |     |      | (ch)         | rs          | -         |      |

|----------------------------------|------|-----------------------------|-----------------|--------------------|------------------|------------------|-----------------------|------------------------------|-----|------|--------------|-------------|-----------|------|

| PIC24F<br>Device                 | Pins | Flash<br>Program<br>(bytes) | SRAM<br>(bytes) | EE Data<br>(bytes) | Timers<br>16-Bit | Capture<br>Input | Compare/PWM<br>Output | UART w/<br>IrDA <sup>®</sup> | IdS | I²C™ | 12-Bit A/D ( | Comparators | CTMU (ch) | RTCC |

| PIC24FV16KA301/<br>PIC24F16KA301 | 20   | 16K                         | 2K              | 512                | 5                | 3                | 3                     | 2                            | 2   | 2    | 12           | 3           | 12        | Y    |

| PIC24FV32KA301/<br>PIC24F32KA301 | 20   | 32K                         | 2K              | 512                | 5                | 3                | 3                     | 2                            | 2   | 2    | 12           | 3           | 12        | Y    |

| PIC24FV16KA302/<br>PIC24F16KA302 | 28   | 16K                         | 2K              | 512                | 5                | 3                | 3                     | 2                            | 2   | 2    | 13           | 3           | 13        | Y    |

| PIC24FV32KA302/<br>PIC24F32KA302 | 28   | 32K                         | 2K              | 512                | 5                | 3                | 3                     | 2                            | 2   | 2    | 13           | 3           | 13        | Y    |

| PIC24FV16KA304/<br>PIC24F16KA304 | 44   | 16K                         | 2K              | 512                | 5                | 3                | 3                     | 2                            | 2   | 2    | 16           | 3           | 16        | Y    |

| PIC24FV32KA304/<br>PIC24F32KA304 | 44   | 32K                         | 2K              | 512                | 5                | 3                | 3                     | 2                            | 2   | 2    | 16           | 3           | 16        | Y    |

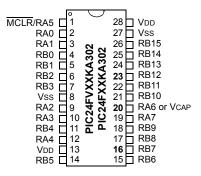

### **Pin Diagrams**

#### 28-Pin SPDIP/SSOP/SOIC<sup>(1,2)</sup>

| 2 V<br>3 C<br>4 P<br>5 P<br>6 A<br>7 A<br>8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                         | PIC24FVXXKA302<br>MCLR/Vpp/RA5<br>VReF+/CVReF+/AN0/C3INC/CTED1/CN2/RA0<br>CVREF-/VREF-/AN1/CN3/RA1 | PIC24FXXKA302                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 2 V<br>3 C<br>4 P<br>5 P<br>6 A<br>7 A<br>8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                         | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                                                               |                                                           |

| 3         C           4         P           5         P           6         A           7         A           8         V           9         C           10         C           11         S           12         S |                                                                                                    |                                                           |

| 4 P<br>5 P<br>6 A<br>7 A<br>8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                                       | CVREF-/VREF-/AN1/CN3/RA1                                                                           | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                      |

| 5 P<br>6 A<br>7 A<br>8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                                              |                                                                                                    | CVREF-/VREF-/AN1/CN3/RA1                                  |

| 6 A<br>7 A<br>8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                                                     | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0                                               | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      |

| 7 A<br>8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                                                            | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                                                          | PGEC1/AN3/C1INC/C2INA/U2RX/CN5/RB1                        |

| 8 V<br>9 C<br>10 C<br>11 S<br>12 S                                                                                                                                                                                   | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2                                                 | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        |

| 9 C<br>10 C<br>11 S<br>12 S                                                                                                                                                                                          | AN5/C1INA/C2INC/SCL2/CN7/RB3                                                                       | AN5/C1INA/C2INC/SCL2/CN7/RB3                              |

| 10         C           11         S           12         S                                                                                                                                                           | Vss                                                                                                | Vss                                                       |

| 11 S<br>12 S                                                                                                                                                                                                         | OSCI/AN13/CLKI/CN30/RA2                                                                            | OSCI/AN13/CLKI/CN30/RA2                                   |

| 12 S                                                                                                                                                                                                                 | OSCO/AN14/CLKO/CN29/RA3                                                                            | OSCO/AN14/CLKO/CN29/RA3                                   |

| -                                                                                                                                                                                                                    | SOSCI/AN15/U2RTS/CN1/RB4                                                                           | SOSCI/AN15/U2RTS/CN1/RB4                                  |

| 13 V                                                                                                                                                                                                                 | SOSCO/SCLKI/U2CTS/CN0/RA4                                                                          | SOSCO/SCLKI/U2CTS/CN0/RA4                                 |

| 10                                                                                                                                                                                                                   | Vdd                                                                                                | VDD                                                       |

| 14 P                                                                                                                                                                                                                 | PGED3/ASDA <sup>(1)</sup> /SCK2/CN27/RB5                                                           | PGED3/ASDA <sup>(1)</sup> /SCK2/CN27/RB5                  |

| 15 P                                                                                                                                                                                                                 | PGEC3/ASCL <sup>(1)</sup> /SDO2/CN24/RB6                                                           | PGEC3/ASCL <sup>(1)</sup> /SDO2/CN24/RB6                  |

| 16 U                                                                                                                                                                                                                 | U1TX/C2OUT/OC1/INT0/CN23/RB7                                                                       | U1TX/INT0/CN23/RB7                                        |

| 17 S                                                                                                                                                                                                                 | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                                                                   | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          |

| 18 S                                                                                                                                                                                                                 | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                                                                 | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        |

| 19 S                                                                                                                                                                                                                 | SDI2/IC1/CTED3/CN9/RA7                                                                             | SDI2/IC1/CTED3/CN9/RA7                                    |

| 20 V                                                                                                                                                                                                                 | VCAP                                                                                               | C2OUT/OC1/CTED1/INT2/CN8/RA6                              |

| 21 P                                                                                                                                                                                                                 | PGED2/SDI1/OC3/CTED11/CN16/RB10                                                                    | PGED2/SDI1/OC3/CTED11/CN16/RB10                           |

| 22 P                                                                                                                                                                                                                 | PGEC2/SCK1/OC2/CTED9/CN15/RB11                                                                     | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            |

| 23 A                                                                                                                                                                                                                 | AN12/HLVDIN/SS2/IC3/CTED2/INT2/CN14/RB12                                                           | AN12/HLVDIN/SS2/IC3/CTED2/CN14/RB12                       |

| 24 A                                                                                                                                                                                                                 | AN11/SDO1/OCFB/CTPLS/CN13/RB13                                                                     | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            |

| 25 C                                                                                                                                                                                                                 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/RB14                                              | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |

| 26 A                                                                                                                                                                                                                 | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15                                                       | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              |

| 27 V                                                                                                                                                                                                                 |                                                                                                    |                                                           |

| 28 V                                                                                                                                                                                                                 | Vss/AVss                                                                                           | Vss/AVss                                                  |

Legend:

Pin numbers in **bold** indicate pin function differences between PIC24FV and PIC24F devices.

Note 1: Alternative multiplexing for SDA1 (ASDA1) and SCL1 (ASCL1) when the I2CSEL Configuration bit is set.

2: PIC24F32KA304 device pins have a maximum voltage of 3.6V and are not 5V tolerant.

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                            |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  | Pin Number                        |               |                        |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| C3INA    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | Ι   | ANA    | Comparator 3 Input A (+)   |

| C3INB    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator 3 Input B (-)   |

| C3INC    | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | 1   | ANA    | Comparator 3 Input C (+)   |

| C3IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | 1   | ANA    | Comparator 3 Input D (-)   |

| C3OUT    | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | 0   | —      | Comparator 3 Output        |

| CLK I    | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ANA    | Main Clock Input           |

| CLKO     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | 0   | _      | System Clock Output        |

| CN0      | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I   | ST     | Interrupt-on-Change Inputs |

| CN1      | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ST     |                            |

| CN2      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ST     |                            |

| CN3      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ST     |                            |

| CN4      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ST     |                            |

| CN5      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     |                            |

| CN6      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ST     |                            |

| CN7      | _                                | 7                                 | 4             | 24                     | 26             |                                  | 7                                 | 4             | 24                     | 26             | I   | ST     |                            |

| CN8      | 14                               | 20                                | 17            | 7                      | 7              |                                  |                                   |               | _                      |                | I   | ST     |                            |

| CN9      |                                  | 19                                | 16            | 6                      | 6              |                                  | 19                                | 16            | 6                      | 6              | I   | ST     |                            |

| CN10     |                                  | —                                 | —             | 27                     | 29             |                                  |                                   |               | 27                     | 29             | I   | ST     |                            |

| CN11     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 1   | ST     |                            |

| CN12     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 1   | ST     |                            |

| CN13     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | 1   | ST     |                            |

| CN14     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | 1   | ST     |                            |

| CN15     |                                  | 22                                | 19            | 9                      | 10             |                                  | 22                                | 19            | 9                      | 10             | Ι   | ST     | ]                          |

| CN16     |                                  | 21                                | 18            | 8                      | 9              |                                  | 21                                | 18            | 8                      | 9              | Ι   | ST     |                            |

| CN17     |                                  | —                                 | —             | 3                      | 3              |                                  | _                                 | _             | 3                      | 3              | 1   | ST     |                            |

| CN18     | _                                | _                                 | _             | 2                      | 2              | _                                | _                                 | _             | 2                      | 2              | Ι   | ST     | ]                          |

| CN19     |                                  | _                                 | _             | 5                      | 5              | —                                | _                                 |               | 5                      | 5              | 1   | ST     | ]                          |

| CN20     |                                  | _                                 | —             | 4                      | 4              | _                                |                                   |               | 4                      | 4              | I   | ST     |                            |

| CN21     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I   | ST     | ]                          |

| CN22     | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | 1   | ST     |                            |

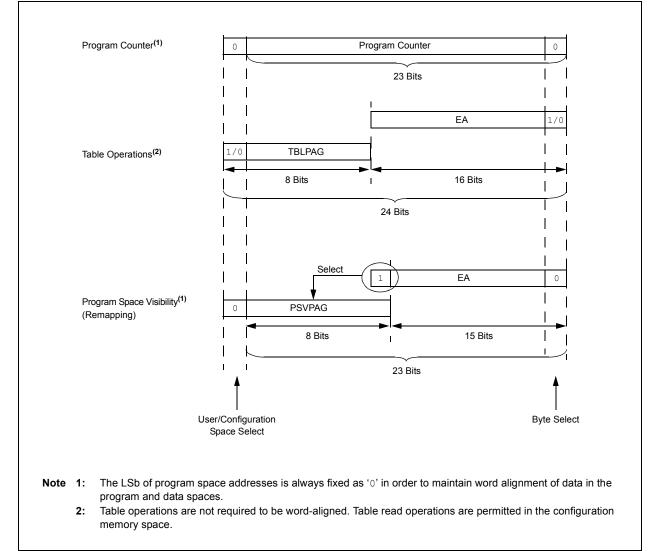

|                                       | Access        | Program Space Address |                              |                                                 |             |  |  |  |  |  |

|---------------------------------------|---------------|-----------------------|------------------------------|-------------------------------------------------|-------------|--|--|--|--|--|

| Access Type                           | Space         | <23>                  | <22:16>                      | <15>                                            | <15> <14:1> |  |  |  |  |  |

| Instruction Access                    | User          | 0                     | 0 PC<22:1>                   |                                                 |             |  |  |  |  |  |

| (Code Execution)                      |               |                       | 0xx xxxx xxxx xxxx xxxx xxx0 |                                                 |             |  |  |  |  |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TBL                   | _PAG<7:0>                    | Data EA<15:0>                                   |             |  |  |  |  |  |

|                                       |               | 0 x                   | XXX XXXX                     | XXXX XXXX XXXX XXXX                             |             |  |  |  |  |  |

|                                       | Configuration | TBL                   | _PAG<7:0>                    | Data EA<15:0>                                   |             |  |  |  |  |  |

|                                       |               | 1x                    | XXX XXXX                     |                                                 |             |  |  |  |  |  |

| Program Space Visibility              | User          | 0                     | PSVPAG<7                     | :0> <sup>(2)</sup> Data EA<14:0> <sup>(1)</sup> |             |  |  |  |  |  |

| (Block Remap/Read)                    |               | 0                     | XXXX XX                      | XXX                                             |             |  |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) in the PIC24FV32KA304 family.

#### 8.3 Interrupt Control and Status Registers

The PIC24FV32KA304 family of devices implements a total of 23 registers for the interrupt controller:

- INTCON1

- INTCON2

- · IFS0, IFS1, IFS3 and IFS4

- · IEC0, IEC1, IEC3 and IEC4

- IPC0 through IPC5, IPC7 and IPC15 through IPC19

- INTTREG

Global Interrupt Enable (GIE) control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIVT.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU Interrupt Priority Level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All Interrupt registers are described in Register 8-1 through Register 8-33, in the following sections.

| REGISTER 8-3: | INTCON1: INTERRUPT CONTROL REGISTER 1 |  |

|---------------|---------------------------------------|--|

|               |                                       |  |

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| —     | —   | —   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | —     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:    |             | HS = Hardware Settable         | bit                    |                    |

|------------|-------------|--------------------------------|------------------------|--------------------|

| R = Reada  | ble bit     | W = Writable bit               | U = Unimplemented bit, | , read as '0'      |

| -n = Value | at POR      | '1' = Bit is set               | '0' = Bit is cleared   | x = Bit is unknown |

|            |             |                                |                        |                    |

| bit 15     | NSTDIS: Ir  | nterrupt Nesting Disable bit   |                        |                    |

|            |             | ot nesting is disabled         |                        |                    |

|            | 0 = Interru | ot nesting is enabled          |                        |                    |

| bit 14-5   | Unimplem    | ented: Read as '0'             |                        |                    |

| bit 4      | MATHERR     | : Arithmetic Error Trap Statu  | s bit                  |                    |

|            | 1 = Overflo | w trap has occurred            |                        |                    |

|            | 0 = Overflo | w trap has not occurred        |                        |                    |

| bit 3      | ADDRERR     | : Address Error Trap Status    | bit                    |                    |

|            | 1 = Addres  | s error trap has occurred      |                        |                    |

|            | 0 = Addres  | s error trap has not occurred  | l                      |                    |

| bit 2      | STKERR:     | Stack Error Trap Status bit    |                        |                    |

|            | 1 = Stack e | error trap has occurred        |                        |                    |

|            | 0 = Stack e | error trap has not occurred    |                        |                    |

| bit 1      | OSCFAIL:    | Oscillator Failure Trap Status | s bit                  |                    |

|            | - ···       |                                |                        |                    |

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

bit 0 Unimplemented: Read as '0'

#### REGISTER 8-11: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

### bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

#### REGISTER 8-21: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | R/W-1         | R/W-0                                | R/W-0              | U-0              | R/W-1            | R/W-0           | R/W-0   |

|--------------|---------------|--------------------------------------|--------------------|------------------|------------------|-----------------|---------|

| _            | CNIP2         | CNIP1                                | CNIP0              | _                | CMIP2            | CMIP1           | CMIP0   |

| bit 15       |               |                                      |                    |                  |                  |                 | bit 8   |

| U-0          | R/W-1         | R/W-0                                | R/W-0              | U-0              | R/W-1            | R/W-0           | R/W-0   |

| —            | MI2C1P2       | MI2C1P1                              | MI2C1P0            | —                | SI2C1P2          | SI2C1P1         | SI2C1P0 |

| bit 7        |               |                                      |                    |                  |                  |                 | bit C   |

| Legend:      |               |                                      |                    |                  |                  |                 |         |

| R = Readat   | ole bit       | W = Writable                         | bit                | U = Unimple      | mented bit, read | d as '0'        |         |

| -n = Value a | at POR        | '1' = Bit is set                     |                    | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |

| -:. 4 C      |               | tad. Daad aa (                       | <u>.</u>           |                  |                  |                 |         |

| bit 15       | -             | ited: Read as '                      |                    | rupt Drigrity b  | ita              |                 |         |

| bit 14-12    |               |                                      | lotification Inter | -                | 115              |                 |         |

|              | • •           | puis Phonty 7 (                      | highest priority   | mterrupt)        |                  |                 |         |

|              | •             |                                      |                    |                  |                  |                 |         |

|              | 001 = Interru | pt is Priority 1                     |                    |                  |                  |                 |         |

|              | 000 = Interru | pt source is dis                     | abled              |                  |                  |                 |         |

| bit 11       | Unimplemen    | ted: Read as '                       | 0'                 |                  |                  |                 |         |

| bit 10-8     | CMIP<2:0>:    | Comparator Int                       | errupt Priority b  | its              |                  |                 |         |

|              | 111 = Interru | pt is Priority 7 (                   | highest priority   | interrupt)       |                  |                 |         |

|              | •             |                                      |                    |                  |                  |                 |         |

|              | •             | untin Duinuity (                     |                    |                  |                  |                 |         |

|              |               | pt is Priority 1<br>pt source is dis | abled              |                  |                  |                 |         |

| bit 7        |               | ited: Read as '                      |                    |                  |                  |                 |         |

| bit 6-4      | -             |                                      | Event Interrupt    | Priority hits    |                  |                 |         |

|              |               |                                      | highest priority   | •                |                  |                 |         |

|              | •             |                                      | ingricor priority  | interrupt)       |                  |                 |         |

|              | •             |                                      |                    |                  |                  |                 |         |

|              |               | pt is Priority 1<br>pt source is dis | abled              |                  |                  |                 |         |

| bit 3        | Unimplemen    | ted: Read as '                       | 0'                 |                  |                  |                 |         |

| bit 2-0      | -             |                                      | vent Interrupt F   | riority bits     |                  |                 |         |

|              |               |                                      | highest priority   | -                |                  |                 |         |

|              | •             |                                      | - · ·              | • •              |                  |                 |         |

|              | •             |                                      |                    |                  |                  |                 |         |

|              | •             |                                      |                    |                  |                  |                 |         |

|              |               | pt is Priority 1<br>pt source is dis |                    |                  |                  |                 |         |

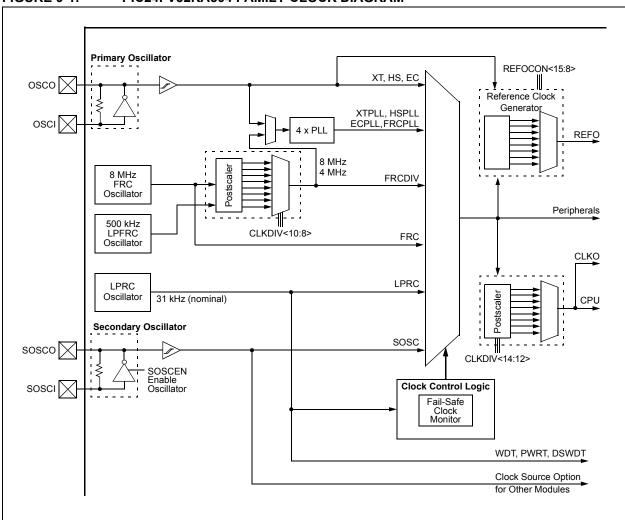

### 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Oscillator Configuration, refer to the "PIC24F Family Reference Manual", Section 38. "Oscillator with 500 kHz Low-Power FRC" (DS39726).

The oscillator system for the PIC24FV32KA304 family of devices has the following features:

- A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for EC mode. When using an external clock source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24FV32KA304 FAMILY CLOCK DIAGRAM

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul>                       |

|       | Hardware is set or cleared when a Start, Repeated Start or Stop is detected.                                                               |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                                                                 |

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                         |

|       | <ol> <li>Read – indicates data transfer is output from the slave</li> </ol>                                                                |

|       | 0 = Write – indicates data transfer is input to the slave                                                                                  |

|       | Hardware is set or clear after the reception of an I <sup>2</sup> C device address byte.                                                   |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> </ul>                        |

|       | Hardware is set when I2CxRCV is written with a received byte; hardware is clear when the software reads I2CxRCV.                           |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit is in progress, I2CxTRN is full                                                                                               |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                                                                 |

Hardware is set when the software writes to I2CxTRN; hardware is clear at the completion of data transmission.

#### 18.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 18-1 provides the formula for computation of the baud rate with BRGH = 0.

### EQUATION 18-1: UARTX BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$   $UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$ Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 18-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is Fcy/16 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(16 \* 65536).

Equation 18-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 18-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

Baud Rate =  $\frac{FCY}{4 \cdot (UxBRG + 1)}$  $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

## **EXAMPLE 18-1:** BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | =   | FCY/(16 (UxBRG + 1))                                            |

|----------------------|-----|-----------------------------------------------------------------|

| Solving for UxBRG va | lue | :                                                               |

| UxBRG                |     | ((FCY/Desired Baud Rate)/16) - 1                                |

| UxBRG                | =   | ((400000/9600)/16) - 1                                          |

| UxBRG                | =   | 25                                                              |

| Calculated Baud Rate | =   | 4000000/(16 (25 + 1))                                           |

|                      | =   | 9615                                                            |

| Error                | =   | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate |

|                      | =   | (9615 - 9600)/9600                                              |

|                      | =   | 0.16%                                                           |

|                      |     |                                                                 |

| Note 1: Based on     | Fc  | Y = FOSC/2; Doze mode and PLL are disabled.                     |

|                      |     |                                                                 |

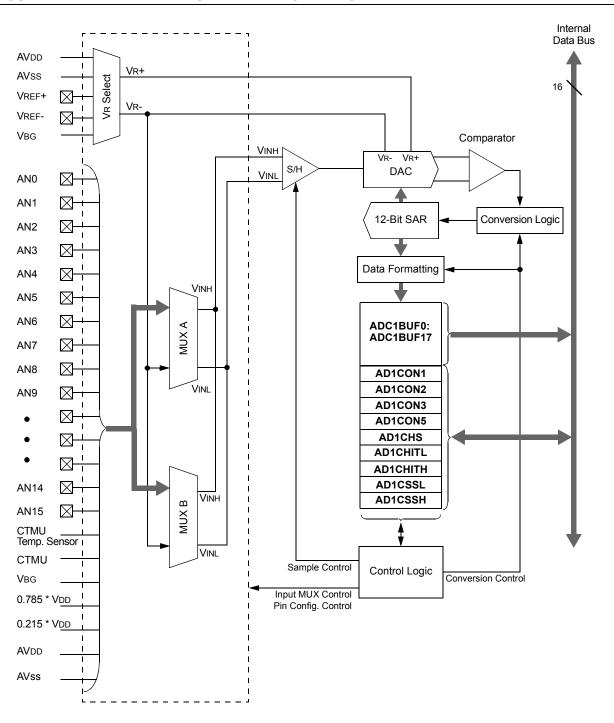

#### FIGURE 22-1: 12-BIT A/D CONVERTER BLOCK DIAGRAM

NOTES:

| REGISTER 26-4: FOSC: OSCILLATOR CONFIGURATION REGISTER |        |         |           |           |          |         |         |  |  |  |

|--------------------------------------------------------|--------|---------|-----------|-----------|----------|---------|---------|--|--|--|

| R/P-1                                                  | R/P-1  | R/P-1   | R/P-1     | R/P-1     | R/P-1    | R/P-1   | R/P-1   |  |  |  |

| FCKSM1                                                 | FCKSM0 | SOSCSEL | POSCFREQ1 | POSCFREQ0 | OSCIOFNC | POSCMD1 | POSCMD0 |  |  |  |

| bit 7                                                  |        |         |           |           |          |         | bit 0   |  |  |  |

|                                                        |        |         |           |           |          |         |         |  |  |  |

| Legend:           |                      |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | <b>FCKSM&lt;1:0&gt;:</b> Clock Switching and Fail-Safe Clock Monitor Selection Configuration bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | SOSCSEL: Secondary Oscillator Power Selection Configuration bit                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Secondary oscillator is configured for high-power operation</li> <li>0 = Secondary oscillator is configured for low-power operation</li> </ul>                                                                                                                                                               |

| bit 4-3 | POSCFREQ<1:0>: Primary Oscillator Frequency Range Configuration bits                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Primary oscillator/external clock input frequency is greater than 8 MHz</li> <li>10 = Primary oscillator/external clock input frequency is between 100 kHz and 8 MHz</li> <li>01 = Primary oscillator/external clock input frequency is less than 100 kHz</li> <li>00 = Reserved; do not use</li> </ul>     |

| bit 2   | OSCIOFNC: CLKO Enable Configuration bit                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = CLKO output signal is active on the OSCO pin; primary oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMD&lt;1:0&gt; = 11 or 00)</li> <li>0 = CLKO output is disabled</li> </ul>                                                                    |

| bit 1-0 | POSCMD<1:0>: Primary Oscillator Configuration bits                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Primary Oscillator mode is disabled</li> <li>10 = HS Oscillator mode is selected</li> <li>01 = XT Oscillator mode is selected</li> <li>00 = External Clock mode is selected</li> </ul>                                                                                                                      |

| R/P-1         | R/P-1                                                                                | U-0                                                        | R/P-1                               | R/P-1             | R/P-1            | R/P-1           | R/P-1    |  |  |  |

|---------------|--------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------|-------------------|------------------|-----------------|----------|--|--|--|

| DSWDTEN       | DSBOREN                                                                              | _                                                          | DSWDTOSC                            | DSWDTPS3          | DSWDTPS2         | DSWDTPS1        | DSWDTPS0 |  |  |  |

| bit 7         |                                                                                      |                                                            |                                     |                   |                  |                 | bit 0    |  |  |  |

|               |                                                                                      |                                                            |                                     |                   |                  |                 |          |  |  |  |

| Legend:       |                                                                                      |                                                            |                                     |                   |                  |                 |          |  |  |  |

| R = Readabl   | le bit                                                                               | P = Program                                                | nable bit                           | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | t POR                                                                                | '1' = Bit is set                                           | :                                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |

|               |                                                                                      |                                                            |                                     |                   |                  |                 |          |  |  |  |

| bit 7         |                                                                                      |                                                            | chdog Timer Er                      | nable bit         |                  |                 |          |  |  |  |

|               | 1 = DSWDT is<br>0 = DSWDT is                                                         |                                                            |                                     |                   |                  |                 |          |  |  |  |

| bit 6         |                                                                                      |                                                            | Power BOR En<br>on Deep Sleep       |                   |                  |                 |          |  |  |  |

|               | 1 = Deep Slee                                                                        | p BOR is enab                                              | led in Deep Sle<br>bled in Deep Sle | ер                |                  |                 |          |  |  |  |

| bit 5         | Unimplement                                                                          |                                                            | •                                   | - 1               |                  |                 |          |  |  |  |

| bit 4         | DSWDTOSC:                                                                            | DSWDT Refer                                                | ence Clock Sele                     | ect bit           |                  |                 |          |  |  |  |

|               |                                                                                      |                                                            | ne reference clo                    |                   |                  |                 |          |  |  |  |

|               |                                                                                      |                                                            | he reference clo                    |                   |                  |                 |          |  |  |  |

| bit 3-0       |                                                                                      | -                                                          | p Watchdog Tin                      |                   |                  | <b>C A</b>      |          |  |  |  |

|               | •                                                                                    |                                                            | this creates an                     | • •               | ase time unit o  | r i ms.         |          |  |  |  |

|               |                                                                                      |                                                            | 7 days) nominal<br>avs) nominal     | I                 |                  |                 |          |  |  |  |

|               | 1110 = 1:536,870,912 (6.4 days) nominal<br>1101 = 1:134,217,728 (38.5 hours) nominal |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 1100 = 1:33,554,432 (9.6 hours) nominal                                              |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 1011 = 1:8,388,608 (2.4 hours) nominal<br>1010 = 1:2,097,152 (36 minutes) nominal    |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 1010 = 1.2,091<br>1001 = 1:524,2                                                     |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 1000 = 1:131,0                                                                       |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 0111 = 1:32,76                                                                       |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               |                                                                                      | 3,192 (8.5 seconds) nominal<br>2,048 (2.1 seconds) nominal |                                     |                   |                  |                 |          |  |  |  |

|               | 0101 = 1.2,040<br>0100 = 1:512 (                                                     |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 0011 = 1:128 (                                                                       |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 0010 <b>= 1:32 (3</b>                                                                |                                                            |                                     |                   |                  |                 |          |  |  |  |

|               | 0001 = 1:8 (8.3                                                                      |                                                            |                                     |                   |                  |                 |          |  |  |  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL  | Expr            | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL  | Wn              | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET  |                 | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE |                 | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW  | #lit10,Wn       | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC    | f               | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC    | f               | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE     | Ws,Wnd          | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM   | f               | f = FFFFh                               | 1             | 1              | None                     |

|                      | SETM   | WREG            | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM   | Ws              | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL     | f               | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

|                      | SL     | f,WREG          | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Ws,Wd           | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB    | f               | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | f,WREG          | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | #lit10,Wn       | Wn = Wn – lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | #lit10,Wn       | Wn = Wn – lit10 – $(\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR   | f               | f = WREG - f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | f,WREG          | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

| i                    | SUBBR  | f,WREG          | $WREG = WREG - f - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      |        |                 | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              |                          |

|                      | SUBBR  | Wb,Ws,Wd        |                                         |               |                | C, DC, N, OV, Z          |

| ONAD                 | SUBBR  | Wb,#lit5,Wd     | Wd = lit5 – Wb – (C)                    | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b | Wn              | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP   | Wn              | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

| TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>             | 1             | 2              | None                     |

#### TABLE 29-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min         | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                    | TJ     | -40         | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40         |             | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | Pint + Pi/o |             | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                       | PDMAX  | (           | TJ — ΤΑ)/θJ | JA   | W    |

#### TABLE 29-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур  | Max | Unit | Notes |

|------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 20-Pin SPDIP | θJA    | 62.4 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 60   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SSOP  | θJA    | 108  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θJA    | 71   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SOIC  | θJA    | 75   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 80.2 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN   | θJA    | 32   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN   | θJA    | 29   | _   | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN  | θJA    | _    | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 29-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHA                             | RACTERI | STICS                                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                   |  |

|------------------------------------|---------|------------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|-----------------------------------|--|

| Param<br>No. Symbol Characteristic |         |                                                                  |                                                       | Typ <sup>(1)</sup> | Max | Units | Conditions                        |  |

| DC10                               | Vdd     | Supply Voltage                                                   | 1.8                                                   | _                  | 3.6 | V     | For F devices                     |  |

|                                    |         |                                                                  | 2.0                                                   |                    | 5.5 | V     | For FV devices                    |  |

| DC12                               |         |                                                                  | 1.5                                                   |                    | _   | V     | For F devices                     |  |

|                                    |         | Voltage <sup>(2)</sup>                                           | 1.7                                                   |                    | _   | V     | For FV devices                    |  |

| DC16                               | VPOR    | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | Vss                                                   | —                  | 0.7 | V     |                                   |  |

| DC17                               | SVDD    | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                  | —                  |     | V/ms  | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** This is the limit to which VDD can be lowered without losing RAM data.

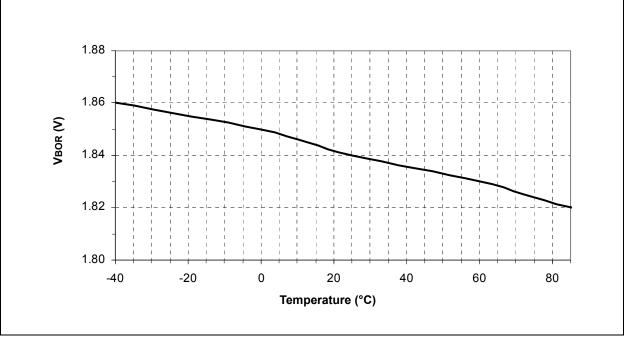

FIGURE 30-23: TYPICAL VBOR vs. TEMPERATURE (BOR TRIP POINT 3)

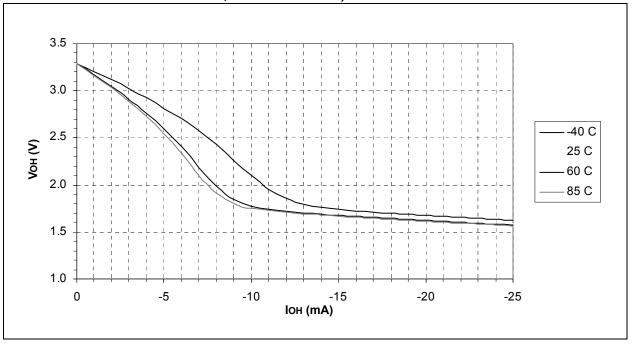

FIGURE 30-25: TYPICAL VOH vs. IOH (GENERAL PURPOSE I/O, AS A FUNCTION OF TEMPERATURE,  $2.0V \le VDD \le 5.5V$ )

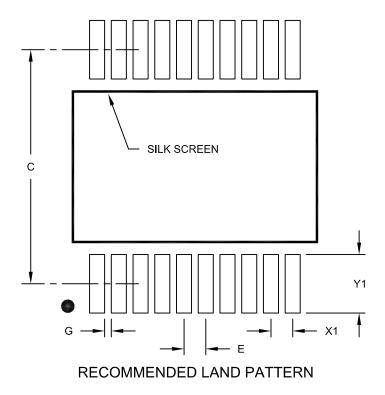

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |      |      |      |  |

|--------------------------|------------------|------|------|------|--|

| Dimension                | Dimension Limits |      |      | MAX  |  |

| Contact Pitch            | act Pitch E      |      |      |      |  |

| Contact Pad Spacing      | С                |      | 7.20 |      |  |

| Contact Pad Width (X20)  | X1               |      |      | 0.45 |  |

| Contact Pad Length (X20) | Y1               |      |      | 1.75 |  |

| Distance Between Pads    | G                | 0.20 |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A