# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka302-e-sp |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams**

|                          | 44-Pin TQFP/QFN <sup>(1,2,3)</sup>                                                                                    | Pir      |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|

|                          |                                                                                                                       | 1        |

|                          |                                                                                                                       |          |

|                          |                                                                                                                       | 2        |

|                          | RB RC 8 VDD 7 VDD 7 VC 8 RB RC 8 RC 8 RC 8 RC 8 RC 8 RC 8 RC                         | 3        |

|                          | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                                                | 4        |

|                          | 4 4 4 7 4 7 4 7 4 7 4 7 4 7 4 7 4 7 4 7                                                                               | 5<br>6   |

| RB                       |                                                                                                                       | 7        |

| RC                       | 7 3 31 RA3                                                                                                            | 8        |

| RC                       |                                                                                                                       | 9        |

| RA<br>RA6 or VCA<br>RB10 | 7 6 PIC24FXXKA304 28 VDD<br>7 PIC24FXXKA304 27 RC2                                                                    | 10       |

| RB1                      |                                                                                                                       | 11       |

| RB12<br>RB13             |                                                                                                                       | 12       |

| KD I.                    | 3 11 23 RB2                                                                                                           | 13       |

|                          | RA10<br>RA11<br>RA11<br>RB15<br>VSS<br>VSS<br>VDD<br>MCLR/RA5<br>RA1<br>RA1<br>RA1<br>RA1<br>RA1<br>RA1<br>RB1<br>RB1 | 14       |

|                          | WCI                                                                                                                   | 15       |

|                          |                                                                                                                       | 16       |

|                          |                                                                                                                       | 17       |

|                          |                                                                                                                       | 18       |

|                          |                                                                                                                       | 19       |

|                          |                                                                                                                       | 20       |

|                          |                                                                                                                       | 21       |

|                          |                                                                                                                       | 22       |

|                          |                                                                                                                       | 23       |

|                          |                                                                                                                       | 24       |

|                          |                                                                                                                       | 25       |

|                          |                                                                                                                       | 26       |

|                          |                                                                                                                       | 27       |

|                          |                                                                                                                       | 28       |

|                          |                                                                                                                       | 29       |

|                          |                                                                                                                       | 30       |

|                          |                                                                                                                       | 31       |

|                          |                                                                                                                       | 32<br>33 |

|                          |                                                                                                                       | 33       |

| Legend:                  | Pin numbers in <b>bold</b> indicate pin                                                                               | 34       |

|                          | function differences between<br>PIC24FV and PIC24F devices.                                                           | 35       |

| Note 1:                  | Exposed pad on underside of devices.                                                                                  | 30       |

| Note I.                  | is connected to Vss.                                                                                                  | 38       |

| 2:                       | Alternative multiplexing for SDA1                                                                                     | 39       |

|                          | (ASDA1) and SCL1 (ASCL1) when                                                                                         | 40       |

|                          | the I2CSEL Configuration bit is set.                                                                                  | 41       |

| 3:                       | PIC24F32KA304 device pins have a                                                                                      | 42       |

|                          | maximum voltage of 3.6V and are not 5V tolerant.                                                                      | 43       |

|                          |                                                                                                                       | 44       |

| Pin | Pin F                                                         | eatures                                                       |

|-----|---------------------------------------------------------------|---------------------------------------------------------------|

| Pin | PIC24FVXXKA304                                                | PIC24FXXKA304                                                 |

| 1   | SDA1/T1CK/U1RTS/CTED4/CN21/<br>RB9                            | SDA1/T1CK/U1RTS/CTED4/CN21/<br>RB9                            |

| 2   | U1RX/CN18/RC6                                                 | U1RX/CN18/RC6                                                 |

| 3   | U1TX/CN17/RC7                                                 | U1TX/CN17/RC7                                                 |

| 4   | OC2/CN20/RC8                                                  | OC2/CN20/RC8                                                  |

| 5   | IC2/CTED7/CN19/RC9                                            | IC2/CTED7/CN19/RC9                                            |

| 6   | IC1/CTED3/CN9/RA7                                             | IC1/CTED3/CN9/RA7                                             |

| 7   | VCAP                                                          | C2OUT/OC1/CTED1/INT2/CN8/RAG                                  |

| 8   | PGED2/SDI1/CTED11/CN16/RB10                                   | PGED2/SDI1/CTED11/CN16/RB10                                   |

| 9   | PGEC2/SCK1/CTED9/CN15/RB11                                    | PGEC2/SCK1/CTED9/CN15/RB11                                    |

| 10  | AN12/HLVDIN/CTED2/INT2/CN14/<br>RB12                          | AN12/HLVDIN/CTED2/CN14/RB12                                   |

| 11  | AN11/SDO1/CTPLS/CN13/RB13                                     | AN11/SDO1/CTPLS/CN13/RB13                                     |

| 12  | OC3/CN35/RA10                                                 | OC3/CN35/RA10                                                 |

| 13  | IC3/CTED8/CN36/RA11                                           | IC3/CTED8/CN36/RA11                                           |

| 14  | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |

| 15  | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15              | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15              |

| 16  | Vss/AVss                                                      | Vss/AVss                                                      |

| 17  | Vdd/AVdd                                                      | Vdd/AVdd                                                      |

| 18  | MCLR/Vpp/RA5                                                  | MCLR/VPP/RA5                                                  |

| 19  | VREF+/CVREF+/AN0/C3INC/<br>CTED1/CN2/RA0                      | VREF+/CVREF+/AN0/C3INC/CN2/<br>RA0                            |

| 20  | CVREF-/VREF-/AN1/CN3/RA1                                      | CVREF-/VREF-/AN1/CN3/RA1                                      |

| 21  | PGED1/AN2/ULPWU/CTCMP/<br>C1IND/C2INB/C3IND/U2TX/CN4/RB0      | PGED1/AN2/ULPWU/CTCMP/C1IND<br>C2INB/C3IND/U2TX/CN4/RB0       |

| 22  | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1                 | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1                 |

| 23  | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2             | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2             |

| 24  | AN5/C1INA/C2INC/SCL2/CN7/<br>RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RB3                                  |

| 25  | AN6/CN32/RC0                                                  | AN6/CN32/RC0                                                  |

| 26  | AN7/CN31/RC1                                                  | AN7/CN31/RC1                                                  |

| 27  | AN8/CN10/RC2                                                  | AN8/CN10/RC2                                                  |

| 28  | VDD                                                           | VDD                                                           |

| 29  | Vss                                                           | Vss                                                           |

| 30  | OSCI/AN13/CLKI/CN30/RA2                                       | OSCI/AN13/CLKI/CN30/RA2                                       |

| 31  | OSCO/AN14/CLKO/CN29/RA3                                       | OSCO/AN14/CLKO/CN29/RA3                                       |

| 32  | OCFB/CN33/RA8                                                 | OCFB/CN33/RA8                                                 |

| 33  | SOSCI/AN15/U2RTS/CN1/RB4                                      | SOSCI/AN15/U2RTS/CN1/RB4                                      |

| 34  | SOSCO/SCLKI/U2CTS/CN0/RA4                                     | SOSCO/SCLKI/U2CTS/CN0/RA4                                     |

| 35  | SS2/CN34/RA9                                                  | SS2/CN34/RA9                                                  |

| 36  | SDI2/CN28/RC3                                                 | SDI2/CN28/RC3                                                 |

| 37  | SDO2/CN25/RC4                                                 | SDO2/CN25/RC4                                                 |

| 38  | SCK2/CN26/RC5                                                 | SCK2/CN26/RC5                                                 |

| 39  | Vss                                                           | Vss                                                           |

| 40  | VDD                                                           | VDD                                                           |

| 41  | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                          | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                          |

| 42  | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                          | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                          |

| 43  | C2OUT/OC1/INT0/CN23/RB7                                       | INT0/CN23/RB7                                                 |

| 44  | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                          | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                          |

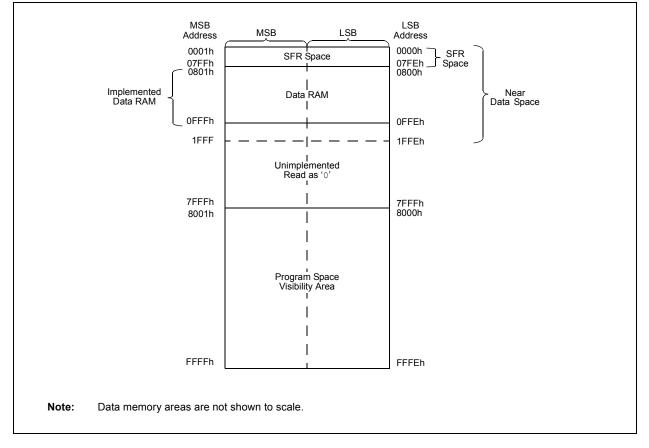

### 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility"). PIC24FV32KA304 family devices implement a total of 1024 words of data memory. If an EA points to a location outside of this area, an all zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### FIGURE 4-3: DATA SPACE MEMORY MAP FOR PIC24FV32KA304 FAMILY DEVICES

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0           | U-0    | U-0              | U-0 | U-0                                | U-0  | U-0            | U-0     |

|---------------|--------|------------------|-----|------------------------------------|------|----------------|---------|

| _             | —      | —                | _   | —                                  |      | _              | —       |

| bit 15        |        |                  |     |                                    |      |                | bit 8   |

|               |        |                  |     |                                    |      |                |         |

| U-0           | U-0    | U-0              | U-0 | U-0                                | U-0  | U-0            | R/W-0   |

| —             | —      | —                | —   | —                                  | —    | —              | ULPWUIE |

| bit 7         |        |                  |     |                                    |      |                | bit 0   |

|               |        |                  |     |                                    |      |                |         |

| Legend:       |        |                  |     |                                    |      |                |         |

| R = Readabl   | le bit | W = Writable I   | oit | U = Unimplemented bit, read as '0' |      |                |         |

| -n = Value at | POR    | '1' = Bit is set |     | '0' = Bit is clea                  | ared | x = Bit is unk | nown    |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

|                                           |

### 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FV32KA304 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

### (1)

| U-0          | U-0               | U-0                                                                                                                                                                            | U-0                                    | U-0                    | U-0             | U-0            | R/W-0, HS              |  |

|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|-----------------|----------------|------------------------|--|

| _            | _                 |                                                                                                                                                                                | _                                      | _                      | _               |                | DSINT0                 |  |

| bit 15       |                   |                                                                                                                                                                                |                                        |                        |                 |                | bit                    |  |

|              |                   |                                                                                                                                                                                |                                        |                        |                 |                |                        |  |

| R/W-0, HS    | U-0               | U-0                                                                                                                                                                            | R/W-0, HS                              | R/W-0, HS              | R/W-0, HS       | U-0            | R/W-0, HS              |  |

| DSFLT        | —                 | —                                                                                                                                                                              | DSWDT                                  | DSRTCC                 | DSMCLR          | _              | DSPOR <sup>(2,3)</sup> |  |

| bit 7        |                   |                                                                                                                                                                                |                                        |                        |                 |                | bit                    |  |

|              |                   |                                                                                                                                                                                |                                        |                        |                 |                |                        |  |

| Legend:      |                   | HS = Hardwa                                                                                                                                                                    | re Settable bit                        |                        |                 |                |                        |  |

| R = Readab   |                   | W = Writable                                                                                                                                                                   |                                        | •                      | nented bit, rea | d as '0'       |                        |  |

| -n = Value a | at POR            | '1' = Bit is set                                                                                                                                                               |                                        | '0' = Bit is cle       | ared            | x = Bit is un  | known                  |  |

|              |                   |                                                                                                                                                                                |                                        |                        |                 |                |                        |  |

| bit 15-9     | -                 | nted: Read as                                                                                                                                                                  |                                        |                        |                 |                |                        |  |

| bit 8        |                   | • •                                                                                                                                                                            | upt-on-Change b                        |                        |                 |                |                        |  |

|              |                   |                                                                                                                                                                                | s asserted during<br>s not asserted du |                        | ep              |                |                        |  |

| bit 7        | DSFLT: Dee        | p Sleep Fault D                                                                                                                                                                | etect bit                              |                        |                 |                |                        |  |

|              |                   |                                                                                                                                                                                | g Deep Sleep an                        | d some Deep S          | Sleep configura | ation settings | may have bee           |  |

|              | corrupte          |                                                                                                                                                                                | during Deep Sle                        | on                     |                 |                |                        |  |

| bit 6-5      |                   | nted: Read as                                                                                                                                                                  | •                                      | ер                     |                 |                |                        |  |

| bit 4        | -                 |                                                                                                                                                                                | o<br>ndog Timer Time                   | -out bit               |                 |                |                        |  |

|              |                   |                                                                                                                                                                                | dog Timer timed                        |                        | n Sleen         |                |                        |  |

|              |                   |                                                                                                                                                                                | dog Timer did no                       |                        |                 |                |                        |  |

| bit 3        | DSRTCC: D         | eep Sleep Rea                                                                                                                                                                  | -Time Clock and                        | Calendar (RT           | CC) Alarm bit   |                |                        |  |

|              |                   |                                                                                                                                                                                | nd Calendar trigg                      |                        |                 |                |                        |  |

|              |                   |                                                                                                                                                                                | nd Calendar did r                      | not trigger an a       | larm during De  | ep Sleep       |                        |  |

| bit 2        |                   | eep Sleep MC                                                                                                                                                                   |                                        |                        |                 |                |                        |  |

|              |                   | <ul> <li>1 = The MCLR pin was active and was asserted during Deep Sleep</li> <li>0 = The MCLR pin was not active, or was active, but not asserted during Deep Sleep</li> </ul> |                                        |                        |                 |                |                        |  |

| bit 1        | Unimpleme         | nted: Read as                                                                                                                                                                  | ʻ0 <b>'</b>                            |                        |                 |                |                        |  |

| bit 0        | DSPOR: De         | ep Sleep Powe                                                                                                                                                                  | r-on Reset Even                        | t bit <sup>(2,3)</sup> |                 |                |                        |  |

|              |                   |                                                                                                                                                                                | rcuit was active a rcuit was not act   |                        |                 |                | R event                |  |

| Note 1: A    | All register bits | are cleared wh                                                                                                                                                                 | en the DSEN (DS                        | SCON<15>) bit          | is set.         |                |                        |  |

|              | •                 |                                                                                                                                                                                | the case of a P                        | ,                      |                 | ep mode, ex    | cept bit.              |  |

All register bits are reset only in the case of a POR event outside of Deep Sleep mode, except bit, 2: DSPOR, which does not reset on a POR event that is caused due to a Deep Sleep exit.

3: Unlike the other bits in this register, this bit can be set outside of Deep Sleep.

### 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even numbered module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bit (ICxCON2<8>) for both modules.

### 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. If Synchronous mode is to be used, disable the Sync source before proceeding.

- 2. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 3. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired Sync/trigger source.

- Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSELx bits before the input capture module is enabled, for proper synchronization with the desired clock source.

- 5. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- 6. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 7. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 8. Enable the selected Sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same Sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bit settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the Sync source as the last step. Both input capture modules are held in Reset until the Sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the Sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

### EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 16-1: SAMPLE SCKx FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               |      | Secondary Prescaler Settings |      |      |      |      |  |

|----------------------------|------|------------------------------|------|------|------|------|--|

|                            | 1:1  | 2:1                          | 4:1  | 6:1  | 8:1  |      |  |

| Primary Prescaler Settings | 1:1  | Invalid                      | 8000 | 4000 | 2667 | 2000 |  |

|                            | 4:1  | 4000                         | 2000 | 1000 | 667  | 500  |  |

|                            | 16:1 | 1000                         | 500  | 250  | 167  | 125  |  |

|                            | 64:1 | 250                          | 125  | 63   | 42   | 31   |  |

| Fcy <b>= 5 MHz</b>         |      |                              |      |      |      |      |  |

| Primary Prescaler Settings | 1:1  | 5000                         | 2500 | 1250 | 833  | 625  |  |

|                            | 4:1  | 1250                         | 625  | 313  | 208  | 156  |  |

|                            | 16:1 | 313                          | 156  | 78   | 52   | 39   |  |

|                            | 64:1 | 78                           | 39   | 20   | 13   | 10   |  |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: SCKx frequencies are indicated in kHz.

NOTES:

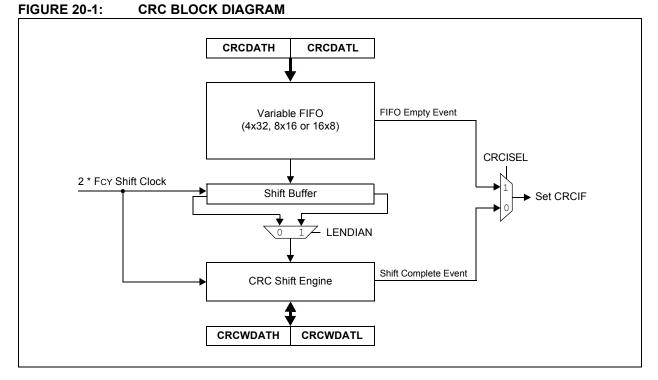

### 20.0 32-BIT PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 41. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS39729).

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- Independent data and polynomial lengths

- · Configurable interrupt output

- Data FIFO

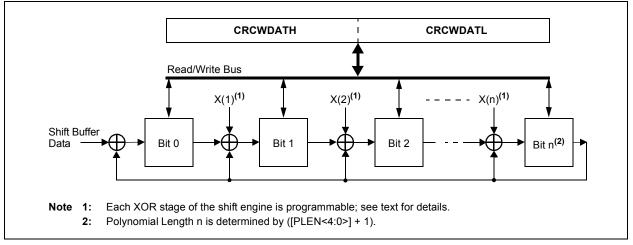

A simplified block diagram of the CRC generator is shown in Figure 20-1. A simple version of the CRC shift engine is shown in Figure 20-2.

### FIGURE 20-2: CRC SHIFT ENGINE DETAIL

#### REGISTER 24-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0           | U-0          | U-0                                  | U-0            | U-0               | U-0             | U-0             | U-0   |

|---------------|--------------|--------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| —             | —            | —                                    | _              | —                 | —               | —               |       |

| bit 15        |              |                                      |                |                   |                 |                 | bit   |

|               |              |                                      |                |                   |                 |                 |       |

| R/W-0         | R/W-0        | R/W-0                                | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| CVREN         | CVROE        | CVRSS                                | CVR4           | CVR3              | CVR2            | CVR1            | CVR0  |

| bit 7         |              |                                      |                |                   |                 |                 | bit ( |

|               |              |                                      |                |                   |                 |                 |       |

| Legend:       |              |                                      | ,              |                   |                 |                 |       |

| R = Readabl   |              | W = Writable                         |                | •                 | nented bit, rea |                 |       |

| -n = Value at | POR          | '1' = Bit is set                     |                | '0' = Bit is clea | ared            | x = Bit is unki | nown  |

| bit 15-8      | Unimplomon   | tod: Dood oo '                       | `,             |                   |                 |                 |       |

|               | -            | ted: Read as '                       |                |                   |                 |                 |       |

| bit 7         |              | nparator Voltage                     |                | nable bit         |                 |                 |       |

|               |              | rcuit is powered<br>rcuit is powered |                |                   |                 |                 |       |

| bit 6         |              | nparator VREF C                      |                | bit               |                 |                 |       |

|               |              | oltage level is o                    | •              |                   |                 |                 |       |

|               |              | •                                    | •              | rom the CVREF     | pin             |                 |       |

| bit 5         | CVRSS: Com   | parator VREF S                       | ource Selecti  | on bit            |                 |                 |       |

|               | 1 = Compara  | tor reference s                      | ource, CVRSR   | C = VREF + - V    | REF-            |                 |       |

|               | 0 = Compara  | tor reference s                      | ource, CVRSR   | c = AVDD - AV     | /ss             |                 |       |

| bit 4-0       | CVR<4:0>: C  | omparator VRE                        | F Value Selec  | tion 0 ≤ CVR<4    | :0> ≤ 31 bits   |                 |       |

|               | When CVRSS   |                                      |                |                   |                 |                 |       |

|               |              | EF-) + (CVR<4:(                      | )>/32) • (VREF | + – Vref-)        |                 |                 |       |

|               | When CVRSS   |                                      |                | () () ()          |                 |                 |       |

|               | UVREF = (AVS | ss) + (CVR<4:0                       | >/32) • (AVDD  | – AVSS)           |                 |                 |       |

|               |              |                                      |                |                   |                 |                 |       |

| REGISTER 2 | 26-4: FOSC | : OSCILLAT | OR CONFIGU | JRATION REC | SISTER   |         |         |

|------------|------------|------------|------------|-------------|----------|---------|---------|

| R/P-1      | R/P-1      | R/P-1      | R/P-1      | R/P-1       | R/P-1    | R/P-1   | R/P-1   |

| FCKSM1     | FCKSM0     | SOSCSEL    | POSCFREQ1  | POSCFREQ0   | OSCIOFNC | POSCMD1 | POSCMD0 |

| bit 7      |            |            |            |             |          |         | bit 0   |

|            |            |            |            |             |          |         |         |

| Legend:           |                      |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | <b>FCKSM&lt;1:0&gt;:</b> Clock Switching and Fail-Safe Clock Monitor Selection Configuration bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | SOSCSEL: Secondary Oscillator Power Selection Configuration bit                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Secondary oscillator is configured for high-power operation</li> <li>0 = Secondary oscillator is configured for low-power operation</li> </ul>                                                                                                                                                               |

| bit 4-3 | POSCFREQ<1:0>: Primary Oscillator Frequency Range Configuration bits                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Primary oscillator/external clock input frequency is greater than 8 MHz</li> <li>10 = Primary oscillator/external clock input frequency is between 100 kHz and 8 MHz</li> <li>01 = Primary oscillator/external clock input frequency is less than 100 kHz</li> <li>00 = Reserved; do not use</li> </ul>     |

| bit 2   | OSCIOFNC: CLKO Enable Configuration bit                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = CLKO output signal is active on the OSCO pin; primary oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMD&lt;1:0&gt; = 11 or 00)</li> <li>0 = CLKO output is disabled</li> </ul>                                                                    |

| bit 1-0 | POSCMD<1:0>: Primary Oscillator Configuration bits                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Primary Oscillator mode is disabled</li> <li>10 = HS Oscillator mode is selected</li> <li>01 = XT Oscillator mode is selected</li> <li>00 = External Clock mode is selected</li> </ul>                                                                                                                      |

| DC CHARACTERISTICS |                | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ |                        |    |      |                              |  |

|--------------------|----------------|----------------------------------------------------------|------------------------|----|------|------------------------------|--|

| Parameter No.      | Device         | Typical                                                  | Typical Max Units Conc |    |      |                              |  |

| IDD Current        |                |                                                          |                        |    |      |                              |  |

| D20                | PIC24FV32KA3XX | 269                                                      | 450                    | μA | 2.0V |                              |  |

|                    |                | 465                                                      | 830                    | μA | 5.0V | 0.5 MIPS,                    |  |

|                    | PIC24F32KA3XX  | 200                                                      | 330                    | μA | 1.8V | Fosc = 1 MHz <sup>(1)</sup>  |  |

|                    |                | 410                                                      | 750                    | μA | 3.3V |                              |  |

| DC22               | PIC24FV32KA3XX | 490                                                      | _                      | μA | 2.0V |                              |  |

|                    | PIC24F32KA3XX  | 880                                                      |                        | μA | 5.0V | 1 MIPS,                      |  |

|                    |                | 407                                                      |                        | μA | 1.8V | Fosc = 2 MHz <sup>(1)</sup>  |  |

|                    |                | 800                                                      |                        | μA | 3.3V |                              |  |

| DC24               | PIC24FV32KA3XX | 13.0                                                     | 20.0                   | mA | 5.0V | 16 MIPS,                     |  |

|                    | PIC24F32KA3XX  | 12.0                                                     | 18.0                   | mA | 3.3V | Fosc = 32 MHz <sup>(1)</sup> |  |

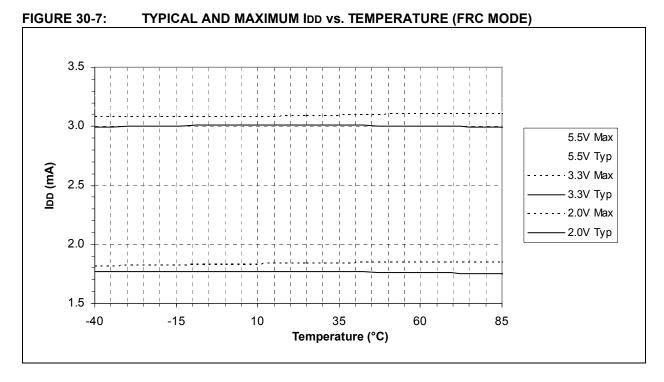

| DC26               | PIC24FV32KA3XX | 2.0                                                      |                        | mA | 2.0V |                              |  |

|                    |                | 3.5                                                      |                        | mA | 5.0V | FRC (4 MIPS),                |  |

|                    | PIC24F32KA3XX  | 1.80                                                     |                        | mA | 1.8V | Fosc = 8 MHz                 |  |

|                    |                | 3.40                                                     |                        | mA | 3.3V |                              |  |

| DC30               | PIC24FV32KA3XX | 48.0                                                     | 250                    | μA | 2.0V |                              |  |

|                    |                | 75.0                                                     | 450                    | μA | 5.0V | LPRC (15.5 KIPS),            |  |

|                    | PIC24F32KA3XX  | 8.1                                                      | 28                     | μA | 1.8V | Fosc = 31 kHz                |  |

|                    |                | 13.50                                                    | 150                    | μA | 3.3V |                              |  |

### TABLE 29-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

Legend: Unshaded rows represent PIC24F32KA3XX devices and shaded rows represent PIC24FV32KA3XX devices.

**Note 1:** Oscillator is in External Clock mode (FOSCSEL<2:0> = 010, FOSC<1:0> = 00).

|                    |       |                                                                                 | Standard Operating Conditions: 1.8V to 3.6V PIC24F32KA3XX<br>2.0V to 5.5V PIC24FV32KA3XX |                    |            |        |                                                                                                                                       |

|--------------------|-------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| DC CHARACTERISTICS |       |                                                                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                     |                    |            |        |                                                                                                                                       |

| Param<br>No.       | Sym   | Characteristic                                                                  | Min                                                                                      | Typ <sup>(1)</sup> | Max        | Units  | Conditions                                                                                                                            |

|                    | VIL   | Input Low Voltage <sup>(4)</sup>                                                |                                                                                          |                    |            |        |                                                                                                                                       |

| DI10               |       | I/O Pins                                                                        | Vss                                                                                      |                    | 0.2 Vdd    | V      |                                                                                                                                       |

| DI15               |       | MCLR                                                                            | Vss                                                                                      | —                  | 0.2 Vdd    | V      |                                                                                                                                       |

| DI16               |       | OSCI (XT mode)                                                                  | Vss                                                                                      | —                  | 0.2 Vdd    | V      |                                                                                                                                       |

| DI17               |       | OSCI (HS mode)                                                                  | Vss                                                                                      |                    | 0.2 Vdd    | V      |                                                                                                                                       |

| DI18               |       | I/O Pins with I <sup>2</sup> C™ Buffer                                          | Vss                                                                                      | _                  | 0.3 Vdd    | V      | SMBus is disabled                                                                                                                     |

| DI19               |       | I/O Pins with SMBus Buffer                                                      | Vss                                                                                      |                    | 0.8        | V      | SMBus is enabled                                                                                                                      |

|                    | Vih   | Input High Voltage <sup>(4)</sup>                                               |                                                                                          |                    |            |        |                                                                                                                                       |

| DI20               |       | I/O Pins:<br>with Analog Functions<br>Digital Only                              | 0.8 Vdd<br>0.8 Vdd                                                                       | _                  | Vdd<br>Vdd | V<br>V |                                                                                                                                       |

| DI25               |       | MCLR                                                                            | 0.8 VDD                                                                                  | _                  | Vdd        | V      |                                                                                                                                       |

| DI26               |       | OSCI (XT mode)                                                                  | 0.7 Vdd                                                                                  | _                  | Vdd        | V      |                                                                                                                                       |

| DI27               |       | OSCI (HS mode)                                                                  | 0.7 Vdd                                                                                  | _                  | Vdd        | V      |                                                                                                                                       |

| DI28               |       | I/O Pins with I <sup>2</sup> C Buffer:<br>with Analog Functions<br>Digital Only | 0.7 Vdd<br>0.7 Vdd                                                                       |                    | Vdd<br>Vdd | V<br>V |                                                                                                                                       |

| DI29               |       | I/O Pins with SMBus                                                             | 2.1                                                                                      | _                  | Vdd        | V      | $2.5V \le V\text{PIN} \le V\text{DD}$                                                                                                 |

| DI30               | ICNPU | CNx Pull-up Current                                                             | 50                                                                                       | 250                | 500        | μA     | VDD = 3.3V, VPIN = VSS                                                                                                                |

|                    | lı∟   | Input Leakage<br>Current <sup>(2,3)</sup>                                       |                                                                                          |                    |            |        |                                                                                                                                       |

| DI50               |       | I/O Ports                                                                       | _                                                                                        | 0.05               | 0.1        | μA     | $\label{eq:VSS} \begin{split} &VSS \leq V PIN \leq V DD, \\ &Pin \text{ at high-impedance} \end{split}$                               |

| DI55               |       | MCLR                                                                            | _                                                                                        | —                  | 0.1        | μA     | $VSS \leq VPIN \leq VDD$                                                                                                              |

| DI56               |       | OSCI                                                                            | _                                                                                        | _                  | 5          | μA     | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$ |

#### TABLE 29-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

4: Refer to Table 1-3 for I/O pin buffer types.

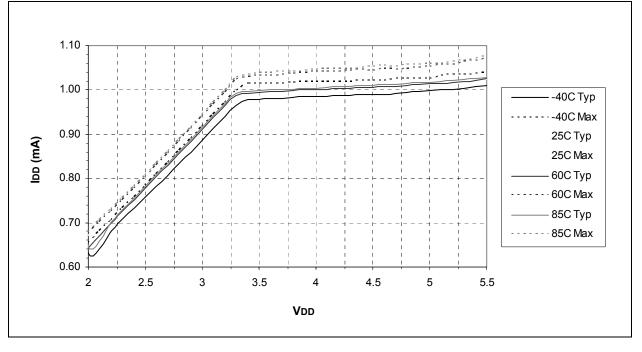

FIGURE 30-8: TYPICAL AND MAXIMUM lidle vs. Vdd (FRC MODE)

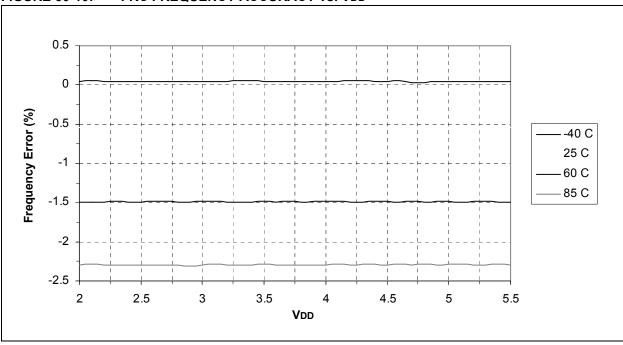

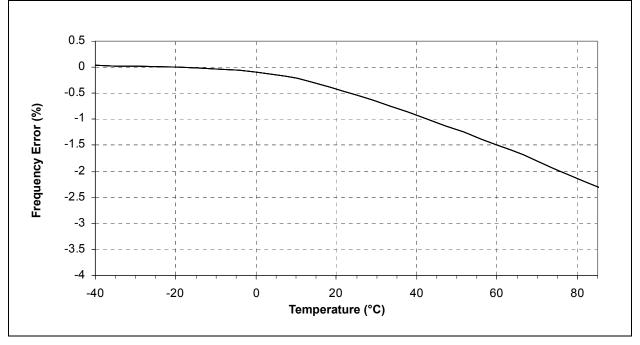

FIGURE 30-10: FRC FREQUENCY ACCURACY vs. VDD

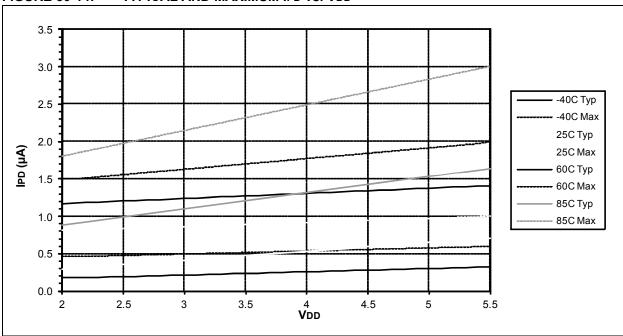

#### FIGURE 30-14: TYPICAL AND MAXIMUM IPD vs. VDD

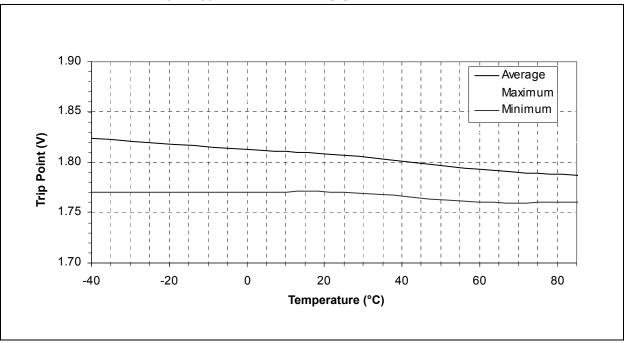

FIGURE 30-36: HLVD TRIP POINT VOLTAGE vs. TEMPERATURE (HLVDL<3:0> = 0000, PIC24F32KA304 FAMILY DEVICES ONLY

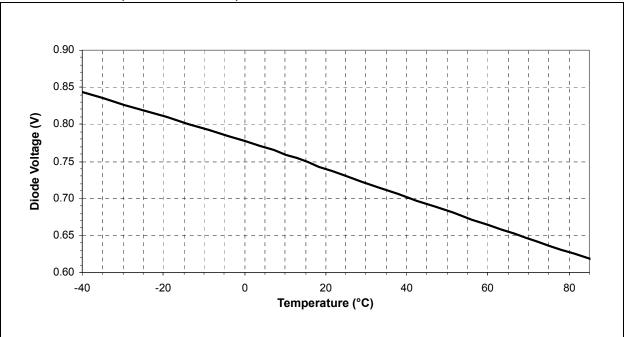

FIGURE 30-37: TEMPERATURE SENSOR DIODE VOLTAGE vs. TEMPERATURE (2.0V  $\leq$  VDD  $\leq$  5.5V)

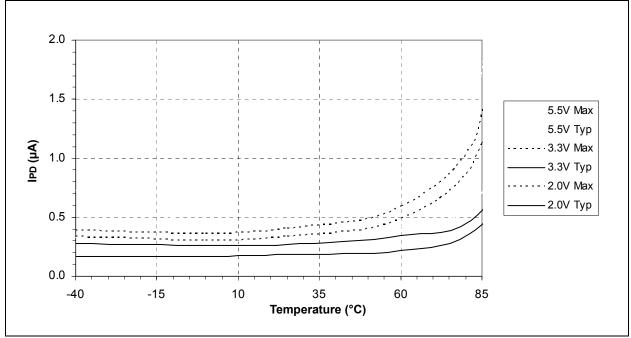

FIGURE 30-44: TYPICAL AND MAXIMUM IPD vs. VDD (DEEP SLEEP MODE)

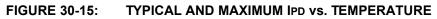

#### FIGURE 30-45: TYPICAL AND MAXIMUM IPD vs. TEMPERATURE (DEEP SLEEP MODE)

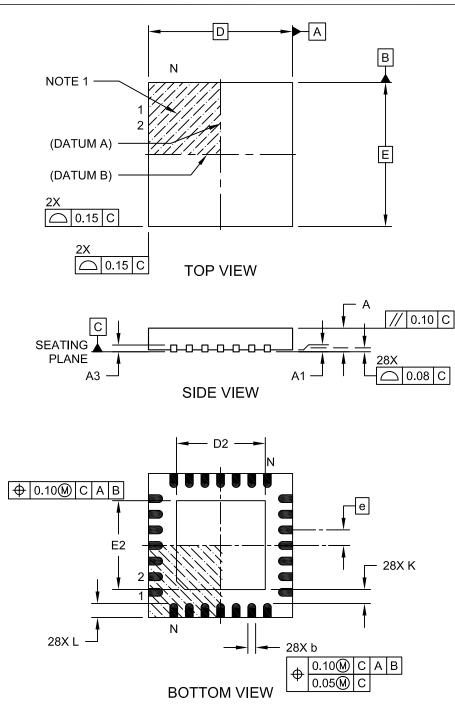

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2