Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka302-e-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.4 Voltage Regulator Pin (VCAP)

| Note: | This section applies only to PIC24F K      |

|-------|--------------------------------------------|

|       | devices with an On-Chip Voltage Regulator. |

Some of the PIC24F K devices have an internal Voltage Regulator. These devices have the Voltage Regulator output brought out on the VCAP pin. On the PIC24F K devices with regulators, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the Voltage Regulator output. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

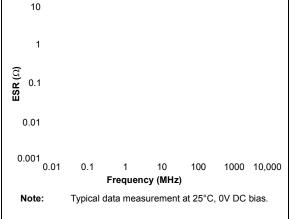

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 29.0** "**Electrical Characteristics**" for additional information. Refer to **Section 29.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

### FIGURE 2-3: FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |

|-----------|--------------------|------------------------|----------------|---------------|--------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

### TABLE 4-9: I2Cx REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 | —       | _      | _       | _      | _      | _      | —      | _     |       |       |       | I2CF  | RCV   |       |       |       | 0000          |

| I2C1TRN   | 0202 | _       | _      | _       | —      | _      | _      | _      | _     |       |       |       | I2CT  | RN    |       |       |       | OOFF          |

| I2C1BRG   | 0204 | _       | _      | _       | —      | _      | _      | _      | _     |       |       |       | I2CE  | BRG   |       |       |       | 0000          |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | _       | _      | _       | —      | _      | _      |        |       |       |       | I2CA  | DD    |       |       |       |       | 0000          |

| I2C1MSK   | 020C | —       | _      | _       | —      | —      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

| I2C2RCV   | 0210 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CF  | RCV   |       |       |       | 0000          |

| I2C2TRN   | 0212 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CT  | RN    |       |       |       | OOFF          |

| I2C2BRG   | 0214 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CE  | BRG   |       |       |       | 0000          |

| I2C2CON   | 0216 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT  | 0218 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD   | 021A | _       |        | _       | _      |        | _      |        | -     |       | •     | I2CA  | DD    | •     | •     | •     | •     | 0000          |

| I2C2MSK   | 021C | _       |        | _       | _      | _      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-10: UARTx REGISTER MAP

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|----------|--------|----------|--------|--------|--------|-------|-------|----------|----------|-------|-------|-------|--------|--------|-------|---------------|

| U1MODE       | 0220 | UARTEN   | _      | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | —        |        | —        |        | _      |        | _     |       |          |          | U1T   | XREG  |       |        |        |       | XXXX          |

| U1RXREG      | 0226 | —        |        | —        |        | _      |        | _     |       |          |          | U1F   | RXREG |       |        |        |       | 0000          |

| U1BRG        | 0228 |          |        |          |        |        |        |       | I     | BRG      |          |       |       |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _        | _      | _        | —      | _      | _      | _     |       |          |          | U2T   | XREG  |       |        |        |       | XXXX          |

| U2RXREG      | 0236 | —        |        | —        |        | —      |        | _     |       |          |          | U2F   | RXREG |       |        |        |       | 0000          |

| U2BRG        | 0238 |          |        |          |        |        |        |       |       | BRG      |          |       |       |       |        |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-21: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|---------|---------|---------|---------|---------|--------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1      | 0640 | CRCEN  | —      | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0  | CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | —     | —     | —     | 0000          |

| CRCCON2      | 0642 | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0 | _      | _      | —       | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL      | 0644 | X15    | X14    | X13    | X12     | X11     | X10     | X9      | X8      | X7     | X6     | X5      | X4    | X3      | X2    | X1    | _     | 0000          |

| CRCXORH      | 0646 | X31    | X30    | X29    | X28     | X27     | X26     | X25     | X24     | X23    | X22    | X21     | X20   | X19     | X18   | X17   | X16   | 0000          |

| CRCDATL      | 0648 |        |        |        |         |         |         |         | CRCDA   | TL     |        |         |       |         |       |       |       | XXXX          |

| CRCDATH      | 064A |        |        |        |         |         |         |         | CRCDA   | ГН     |        |         |       |         |       |       |       | XXXX          |

| CRCWDATL     | 064C |        |        |        |         |         |         |         | CRCWD   | ATL .  |        |         |       |         |       |       |       | XXXX          |

| CRCWDATH     | 064E |        |        |        |         |         |         |         | CRCWDA  | ΛTH    |        |         |       |         |       |       |       | XXXX          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: CLOCK CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | RETEN  | —      | DPSLP  | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3140          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   | _      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | _      | HLSIDL | _      | _      | _      | _      | -      | VDIR    | BGVST | IRVST  | —     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses and by type of Reset.

### TABLE 4-23: DEEP SLEEP REGISTER MAP

| File Name             | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1 | Bit 0   | All<br>Resets |

|-----------------------|------|--------|--------|--------|--------|--------|--------|-------|----------|--------|-------|-------|-------|--------|---------|-------|---------|---------------|

| DSCON                 | 0758 | DSEN   | _      | —      | —      | _      | _      | _     | RTCCWDIS | _      | —     | —     |       | —      | ULPWDIS | DSBOR | RELEASE | 0000          |

| DSWAKE                | 075A | _      | -      | _      | _      | -      | -      | _     | DSINT0   | DSFLT  | _     | _     | DSWDT | DSRTCC | DSMCLR  | _     | DSPOR   | 0000          |

| DSGPR0 <sup>(1)</sup> | 075C |        |        |        |        |        |        |       |          | DSGPR0 |       |       |       |        |         |       |         | 0000          |

| DSGPR1 <sup>(1)</sup> | 075E |        |        |        |        |        |        |       |          | DSGPR1 |       |       |       |        |         |       |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Deep Sleep registers, DSGPR0 and DSGPR1, are only reset on a VDD POR event.

### 8.3 Interrupt Control and Status Registers

The PIC24FV32KA304 family of devices implements a total of 23 registers for the interrupt controller:

- INTCON1

- INTCON2

- · IFS0, IFS1, IFS3 and IFS4

- · IEC0, IEC1, IEC3 and IEC4

- IPC0 through IPC5, IPC7 and IPC15 through IPC19

- INTTREG

Global Interrupt Enable (GIE) control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIVT.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU Interrupt Priority Level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All Interrupt registers are described in Register 8-1 through Register 8-33, in the following sections.

NOTES:

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enabled bit                                                |  |

|---------|------------------------------------------------------------------------------------------|--|

|         | If FSCM is enabled (FCKSM1 = <u>1):</u>                                                  |  |

|         | 1 = Clock and PLL selections are locked                                                  |  |

|         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |  |

|         | If FSCM is disabled (FCKSM1 = 0):                                                        |  |

|         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |  |

| bit 6   | Unimplemented: Read as '0'                                                               |  |

| bit 5   | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                 |  |

|         | 1 = PLL module is in lock or PLL module start-up timer is satisfied                      |  |

|         | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled          |  |

| bit 4   | Unimplemented: Read as '0'                                                               |  |

| bit 3   | CF: Clock Fail Detect bit                                                                |  |

|         | 1 = FSCM has detected a clock failure                                                    |  |

|         | 0 = No clock failure has been detected                                                   |  |

| bit 2   | SOSCDRV: Secondary Oscillator Drive Strength bit <sup>(3)</sup>                          |  |

|         | 1 = High-power SOSC circuit is selected                                                  |  |

|         | 0 = Low/high-power select is done via the SOSCSRC Configuration bit                      |  |

| bit 1   | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |  |

|         | 1 = Enables the secondary oscillator                                                     |  |

|         | 0 = Disables the secondary oscillator                                                    |  |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                      |  |

|         | 1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits   |  |

|         | 0 = Oscillator switch is complete                                                        |  |

| Note 1: | Reset values for these bits are determined by the FNOSCx Configuration bits.             |  |

- 2: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O Ports, refer to the "PIC24F Family Reference Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24FV32KA304 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

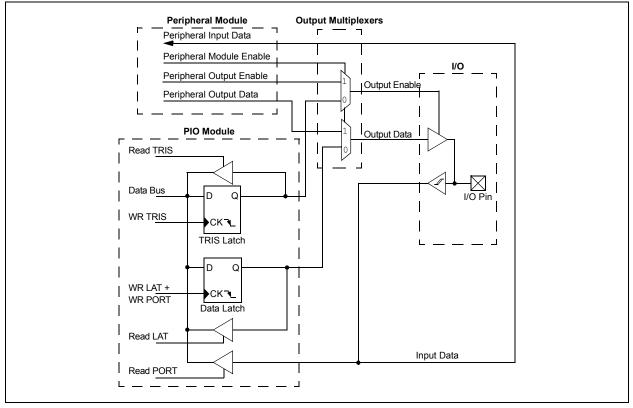

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LAT), read the latch. Writes to the latch, write the latch. Reads from the port (PORT), read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The maximum open-drain voltage allowed is the same as the maximum  $V_{\text{IH}}$  specification.

### 11.2 Configuring Analog Port Pins

The use of the ANS and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

### 11.2.1 ANALOG SELECTION REGISTERS

I/O pins with shared analog functionality, such as A/D inputs and comparator inputs, must have their digital inputs shut off when analog functionality is used. Note that analog functionality includes an analog voltage being applied to the pin externally.

To allow for analog control, the ANSx registers are provided. There is one ANS register for each port (ANSA, ANSB and ANSC). Within each ANSx register, there is a bit for each pin that shares analog functionality with the digital I/O functionality.

If a particular pin does not have an analog function, that bit is unimplemented. See Register 11-1 to Register 11-3 for implementation.

### REGISTER 11-1: ANSA: ANALOG SELECTION (PORTA)

| U-0           | U-0   | U-0              | U-0 | U-0               | U-0              | U-0             | U-0   |

|---------------|-------|------------------|-----|-------------------|------------------|-----------------|-------|

| —             | —     | —                | —   | —                 | —                | —               | —     |

| bit 15        |       |                  |     |                   |                  |                 | bit 8 |

|               |       |                  |     |                   |                  |                 |       |

| U-0           | U-0   | U-0              | U-0 | R/W-1             | R/W-1            | R/W-1           | R/W-1 |

|               | —     | —                | —   | ANSA3             | ANSA2            | ANSA1           | ANSA0 |

| bit 7         |       |                  |     |                   |                  |                 | bit 0 |

|               |       |                  |     |                   |                  |                 |       |

| Legend:       |       |                  |     |                   |                  |                 |       |

| R = Readable  | e bit | W = Writable I   | bit | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-4 Unimplemented: Read as '0'

bit 3-0 ANSA<3:0>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

# 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 34. "Input Capture with Dedicated Timer" (DS39722).

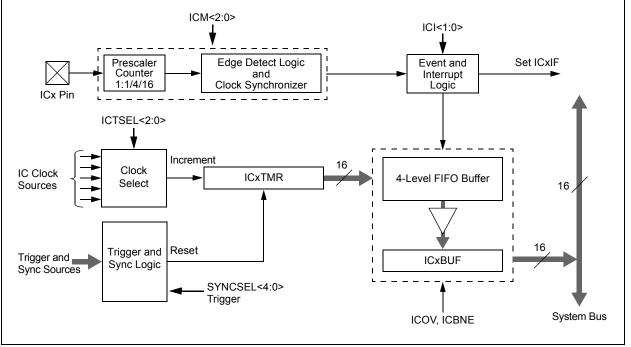

All devices in the PIC24FV32KA304 family feature three independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events, and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 20 user-selectable Sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

### 14.1 General Operating Modes

### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the input capture module operates in a Free-Running mode. The internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected Sync source, the internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSELx bits to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the Sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

### 15.3.1 PWM PERIOD

In Edge-Aligned PWM mode, the period is specified by the value of the OCxRS register. In Center-Aligned PWM mode, the period of the synchronization source, such as the Timers' PRy, specifies the period. The period in both cases can be calculated using Equation 15-1.

### EQUATION 15-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period = [Value + 1] x TCY x (Prescaler Value)

Where:

Value = OCxRS in Edge-Aligned PWM mode and can be PRy in Center-Aligned PWM mode (if TMRy is the Sync source).

**Note 1:** Based on Tcy = Tosc \* 2; Doze mode and PLL are disabled.

### 15.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS and OCxR registers. The OCxRS and OCxR registers can be written to at any time, but the duty cycle value is not latched until a period is complete. This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation.

Some important boundary parameters of the PWM duty cycle include:

- Edge-Aligned PWM:

- If OCxR and OCxRS are loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than OCxR, the pin will remain high (100% duty cycle).

- Center-Aligned PWM (with TMRy as the Sync source):

- If OCxR, OCxRS and PRy are all loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than PRy, the pin will go high (100% duty cycle).

See Example 15-3 for PWM mode timing details. Table 15-1 and Table 15-2 show example PWM frequencies and resolutions for a device operating at 4 MIPS and 10 MIPS, respectively.

### EQUATION 15-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

Maximum PWM Resolution (bits) =

$$\frac{\log_{10} \left( \frac{F_{CY}}{F_{PWM} \cdot (Prescale Value)} \right)}{\log_{10}(2)}$$

bits

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### EQUATION 15-3: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

Find the OCxRS register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a prescaler setting of 1:1 using Edge-Aligned PWM mode:

TCY = 2 • Tosc = 62.5 ns

PWM Period = 1/PWM Frequency = 1/52.08 kHz = 19.2 μs

PWM Period = (OCxRS + 1) • TCY • (OCx Prescale Value)

19.2 μs = (OCxRS + 1) • 62.5 ns • 1

OCxRS = 306

OCxRS = 306

Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution = log<sub>10</sub>(FCY/FPWM)/log<sub>10</sub>2) bits

= (log<sub>10</sub>(16 MHz/52.08 kHz)/log<sub>10</sub>2) bits

= 8.3 bits

= 8.3 bits

= 1/2

= 1/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

= 0/2

**Note 1:** Based on TCY = 2 \* TOSC; Doze mode and PLL are disabled.

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This output compare module<sup>(1)</sup>

- 11110 = **Reserved** 11101 = Reserved 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 100xx = Reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1

- 01010 = Input Capture 5<sup>(2)</sup>

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Output Compare 5<sup>(1)</sup>

- 00100 = Output Compare 4<sup>(1)</sup>

- 00011 = Output Compare 3<sup>(1)</sup>

- 00010 = Output Compare 2<sup>(1)</sup>

- 00001 = Output Compare 1<sup>(1)</sup>

- 00000 = Not synchronized to any other module

- Note 1: Do not use an output compare module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as trigger sources only and never as Sync sources.

- 3: These bits affect the rising edge when OCINV = 1. The bits have no effect when the OCMx bits (OCxCON1<2:0>) = 001.

### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of  |

|-------|---------------------------------------------|

|       | this group of PIC24F devices. It is not     |

|       | intended to be a comprehensive reference    |

|       | source. For more information on the Univer- |

|       | sal Asynchronous Receiver Transmitter,      |

|       | refer to the "PIC24F Family Reference       |

|       | Manual", Section 21. "UART" (DS39708).      |

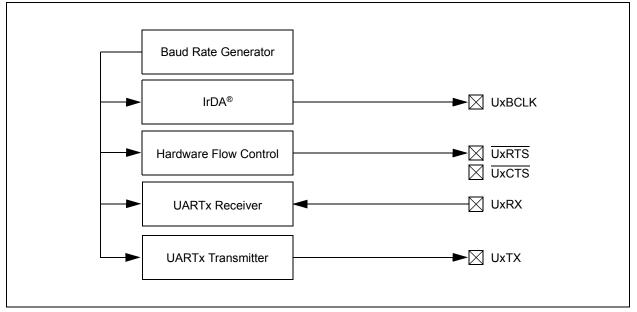

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx is shown in Figure 18-1. The UARTx module consists of these important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

- Note: Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

### FIGURE 18-1: UARTX SIMPLIFIED BLOCK DIAGRAM

### 22.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", Section 51. "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (Internal and External)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU and a configurable results buffer. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 22-1.

| U-0          | U-0   | U-0           | U-0   | U-0          | U-0             | R/C-1    | R/C-1 |

|--------------|-------|---------------|-------|--------------|-----------------|----------|-------|

| —            |       | —             | _     | —            |                 | GSS0     | GWRP  |

| bit 7        | •     |               | •     |              |                 |          | bit 0 |

|              |       |               |       |              |                 |          |       |

| Legend:      |       |               |       |              |                 |          |       |

| R = Readable | hit   | C = Clearable | hit   | U = Unimplem | onted hit read  | 1 26 '0' |       |

| R = Readable | , DIL |               | , DIL |              | chica bit, icac |          |       |

| bit 7-2 | Unimplemented: Read as '0'                                                                          |

|---------|-----------------------------------------------------------------------------------------------------|

| bit 1   | GSS0: General Segment Code Flash Code Protection bit                                                |

|         | <ul><li>1 = No protection</li><li>0 = Standard security is enabled</li></ul>                        |

| bit 0   | GWRP: General Segment Code Flash Write Protection bit                                               |

|         | <ul><li>1 = General segment may be written</li><li>0 = General segment is write-protected</li></ul> |

**REGISTER 26-2: FGS: GENERAL SEGMENT CONFIGURATION REGISTER**

### **REGISTER 26-3:** FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| R/P-1 | R/P-1   | R/P-1   | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  |

|-------|---------|---------|-----|-----|--------|--------|--------|

| IESO  | LPRCSEL | SOSCSRC | —   | —   | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7 |         |         |     |     |        |        | bit 0  |

| Legend:                                                           |                   |                                                                    |                                    |                    |  |  |  |

|-------------------------------------------------------------------|-------------------|--------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit                                                  |                   | P = Programmable bit                                               | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value                                                        | at POR            | '1' = Bit is set                                                   | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

|                                                                   |                   |                                                                    |                                    |                    |  |  |  |

| bit 7                                                             | IESO: Inte        | ernal External Switchover bit                                      |                                    |                    |  |  |  |

|                                                                   |                   | al External Switchover mode is<br>al External Switchover mode is   |                                    |                    |  |  |  |

| bit 6                                                             | LPRCSEL           | .: Internal LPRC Oscillator Pow                                    | ver Select bit                     |                    |  |  |  |

| 1 = High-Power/High-Accuracy mo<br>0 = Low-Power/Low-Accuracy mod |                   |                                                                    |                                    |                    |  |  |  |

| bit 5                                                             | SOSCSR            | C: Secondary Oscillator Clock                                      | Source Configuration bit           |                    |  |  |  |

|                                                                   |                   | analog crystal function is ava<br>crystal is disabled; digital SCI |                                    | -                  |  |  |  |

| bit 4-3                                                           | Unimplen          | nented: Read as '0'                                                |                                    |                    |  |  |  |

| bit 2-0                                                           | FNOSC<2           | 2:0>: Oscillator Selection bits                                    |                                    |                    |  |  |  |

|                                                                   | 000 <b>= Fa</b> s | st RC Oscillator (FRC)                                             |                                    |                    |  |  |  |

|                                                                   |                   | st RC Oscillator with Divide-by-                                   | N with PLL module (FRCD            | V+PLL)             |  |  |  |

- 010 = Primary Oscillator (XT, HS, EC)

- 011 = Primary Oscillator with PLL module (HS+PLL, EC+PLL)

- 100 = Secondary Oscillator (SOSC)

- 101 = Low-Power RC Oscillator (LPRC)

- 110 = 500 kHz Low-Power FRC Oscillator with Divide-by-N (LPFRCDIV)

- 111 = 8 MHz FRC Oscillator with Divide-by-N (FRCDIV)

| R/P-1                                                                                                                                                                | R/P-1                                                                        | U-0                                                                        | R/P-1                         | R/P-1             | R/P-1            | R/P-1           | R/P-1    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|-------------------|------------------|-----------------|----------|--|--|

| DSWDTEN                                                                                                                                                              | DSBOREN                                                                      | _                                                                          | DSWDTOSC                      | DSWDTPS3          | DSWDTPS2         | DSWDTPS1        | DSWDTPS0 |  |  |

| bit 7                                                                                                                                                                |                                                                              |                                                                            |                               |                   |                  |                 | bit 0    |  |  |

|                                                                                                                                                                      |                                                                              |                                                                            |                               |                   |                  |                 |          |  |  |

| Legend:                                                                                                                                                              |                                                                              |                                                                            |                               |                   |                  |                 |          |  |  |

| R = Readabl                                                                                                                                                          | le bit                                                                       | P = Program                                                                | nable bit                     | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |

| -n = Value at                                                                                                                                                        | t POR                                                                        | '1' = Bit is set                                                           |                               | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |

|                                                                                                                                                                      |                                                                              |                                                                            |                               |                   |                  |                 |          |  |  |

| bit 7                                                                                                                                                                |                                                                              |                                                                            | chdog Timer Er                | nable bit         |                  |                 |          |  |  |

|                                                                                                                                                                      | 1 = DSWDT is<br>0 = DSWDT is                                                 |                                                                            |                               |                   |                  |                 |          |  |  |

| bit 6                                                                                                                                                                |                                                                              |                                                                            | Power BOR En<br>on Deep Sleep |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 1 = Deep Slee                                                                | p BOR is enab                                                              | led in Deep Sle               | ер                |                  |                 |          |  |  |

| bit 5                                                                                                                                                                |                                                                              | 0 = Deep Sleep BOR is disabled in Deep Sleep<br>Unimplemented: Read as '0' |                               |                   |                  |                 |          |  |  |

| bit 4                                                                                                                                                                | DSWDTOSC:                                                                    | DSWDT Refer                                                                | ence Clock Sele               | ect bit           |                  |                 |          |  |  |

|                                                                                                                                                                      | 1 = DSWDT uses LPRC as the reference clock                                   |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      |                                                                              |                                                                            | he reference clo              |                   |                  |                 |          |  |  |

| bit 3-0 <b>DSWDTPS&lt;3:0&gt;:</b> Deep Sleep Watchdog Timer Postscale Select bits<br>The DSWDT prescaler is 32; this creates an approximate base time unit of 1 ms. |                                                                              |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | •                                                                            |                                                                            |                               | • •               | ase time unit o  | t i ms.         |          |  |  |

| 1111 = 1:2,147,483,648 (25.7 days) nominal<br>1110 = 1:536,870,912 (6.4 days) nominal                                                                                |                                                                              |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 1101 = 1:134,2                                                               |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 1100 <b>= 1:33,5</b>                                                         | •                                                                          | ,                             |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 1011 = 1:8,388<br>1010 = 1:2,097                                             |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 1010 = 1.2,091<br>1001 = 1:524,2                                             |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 1000 = 1:131,0                                                               |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 0111 = 1:32,768 (34 seconds) nominal                                         |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 0110 = 1:8,192 (8.5 seconds) nominal<br>0101 = 1:2,048 (2.1 seconds) nominal |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 0101 = 1.2,040<br>0100 = 1:512 (                                             |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 0011 = 1:128 (                                                               |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      | 0010 = 1:32 (33 ms) nominal<br>0001 = 1:8 (8.3 ms) nominal                   |                                                                            |                               |                   |                  |                 |          |  |  |

|                                                                                                                                                                      |                                                                              |                                                                            |                               |                   |                  |                 |          |  |  |

### 29.1 DC Characteristics

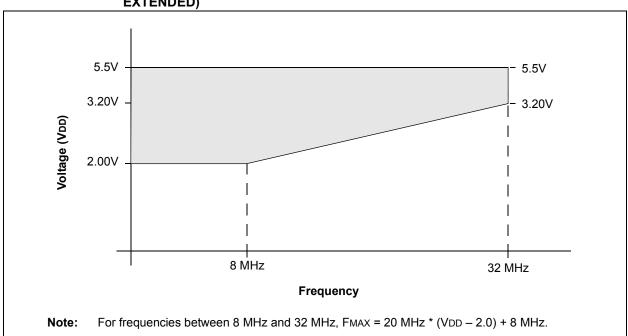

### FIGURE 29-1: PIC24FV32KA304 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL AND EXTENDED)

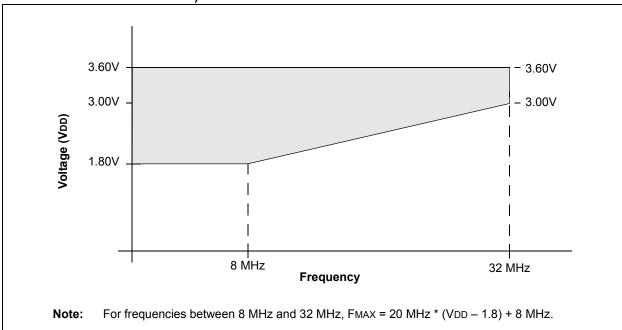

### FIGURE 29-2: PIC24F32KA304 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL AND EXTENDED)

### TABLE 29-40: A/D MODULE SPECIFICATIONS

|              |           |                                                      | Standard Opera                                       | ting C |                                |       |                                                |  |

|--------------|-----------|------------------------------------------------------|------------------------------------------------------|--------|--------------------------------|-------|------------------------------------------------|--|

| AC CHA       | ARACTERI  | STICS                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |                                |       |                                                |  |

| Param<br>No. | Symbol    | Characteristic                                       | Min.                                                 | Тур    | Max.                           | Units | Conditions                                     |  |

|              |           |                                                      | Device S                                             | upply  |                                |       |                                                |  |

| AD01         | AVDD      | Module VDD Supply                                    | Greater of:<br>VDD – 0.3 or 1.8                      |        | Lesser of:<br>VDD + 0.3 or 3.6 | V     | PIC24FXXKA30X devices                          |  |

|              |           |                                                      | Greater of:<br>VDD – 0.3 or 2.0                      |        | Lesser of:<br>VDD + 0.3 or 5.5 | V     | PIC24FVXXKA30X<br>devices                      |  |

| AD02         | AVss      | Module Vss Supply                                    | Vss – 0.3                                            |        | Vss + 0.3                      | V     |                                                |  |

|              |           | 1                                                    | Reference                                            | Inputs | 6                              |       |                                                |  |

| AD05         | VREFH     | Reference Voltage High                               | AVss + 1.7                                           | —      | AVDD                           | V     |                                                |  |

| AD06         | VREFL     | Reference Voltage Low                                | AVss                                                 | —      | AVDD – 1.7                     | V     |                                                |  |

| AD07         | Vref      | Absolute Reference<br>Voltage                        | AVss – 0.3                                           |        | AVDD + 0.3                     | V     |                                                |  |

| AD08         | IVREF     | Reference Voltage Input<br>Current                   | _                                                    | 1.25   | —                              | mA    |                                                |  |

| AD09         | Zvref     | Reference Input<br>Impedance                         | —                                                    | 10k    | —                              | Ω     |                                                |  |

|              |           |                                                      | Analog                                               | nput   |                                |       | ·                                              |  |

| AD10         | VINH-VINL | Full-Scale Input Span                                | VREFL                                                |        | VREFH                          | V     | (Note 2)                                       |  |

| AD11         | VIN       | Absolute Input Voltage                               | AVss - 0.3                                           |        | AVDD + 0.3                     | V     |                                                |  |

| AD12         | VINL      | Absolute Vın∟ Input<br>Voltage                       | AVss – 0.3                                           |        | AVDD/2                         | V     |                                                |  |

| AD17         | RIN       | Recommended<br>Impedance of Analog<br>Voltage Source | —                                                    | _      | 1k                             | Ω     | 12-bit                                         |  |

|              |           |                                                      | A/D Acc                                              | uracy  |                                |       |                                                |  |

| AD20b        | NR        | Resolution                                           | —                                                    | 12     | —                              | bits  |                                                |  |

| AD21b        | INL       | Integral Nonlinearity                                | _                                                    | ±1     | ±9                             | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |  |

| AD22b        | DNL       | Differential Nonlinearity                            | —                                                    | ±1     | ±5                             | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |  |

| AD23b        | Gerr      | Gain Error                                           | —                                                    | ±1     | ±9                             | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |  |

| AD24b        | EOFF      | Offset Error                                         | _                                                    | ±1     | ±5                             | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V |  |

| AD25b        |           | Monotonicity <sup>(1)</sup>                          |                                                      | _      | _                              | _     | Guaranteed                                     |  |

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage.

2: Measurements are taken with external VREF+ and VREF- used as the A/D voltage reference.

NOTES:

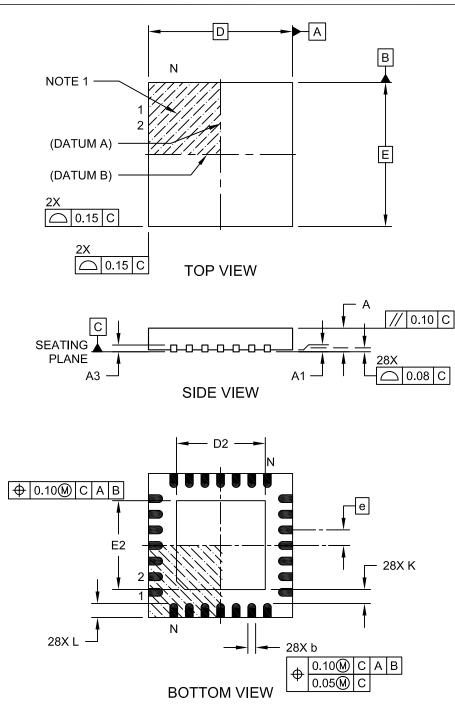

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2