#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka302-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE I-I. DEVICE FEATO                            |                     |                               |                   |                |                                              |                |  |  |  |  |

|----------------------------------------------------|---------------------|-------------------------------|-------------------|----------------|----------------------------------------------|----------------|--|--|--|--|

| Features                                           | PIC24FV16KA301      | PIC24FV32KA301                | PIC24FV16KA302    | PIC24FV32KA302 | PIC24FV16KA304                               | PIC24FV32KA304 |  |  |  |  |

| Operating Frequency                                | DC – 32 MHz         |                               |                   |                |                                              |                |  |  |  |  |

| Program Memory (bytes)                             | 16K                 | 32K                           | 16K               | 32K            | 16K                                          | 32K            |  |  |  |  |

| Program Memory (instructions)                      | 5632                | 11264                         | 5632              | 11264          | 5632                                         | 11264          |  |  |  |  |

| Data Memory (bytes)                                |                     |                               | 2048              |                |                                              |                |  |  |  |  |

| Data EEPROM Memory (bytes)                         |                     |                               | 512               |                |                                              |                |  |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)     |                     |                               | 30 (26/           | 4)             |                                              |                |  |  |  |  |

| I/O Ports                                          | PORTA<br>PORTB<15:1 |                               | PORTA<br>PORTB    |                | PORTA<11:7,5:0><br>PORTB<15:0><br>PORTC<9:0> |                |  |  |  |  |

| Total I/O Pins                                     | 17                  | 7                             | 2                 | 3              | 3                                            | 8              |  |  |  |  |

| Timers: Total Number (16-bit)                      | 5                   |                               |                   |                |                                              |                |  |  |  |  |

| 32-Bit (from paired 16-bit timers)                 |                     |                               | 2                 |                |                                              |                |  |  |  |  |

| Input Capture Channels                             |                     |                               | 3                 |                |                                              |                |  |  |  |  |

| Output Compare/PWM Channels                        |                     |                               | 3                 |                |                                              |                |  |  |  |  |

| Input Change Notification Interrupt                | 16                  | 6                             | 2                 | 2              | 3                                            | 7              |  |  |  |  |

| Serial Communications: UART<br>SPI (3-wire/4-wire) |                     |                               | 2                 |                |                                              |                |  |  |  |  |

| I <sup>2</sup> C™                                  |                     |                               | 2                 |                |                                              |                |  |  |  |  |

| 12-Bit Analog-to-Digital Module (input channels)   | 12                  | 2                             | 1:                | 3              | 1                                            | 6              |  |  |  |  |

| Analog Comparators                                 |                     |                               | 3                 |                |                                              |                |  |  |  |  |

| Resets (and delays)                                |                     | BOR, RESET<br>Instruction, Ha |                   | , Configurati  |                                              |                |  |  |  |  |

| Instruction Set                                    | 76 B                | ase Instructio                | ns, Multiple A    | ddressing M    | ode Variation                                | s              |  |  |  |  |

| Packages                                           | 20-F<br>PDIP/SSC    |                               | 28-<br>SPDIP/SSOF |                | 44-Pin QI<br>48-Pin                          |                |  |  |  |  |

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                | 1   |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 1/0 | Buffer            | Description                       |

| AN0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | Т   | ANA               |                                   |

| AN2      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               |                                   |

| AN3      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               |                                   |

| AN4      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ANA               |                                   |

| AN5      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I   | ANA               |                                   |

| AN6      | _                                | _                                 | _             | 25                     | 27             | _                                | _                                 | _             | 25                     | 27             | I   | ANA               |                                   |

| AN7      | _                                | _                                 | _             | 26                     | 28             | _                                | —                                 | _             | 26                     | 28             | I   | ANA               |                                   |

| AN8      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I   | ANA               |                                   |

| AN9      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ANA               |                                   |

| AN10     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA               |                                   |

| AN11     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | Т   | ANA               |                                   |

| AN12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | Т   | ANA               |                                   |

| AN13     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | Т   | ANA               |                                   |

| AN14     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ANA               |                                   |

| AN15     | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA               |                                   |

| ASCL1    | -                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | l <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | -                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | l <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                                | 25            | 17                     | 18             | 20                               | 28                                | 25            | 17                     | 18             | 1   | ANA               | A/D Supply Pins                   |

| AVss     | 19                               | 27                                | 24            | 16                     | 17             | 19                               | 27                                | 24            | 16                     | 17             | Т   | ANA               |                                   |

| C1INA    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | 1   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | 1   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 1 Input D (-)          |

| C1OUT    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | —                 | Comparator 1 Output               |

| C2INA    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ANA               | Comparator 2 Input A (+)          |

| C2INB    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 2 Input B (-)          |

| C2INC    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | I   | ANA               | Comparator 2 Input C (+)          |

| C2IND    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | I   | ANA               | Comparator 2 Input D (-)          |

| C2OUT    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 16                                | 13            | 43                     | 47             | 0   | —                 | Comparator 2 Output               |

NOTES:

#### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

| IADLE 4      | -10. |        | EGISTE        |               |        |          |        |        |          |        |        |        |        |        |        |        |        |               |

|--------------|------|--------|---------------|---------------|--------|----------|--------|--------|----------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14        | Bit 13        | Bit 12 | Bit 11   | Bit 10 | Bit 9  | Bit 8    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| ADC1BUF0     | 0300 |        |               |               |        |          |        |        | ADC1BUF  | 0      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF1     | 0302 |        | ADC1BUF1 xxxx |               |        |          |        |        |          |        |        |        |        |        |        |        |        |               |

| ADC1BUF2     | 0304 |        |               | ADC1BUF2 xxxx |        |          |        |        |          |        |        |        |        |        |        |        |        |               |

| ADC1BUF3     | 0306 |        |               |               |        |          |        |        | ADC1BUF  | 3      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF4     | 0308 |        |               |               |        |          |        |        | ADC1BUF  | 4      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF5     | 030A |        | ADC1BUF5 xxxx |               |        |          |        |        |          |        |        |        |        |        |        |        |        |               |

| ADC1BUF6     | 030C |        | ADC1BUF6 xxxx |               |        |          |        |        |          |        |        |        |        |        |        |        |        |               |

| ADC1BUF7     | 030E |        |               |               |        |          |        |        | ADC1BUF  | 7      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF8     | 0310 |        |               |               |        |          |        |        | ADC1BUF  | В      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF9     | 0312 |        |               |               |        |          |        |        | ADC1BUF  | 9      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF10    | 0314 |        |               |               |        |          |        |        | ADC1BUF1 | 0      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF11    | 0316 |        |               |               |        |          |        |        | ADC1BUF1 | 1      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF12    | 0318 |        |               |               |        |          |        |        | ADC1BUF1 | 2      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF13    | 031A |        |               |               |        |          |        |        | ADC1BUF1 | 3      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF14    | 031C |        |               |               |        |          |        |        | ADC1BUF1 | 4      |        |        |        |        |        |        |        | xxxx          |

| ADC1BUF15    | 031E |        |               |               |        |          |        |        | ADC1BUF1 | 5      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF16    | 0320 |        |               |               |        |          |        |        | ADC1BUF1 | 6      |        |        |        |        |        |        |        | XXXX          |

| ADC1BUF17    | 0322 |        | -             |               |        |          | _      |        | ADC1BUF1 | 7      |        |        |        |        |        |        |        | XXXX          |

| AD1CON1      | 0340 | ADON   | —             | ADSIDL        | _      | —        | MODE12 | FORM1  | FORM0    | SSRC3  | SSRC2  | SSRC1  | SSRC0  | —      | ASAM   | SAMP   | DONE   | 0000          |

| AD1CON2      | 0342 | PVCFG1 | PVCFG0        | NVCFG0        | OFFCAL | BUFREGEN | CSCNA  | _      |          | BUFS   | SMPI4  | SMPI3  | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000          |

| AD1CON3      | 0344 | ADRC   | EXTSAM        | _             | SAMC4  | SAMC3    | SAMC2  | SAMC1  | SAMC0    | ADCS7  | ADCS6  | ADCS5  | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000          |

| AD1CHS       | 0348 | CH0NB2 | CH0NB1        | CH0NB0        | CH0SB4 | CH0SB3   | CH0SB2 | CH0SB1 | CH0SB0   | CH0NA2 | CH0NA1 | CH0NA0 | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000          |

| AD1CSSH      | 034E | _      | CSSL30        | CSSL29        | CSSL28 | CSSL27   | CSSL26 | _      |          | —      | —      | —      | —      | —      | —      | CSSL17 | CSSL16 | 0000          |

| AD1CSSL      | 0350 | CSSL15 | CSSL14        | CSSL13        | CSSL12 | CSSL11   | CSSL10 | CSSL9  | CSSL8    | CSSL7  | CSSL6  | CSSL5  | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000          |

| AD1CON5      | 0354 | ASEN   | LPEN          | CTMUREQ       | BGREQ  | r        | _      | ASINT1 | ASINT0   |        | _      | —      | —      | WM1    | WM0    | CM1    | CM0    | 0000          |

| AD1CHITH     | 0356 | _      | —             | _             | _      | _        | _      | _      |          | —      | _      | —      | —      | _      | —      | CHH17  | CHH16  | 0000          |

| AD1CHITL     | 0358 | CHH15  | CHH14         | CHH13         | CHH12  | CHH11    | CHH10  | CHH9   | CHH8     | CHH7   | CHH6   | CHH5   | CHH4   | CHH3   | CHH2   | CHH1   | CHH0   | 0000          |

### TABLE 4-16: A/D REGISTER MAP

Legend: — = unimplemented, read as '0'; r = reserved. Reset values are shown in hexadecimal.

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0      | U-0 | U-0         | U-0             | U-0 | U-0 | U-0 | U-0       |

|----------|-----|-------------|-----------------|-----|-----|-----|-----------|

| _        | —   | —           | —               | —   | —   | _   | —         |

| bit 15   |     |             | •               |     | •   |     | bit 8     |

|          |     |             |                 |     |     |     |           |

| U-0      | U-0 | U-0         | U-0             | U-0 | U-0 | U-0 | R/W-0, HS |

| _        | _   | —           | —               | —   | —   | -   | ULPWUIF   |

| bit 7    |     |             |                 |     |     |     | bit 0     |

|          |     |             |                 |     |     |     |           |

| l edenq. |     | HS = Hardwa | re Settable bit |     |     |     |           |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0           | U-0    | U-0              | U-0 | U-0               | U-0                               | U-0      | U-0     |  |  |

|---------------|--------|------------------|-----|-------------------|-----------------------------------|----------|---------|--|--|

| _             | —      | —                | _   | —                 |                                   | _        | —       |  |  |

| bit 15        |        |                  |     |                   |                                   |          | bit 8   |  |  |

|               |        |                  |     |                   |                                   |          |         |  |  |

| U-0           | U-0    | U-0              | U-0 | U-0               | U-0                               | U-0      | R/W-0   |  |  |

| —             | —      | —                | —   | —                 | —                                 | —        | ULPWUIE |  |  |

| bit 7         |        |                  |     |                   |                                   |          | bit 0   |  |  |

|               |        |                  |     |                   |                                   |          |         |  |  |

| Legend:       |        |                  |     |                   |                                   |          |         |  |  |

| R = Readabl   | le bit | W = Writable I   | oit | U = Unimplen      | nented bit, read                  | l as '0' |         |  |  |

| -n = Value at | POR    | '1' = Bit is set |     | '0' = Bit is clea | Bit is cleared x = Bit is unknown |          |         |  |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-29: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0                           | R/W-1                                                       | R/W-0                                                                                          | R/W-0                                                           | U-0               | R/W-1                              | R/W-0           | R/W-0   |  |  |  |  |  |  |  |  |  |  |

|-------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------|------------------------------------|-----------------|---------|--|--|--|--|--|--|--|--|--|--|

|                               | CRCIP2                                                      | CRCIP1                                                                                         | CRCIP0                                                          | _                 | U2ERIP2                            | U2ERIP1         | U2ERIP0 |  |  |  |  |  |  |  |  |  |  |

| pit 15                        |                                                             |                                                                                                | •                                                               |                   | •                                  | •               | bit     |  |  |  |  |  |  |  |  |  |  |

| U-0                           | R/W-1                                                       | R/W-0                                                                                          | R/W-0                                                           | U-0               | U-0                                | U-0             | U-0     |  |  |  |  |  |  |  |  |  |  |

| 0-0                           | U1ERIP2                                                     | U1ERIP1                                                                                        | U1ERIP0                                                         | 0-0               | 0-0                                | 0-0             | 0-0     |  |  |  |  |  |  |  |  |  |  |

| bit 7                         | UTERIFZ                                                     | UTERIFT                                                                                        | UTERIFU                                                         |                   |                                    |                 | bit     |  |  |  |  |  |  |  |  |  |  |

|                               |                                                             |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| _egend:                       | le hit                                                      | \\/ - \\/:itable                                                                               | <b>L</b> :4                                                     |                   | antad bit waar                     |                 |         |  |  |  |  |  |  |  |  |  |  |

| R = Readab                    |                                                             | W = Writable                                                                                   |                                                                 | •                 | nented bit, read                   |                 |         |  |  |  |  |  |  |  |  |  |  |

| n = Value a                   | IT POR                                                      | '1' = Bit is set                                                                               |                                                                 | '0' = Bit is clea | ared                               | x = Bit is unkr | IOWN    |  |  |  |  |  |  |  |  |  |  |

| oit 15                        | Unimplemen                                                  | ted: Read as '                                                                                 | ר <b>י</b>                                                      |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| oit 14-12                     | •                                                           |                                                                                                | or Error Interru                                                | ot Priority bite  |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| <i>n</i> ( 1 <del>4</del> -12 |                                                             |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | •                                                           | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li>•</li> </ul>      |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | :                                                           |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | •<br>001 = Interrupt is Priority 1                          |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               |                                                             | pt source is dis                                                                               | abled                                                           |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| oit 11                        | Unimplemen                                                  | ted: Read as '                                                                                 | ) <b>'</b>                                                      |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| oit 10-8                      | U2ERIP<2:0>: UART2 Error Interrupt Priority bits            |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 111 = Interru                                               | ot is Priority 7 (                                                                             | highest priority                                                | interrupt)        |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | •                                                           | •                                                                                              |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | •                                                           |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 001 = Interrupt is Priority 1                               |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               |                                                             |                                                                                                |                                                                 |                   | 000 = Interrupt source is disabled |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               |                                                             |                                                                                                | abled                                                           |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| pit 7                         | 000 <b>= Interru</b>                                        |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen                                 | ot source is dis<br>ted: Read as '                                                             |                                                                 | ity bits          |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                  | pt source is dis<br>ted: Read as '<br>: UART1 Error                                            | כ'                                                              | -                 |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                  | pt source is dis<br>ted: Read as '<br>: UART1 Error                                            | o'<br>· Interrupt Priori                                        | -                 |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

| bit 7<br>bit 6-4              | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru | ot source is dis<br>ted: Read as '<br>UART1 Error<br>ot is Priority 7 (                        | o'<br>· Interrupt Priori                                        | -                 |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 (<br>ot is Priority 1 | o'<br>Interrupt Priori<br>highest priority                      | -                 |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru | ot source is dis<br>ted: Read as '<br>UART1 Error<br>ot is Priority 7 (                        | <sub>D</sub> ,<br>Interrupt Priori<br>highest priority<br>abled | -                 |                                    |                 |         |  |  |  |  |  |  |  |  |  |  |

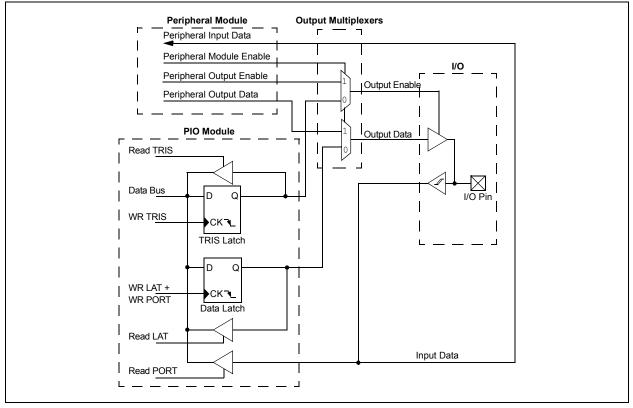

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O Ports, refer to the "PIC24F Family Reference Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24FV32KA304 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LAT), read the latch. Writes to the latch, write the latch. Reads from the port (PORT), read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

## 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 35. "Output Compare with Dedicated Timer" (DS39723).

All devices in the PIC24FV32KA304 family feature 3 independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events. Also, the modules can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 21 user-selectable Sync/trigger sources available

- Two separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

### 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the output compare module operates in a Free-Running mode. The internal 16-bit counter, OCxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected Sync source, the module's internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSELx bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode. Setting this bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the Sync/trigger source.

### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit Timer and Duty Cycle registers. To increase the range, adjacent even and odd numbered modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even numbered module (OCy) provides the Most Significant 16 bits. Wraparounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules.

## EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 16-1: SAMPLE SCKx FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               |      | Secondary Prescaler Settings |      |      |      |      |  |  |  |

|----------------------------|------|------------------------------|------|------|------|------|--|--|--|

|                            |      | 1:1                          | 2:1  | 4:1  | 6:1  | 8:1  |  |  |  |

| Primary Prescaler Settings | 1:1  | Invalid                      | 8000 | 4000 | 2667 | 2000 |  |  |  |

|                            | 4:1  | 4000                         | 2000 | 1000 | 667  | 500  |  |  |  |

|                            | 16:1 | 1000                         | 500  | 250  | 167  | 125  |  |  |  |

|                            | 64:1 | 250                          | 125  | 63   | 42   | 31   |  |  |  |

| Fcy <b>= 5 MHz</b>         |      |                              |      |      |      |      |  |  |  |

| Primary Prescaler Settings | 1:1  | 5000                         | 2500 | 1250 | 833  | 625  |  |  |  |

|                            | 4:1  | 1250                         | 625  | 313  | 208  | 156  |  |  |  |

|                            | 16:1 | 313                          | 156  | 78   | 52   | 39   |  |  |  |

|                            | 64:1 | 78                           | 39   | 20   | 13   | 10   |  |  |  |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: SCKx frequencies are indicated in kHz.

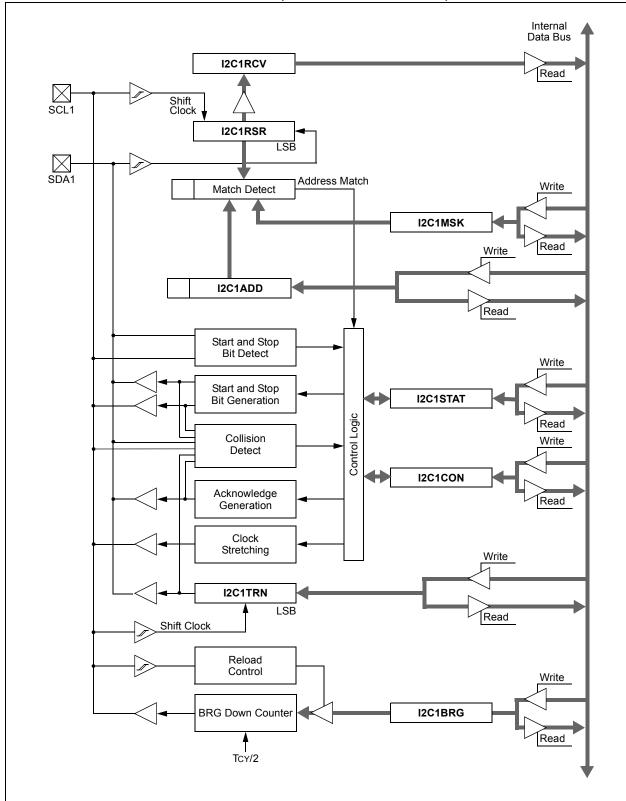

### FIGURE 17-1: I<sup>2</sup>C<sup>™</sup> BLOCK DIAGRAM (I2C1 MODULE IS SHOWN)

| R/W-0                  | R/W-0                                                                                                                                                         | R/W-0                                          | R/W-0          | R/W-0            | R/W-0                        | R/W-0              | R/W-0         |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|------------------|------------------------------|--------------------|---------------|--|--|--|--|--|

| ALRMEN                 | CHIME                                                                                                                                                         | AMASK3                                         | AMASK2         | AMASK1           | AMASK0                       | ALRMPTR1           | ALRMPTRO      |  |  |  |  |  |

| bit 15                 |                                                                                                                                                               |                                                |                |                  |                              |                    | bit 8         |  |  |  |  |  |

| R/W-0                  | R/W-0                                                                                                                                                         | R/W-0                                          | R/W-0          | R/W-0            | R/W-0                        | R/W-0              | R/W-0         |  |  |  |  |  |

| ARPT7                  | ARPT6                                                                                                                                                         | ARPT5                                          | ARPT4          | ARPT3            | ARPT2                        | ARPT1              | ARPT0         |  |  |  |  |  |

| bit 7                  | /                                                                                                                                                             | /                                              | 7              | 7                | /                            | 7.0.0.11           | bit (         |  |  |  |  |  |

|                        |                                                                                                                                                               |                                                |                |                  |                              |                    |               |  |  |  |  |  |

| Legend:<br>R = Readabl | e bit                                                                                                                                                         | W = Writable                                   | bit            | U = Unimplen     | nented bit, rea              | d as '0'           |               |  |  |  |  |  |

| -n = Value at          |                                                                                                                                                               | '1' = Bit is set                               |                | '0' = Bit is cle |                              | x = Bit is unkr    | nown          |  |  |  |  |  |

| bit 15                 |                                                                                                                                                               | larm Enable bit                                |                |                  |                              |                    |               |  |  |  |  |  |

| DIL 15                 |                                                                                                                                                               | enabled (clear                                 | red automatica | lly after an ala | irm event whe                | never ARPT<7       | :0> = 00h and |  |  |  |  |  |

|                        | 0 = Alarm is                                                                                                                                                  | disabled                                       |                |                  |                              |                    |               |  |  |  |  |  |

| bit 14                 | CHIME: Chin                                                                                                                                                   | ne Enable bit                                  |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               | s enabled; ARP <sup>-</sup><br>s disabled; ARP |                |                  |                              | to FFh             |               |  |  |  |  |  |

| bit 13-10              |                                                                                                                                                               | >: Alarm Mask                                  |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               | ry half second                                 | <b>J</b>       |                  |                              |                    |               |  |  |  |  |  |

|                        | 0001 = Eve                                                                                                                                                    |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               | ry 10 seconds                                  |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 0011 = Every minute<br>0100 = Every 10 minutes                                                                                                                |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 0100 = Every for minutes                                                                                                                                      |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 0110 = Onc                                                                                                                                                    | -                                              |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 0111 = Onc                                                                                                                                                    | •                                              |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 1000 = Onc                                                                                                                                                    | e a month                                      |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               | ce a year (excep                               | -              | ired for Februa  | ry 29 <sup>th</sup> , once e | every 4 years)     |               |  |  |  |  |  |

|                        |                                                                                                                                                               | erved – do not                                 |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               | erved – do not                                 |                |                  |                              |                    |               |  |  |  |  |  |

| bit 9-8                | ALRMPTR<1:0>: Alarm Value Register Window Pointer bits<br>Points to the corresponding Alarm Value registers when reading the ALRMVALH and ALRMVALL registers. |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               | R<1:0> value d                                 | ecrements on e | very read or wr  | ITE OF ALRIVIVA              | LH until it reache | es '00'.      |  |  |  |  |  |

|                        | ALRMVAL<1<br>00 = ALRMV                                                                                                                                       |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 01 = ALRMV                                                                                                                                                    |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 10 = ALRMM                                                                                                                                                    |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 11 = Unimple                                                                                                                                                  | emented                                        |                |                  |                              |                    |               |  |  |  |  |  |

|                        | <u>ALRMVAL&lt;7</u>                                                                                                                                           | <u>:0&gt;:</u>                                 |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 00 <b>= ALRMS</b>                                                                                                                                             | -                                              |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 01 = ALRMH                                                                                                                                                    |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 10 = ALRMD<br>11 = Unimple                                                                                                                                    |                                                |                |                  |                              |                    |               |  |  |  |  |  |

| bit 7-0                |                                                                                                                                                               | Alarm Repeat                                   | Counter Value  | hita             |                              |                    |               |  |  |  |  |  |

| DIL 7-0                |                                                                                                                                                               | •                                              |                |                  |                              |                    |               |  |  |  |  |  |

|                        | =                                                                                                                                                             | Alarm will rep                                 | eat 255 more t | intes            |                              |                    |               |  |  |  |  |  |

|                        | •                                                                                                                                                             |                                                |                |                  |                              |                    |               |  |  |  |  |  |

|                        | 00000000 =                                                                                                                                                    | Alarm will not                                 | repeat         |                  |                              |                    |               |  |  |  |  |  |

|                        |                                                                                                                                                               |                                                | any alarm eve  |                  |                              |                    |               |  |  |  |  |  |

## 22.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", Section 51. "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (Internal and External)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU and a configurable results buffer. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 22-1.

### 22.1 A/D Control Registers

The 12-bit A/D Converter module uses up to 43 registers for its operation. All registers are mapped in the data memory space.

#### 22.1.1 CONTROL REGISTERS

Depending on the specific device, the module has up to eleven control and status registers:

- AD1CON1: A/D Control Register 1

- AD1CON2: A/D Control Register 2

- AD1CON3: A/D Control Register 3

- AD1CON5: A/D Control Register 5

- AD1CHS: A/D Sample Select Register

- AD1CHITH and AD1CHITL: A/D Scan Compare Hit Registers

- AD1CSSL and AD1CSSH: A/D Input Scan Select Registers

- AD1CTMUENH and AD1CTMUENL: CTMU Enable Registers

The AD1CON1, AD1CON2 and AD1CON3 registers (Register 22-1, Register 22-2 and Register 22-3) control the overall operation of the A/D module. This includes enabling the module, configuring the conversion clock and voltage reference sources, selecting the sampling and conversion triggers, and manually controlling the sample/convert sequences. The AD1CON5 register (Register 22-4) specifically controls features of the Threshold Detect operation, including its function in power-saving modes.

The AD1CHS register (Register 22-5) selects the input channels to be connected to the S/H amplifier. It also allows the choice of input multiplexers and the selection of a reference source for differential sampling.

The AD1CHITH and AD1CHITL registers (Register 22-6 and Register 22-7) are semaphore registers used with Threshold Detect operations. The status of individual bits, or bit pairs in some cases,

indicate if a match condition has occurred. AD1CHITL is always implemented, whereas AD1CHITH may not be implemented in devices with 16 or fewer channels.

The AD1CSSH/L registers (Register 22-8 and Register 22-9) select the channels to be included for sequential scanning.

The AD1CTMUENH/L registers (Register 22-10 and Register 22-11) select the channel(s) to be used by the CTMU during conversions. Selecting a particular channel allows the A/D Converter to control the CTMU (particularly, its current source) and read its data through that channel. AD1CTMUENL is always implemented, whereas AD1CTMUENH may not be implemented in devices with 16 or fewer channels.

#### 22.1.2 A/D RESULT BUFFERS

The module incorporates a multi-word, dual port RAM, called ADC1BUF. The buffer is composed of at least the same number of word locations as there are external analog channels for a particular device, with a maximum number of 32. The number of buffer addresses is always even. Each of the locations is mapped into the data memory space and is separately addressable. The buffer locations are referred to as ADC1BUF0 through ADC1BUFn (up to 31).

The A/D result buffers are both readable and writable. When the module is active (AD1CON<15> = 1), the buffers are read-only, and store the results of A/D conversions. When the module is inactive (AD1CON<15> = 0), the buffers are both readable and writable. In this state, writing to a buffer location programs a conversion threshold for Threshold Detect operations.

Buffer contents are not cleared when the module is deactivated with the ADON bit (AD1CON1<15>). Conversion results and any programmed threshold values are maintained when ADON is set or cleared.

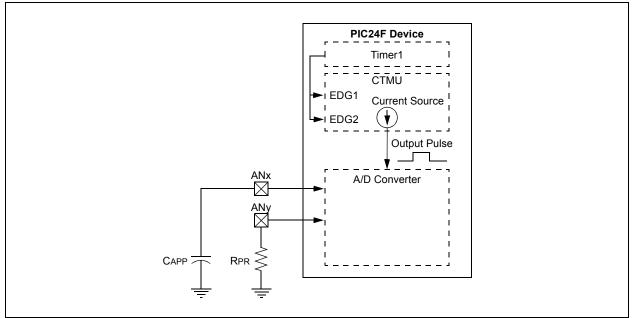

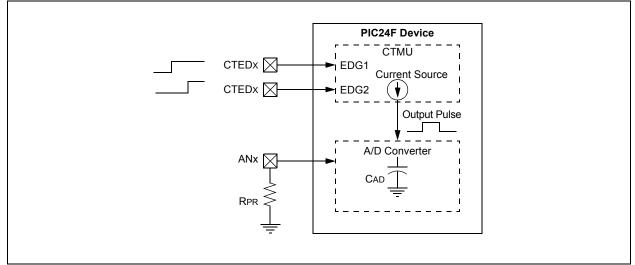

## FIGURE 25-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

### 25.2 Measuring Time

Time measurements on the pulse width can be similarly performed using the A/D module's Internal Capacitor (CAD) and a precision resistor for current calibration. Figure 25-2 displays the external connections used for time measurements, and how the CTMU and A/D modules are related in this application. This example also shows both edge events coming from the external CTEDx pins, but other configurations using internal edge sources are possible.

## FIGURE 25-2: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

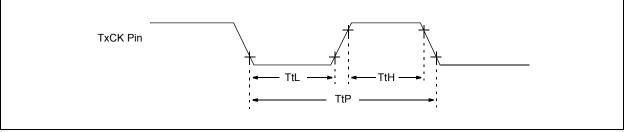

#### FIGURE 29-8: TIMER1/2/3/4/5 EXTERNAL CLOCK INPUT TIMING

#### TABLE 29-27: TIMER1/2/3/4/5 EXTERNAL CLOCK INPUT REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic              |                   | Min                                              | Max | Units | Conditions                      |

|---------------|--------|-----------------------------|-------------------|--------------------------------------------------|-----|-------|---------------------------------|

|               | TtH    | TtH TxCK High Pulse<br>Time | Sync w/Prescaler  | Tcy + 20                                         | _   | ns    | Must also meet<br>Parameter Ttp |

|               |        |                             | Async w/Prescaler | 10                                               | _   | ns    |                                 |

|               |        |                             | Async Counter     | 20                                               | _   | ns    |                                 |

|               | TtL    | TxCK Low Pulse              | Sync w/Prescaler  | Tcy + 20                                         | _   | ns    | Must also meet<br>Parameter Ttp |

|               |        | Time                        | Async w/Prescaler | 10                                               | _   | ns    |                                 |

|               |        |                             | Async Counter     | 20                                               | _   | ns    |                                 |

|               | TtP    | TxCK External Input         | Sync w/Prescaler  | 2 * Tcy + 40                                     | _   | ns    | N = Prescale Value              |

|               |        | Period                      | Async w/Prescaler | Greater of:<br>20 or<br><u>2 * Tcy + 40</u><br>N | —   | ns    | (1, 4, 8, 16)                   |

|               |        |                             | Async Counter     | 40                                               |     | ns    |                                 |

|               |        | Delay for Input Edge        | Synchronous       | 1                                                | 2   | TCY   |                                 |

|               |        | to Timer Increment          | Asynchronous      | —                                                | 20  | ns    |                                 |

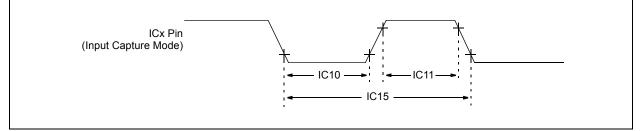

### FIGURE 29-9: INPUT CAPTURE x TIMINGS

#### TABLE 29-28: INPUT CAPTURE x REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                       |                | Min                      | Мах | Units | Conditions                       |

|---------------|--------|--------------------------------------|----------------|--------------------------|-----|-------|----------------------------------|

| IC10          | TccL   | ICx Input Low Time –                 | No Prescaler   | Tcy + 20                 | —   | ns    | Must also meet                   |

|               |        | Synchronous Timer                    | With Prescaler | 20                       | _   | ns    | Parameter IC15                   |

| IC11 TccH     | ТссН   | Cumebraneus Timer                    | No Prescaler   | Tcy + 20                 | —   | ns    | Must also meet<br>Parameter IC15 |

|               |        |                                      | With Prescaler | 20                       | —   | ns    |                                  |

| IC15          | TccP   | ICx Input Period – Synchronous Timer |                | <u>2 * Tcy + 40</u><br>N | —   | ns    | N = prescale value<br>(1, 4, 16) |

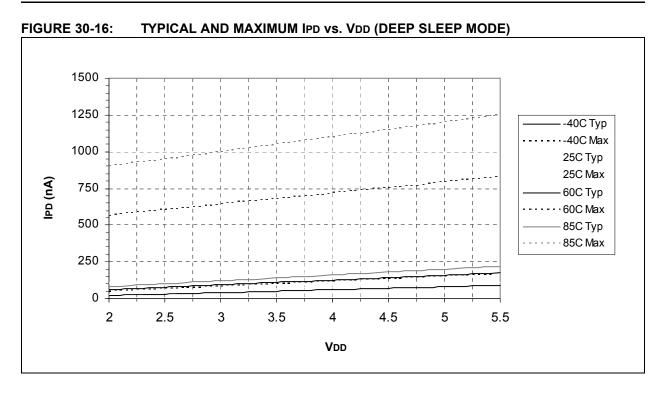

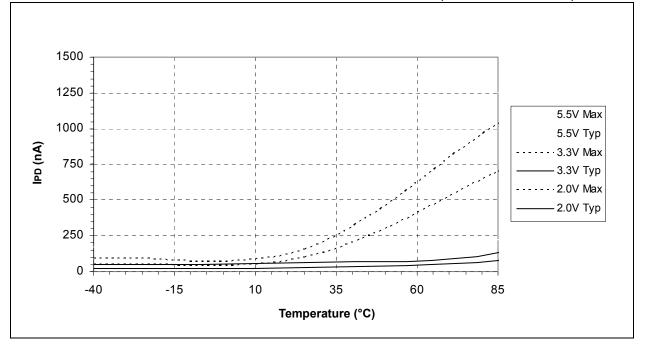

FIGURE 30-17: TYPICAL AND MAXIMUM IPD vs. TEMPERATURE (DEEP SLEEP MODE)

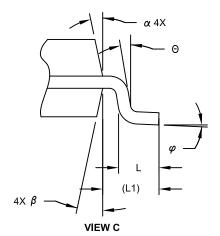

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |  |

|--------------------------|-------------|-----------|-----|------|--|--|

| Dimension Limits         |             | MIN       | NOM | MAX  |  |  |

| Number of Pins           | N           | 20        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |  |

| Overall Length           | D           | 12.80 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |  |

| Foot Length              | L           | 0.40 -    |     | 1.27 |  |  |

| Footprint                | L1 1.40 REF |           |     |      |  |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |  |

| Lead Thickness           | с           | 0.20      | -   | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.