Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka302-i-sp |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  | +1 V J Z I ()4                    | F             |                        |                |                                  |                                   | FV            | -                      |                |     |        |             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|-------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description |

| RA0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I/O | ST     | PORTA Pins  |

| RA1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I/O | ST     |             |

| RA2      | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I/O | ST     |             |

| RA3      | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I/O | ST     |             |

| RA4      | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I/O | ST     |             |

| RA5      | 1                                | 1                                 | 26            | 18                     | 19             | 1                                | 1                                 | 26            | 18                     | 19             | I/O | ST     |             |

| RA6      | 14                               | 20                                | 17            | 7                      | 7              | _                                | _                                 | —             | _                      | _              | I/O | ST     |             |

| RA7      | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I/O | ST     |             |

| RA8      | _                                | _                                 |               | 32                     | 35             | _                                | _                                 | —             | 32                     | 35             | I/O | ST     |             |

| RA9      | _                                | _                                 |               | 35                     | 38             | _                                | _                                 | —             | 35                     | 38             | I/O | ST     |             |

| RA10     | _                                | _                                 |               | 12                     | 13             | _                                | _                                 | —             | 12                     | 13             | I/O | ST     |             |

| RA11     | _                                | _                                 |               | 13                     | 14             | _                                | _                                 | —             | 13                     | 14             | I/O | ST     |             |

| RB0      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I/O | ST     | PORTB Pins  |

| RB1      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I/O | ST     |             |

| RB2      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I/O | ST     |             |

| RB3      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I/O | ST     |             |

| RB4      | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I/O | ST     |             |

| RB5      | _                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | ST     |             |

| RB6      | _                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | ST     |             |

| RB7      | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I/O | ST     |             |

| RB8      | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I/O | ST     |             |

| RB9      | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I/O | ST     |             |

| RB10     | _                                | 21                                | 18            | 8                      | 9              | _                                | 21                                | 18            | 8                      | 9              | I/O | ST     |             |

| RB11     | _                                | 22                                | 19            | 9                      | 10             | _                                | 22                                | 19            | 9                      | 10             | I/O | ST     |             |

| RB12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I/O | ST     |             |

| RB13     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | I/O | ST     |             |

| RB14     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I/O | ST     |             |

| RB15     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I/O | ST     |             |

# EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM INSTRUCTION PER ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234; // Global variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM INSTRUCTION PER ROW]; // Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4001;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr); // Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr); // Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM INSTRUCTION PER ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

# EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; 1 | Block all interrupts                  |

|------|-------------|-----|---------------------------------------|

|      |             | :   | for next 5 instructions               |

| MOV  | #0x55, W0   |     |                                       |

| MOV  | W0, NVMKEY  | ; 1 | Write the 55 key                      |

| MOV  | #0xAA, W1   | ;   |                                       |

| MOV  | W1, NVMKEY  | ; 1 | Write the AA key                      |

| BSET | NVMCON, #WR | ; ; | Start the erase sequence              |

| NOP  |             | ; : | 2 NOPs required after setting WR      |

| NOP  |             | ;   |                                       |

| BTSC | NVMCON, #15 | ; 1 | Wait for the sequence to be completed |

| BRA  | \$-2        | ;   |                                       |

|      |             |     |                                       |

### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| <pre>// C example using MPLAB C30</pre> |                                                 |

|-----------------------------------------|-------------------------------------------------|

| asm("DISI #5");                         | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();                    | // Perform unlock sequence and set WR           |

### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing a bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- 2. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin the erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3.

### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in the previous section) if the PGMONLY bit (NVMCON<12>) is set to '1'.

- 2. Write the data word into the data EEPROM latch.

- 3. Program the data word into the EEPROM:

- Configure the NVMCON register to program one EEPROM word (NVMCON<5:0> = 0001xx).

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin the erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4.

# EXAMPLE 6-3: DATA EEPROM BULK ERASE

// Set up NVMCON to bulk erase the data EEPROM NVMCON =  $0 \times 4050;$

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

```

// Issue Unlock Sequence and Start Erase Cycle

__builtin_write_NVM();

```

# EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

```

int attribute ((space(eedata))) eeData = 0x1234;

// New data to write to EEPROM

int newData;

/*_____

_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the write

-------

*/

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4004;

\ensuremath{//} Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData);

// Initialize EE Data page pointer

// Initizlize lower word of address

offset = __builtin_tbloffset(&eeData);

builtin tblwtl(offset, newData);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

builtin write NVM();

// Issue Unlock Sequence & Start Write Cycle

while (NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

| REGISTER      | 8-4: INTC       | ON2: INTERR                             | UPT CONTE                  | ROL REGIST       | ER2              |                 |        |

|---------------|-----------------|-----------------------------------------|----------------------------|------------------|------------------|-----------------|--------|

| R/W-0         | R-0, HSC        | U-0                                     | U-0                        | U-0              | U-0              | U-0             | U-0    |

| ALTIVT        | DISI            | —                                       | _                          | _                | —                | —               | —      |

| bit 15        |                 |                                         |                            |                  |                  |                 | bit 8  |

|               |                 |                                         |                            |                  |                  |                 |        |

| U-0           | U-0             | U-0                                     | U-0                        | U-0              | R/W-0            | R/W-0           | R/W-0  |

| —             |                 | —                                       |                            | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7         |                 |                                         |                            |                  |                  |                 | bit 0  |

|               |                 |                                         |                            |                  |                  |                 |        |

| Legend:       |                 | HSC = Hardwa                            | are Settable/C             |                  |                  |                 |        |

| R = Readabl   | le bit          | W = Writable b                          | oit                        | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | t POR           | '1' = Bit is set                        |                            | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|               |                 |                                         |                            |                  |                  |                 |        |

| bit 15        | ALTIVT: Enat    | ole Alternate Inte                      | errupt Vector <sup>-</sup> | lable bit        |                  |                 |        |

|               |                 | rnate Interrupt \<br>ndard (default) Ir | · ·                        | ,                |                  |                 |        |

| bit 14        | DISI: DISI In   | struction Status                        | bit                        |                  |                  |                 |        |

|               |                 | ruction is active                       |                            |                  |                  |                 |        |

|               | 0 = DISI inst   | ruction is not ac                       | tive                       |                  |                  |                 |        |

| bit 13-3      | Unimplemen      | ted: Read as '0                         | 3                          |                  |                  |                 |        |

| bit 2         | INT2EP: Exte    | ernal Interrupt 2                       | Edge Detect F              | Polarity Select  | bit              |                 |        |

|               |                 | s on the negatives on the positive      | 0                          |                  |                  |                 |        |

| bit 1         | INT1EP: Exte    | ernal Interrupt 1                       | Edge Detect F              | Polarity Select  | bit              |                 |        |

|               | 1 = Interrupt i | s on the negativ                        | e edge                     |                  |                  |                 |        |

|               | 0 = Interrupt i | s on the positive                       | e edge                     |                  |                  |                 |        |

| bit 0         | INTOEP: Exte    | ernal Interrupt 0                       | Edge Detect F              | Polarity Select  | bit              |                 |        |

|               |                 | s on the negativ                        |                            |                  |                  |                 |        |

|               | 0 = Interrupt i | s on the positive                       | e edge                     |                  |                  |                 |        |

# REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

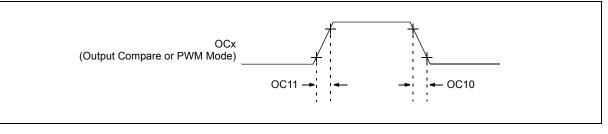

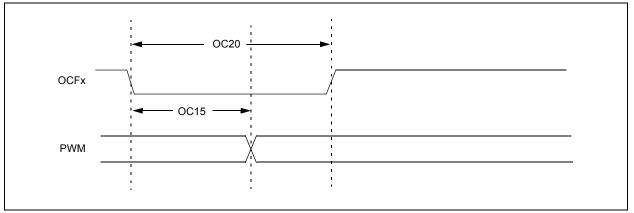

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This output compare module<sup>(1)</sup>

- 11110 = **Reserved** 11101 = Reserved 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 100xx = Reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1

- 01010 = Input Capture 5<sup>(2)</sup>

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Output Compare 5<sup>(1)</sup>

- 00100 = Output Compare 4<sup>(1)</sup>

- 00011 = Output Compare 3<sup>(1)</sup>

- 00010 = Output Compare 2<sup>(1)</sup>

- 00001 = Output Compare 1<sup>(1)</sup>

- 00000 = Not synchronized to any other module

- Note 1: Do not use an output compare module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as trigger sources only and never as Sync sources.

- 3: These bits affect the rising edge when OCINV = 1. The bits have no effect when the OCMx bits (OCxCON1<2:0>) = 001.

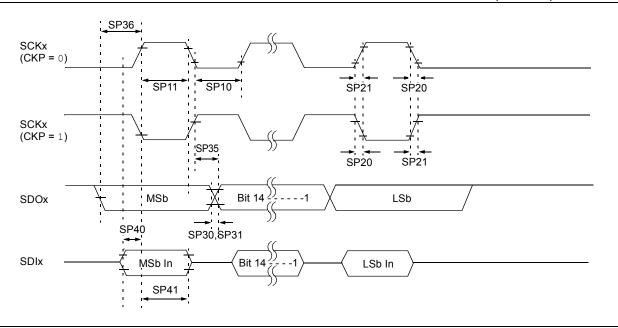

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

#### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R/W-0                                  | R/W-0                                                                                                                                                                                                                            | R/W-0                                                                                         | U-0                                                                                                    | U-0                                 | U-0             | U-0             | U-0    |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-----------------|--------|--|--|

| FRMEN                                  | SPIFSD                                                                                                                                                                                                                           | SPIFPOL                                                                                       | _                                                                                                      | _                                   | _               | _               | _      |  |  |

| bit 15                                 |                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        | ·                                   |                 | -               | bit 8  |  |  |

|                                        |                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        |                                     |                 |                 |        |  |  |

| U-0                                    | U-0                                                                                                                                                                                                                              | U-0                                                                                           | U-0                                                                                                    | U-0                                 | U-0             | R/W-0           | R/W-0  |  |  |

|                                        | —                                                                                                                                                                                                                                | —                                                                                             | —                                                                                                      | —                                   | —               | SPIFE           | SPIBEN |  |  |

| bit 7                                  |                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        |                                     |                 |                 | bit 0  |  |  |

|                                        |                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        |                                     |                 |                 |        |  |  |

| Legend:                                |                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        |                                     |                 |                 |        |  |  |

| R = Readable                           | e bit                                                                                                                                                                                                                            | W = Writable I                                                                                | oit                                                                                                    | U = Unimplem                        | nented bit, rea | d as '0'        |        |  |  |

| -n = Value at                          | POR                                                                                                                                                                                                                              | '1' = Bit is set                                                                              |                                                                                                        | '0' = Bit is clea                   | ared            | x = Bit is unkr | iown   |  |  |

| bit 15<br>bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: SPI2<br>1 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy                                                                                                     | nc pulse input (<br>nc pulse output<br>Plx Frame Sync<br>nc pulse is acti<br>nc pulse is acti | enabled<br>disabled<br>Pulse Direction<br>(slave)<br>t (master)<br>Pulse Polarity<br>ve-high<br>ve-low | n Control on SS:<br>/ bit (Frame mo |                 |                 |        |  |  |

| bit 1                                  | <ul> <li>Unimplemented: Read as '0'</li> <li>SPIFE: SPIx Frame Sync Pulse Edge Select bit</li> <li>1 = Frame Sync pulse coincides with the first bit clock</li> <li>0 = Frame Sync pulse precedes the first bit clock</li> </ul> |                                                                                               |                                                                                                        |                                     |                 |                 |        |  |  |

| bit 0                                  | 1 = Enhanced                                                                                                                                                                                                                     | x Enhanced Bu<br>I buffer is enabl<br>I buffer is disab                                       | ed                                                                                                     |                                     |                 |                 |        |  |  |

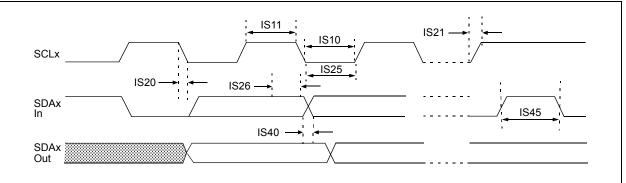

# REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master; applicable during master receive)                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                     |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master; applicable during master receive)                                                                                                                      |

|       | <ul> <li>1 = Initiates the Acknowledge sequence on the SDAx and SCLx pins, and transmits the ACKDT data bit;<br/>hardware is clear at the end of the master Acknowledge sequence</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                      |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C; hardware is clear at the end of the eighth bit of the master receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                 |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                          |

| ~     | 1 = Initiates Stop condition on SDAx and SCLx pins; hardware is clear at end of master Stop sequence<br>0 = Stop condition is not in progress                                                                                                    |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                     |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins; hardware is clear at the end of the master Repeated Start sequence                                                                                                                 |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                                  |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                      |

|       | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins; hardware is clear at the end of the<br/>master Start sequence</li> </ul>                                                                                                           |

|       | $\circ = 0$ text condition is not in pressure.                                                                                                                                                                                                   |

0 = Start condition is not in progress

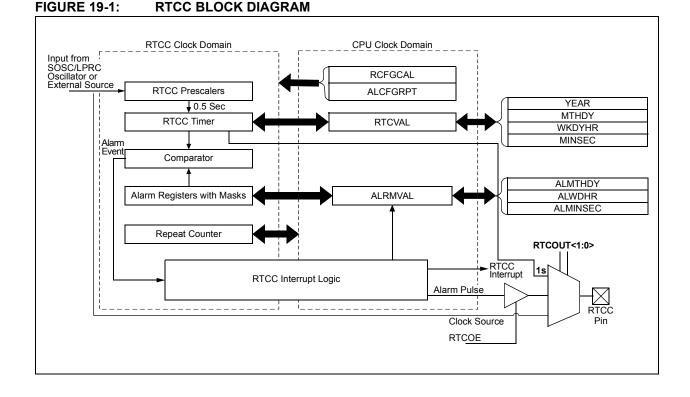

# 19.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", Section 29. "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- Operates in Deep Sleep mode

- Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- · Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long-term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long-term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

# 19.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

# © 2011-2013 Microchip Technology Inc.

| R/W-0         | R/W-0                      | R/W-0                                      | R/W-0                                                                                                                                        | R/W-0            | R/W-0                         | R/W-0              | R/W-0         |

|---------------|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|--------------------|---------------|

| ALRMEN        | CHIME                      | AMASK3                                     | AMASK2                                                                                                                                       | AMASK1           | AMASK0                        | ALRMPTR1           | ALRMPTRO      |

| bit 15        |                            | •                                          |                                                                                                                                              |                  |                               | •                  | bit 8         |

| R/W-0         | R/W-0                      | R/W-0                                      | R/W-0                                                                                                                                        | R/W-0            | R/W-0                         | R/W-0              | R/W-0         |

| ARPT7         | ARPT6                      | ARPT5                                      | ARPT4                                                                                                                                        | ARPT3            | ARPT2                         | ARPT1              | ARPT0         |

| bit 7         |                            |                                            |                                                                                                                                              |                  |                               |                    | bit (         |

| Legend:       |                            |                                            |                                                                                                                                              |                  |                               |                    |               |

| R = Readabl   | e bit                      | W = Writable                               | bit                                                                                                                                          | U = Unimplen     | nented bit, rea               | d as '0'           |               |

| -n = Value at |                            | '1' = Bit is set                           |                                                                                                                                              | '0' = Bit is cle |                               | x = Bit is unkr    | nown          |

| bit 15        | ALRMEN: AI                 | arm Enable bit                             |                                                                                                                                              |                  |                               |                    |               |

|               | CHIME =                    | = 0)                                       | ed automatica                                                                                                                                | lly after an ala | arm event whe                 | enever ARPT<7      | :0> = 00h and |

|               | 0 = Alarm is               | disabled                                   |                                                                                                                                              |                  |                               |                    |               |

| bit 14        | CHIME: Chin                |                                            |                                                                                                                                              |                  |                               |                    |               |

|               |                            | enabled; ARP <sup>-</sup><br>disabled; ARP |                                                                                                                                              |                  |                               | to FFh             |               |

| bit 13-10     |                            | >: Alarm Mask                              |                                                                                                                                              |                  |                               |                    |               |

|               |                            | ry half second                             | <u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u></u> |                  |                               |                    |               |

|               | 0001 = Eve                 | •                                          |                                                                                                                                              |                  |                               |                    |               |

|               |                            | ry 10 seconds                              |                                                                                                                                              |                  |                               |                    |               |

|               | 0011 = Eve                 |                                            |                                                                                                                                              |                  |                               |                    |               |

|               |                            | ry 10 minutes                              |                                                                                                                                              |                  |                               |                    |               |

|               | 0101 = Eve<br>0110 = Onc   | •                                          |                                                                                                                                              |                  |                               |                    |               |

|               | 0111 = Onc                 | •                                          |                                                                                                                                              |                  |                               |                    |               |

|               | 1000 = Onc                 | e a month                                  |                                                                                                                                              |                  |                               |                    |               |

|               | 1001 = Onc                 | e a year (excep                            | ot when configu                                                                                                                              | ired for Februa  | ıry 29 <sup>th</sup> , once e | every 4 years)     |               |

|               |                            | erved – do not                             |                                                                                                                                              |                  |                               |                    |               |

|               |                            | erved – do not                             |                                                                                                                                              |                  |                               |                    |               |

| bit 9-8       |                            | 1:0>: Alarm Val                            | -                                                                                                                                            |                  |                               |                    |               |

|               |                            |                                            |                                                                                                                                              |                  |                               | ALH and ALRM       |               |

|               |                            |                                            | ecrements on e                                                                                                                               | very read or wr  | ITE OF ALRIVIA                | LH until it reache | es '00'.      |

|               | ALRMVAL<1                  |                                            |                                                                                                                                              |                  |                               |                    |               |

|               | 00 - ALRIVIV<br>01 - ALRMW |                                            |                                                                                                                                              |                  |                               |                    |               |

|               | 10 <b>= ALRMM</b>          |                                            |                                                                                                                                              |                  |                               |                    |               |

|               | 11 = Unimple               | emented                                    |                                                                                                                                              |                  |                               |                    |               |

|               | ALRMVAL<7                  | :0>:                                       |                                                                                                                                              |                  |                               |                    |               |

|               | 00 <b>= ALRMS</b>          | EC                                         |                                                                                                                                              |                  |                               |                    |               |

|               | 01 = ALRMH                 |                                            |                                                                                                                                              |                  |                               |                    |               |

|               | 10 = ALRMD                 |                                            |                                                                                                                                              |                  |                               |                    |               |

|               | 11 = Unimple               |                                            |                                                                                                                                              |                  |                               |                    |               |

| bit 7-0       |                            | Alarm Repeat                               |                                                                                                                                              |                  |                               |                    |               |

|               | 11111111 =                 | Alarm will rep                             | eat 255 more ti                                                                                                                              | imes             |                               |                    |               |

|               | •<br>•                     |                                            |                                                                                                                                              |                  |                               |                    |               |

|               |                            |                                            |                                                                                                                                              |                  |                               |                    |               |

|               | 000000000                  | Alarm will not                             | repeat                                                                                                                                       |                  |                               |                    |               |

# REGISTER 19-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

#### 19.2.5 RTCVAL REGISTER MAPPINGS

# REGISTER 19-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | —      | —      | —      | —      | —      | —      |

| bit 15 |        |        | •      | •      |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-x  |

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

# Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

### REGISTER 19-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12    | <b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'. |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits                                   |

|           | Contains a value from 0 to 9.                                                                        |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits                                     |

|           | Contains a value from 0 to 3.                                                                        |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits                                     |

|           | Contains a value from 0 to 9.                                                                        |

|           |                                                                                                      |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

| U-0              | R/W-x         | R/W-x            | R/W-x          | R/W-x                | R/W-x            | R/W-x              | R/W-x   |

|------------------|---------------|------------------|----------------|----------------------|------------------|--------------------|---------|

|                  | MINTEN2       | MINTEN1          | MINTEN0        | MINONE3              | MINONE2          | MINONE1            | MINONE0 |

| bit 15           |               |                  |                |                      |                  |                    | bit 8   |

|                  |               |                  |                |                      |                  |                    |         |

| U-0              | R/W-x         | R/W-x            | R/W-x          | R/W-x                | R/W-x            | R/W-x              | R/W-x   |

| —                | SECTEN2       | SECTEN1          | SECTEN0        | SECONE3              | SECONE2          | SECONE1            | SECONE0 |

| bit 7            |               |                  |                |                      |                  |                    | bit 0   |

|                  |               |                  |                |                      |                  |                    |         |

| Legend:          |               |                  |                |                      |                  |                    |         |

| R = Readable bit |               | W = Writable bit |                | U = Unimplem         | nented bit, read | l as '0'           |         |

| -n = Value a     | t POR         | '1' = Bit is set |                | '0' = Bit is cleared |                  | x = Bit is unknown |         |

|                  |               |                  |                |                      |                  |                    |         |

| bit 15           | Unimplement   | ted: Read as '0  | ,              |                      |                  |                    |         |

| bit 14-12        | MINTEN<2:0    | >: Binary Code   | d Decimal Valu | ue of Minute's T     | ens Digit bits   |                    |         |

|                  | Contains a va | lue from 0 to 5  |                |                      |                  |                    |         |

| bit 11-8         | MINONE<3:0    | >: Binary Code   | d Decimal Val  | ue of Minute's 0     | Ones Digit bits  |                    |         |

|                  | Contains a va | lue from 0 to 9  |                |                      |                  |                    |         |

| bit 7            | Unimplemen    | ted: Read as '   | o'             |                      |                  |                    |         |

| bit 6-4          | SECTEN<2:0    | >: Binary Code   | ed Decimal Val | ue of Second's       | Tens Digit bits  |                    |         |

|                  | Contains a va | lue from 0 to 5  |                |                      |                  |                    |         |

| bit 3-0          | SECONE<3:0    | >: Binary Code   | ed Decimal Va  | lue of Second's      | Ones Digit bits  | 6                  |         |

|                  | Contains a va | lue from 0 to 9  |                |                      |                  |                    |         |

|                  |               |                  |                |                      |                  |                    |         |

# REGISTER 19-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

# REGISTER 19-11: RTCCSWT: CONTROL/SAMPLE WINDOW TIMER REGISTER<sup>(1)</sup>

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSAMP7 | PWCSAMP6 | PWCSAMP5 | PWCSAMP4 | PWCSAMP3 | PWCSAMP2 | PWCSAMP1 | PWCSAMP0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | PWCSTAB<7:0>: PWM Stability Window Timer bits<br>11111111 = Stability window is 255 TPWCCLK clock periods                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 00000000 = Stability window is 0 TPWCCLK clock periods<br>The sample window starts when the alarm event triggers. The stability window timer starts counting<br>from every alarm event when PWCEN = 1.                               |

| bit 7-0  | <pre>PWCSAMP&lt;7:0&gt;: PWM Sample Window Timer bits 1111111 = Sample window is always enabled, even when PWCEN = 0 11111110 = Sample window is 254 TPWCCLK clock periods 00000000 = Sample window is 0 TPWCCLK clock periods</pre> |

|          | The sample window timer starts counting at the end of the stability window when PWCEN = 1. If PWCSTAB<7:0> = $00000000$ , the sample window timer starts counting from every alarm event when PWCEN = 1.                             |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

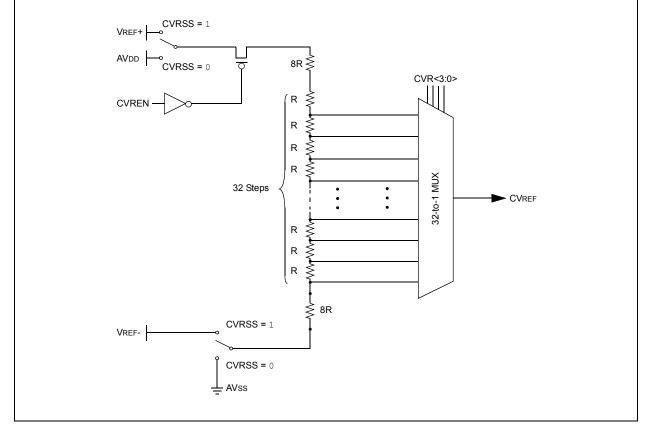

# 24.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator Voltage Reference, refer to the "PIC24F Family Reference Manual", Section 20. "Comparator Module Voltage Reference Module" (DS39709).

# 24.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 24-1). The comparator voltage reference provides a range of output voltages, with 32 distinct levels.

The comparator voltage reference supply voltage can come from either VDD and VSS or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

#### CTMUCONO, CTMU CONTROL DECISTER 2

| REGISTER 2    |                                                                                                                                          | JCON2: CTM                          |                                  |                   |                   |                 |          |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|-------------------|-------------------|-----------------|----------|--|--|--|

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                               | R/W-0                            | R/W-0             | R/W-0             | R/W-0           | R/W-0    |  |  |  |

| EDG1MOD       | EDG1POL                                                                                                                                  | EDG1SEL3                            | EDG1SEL2                         | EDG1SEL1          | EDG1SEL0          | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        |                                                                                                                                          |                                     |                                  |                   |                   |                 | bit      |  |  |  |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                               | R/W-0                            | R/W-0             | R/W-0             | U-0             | U-0      |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                                                  | EDG2SEL3                            | 1                                |                   |                   | 0-0             | 0-0      |  |  |  |

|               | EDG2POL                                                                                                                                  | EDG25EL3                            | EL3 EDG2SEL2 EDG2SEL1 EDG2SEL0 — |                   |                   |                 |          |  |  |  |

| bit 7         |                                                                                                                                          |                                     |                                  |                   |                   |                 | bit      |  |  |  |

| Legend:       |                                                                                                                                          |                                     |                                  |                   |                   |                 |          |  |  |  |

| R = Readable  | e bit                                                                                                                                    | W = Writable                        | bit                              | U = Unimplem      | nented bit, read  | l as '0'        |          |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set                    |                                  | '0' = Bit is clea | ared              | x = Bit is unkr | nown     |  |  |  |

| bit 15        |                                                                                                                                          | Edge 1 Edge-So                      | ansitiva Salact                  | bit               |                   |                 |          |  |  |  |

| bit 15        | 1 = Input is ed                                                                                                                          |                                     |                                  | bit               |                   |                 |          |  |  |  |

|               | 0 = Input is le                                                                                                                          | vel-sensitive                       |                                  |                   |                   |                 |          |  |  |  |

| bit 14        |                                                                                                                                          | EDG1POL: Edge 1 Polarity Select bit |                                  |                   |                   |                 |          |  |  |  |

|               | <ul> <li>1 = Edge 1 is programmed for a positive edge response</li> <li>0 = Edge 1 is programmed for a negative edge response</li> </ul> |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | •                                                                                                                                        |                                     | •                                | •                 |                   |                 |          |  |  |  |

| bit 13-10     | EDG1SEL<3:0>: Edge 1 Source Select bits                                                                                                  |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1111 = Edge 1 source is Comparator 3 output                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1110 = Edge 1 source is Comparator 2 output                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1101 = Edge 1 source is Comparator 1 output                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1100 = Edge 1 source is IC3                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1011 = Edge 1 source is IC2                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1010 = Edge 1 source is IC1                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 1001 = Edge 1 source is CTED8<br>1000 = Edge 1 source is CTED7                                                                           |                                     |                                  |                   |                   |                 |          |  |  |  |

|               |                                                                                                                                          |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0111 = Edge 1 source is CTED6<br>0110 = Edge 1 source is CTED5                                                                           |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0110 = Edge 1 source is CTED5                                                                                                            |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0100 = Edge 1 source is CTED3 <sup>(2)</sup>                                                                                             |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0011 = Edge 1 source is CTED1                                                                                                            |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0010 = Edge 1 source is CTED2                                                                                                            |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0001 = Edge 1 source is OC1                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0000 <b>= Edge</b>                                                                                                                       | 1 source is Tin                     | ner1                             |                   |                   |                 |          |  |  |  |

| bit 9         | EDG2STAT: Edge 2 Status bit                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | Indicates the                                                                                                                            | status of Edge                      | 2 and can be w                   | ritten to contro  | of the current so | ource.          |          |  |  |  |

|               | 1 = Edge 2 has occurred                                                                                                                  |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | 0 = Edge 2 has not occurred                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

| bit 8         | EDG1STAT: Edge 1 Status bit                                                                                                              |                                     |                                  |                   |                   |                 |          |  |  |  |

|               | Indicates the                                                                                                                            | status of Edge                      | 1 and can be w                   | ritten to contro  | ol the current so | ource.          |          |  |  |  |

|               | 1 = Edge 1 ha                                                                                                                            | as occurred                         |                                  |                   |                   |                 |          |  |  |  |

|               | 0 = Edge 1 ha                                                                                                                            | as not occurred                     |                                  |                   |                   |                 |          |  |  |  |

|               |                                                                                                                                          |                                     |                                  |                   |                   |                 |          |  |  |  |

| bit 7         | EDG2MOD: E                                                                                                                               | Edge 2 Edge-Se                      | ensitive Select                  | bit               |                   |                 |          |  |  |  |