#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

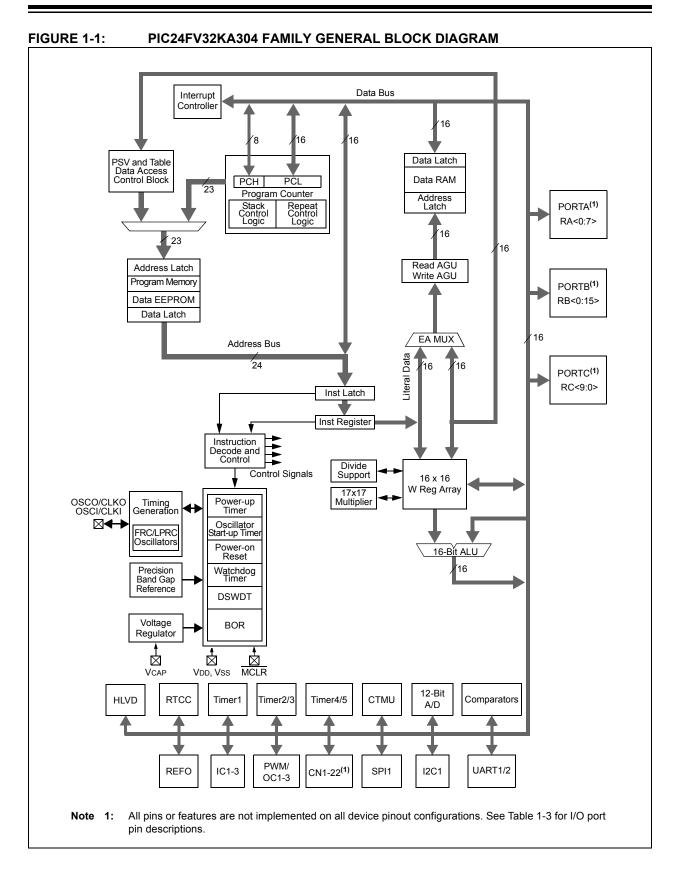

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka302-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                | 1   |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 1/0 | Buffer            | Description                       |

| AN0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | Т   | ANA               |                                   |

| AN2      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               |                                   |

| AN3      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               |                                   |

| AN4      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ANA               |                                   |

| AN5      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I   | ANA               |                                   |

| AN6      | _                                | _                                 | _             | 25                     | 27             | _                                | _                                 | _             | 25                     | 27             | I   | ANA               |                                   |

| AN7      | _                                | _                                 | _             | 26                     | 28             | _                                | —                                 | _             | 26                     | 28             | I   | ANA               |                                   |

| AN8      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I   | ANA               |                                   |

| AN9      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ANA               |                                   |

| AN10     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA               |                                   |

| AN11     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | Т   | ANA               |                                   |

| AN12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | Т   | ANA               |                                   |

| AN13     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | Т   | ANA               |                                   |

| AN14     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ANA               |                                   |

| AN15     | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA               |                                   |

| ASCL1    | -                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | l <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | -                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | l <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                                | 25            | 17                     | 18             | 20                               | 28                                | 25            | 17                     | 18             | 1   | ANA               | A/D Supply Pins                   |

| AVss     | 19                               | 27                                | 24            | 16                     | 17             | 19                               | 27                                | 24            | 16                     | 17             | Т   | ANA               |                                   |

| C1INA    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | 1   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | 1   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | Т   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 1 Input D (-)          |

| C1OUT    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | —                 | Comparator 1 Output               |

| C2INA    | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ANA               | Comparator 2 Input A (+)          |

| C2INB    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA               | Comparator 2 Input B (-)          |

| C2INC    | 8                                | 7                                 | 4             | 24                     | 26             | 8                                | 7                                 | 4             | 24                     | 26             | I   | ANA               | Comparator 2 Input C (+)          |

| C2IND    | 7                                | 6                                 | 3             | 23                     | 25             | 7                                | 6                                 | 3             | 23                     | 25             | I   | ANA               | Comparator 2 Input D (-)          |

| C2OUT    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 16                                | 13            | 43                     | 47             | 0   | —                 | Comparator 2 Output               |

#### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                            |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    | •                      |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| C3INA    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | Ι   | ANA    | Comparator 3 Input A (+)   |

| C3INB    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator 3 Input B (-)   |

| C3INC    | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | 1   | ANA    | Comparator 3 Input C (+)   |

| C3IND    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | 1   | ANA    | Comparator 3 Input D (-)   |

| C3OUT    | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | 0   | —      | Comparator 3 Output        |

| CLK I    | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ANA    | Main Clock Input           |

| CLKO     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | 0   | _      | System Clock Output        |

| CN0      | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I   | ST     | Interrupt-on-Change Inputs |

| CN1      | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ST     |                            |

| CN2      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ST     |                            |

| CN3      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ST     |                            |

| CN4      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ST     |                            |

| CN5      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     |                            |

| CN6      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ST     |                            |

| CN7      | _                                | 7                                 | 4             | 24                     | 26             |                                  | 7                                 | 4             | 24                     | 26             | I   | ST     |                            |

| CN8      | 14                               | 20                                | 17            | 7                      | 7              |                                  |                                   |               | _                      |                | I   | ST     |                            |

| CN9      |                                  | 19                                | 16            | 6                      | 6              |                                  | 19                                | 16            | 6                      | 6              | I   | ST     |                            |

| CN10     |                                  | —                                 | —             | 27                     | 29             |                                  |                                   |               | 27                     | 29             | I   | ST     |                            |

| CN11     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 1   | ST     |                            |

| CN12     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 1   | ST     |                            |

| CN13     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | 1   | ST     |                            |

| CN14     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | 1   | ST     |                            |

| CN15     |                                  | 22                                | 19            | 9                      | 10             |                                  | 22                                | 19            | 9                      | 10             | Ι   | ST     | ]                          |

| CN16     |                                  | 21                                | 18            | 8                      | 9              |                                  | 21                                | 18            | 8                      | 9              | Ι   | ST     |                            |

| CN17     |                                  | —                                 | —             | 3                      | 3              |                                  | —                                 | _             | 3                      | 3              | 1   | ST     |                            |

| CN18     | _                                | _                                 | _             | 2                      | 2              | —                                | _                                 | _             | 2                      | 2              | Ι   | ST     | ]                          |

| CN19     |                                  | _                                 | _             | 5                      | 5              | —                                | _                                 |               | 5                      | 5              | 1   | ST     | ]                          |

| CN20     |                                  | _                                 | —             | 4                      | 4              | _                                |                                   |               | 4                      | 4              | I   | ST     |                            |

| CN21     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I   | ST     | ]                          |

| CN22     | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | 1   | ST     |                            |

NOTES:

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM INSTRUCTION PER ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234; // Global variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM INSTRUCTION PER ROW]; // Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4001;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr); // Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr); // Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM INSTRUCTION PER ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; 1 | Block all interrupts                  |

|------|-------------|-----|---------------------------------------|

|      |             | :   | for next 5 instructions               |

| MOV  | #0x55, W0   |     |                                       |

| MOV  | W0, NVMKEY  | ; 1 | Write the 55 key                      |

| MOV  | #0xAA, W1   | ;   |                                       |

| MOV  | W1, NVMKEY  | ; 1 | Write the AA key                      |

| BSET | NVMCON, #WR | ; ; | Start the erase sequence              |

| NOP  |             | ; : | 2 NOPs required after setting WR      |

| NOP  |             | ;   |                                       |

| BTSC | NVMCON, #15 | ; 1 | Wait for the sequence to be completed |

| BRA  | \$-2        | ;   |                                       |

|      |             |     |                                       |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| <pre>// C example using MPLAB C30</pre> |                                                 |

|-----------------------------------------|-------------------------------------------------|

| asm("DISI #5");                         | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();                    | // Perform unlock sequence and set WR           |

| REGISTER     | 8-17: IPC0                                                                                                                              | : INTERRUPT                             | PRIORITY (       | CONTROL RI        | EGISTER 0       |                 |         |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|

| U-0          | R/W-1                                                                                                                                   | R/W-0                                   | R/W-0            | U-0               | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

| —            | T1IP2                                                                                                                                   | T1IP1                                   | T1IP0            | —                 | OC1IP2          | OC1IP1          | OC1IP0  |  |  |  |  |  |

| bit 15       |                                                                                                                                         |                                         |                  |                   |                 |                 | bit 8   |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                                   | R/W-0                                   | R/W-0            | U-0               | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

|              | IC1IP2                                                                                                                                  | IC1IP1                                  | IC1IP0           |                   | INT0IP2         | INT0IP1         | INTOIPO |  |  |  |  |  |

| bit 7        |                                                                                                                                         |                                         |                  |                   |                 |                 | bit 0   |  |  |  |  |  |

| Logondu      |                                                                                                                                         |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

| Legend:      | la hit                                                                                                                                  | VV - VVritabla I                        | .:+              |                   | nantad hit raa  | d aa 'O'        |         |  |  |  |  |  |

| R = Readab   |                                                                                                                                         | W = Writable I                          | אנ               | -                 | nented bit, rea |                 |         |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                   | '1' = Bit is set                        |                  | '0' = Bit is cle  | ared            | x = Bit is unkr | iown    |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                               | nted: Read as 'o                        | ,                |                   |                 |                 |         |  |  |  |  |  |

| bit 14-12    | T1IP<2:0>: ⊺                                                                                                                            | Timer1 Interrupt                        | Priority bits    |                   |                 |                 |         |  |  |  |  |  |

|              | 111 <b>= Interru</b>                                                                                                                    | upt is Priority 7 (ł                    | nighest priority | interrupt)        |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       | •<br>001 = Interrupt is Priority 1      |                  |                   |                 |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                                     |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

| bit 11       |                                                                                                                                         | nted: Read as '0                        |                  |                   |                 |                 |         |  |  |  |  |  |

| bit 10-8     | -                                                                                                                                       |                                         |                  | nterrunt Priorit  | v bite          |                 |         |  |  |  |  |  |

| DIL 10-0     | <b>OC1IP&lt;2:0&gt;:</b> Output Compare Channel 1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                                                                           |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              |                                                                                                                                         | upt source is disa                      |                  |                   |                 |                 |         |  |  |  |  |  |

| bit 7        | Unimpleme                                                                                                                               | nted: Read as '0                        | 3                |                   |                 |                 |         |  |  |  |  |  |

| bit 6-4      | IC1IP<2:0>:                                                                                                                             | Input Capture C                         | hannel 1 Inter   | rupt Priority bit | S               |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                                                                                           | upt is Priority 7 (ł                    | nighest priority | interrupt)        |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | •<br>001 <b>– Intorr</b> i                                                                                                              | upt is Priority 1                       |                  |                   |                 |                 |         |  |  |  |  |  |

|              |                                                                                                                                         | upt source is disa                      | abled            |                   |                 |                 |         |  |  |  |  |  |

| bit 3        |                                                                                                                                         | nted: Read as '0                        |                  |                   |                 |                 |         |  |  |  |  |  |

| bit 2-0      | -                                                                                                                                       |                                         |                  | its               |                 |                 |         |  |  |  |  |  |

| 5112 0       | INT0IP<2:0>: External Interrupt 0 Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)                           |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              |                                                                                                                                         |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |  |  |  |

|              |                                                                                                                                         | upt is Priority 1<br>upt source is disa |                  |                   |                 |                 |         |  |  |  |  |  |

#### REGISTER 8-22: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| —       | —   | —   | —   | _   | —       | —       | _       |

| bit 15  |     | •   |     |     |         |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —       |     | —   | —   | —   | INT1IP2 | INT1IP1 | INT1IP0 |

| bit 7   |     |     |     |     |         | •       | bit 0   |

|         |     |     |     |     |         |         |         |

| Legend: |     |     |     |     |         |         |         |

|         |     |     |     |     |         |         |         |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- :

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0          | U-0           | U-0                | U-0              | U-0               | R/W-1            | R/W-0              | R/W-0  |  |

|--------------|---------------|--------------------|------------------|-------------------|------------------|--------------------|--------|--|

| _            | —             | —                  | —                | —                 | RTCIP2           | RTCIP1             | RTCIP0 |  |

| bit 15       |               |                    |                  |                   |                  |                    | bit 8  |  |

|              |               |                    |                  |                   |                  |                    |        |  |

| U-0          | U-0           | U-0                | U-0              | U-0               | U-0              | U-0                | U-0    |  |

|              | _             |                    | —                | —                 | _                | —                  | —      |  |

| bit 7        |               |                    |                  |                   |                  |                    | bit 0  |  |

|              |               |                    |                  |                   |                  |                    |        |  |

| Legend:      |               |                    |                  |                   |                  |                    |        |  |

| R = Readab   | le bit        | W = Writable       | bit              | U = Unimplem      | nented bit, read | l as '0'           |        |  |

| -n = Value a | t POR         | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |

|              |               |                    |                  |                   |                  |                    |        |  |

| bit 15-11    | Unimplemen    | ted: Read as '     | )'               |                   |                  |                    |        |  |

| bit 10-8     | RTCIP<2:0>:   | Real-Time Clo      | ck and Calend    | ar Interrupt Pric | ority bits       |                    |        |  |

|              | 111 = Interru | pt is Priority 7 ( | highest priority | interrupt)        |                  |                    |        |  |

|              | •             |                    |                  |                   |                  |                    |        |  |

|              | •             |                    |                  |                   |                  |                    |        |  |

|              | 001 = Interru |                    |                  |                   |                  |                    |        |  |

|              | -             | ot source is dis   |                  |                   |                  |                    |        |  |

| bit 7-0      | Unimplemen    | ted: Read as '     | )'               |                   |                  |                    |        |  |

|              |               |                    |                  |                   |                  |                    |        |  |

#### REGISTER 8-28: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

#### 19.2.5 RTCVAL REGISTER MAPPINGS

#### REGISTER 19-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | —      | —      | —      | —      | —      | —      |

| bit 15 |        |        | •      | •      |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-x  |

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

#### Legend:

| Legenu.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

#### REGISTER 19-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0            | R/W-x | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|----------------|-------|---------|---------|---------|---------|---------|

| —     | DAYTEN1 DAYTEN |       | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |                |       |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                                    |  |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12    | <b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'. |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits                                   |

|           | Contains a value from 0 to 9.                                                                        |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits                                     |

|           | Contains a value from 0 to 3.                                                                        |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits                                     |

|           | Contains a value from 0 to 9.                                                                        |

|           |                                                                                                      |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### 19.3 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value, loaded into the lower half of RCFGCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

- 3. a) If the oscillator is faster than ideal (negative result from Step 2), the RCFGCAL register value must be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower than ideal (positive result from Step 2), the RCFGCAL register value must be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

#### **EQUATION 19-1:**

| (Ideal Frequency + – Measured Frequency) * |  |  |  |  |  |  |  |

|--------------------------------------------|--|--|--|--|--|--|--|

| 60 = Clocks per Minute                     |  |  |  |  |  |  |  |

| † Ideal Frequency = 32,768 Hz              |  |  |  |  |  |  |  |

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off, or immediately after the rising edge of the seconds pulse, except when SECONDS = 00, 15, 30 or 45. This is due to the auto-adjust of the RTCC at 15 second intervals.

**Note:** It is up to the user to include, in the error value, the initial error of the crystal: drift due to temperature and drift due to crystal aging.

#### 19.4 Alarm

- Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>)

- One-time alarm and repeat alarm options are available

#### 19.4.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 19-2, the interval selection of the alarm is configured through the AMASKx bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT<7:0> bits (ALCFGRPT<7:0>). When the value of the ARPTx bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled, and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.

After each alarm is issued, the value of the ARPTx bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which, the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPTx bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

#### 19.4.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a trigger clock to other peripherals.

Note: Changing any of the registers, other than the RCFGCAL and ALCFGRPT registers, and the CHIME bit while the alarm is enabled (ALRMEN = 1), can result in a false alarm event leading to a false alarm interrupt. To avoid a false alarm event, the timer and alarm values should only be changed while the alarm is disabled (ALRMEN = 0). It is recommended that the ALCFGRPT register and CHIME bit be changed when RTCSYNC = 0.

#### 22.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter with Threshold Detect, refer to the "PIC24F Family Reference Manual", Section 51. "12-Bit A/D Converter with Threshold Detect" (DS39739).

The PIC24F 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR)

Conversion

- Conversion Speeds of up to 100 ksps

- Up to 32 Analog Input Channels (Internal and External)

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H)

Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed-Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in some PIC24 devices. Both modules are Successive Approximation Register (SAR) converters at their cores, surrounded by a range of hardware features for flexible configuration. This version of the module extends functionality by providing 12-bit resolution, a wider range of automatic sampling options and tighter integration with other analog modules, such as the CTMU and a configurable results buffer. This module also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results.

A simplified block diagram for the module is illustrated in Figure 22-1.

| REGISTER 26-7: FICD: IN-CIRCUIT DEBUGGER CONFIGURATION REGISTER                                                                                                                                                                                                                   |         |                  |           |                   |                  |                    |       |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|-----------|-------------------|------------------|--------------------|-------|--|--|--|

| R/P-1                                                                                                                                                                                                                                                                             | U-0     | U-0              | U-0       | U-0               | U-0              | R/P-1              | R/P-1 |  |  |  |

| DEBUG                                                                                                                                                                                                                                                                             | —       | —                | —         | —                 | —                | FICD1              | FICD0 |  |  |  |

| bit 7                                                                                                                                                                                                                                                                             |         |                  |           |                   |                  |                    | bit 0 |  |  |  |

| Languale                                                                                                                                                                                                                                                                          |         |                  |           |                   |                  |                    |       |  |  |  |

| Legend:                                                                                                                                                                                                                                                                           |         |                  |           |                   |                  |                    |       |  |  |  |

| R = Readab                                                                                                                                                                                                                                                                        | ole bit | P = Programn     | nable bit | U = Unimplem      | nented bit, read | l as '0'           |       |  |  |  |

| -n = Value a                                                                                                                                                                                                                                                                      | at POR  | '1' = Bit is set |           | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |  |  |

| bit 7       DEBUG: Background Debugger Enable bit         1 = Background debugger is disabled         0 = Background debugger functions are enabled         bit 6-2       Unimplemented: Read as '0'         bit 1-0       FICD<1:0:>: ICD Pin Select bits                        |         |                  |           |                   |                  |                    |       |  |  |  |

| <ul> <li>11 = PGEC1/PGED1 are used for programming and debugging the device</li> <li>10 = PGEC2/PGED2 are used for programming and debugging the device</li> <li>01 = PGEC3/PGED3 are used for programming and debugging the device</li> <li>00 = Reserved; do not use</li> </ul> |         |                  |           |                   |                  |                    |       |  |  |  |

#### 28.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |  |  |  |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |  |  |  |  |  |  |

|       | reference source.                          |  |  |  |  |  |  |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| DC CHARACTERISTICS |                |                   | <b>Operating</b><br>temperature |    | <b>2.0V t</b><br>≤ TA ≤ +85 | $\begin{array}{l} \textbf{1.8V to 3.6V PIC24F32KA3XX} \\ \textbf{2.0V to 5.5V PIC24FV32KA3XX} \\ TA \leq +85^{\circ}C \text{ for Industrial} \\ TA \leq +125^{\circ}C \text{ for Extended} \end{array}$ |  |  |

|--------------------|----------------|-------------------|---------------------------------|----|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter No.      | Device         | Typical Max Units |                                 |    |                             | Conditions                                                                                                                                                                                              |  |  |

| IDD Current        |                |                   |                                 |    |                             |                                                                                                                                                                                                         |  |  |

| D20                | PIC24FV32KA3XX | 269               | 450                             | μA | 2.0V                        |                                                                                                                                                                                                         |  |  |

|                    |                | 465               | 830                             | μA | 5.0V                        | 0.5 MIPS,                                                                                                                                                                                               |  |  |

|                    | PIC24F32KA3XX  | 200               | 330                             | μA | 1.8V                        | Fosc = 1 MHz <sup>(1)</sup>                                                                                                                                                                             |  |  |

|                    |                | 410               | 750                             | μA | 3.3V                        |                                                                                                                                                                                                         |  |  |

| DC22               | PIC24FV32KA3XX | 490               | _                               | μA | 2.0V                        |                                                                                                                                                                                                         |  |  |

|                    |                | 880               |                                 | μA | 5.0V                        | 1 MIPS,                                                                                                                                                                                                 |  |  |

|                    | PIC24F32KA3XX  | 407               |                                 | μA | 1.8V                        | Fosc = 2 MHz <sup>(1)</sup>                                                                                                                                                                             |  |  |

|                    |                | 800               |                                 | μA | 3.3V                        |                                                                                                                                                                                                         |  |  |

| DC24               | PIC24FV32KA3XX | 13.0              | 20.0                            | mA | 5.0V                        | 16 MIPS,                                                                                                                                                                                                |  |  |

|                    | PIC24F32KA3XX  | 12.0              | 18.0                            | mA | 3.3V                        | Fosc = 32 MHz <sup>(1)</sup>                                                                                                                                                                            |  |  |

| DC26               | PIC24FV32KA3XX | 2.0               |                                 | mA | 2.0V                        |                                                                                                                                                                                                         |  |  |

|                    |                | 3.5               |                                 | mA | 5.0V                        | FRC (4 MIPS),                                                                                                                                                                                           |  |  |

|                    | PIC24F32KA3XX  | 1.80              |                                 | mA | 1.8V                        | Fosc = 8 MHz                                                                                                                                                                                            |  |  |

|                    |                | 3.40              |                                 | mA | 3.3V                        |                                                                                                                                                                                                         |  |  |

| DC30               | PIC24FV32KA3XX | 48.0              | 250                             | μA | 2.0V                        |                                                                                                                                                                                                         |  |  |

|                    |                | 75.0              | 450                             | μA | 5.0V                        | LPRC (15.5 KIPS),                                                                                                                                                                                       |  |  |

|                    | PIC24F32KA3XX  | 8.1               | 28                              | μA | 1.8V                        | Fosc = 31 kHz                                                                                                                                                                                           |  |  |

|                    |                | 13.50             | 150                             | μA | 3.3V                        |                                                                                                                                                                                                         |  |  |

#### TABLE 29-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

Legend: Unshaded rows represent PIC24F32KA3XX devices and shaded rows represent PIC24FV32KA3XX devices.

**Note 1:** Oscillator is in External Clock mode (FOSCSEL<2:0> = 010, FOSC<1:0> = 00).

| DC CHARACTERISTICS |     |                     | Operating temperature            |   |     | nditions: 1.8V to 3.6V PIC24F32KA3XX<br>2.0V to 5.5V PIC24FV32KA3XX<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |               |            |  |

|--------------------|-----|---------------------|----------------------------------|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|--|

| Param<br>No.       | Sym | Characteristic      | Min Typ <sup>(1)</sup> Max Units |   |     | Conditions                                                                                                                                                       |               |            |  |

|                    | Vol | Output Low Voltage  |                                  |   |     |                                                                                                                                                                  |               |            |  |

| DO10               |     | All I/O Pins        | —                                | — | 0.4 | V                                                                                                                                                                | IOL = 8.0 mA  | VDD = 4.5V |  |

|                    |     |                     | —                                | — | 0.4 | V                                                                                                                                                                | IOL = 4.0 mA  | VDD = 3.6V |  |

|                    |     |                     | —                                | — | 0.4 | V                                                                                                                                                                | IOL = 3.5 mA  | VDD = 2.0V |  |

| DO16               |     | OSC2/CLKO           | _                                | _ | 0.4 | V                                                                                                                                                                | IOL = 2.0 mA  | VDD = 4.5V |  |

|                    |     |                     | —                                | — | 0.4 | V                                                                                                                                                                | IOL = 1.2 mA  | VDD = 3.6V |  |

|                    |     |                     | —                                | — | 0.4 | V                                                                                                                                                                | IOL = 0.4 mA  | VDD = 2.0V |  |

|                    | Vон | Output High Voltage |                                  |   |     |                                                                                                                                                                  |               |            |  |

| DO20               |     | All I/O Pins        | 3.8                              | — | —   | V                                                                                                                                                                | IOH = -3.5 mA | VDD = 4.5V |  |

|                    |     |                     | 3                                | — | —   | V                                                                                                                                                                | IOH = -3.0 mA | VDD = 3.6V |  |

|                    |     |                     | 1.6                              | _ | —   | V                                                                                                                                                                | IOH = -1.0 mA | VDD = 2.0V |  |

| DO26               |     | OSC2/CLKO           | 3.8                              | _ | —   | V                                                                                                                                                                | Іон = -2.0 mA | VDD = 4.5V |  |

|                    |     |                     | 3                                | _ | —   | V                                                                                                                                                                | IOH = -1.0 mA | VDD = 3.6V |  |

|                    |     |                     | 1.6                              | _ | _   | V                                                                                                                                                                | Іон = -0.5 mA | VDD = 2.0V |  |

#### TABLE 29-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS              |       |                                      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |       |            |                                               |  |  |

|---------------------------------|-------|--------------------------------------|-------------------------------------------------------|----|-------|------------|-----------------------------------------------|--|--|

| Param<br>No. Sym Characteristic |       | Min                                  | Min Typ <sup>(1)</sup>                                |    | Units | Conditions |                                               |  |  |

|                                 |       | Program Flash Memory                 |                                                       |    |       |            |                                               |  |  |

| D130                            | Eр    | Cell Endurance                       | 10,000 <sup>(2)</sup>                                 | —  | —     | E/W        |                                               |  |  |

| D131                            | Vpr   | VDD for Read                         | VMIN                                                  | _  | 3.6   | V          | VMIN = Minimum operating voltage              |  |  |

| D133A                           | Tiw   | Self-Timed Write Cycle<br>Time       | _                                                     | 2  | —     | ms         |                                               |  |  |

| D134                            | TRETD | Characteristic Retention             | 40                                                    | _  | —     | Year       | Provided no other specifications are violated |  |  |

| D135                            | IDDP  | Supply Current During<br>Programming |                                                       | 10 | —     | mA         |                                               |  |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Self-write and block erase.

#### TABLE 29-24: COMPARATOR TIMINGS

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Мах | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | _   | —   | 10  | μS    |          |