#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 39                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka304-e-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE I-I. DEVICE FEATO                            |                                      |                               |                             |                   |                                              |                |

|----------------------------------------------------|--------------------------------------|-------------------------------|-----------------------------|-------------------|----------------------------------------------|----------------|

| Features                                           | PIC24FV16KA301                       | PIC24FV32KA301                | PIC24FV16KA302              | PIC24FV32KA302    | PIC24FV16KA304                               | PIC24FV32KA304 |

| Operating Frequency                                |                                      |                               | DC – 32 I                   | MHz               |                                              |                |

| Program Memory (bytes)                             | 16K                                  | 32K                           | 16K                         | 32K               | 16K                                          | 32K            |

| Program Memory (instructions)                      | 5632                                 | 11264                         | 5632                        | 11264             | 5632                                         | 11264          |

| Data Memory (bytes)                                |                                      |                               | 2048                        |                   |                                              |                |

| Data EEPROM Memory (bytes)                         |                                      |                               | 512                         |                   |                                              |                |

| Interrupt Sources (soft vectors/<br>NMI traps)     | 30 (26/4)                            |                               |                             |                   |                                              |                |

| I/O Ports                                          | PORTA<5:0><br>PORTB<15:12,9:7,4,2:0> |                               | PORTA<7,5:0><br>PORTB<15:0> |                   | PORTA<11:7,5:0><br>PORTB<15:0><br>PORTC<9:0> |                |

| Total I/O Pins                                     | 17                                   | 7                             | 23                          |                   | 3                                            | 8              |

| Timers: Total Number (16-bit)                      |                                      |                               | 5                           |                   |                                              |                |

| 32-Bit (from paired 16-bit timers)                 |                                      |                               | 2                           |                   |                                              |                |

| Input Capture Channels                             |                                      |                               | 3                           |                   |                                              |                |

| Output Compare/PWM Channels                        |                                      |                               | 3                           |                   |                                              |                |

| Input Change Notification Interrupt                | 16                                   | 6                             | 2                           | 2                 | 37                                           |                |

| Serial Communications: UART<br>SPI (3-wire/4-wire) |                                      |                               | 2                           |                   |                                              |                |

| I <sup>2</sup> C™                                  |                                      |                               | 2                           |                   |                                              |                |

| 12-Bit Analog-to-Digital Module (input channels)   | 12                                   | 2                             | 1:                          | 3                 | 1                                            | 6              |

| Analog Comparators                                 |                                      |                               | 3                           |                   |                                              |                |

| Resets (and delays)                                |                                      | BOR, RESET<br>Instruction, Ha |                             | , Configurati     |                                              |                |

| Instruction Set                                    | 76 B                                 | ase Instructio                | ns, Multiple A              | ddressing M       | ode Variation                                | s              |

| Packages                                           | -                                    | )-Pin                         |                             | Pin<br>P/SOIC/QFN | 44-Pin QI<br>48-Pin                          |                |

#### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

int attribute ((space(auto psv))) progAddr = 0x1234; // Global variable located in Pgm Memory

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

builtin tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5

// instructions

builtin write NVM();

// C30 function to perform unlock

// sequence and set WR

```

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ;  | Set up NVMCO        | N for row programming operatio        | ns                                          |

|----|---------------------|---------------------------------------|---------------------------------------------|

|    | MOV                 | #0x4004, W0                           | ;                                           |

|    | MOV                 | W0, NVMCON                            | ; Initialize NVMCON                         |

| ;  | Set up a poi        | nter to the first program memo        | ry location to be written                   |

| ;  | program memo        | ry selected, and writes enable        | d                                           |

|    | MOV                 | #0x0000, W0                           | ;                                           |

|    | MOV                 | W0, TBLPAG                            | ; Initialize PM Page Boundary SFR           |

|    | MOV                 | #0x6000, W0                           | ; An example program memory address         |

| ;  | Perform the         | TBLWT instructions to write th        | e latches                                   |

| ;  | Oth_program_        |                                       |                                             |

|    | MOV                 | #LOW_WORD_0, W2                       | ;                                           |

|    | MOV                 | #HIGH_BYTE_0, W3                      | ;                                           |

|    |                     | W2, [W0]                              | ; Write PM low word into program latch      |

|    | TBLWTH              | W3, [W0++]                            | ; Write PM high byte into program latch     |

| ;  | lst_program_        |                                       |                                             |

|    | MOV                 | #LOW_WORD_1, W2                       | ;                                           |

|    |                     | #HIGH_BYTE_1, W3                      | ;                                           |

|    |                     | W2, [W0]                              | ; Write PM low word into program latch      |

|    |                     | W3, [W0++]                            | ; Write PM high byte into program latch     |

| ;  | 2nd_program         | —                                     |                                             |

|    | MOV                 | #LOW_WORD_2, W2                       | ;                                           |

|    | MOV                 | <pre>#HIGH_BYTE_2, W3</pre>           |                                             |

|    |                     | W2, [W0]                              | ; Write PM low word into program latch      |

|    | TBLWTH              | W3, [W0++]                            | ; Write PM high byte into program latch     |

|    | •                   |                                       |                                             |

|    | •                   |                                       |                                             |

| Ι. | -                   | trand                                 |                                             |

| '  | 32nd_program<br>MOV |                                       |                                             |

|    | MOV                 | #LOW_WORD_31, W2<br>#HIGH BYTE 31, W3 | ;                                           |

|    |                     | W2, [W0]                              | ;<br>; Write PM low word into program latch |

|    |                     | W2, [W0]<br>W3, [W0]                  | ; Write PM high byte into program latch     |

|    | חואתמו              | M2, [M0]                              | , write in high byte into program fatch     |

|               |                                                                                                                                                                                                                                                           |                                                                                |                          | AT CONTRO        |                |                |                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|------------------|----------------|----------------|----------------|

| R/S-0, HC     | R/W-0                                                                                                                                                                                                                                                     | R/W-0                                                                          | R/W-0                    | U-0              | U-0            | U-0            | U-0            |

| WR            | WREN                                                                                                                                                                                                                                                      | WRERR                                                                          | PGMONLY                  |                  | _              | —              | _              |

| bit 15        |                                                                                                                                                                                                                                                           |                                                                                |                          |                  |                |                | bit 8          |

|               | Dates                                                                                                                                                                                                                                                     | <b>D</b> # 44 0                                                                | <b>D</b> 444 0           | <b>D</b> 444 0   | DAMA           | <b>D</b> 444 0 | <b>D</b> 444 0 |

| U-0           | R/W-0                                                                                                                                                                                                                                                     | R/W-0                                                                          | R/W-0                    | R/W-0            | R/W-0          | R/W-0          | R/W-0          |

| -             | ERASE NVMOP5 NVMOP4 NVMOP3 NVMOP2 NVMOP1 N                                                                                                                                                                                                                |                                                                                |                          |                  |                |                | NVMOP0         |

| bit 7         |                                                                                                                                                                                                                                                           |                                                                                |                          |                  |                |                | bit 0          |

| Legend:       |                                                                                                                                                                                                                                                           | HC = Hardware                                                                  | Clearable bit            | U = Unimple      | mented bit, re | ead as '0'     |                |

| R = Readable  | e bit                                                                                                                                                                                                                                                     | W = Writable bit                                                               |                          | S = Settable     |                |                |                |

| -n = Value at | POR                                                                                                                                                                                                                                                       | '1' = Bit is set                                                               |                          | '0' = Bit is cle | eared          | x = Bit is unk | nown           |

| bit 15        | <ul> <li>bit 15</li> <li>WR: Write Control bit (program or erase)</li> <li>1 = Initiates a data EEPROM erase or write cycle (can be set, but not cleared in software)</li> <li>0 = Write cycle is complete (cleared automatically by hardware)</li> </ul> |                                                                                |                          |                  |                |                |                |

| bit 14        | 1 = Enables a                                                                                                                                                                                                                                             | Enable bit (erase<br>n erase or progra<br>ion allowed (device                  | m operation              | on completion    | of the write/e | erase operatio | n)             |

| bit 13        | 1 = A write on operation                                                                                                                                                                                                                                  | e Flash Error Flag<br>operation is prem<br>)<br>operation comple               | aturely terminat         |                  | R or WDT F     | Reset during   | programming    |

| bit 12        | 1 = Write ope<br>0 = Automatie                                                                                                                                                                                                                            | rogram Only Ena<br>eration is executed<br>c erase-before-wr<br>ns are preceded | l without erasing<br>ite |                  | . ,            | ess(es).       |                |

| bit 11-7      | Unimplement                                                                                                                                                                                                                                               | ted: Read as '0'                                                               |                          |                  |                |                |                |

| bit 6         | 1 = Performs                                                                                                                                                                                                                                              | e Operation Select<br>an erase operation                                       | on when WR is s          |                  |                |                |                |

|               |                                                                                                                                                                                                                                                           | a write operation                                                              |                          |                  |                |                |                |

| bit 5-0       | Erase Operati<br>011010 = Era<br>011001 = Era<br>011000 = Era<br>0100xx = Era                                                                                                                                                                             | ases 4 words<br>ases 1 word<br>ases entire data E<br><u>Operations (when</u>   | E bit is '1'):<br>EPROM  |                  |                |                |                |

#### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

| REGISTER     | 8-9: IFS4  | INTERRUPT                            | FLAG STAT      | US REGISTE        | :R 4             |                 |           |

|--------------|------------|--------------------------------------|----------------|-------------------|------------------|-----------------|-----------|

| U-0          | U-0        | R/W-0, HS                            | U-0            | U-0               | U-0              | U-0             | R/W-0, HS |

| _            | —          | CTMUIF                               | _              | —                 | —                | —               | HLVDIF    |

| bit 15       |            |                                      |                |                   |                  |                 | bit 8     |

|              |            |                                      |                |                   |                  |                 |           |

| U-0          | U-0        | U-0                                  | U-0            | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | U-0       |

| —            | —          | —                                    | —              | CRCIF             | U2ERIF           | U1ERIF          | —         |

| bit 7        |            |                                      |                |                   |                  |                 | bit (     |

|              |            |                                      |                |                   |                  |                 |           |

| Legend:      |            | HS = Hardwar                         |                |                   |                  |                 |           |

| R = Readab   |            | W = Writable t                       | Dit            |                   | nented bit, read |                 |           |

| -n = Value a | It POR     | '1' = Bit is set                     |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |

|              |            |                                      | ,              |                   |                  |                 |           |

| bit 15-14    | -          | nted: Read as '0                     |                |                   |                  |                 |           |

| bit 13       |            | MU Interrupt Fla                     | -              |                   |                  |                 |           |

|              |            | request has occ<br>request has not   |                |                   |                  |                 |           |

| bit 12-9     | •          | nted: Read as '0                     |                |                   |                  |                 |           |

| bit 8        | •          | h/Low-Voltage D                      |                | t Elag Status bit | t                |                 |           |

|              | •          | request has occ                      | •              |                   |                  |                 |           |

|              |            | request has not                      |                |                   |                  |                 |           |

| bit 7-4      | Unimplemer | nted: Read as '0                     | ,              |                   |                  |                 |           |

| bit 3        | CRCIF: CRC | Generator Inter                      | rupt Flag Stat | us bit            |                  |                 |           |

|              |            | request has occ                      |                |                   |                  |                 |           |

|              | -          | request has not                      |                |                   |                  |                 |           |

| bit 2        |            | RT2 Error Interru                    |                | s bit             |                  |                 |           |

|              |            | request has occ                      |                |                   |                  |                 |           |

| <b>L:1</b>   | •          | request has not                      |                | - I-:4            |                  |                 |           |

| bit 1        |            | RT1 Error Interru<br>request has occ |                | SDIL              |                  |                 |           |

|              |            | request has not                      |                |                   |                  |                 |           |

| bit 0        | •          | nted: Read as '0                     |                |                   |                  |                 |           |

|              |            |                                      |                |                   |                  |                 |           |

#### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

#### REGISTER 8-29: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0                           | R/W-1                                                                          | R/W-0                                                                                          | R/W-0                                                           | U-0               | R/W-1                              | R/W-0           | R/W-0   |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------|------------------------------------|-----------------|---------|--|--|--|--|--|

|                               | CRCIP2                                                                         | CRCIP1                                                                                         | CRCIP0                                                          | _                 | U2ERIP2                            | U2ERIP1         | U2ERIP0 |  |  |  |  |  |

| oit 15                        |                                                                                |                                                                                                | •                                                               |                   | •                                  | •               | bit     |  |  |  |  |  |

| U-0                           | R/W-1                                                                          | R/W-0                                                                                          | R/W-0                                                           | U-0               | U-0                                | U-0             | U-0     |  |  |  |  |  |

| 0-0                           | U1ERIP2                                                                        | U1ERIP1                                                                                        | U1ERIP0                                                         | 0-0               | 0-0                                | 0-0             | 0-0     |  |  |  |  |  |

| bit 7                         | UTERIFZ                                                                        | UTERIFT                                                                                        | UTERIFU                                                         |                   |                                    |                 | bit     |  |  |  |  |  |

|                               |                                                                                |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

| _egend:                       | le hit                                                                         | \\/ - \\/:itable                                                                               | <b>L</b> :4                                                     |                   | antad bit waar                     |                 |         |  |  |  |  |  |

| R = Readab                    |                                                                                | W = Writable                                                                                   |                                                                 | •                 | nented bit, read                   |                 |         |  |  |  |  |  |

| n = Value a                   | IT POR                                                                         | '1' = Bit is set                                                                               |                                                                 | '0' = Bit is clea | ared                               | x = Bit is unkr | IOWN    |  |  |  |  |  |

| oit 15                        | Unimplemen                                                                     | ted: Read as '                                                                                 | ר <b>י</b>                                                      |                   |                                    |                 |         |  |  |  |  |  |

| oit 14-12                     | •                                                                              |                                                                                                |                                                                 | ot Priority bite  |                                    |                 |         |  |  |  |  |  |

| <i>n</i> ( 1 <del>4</del> -12 | <b>CRCIP&lt;2:0&gt;:</b> CRC Generator Error Interrupt Priority bits           |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | •                                                                              | •                                                                                              |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | •<br>001 = Interrupt is Priority 1                                             |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               |                                                                                | pt source is dis                                                                               | abled                                                           |                   |                                    |                 |         |  |  |  |  |  |

| oit 11                        | Unimplemen                                                                     | ted: Read as '                                                                                 | с'                                                              |                   |                                    |                 |         |  |  |  |  |  |

| oit 10-8                      | U2ERIP<2:0>: UART2 Error Interrupt Priority bits                               |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | 111 = Interrupt is Priority 7 (highest priority interrupt)                     |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               |                                                                                |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | •                                                                              |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | 001 = Interrupt is Priority 1                                                  |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               |                                                                                |                                                                                                |                                                                 |                   | 000 = Interrupt source is disabled |                 |         |  |  |  |  |  |

|                               |                                                                                |                                                                                                | abled                                                           |                   |                                    |                 |         |  |  |  |  |  |

| pit 7                         | 000 <b>= Interru</b>                                                           |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen                                                    | ot source is dis<br>ted: Read as '                                                             |                                                                 | ity bits          |                                    |                 |         |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                     | pt source is dis<br>ted: Read as '<br>: UART1 Error                                            | כ'                                                              | -                 |                                    |                 |         |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                     | pt source is dis<br>ted: Read as '<br>: UART1 Error                                            | o'<br>· Interrupt Priori                                        | -                 |                                    |                 |         |  |  |  |  |  |

| bit 7<br>bit 6-4              | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru                    | ot source is dis<br>ted: Read as '<br>UART1 Error<br>ot is Priority 7 (                        | o'<br>· Interrupt Priori                                        | -                 |                                    |                 |         |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru                    | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 (<br>ot is Priority 1 | o'<br>Interrupt Priori<br>highest priority                      | -                 |                                    |                 |         |  |  |  |  |  |

|                               | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru                    | ot source is dis<br>ted: Read as '<br>UART1 Error<br>ot is Priority 7 (                        | <sub>D</sub> ,<br>Interrupt Priori<br>highest priority<br>abled | -                 |                                    |                 |         |  |  |  |  |  |

#### REGISTER 8-32: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0      | U-0      | U-0      |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | —   | —        | —        | —        |

| bit 15 |     |     |     |     |          |          | bit 8    |

|        |     |     |     |     |          |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

| —      | —   | —   | —   | —   | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 |

| bit 7  |     |     |     |     |          | •        | bit 0    |

|        |     |     |     |     |          |          |          |

#### Legend:

| Logona.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

bit 6-4 ULPWUIP<2:0>: Ultra Low-Power Wake-up Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- :

• 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0                 | U-0                                  | U-0                                                                      | U-0                                                             | U-0                                | U-0                 | U-0                 | U-0                 |  |  |

|---------------------|--------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|---------------------|---------------------|---------------------|--|--|

| —                   | —                                    | —                                                                        | —                                                               | —                                  |                     | —                   |                     |  |  |

| bit 15              |                                      |                                                                          |                                                                 |                                    |                     |                     | bit 8               |  |  |

|                     |                                      |                                                                          |                                                                 |                                    |                     |                     |                     |  |  |

| U-0                 | U-0                                  | R/W-0                                                                    | R/W-0                                                           | R/W-0                              | R/W-0               | R/W-0               | R/W-0               |  |  |

| —                   | —                                    | TUN5 <sup>(1)</sup>                                                      | TUN4 <sup>(1)</sup>                                             | TUN3 <sup>(1)</sup>                | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |  |  |

| bit 7               |                                      |                                                                          |                                                                 |                                    |                     |                     | bit 0               |  |  |

|                     |                                      |                                                                          |                                                                 |                                    |                     |                     |                     |  |  |

| Legend:             |                                      |                                                                          |                                                                 |                                    |                     |                     |                     |  |  |

| R = Readable        | e bit                                | W = Writable                                                             | bit                                                             | U = Unimplemented bit, read as '0' |                     |                     |                     |  |  |

| -n = Value at       | POR                                  | '1' = Bit is set                                                         |                                                                 | '0' = Bit is cleared x = Bit is    |                     |                     | s unknown           |  |  |

| bit 15-6<br>bit 5-0 | TUN<5:0>: F<br>011111 = Ma<br>011110 | nted: Read as '<br>RC Oscillator T<br>aximum frequer<br>enter frequency, | iuning bits <sup>(1)</sup><br>ncy deviation<br>oscillator is ru | unning at factory                  | y calibrated free   | quency              |                     |  |  |

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

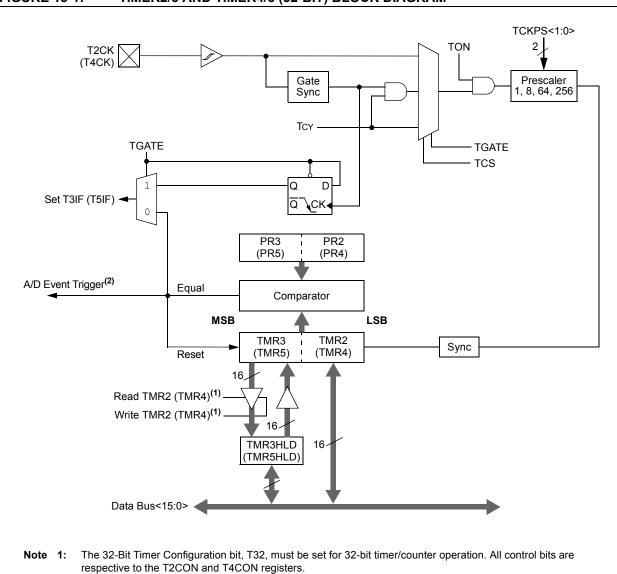

#### FIGURE 13-1: TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

2: The A/D event trigger is available only on Timer2/3 and Timer4/5 in 32-bit mode, and Timer3 and Timer5 in 16-bit mode.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0       | U-0 | U-0      | U-0      | U-0      | U-0      | R/W-0    |

|--------|-----------|-----|----------|----------|----------|----------|----------|

| —      | —         | —   | —        | —        | —        | —        | IC32     |

| bit 15 |           |     |          |          |          |          | bit 8    |

|        |           |     |          |          |          |          |          |

| R/W-0  | R/W-0, HS | U-0 | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-1    |

| ICTRIG | TRIGSTAT  | —   | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| Legend:           | HS = Hardwa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | re Settable bit   |                        |                              |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------|------------------------------|--|--|--|

| R = Readable b    | it W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit L             | J = Unimplemented      | bit, read as '0'             |  |  |  |

| -n = Value at PO  | OR '1' = Bit is se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '(                | 0' = Bit is cleared    | x = Bit is unknown           |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                        |                              |  |  |  |

| bit 15-9 <b>L</b> | Inimplemented: Read as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )'                |                        |                              |  |  |  |

| 1                 | <b>C32:</b> Cascade Two IC Mod<br>= ICx and ICy operate in<br>= ICx functions independ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ascade as a 32-   | bit module (this bit n | nust be set in both modules) |  |  |  |

| 1                 | CTRIG: Input Capture x Sy<br>= Triggers ICx from source<br>= Synchronizes ICx with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e designated by t | the SYNCSELx bits      | bits                         |  |  |  |

| 1                 | <b>TRIGSTAT:</b> Timer Trigger Status bit<br>1 = Timer source has been triggered and is running (set in hardware, can be set in software)<br>0 = Timer source has not been triggered and is being held clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                        |                              |  |  |  |

| bit 5 L           | Inimplemented: Read as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )'                |                        |                              |  |  |  |

|                   | SYNCSEL<4:0>: Trigger/S         1111 = Reserved         1110 = Reserved         1101 = Reserved         1101 = Reserved         1100 = CTMU <sup>(1)</sup> 1011 = A/D <sup>(1)</sup> 1001 = Comparator 3 <sup>(1)</sup> 1001 = Comparator 2 <sup>(1)</sup> 1000 = Comparator 3 <sup>(1)</sup> 1001 = Comparator 3 <sup>(1)</sup> 1001 = Comparator 3 <sup>(1)</sup> 1001 = Comparator 3 <sup>(1)</sup> 1011 = Input Capture 4         0110 = Input Capture 2         0100 = Input Capture 1         0011 = Reserved         0000x = Reserved         0111 = Timer3         1100 = Timer4         1101 = Timer1         1000 = Reserved         1011 = Reserved         1010 = Reserved         1011 = Reserved         1010 = Reserved         1011 = Reserved         1010 = Reserved         1011 = Output Compare 5         1000 = Output Compare 7         1010 = Output Compare 7         1010 = Output Compare 7         1011 = Output Compare 7 |                   |                        |                              |  |  |  |

Note 1: Use these inputs as trigger sources only and never as Sync sources.

bit 7

bit 0

#### **REGISTER 15-1:** OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)

#### bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: Initialize OCx pin low; toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize OCx pin low; toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- **Note 1:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

#### 19.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

#### 19.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value Register Window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 19-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 19-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |  |

|-------------|----------------------------|-------------|--|--|--|--|

| RICPIRSI.02 | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |  |

| 11          | —                          | YEAR        |  |  |  |  |

The Alarm Value Register Window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 19-2).

By writing the ALRMVALH byte, the Alarm Pointer value (ALRMPTR<1:0> bits) decrements by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL, until the pointer value is manually changed.

#### TABLE 19-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |  |

|---------|-----------------------------|--------------|--|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |  |

| 11      | PWCSTAB                     | PWCSAMP      |  |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

#### 19.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RTCPWC<13>) must be set (see Example 19-1).

Note: To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only one instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN. Therefore, it is recommended that code follow the procedure in Example 19-1.

#### 19.2.3 SELECTING RTCC CLOCK SOURCE

There are four reference source clock options that can be selected for the RTCC using the RTCCSEL<1:0> bits: 00 = Secondary Oscillator, 01 = LPRC, 10 = 50 Hz External Clock and 11 = 60 Hz External Clock.

| <br> |          |                                              |

|------|----------|----------------------------------------------|

| asm  | volatile | ("push w7");                                 |

| asm  | volatile | ("push w8");                                 |

| asm  | volatile | ("disi #5");                                 |

| asm  | volatile | ("mov #0x55, w7");                           |

| asm  | volatile | ("mov w7, NVMKEY");                          |

| asm  | volatile | ("mov #0xAA, w8");                           |

| asm  | volatile | ("mov w8, NVMKEY");                          |

| asm  | volatile | ("bset RCFGCAL, #13"); //set the RTCWREN bit |

| asm  | volatile | ("pop w8");                                  |

| asm  | volatile | ("pop w7");                                  |

|      |          |                                              |

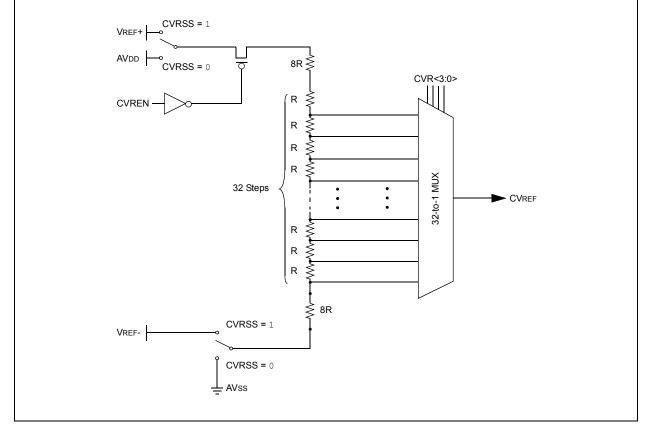

#### 24.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator Voltage Reference, refer to the "PIC24F Family Reference Manual", Section 20. "Comparator Module Voltage Reference Module" (DS39709).

#### 24.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 24-1). The comparator voltage reference provides a range of output voltages, with 32 distinct levels.

The comparator voltage reference supply voltage can come from either VDD and VSS or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

| R/P-1                | R/P-1                             | R/P-1                                | R/P-1                  | R/P-1                | R/P-1                 | R/P-1                     | R/P-1             |

|----------------------|-----------------------------------|--------------------------------------|------------------------|----------------------|-----------------------|---------------------------|-------------------|

| MCLRE <sup>(2)</sup> | BORV1 <sup>(3)</sup>              | BORV0 <sup>(3)</sup>                 | I2C1SEL <sup>(1)</sup> | PWRTEN               | RETCFG <sup>(1)</sup> | BOREN1                    | BOREN0            |

| bit 7                |                                   |                                      |                        |                      |                       |                           | bit (             |

|                      |                                   |                                      |                        |                      |                       |                           |                   |

| Legend:              |                                   |                                      |                        |                      |                       |                           |                   |

| R = Reada            | able bit                          | P = Programr                         | nable bit              | U = Unimplen         | nented bit, read      | as '0'                    |                   |

| -n = Value           | at POR                            | '1' = Bit is set                     |                        | '0' = Bit is clea    | ared                  | x = Bit is unkr           | nown              |

|                      |                                   |                                      | ··(2)                  |                      |                       |                           |                   |

| bit 7                |                                   | R Pin Enable b                       |                        | iaablad              |                       |                           |                   |

|                      |                                   | is enabled; RA pin is enabled;       |                        |                      |                       |                           |                   |

| bit 6-5              |                                   | Brown-out Rese                       |                        |                      |                       |                           |                   |

|                      |                                   | ut Reset is set t                    |                        |                      |                       |                           |                   |

|                      | 10 <b>= Brown-o</b>               |                                      |                        | 0                    |                       |                           |                   |

|                      |                                   | ut Reset is set t                    | •                      | •                    | »••••••••••           |                           |                   |

|                      |                                   | e protection on                      |                        | a – "zero powe       | r" is selected        |                           |                   |

| bit 4                |                                   | ernate I2C1 Pin                      |                        |                      |                       |                           |                   |

|                      |                                   | cation for SCL1,<br>ocation for SCL  |                        |                      |                       |                           |                   |

| bit 3                |                                   | wer-up Timer E                       | •                      |                      |                       |                           |                   |

|                      | 1 = PWRT is e                     | enabled                              |                        |                      |                       |                           |                   |

|                      | 0 = PWRT is c                     | disabled                             |                        |                      |                       |                           |                   |

| bit 2                |                                   | ention Regulate                      |                        | ו bit <sup>(1)</sup> |                       |                           |                   |

|                      |                                   | Regulator is no                      |                        |                      |                       |                           | 0                 |

|                      |                                   | •                                    |                        | -                    | RETEN bit (RCO        | N<12>) during             | Sleep             |

| oit 1-0              |                                   | : Brown-out Re                       |                        |                      | tio dia abla d        |                           |                   |

|                      |                                   | ut Reset is enab<br>it Reset is enab |                        |                      | and disabled in S     | Sleep <sup>,</sup> SBOREN | l bit is disabled |

|                      |                                   | ut Reset is cont                     |                        |                      |                       |                           |                   |

|                      | 00 <b>= Brown-o</b>               | ut Reset is disa                     | bled in hardwa         | re; SBOREN bi        | t is disabled         |                           |                   |

| Note 1:              | This setting only devices.        | / applies to the                     | "FV" devices. 1        | This bit is reser    | ved and should        | be maintained a           | as '1' on "F"     |

| 2:                   | The MCLRE fus<br>user from accide | entally locking o                    | out the device f       | rom the low-vo       | ltage test entry.     | ode entry. This           | prevents a        |

| 3:                   | Refer to Sectio                   |                                      |                        |                      |                       |                           |                   |

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                                                                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|----------------------------------------------------------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                                                                | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                                                                               | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                                                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                                                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                                                                  | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                                                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                                                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                                                                  | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR    | f                | f = f .IOR. WREG                                                                             | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                                                                          | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                                                                          | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                                                                             | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                                                                           | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                                                                           | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                                                                    | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | f,WREG           | WREG = Logical Right Shift f                                                                 | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wd = Logical Right Shift Ws                                                                  | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb,Wns,Wnd       | Wnd = Logical Right Shift Wb by Wns                                                          | 1             | 1              | N, Z                     |

|                      | LSR    | Wb,#lit5,Wnd     | Wnd = Logical Right Shift Wb by lit5                                                         | 1             | 1              | N, Z                     |

| MOV                  | MOV    | f,Wn             | Move f to Wn                                                                                 | 1             | 1              | None                     |

|                      | MOV    | [Wns+Slit10],Wnd | Move [Wns+Slit10] to Wnd                                                                     | 1             | 1              | None                     |

|                      | MOV    | f                | Move f to f                                                                                  | 1             | 1              | N, Z                     |

|                      | MOV    | f,WREG           | Move f to WREG                                                                               | 1             | 1              | N, Z                     |

|                      | MOV    | #lit16,Wn        | Move 16-bit Literal to Wn                                                                    | 1             | 1              | None                     |

|                      | MOV.b  | #lit8,Wn         | Move 8-bit Literal to Wn                                                                     | 1             | 1              | None                     |

|                      | MOV    | Wn,f             | Move Wn to f                                                                                 | 1             | 1              | None                     |