Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 39                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f32ka304t-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

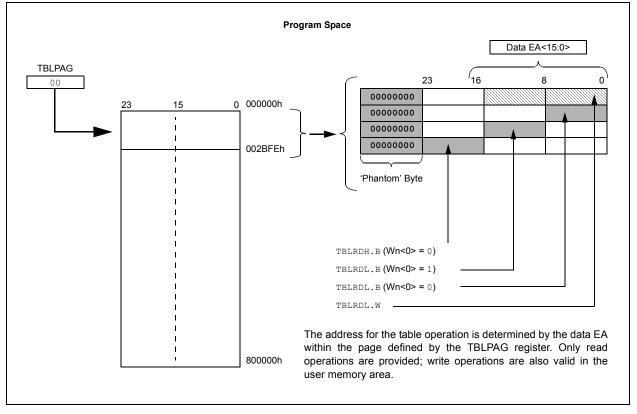

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

#### FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### 7.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. For more information, see **Section 9.0 "Oscillator Configuration"**.

# TABLE 7-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant  |

|------------|---------------------------|

| POR        | FNOSCx Configuration bits |

| BOR        | (FNOSC<10:8>)             |

| MCLR       | COSCx Control bits        |

| WDTO       | (OSCCON<14:12>)           |

| SWR        |                           |

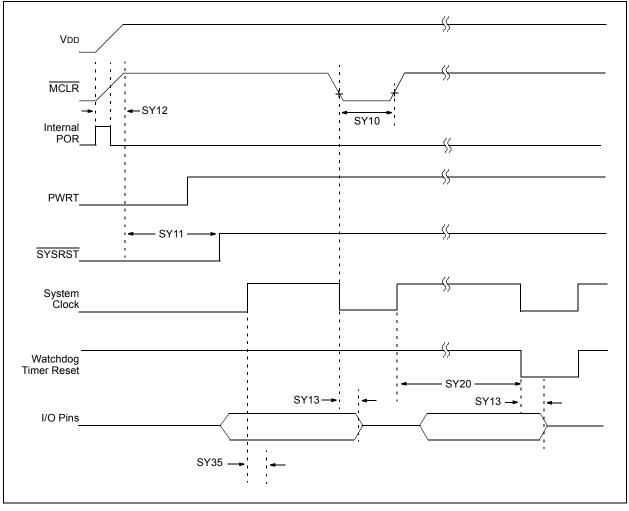

#### 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the System Reset Signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT |                       | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | Тьоск                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Тоѕт                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | TOST + TLOCK          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | —                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | Тьоск                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Тоѕт                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | _                     | None       |

#### TABLE 7-3: DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

- 2: TPWRT = 64 ms nominal if the Power-up Timer (PWRT) is enabled; otherwise, it is zero.

- **3:** TFRC and TLPRC = RC oscillator start-up times.

- **4:** TLOCK = PLL lock time.

- **5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- **6:** If Two-Speed Start-up is enabled, regardless of the primary oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 29.0 "Electrical Characteristics".

| REGISTER     | 8-17: IPC0                                                                                                                              | : INTERRUPT                             | PRIORITY (       | CONTROL RI        | EGISTER 0       |                 |         |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|-------------------|-----------------|-----------------|---------|--|--|

| U-0          | R/W-1                                                                                                                                   | R/W-0                                   | R/W-0            | U-0               | R/W-1           | R/W-0           | R/W-0   |  |  |

| —            | T1IP2                                                                                                                                   | T1IP1                                   | T1IP0            | —                 | OC1IP2          | OC1IP1          | OC1IP0  |  |  |

| bit 15       |                                                                                                                                         |                                         |                  |                   |                 |                 | bit 8   |  |  |

| U-0          | R/W-1                                                                                                                                   | R/W-0                                   | R/W-0            | U-0               | R/W-1           | R/W-0           | R/W-0   |  |  |

|              | IC1IP2                                                                                                                                  | IC1IP1                                  | IC1IP0           |                   | INT0IP2         | INT0IP1         | INTOIPO |  |  |

| bit 7        |                                                                                                                                         |                                         |                  |                   |                 |                 | bit 0   |  |  |

| Logondi      |                                                                                                                                         |                                         |                  |                   |                 |                 |         |  |  |

| Legend:      | la hit                                                                                                                                  | VV - VVritabla I                        | .:+              |                   | nantad hit raa  | d aa 'O'        |         |  |  |

| R = Readab   |                                                                                                                                         | W = Writable I                          | אנ               | -                 | nented bit, rea |                 |         |  |  |

| -n = Value a | t POR                                                                                                                                   | '1' = Bit is set                        |                  | '0' = Bit is cle  | ared            | x = Bit is unkr | iown    |  |  |

| bit 15       | Unimpleme                                                                                                                               | nted: Read as 'o                        | ,                |                   |                 |                 |         |  |  |

| bit 14-12    | T1IP<2:0>: ⊺                                                                                                                            | Timer1 Interrupt                        | Priority bits    |                   |                 |                 |         |  |  |

|              | 111 <b>= Interru</b>                                                                                                                    | upt is Priority 7 (ł                    | nighest priority | interrupt)        |                 |                 |         |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |

|              |                                                                                                                                         |                                         |                  |                   |                 |                 |         |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                                     |                                         |                  |                   |                 |                 |         |  |  |

| bit 11       |                                                                                                                                         | nted: Read as '0                        |                  |                   |                 |                 |         |  |  |

| bit 10-8     | -                                                                                                                                       |                                         |                  | nterrunt Priorit  | v bite          |                 |         |  |  |

| DIL 10-0     | <b>OC1IP&lt;2:0&gt;:</b> Output Compare Channel 1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                         |                  |                   |                 |                 |         |  |  |

|              | •                                                                                                                                       |                                         | lightest phoney  | interrupt)        |                 |                 |         |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |

|              | 001 = Interru                                                                                                                           | upt is Priority 1                       |                  |                   |                 |                 |         |  |  |

|              |                                                                                                                                         | upt source is disa                      |                  |                   |                 |                 |         |  |  |

| bit 7        | Unimpleme                                                                                                                               | nted: Read as '0                        | 3                |                   |                 |                 |         |  |  |

| bit 6-4      | IC1IP<2:0>:                                                                                                                             | Input Capture C                         | hannel 1 Inter   | rupt Priority bit | S               |                 |         |  |  |

|              | 111 = Interru                                                                                                                           | upt is Priority 7 (ł                    | nighest priority | interrupt)        |                 |                 |         |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |

|              | 001 = Interrupt is Priority 1                                                                                                           |                                         |                  |                   |                 |                 |         |  |  |

|              |                                                                                                                                         | upt source is disa                      | abled            |                   |                 |                 |         |  |  |

| bit 3        |                                                                                                                                         | nted: Read as '0                        |                  |                   |                 |                 |         |  |  |

| bit 2-0      | -                                                                                                                                       | : External Intern                       |                  | its               |                 |                 |         |  |  |

| 5112 0       |                                                                                                                                         | upt is Priority 7 (I                    |                  |                   |                 |                 |         |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |

|              |                                                                                                                                         |                                         |                  |                   |                 |                 |         |  |  |

|              | •                                                                                                                                       |                                         |                  |                   |                 |                 |         |  |  |

|              |                                                                                                                                         | upt is Priority 1<br>upt source is disa |                  |                   |                 |                 |         |  |  |

#### REGISTER 8-29: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0              | R/W-1                                                                          | R/W-0                                                                                          | R/W-0                                                           | U-0               | R/W-1                              | R/W-0           | R/W-0   |  |  |  |

|------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------|------------------------------------|-----------------|---------|--|--|--|

|                  | CRCIP2                                                                         | CRCIP1                                                                                         | CRCIP0                                                          | _                 | U2ERIP2                            | U2ERIP1         | U2ERIP0 |  |  |  |

| oit 15           |                                                                                |                                                                                                | •                                                               |                   | •                                  | •               | bit     |  |  |  |

| U-0              | R/W-1                                                                          | R/W-0                                                                                          | R/W-0                                                           | U-0               | U-0                                | U-0             | U-0     |  |  |  |

| 0-0              | U1ERIP2                                                                        | U1ERIP1                                                                                        | U1ERIP0                                                         | 0-0               | 0-0                                | 0-0             | 0-0     |  |  |  |

| bit 7            | UTERIFZ                                                                        | UTERIFT                                                                                        | UTERIFU                                                         |                   |                                    |                 | bit     |  |  |  |

|                  |                                                                                |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

| _egend:          | le hit                                                                         | \\/ - \\/:itable                                                                               | <b>L</b> :4                                                     |                   | antad bit waar                     |                 |         |  |  |  |

| R = Readab       |                                                                                | W = Writable                                                                                   |                                                                 | •                 | nented bit, read                   |                 |         |  |  |  |

| n = Value a      | IT POR                                                                         | '1' = Bit is set                                                                               |                                                                 | '0' = Bit is clea | ared                               | x = Bit is unkr | IOWN    |  |  |  |

| oit 15           | Unimplemen                                                                     | ted: Read as '                                                                                 | ר <b>י</b>                                                      |                   |                                    |                 |         |  |  |  |

| oit 14-12        | •                                                                              |                                                                                                |                                                                 | ot Priority bite  |                                    |                 |         |  |  |  |

| DIL 14-12        | CRCIP<2:0>: CRC Generator Error Interrupt Priority bits                        |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | •                                                                              | •                                                                                              |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | •<br>001 = Interru                                                             | •<br>001 = Interrupt is Priority 1                                                             |                                                                 |                   |                                    |                 |         |  |  |  |

|                  |                                                                                | pt source is dis                                                                               | abled                                                           |                   |                                    |                 |         |  |  |  |

| oit 11           | Unimplemen                                                                     | ted: Read as '                                                                                 | с'                                                              |                   |                                    |                 |         |  |  |  |

| oit 10-8         | U2ERIP<2:0>                                                                    | : UART2 Error                                                                                  | Interrupt Priori                                                | ity bits          |                                    |                 |         |  |  |  |

|                  | 111 = Interrupt is Priority 7 (highest priority interrupt)                     |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | •                                                                              |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | •                                                                              |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | 001 = Interrupt is Priority 1                                                  |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  |                                                                                |                                                                                                |                                                                 |                   | 000 = Interrupt source is disabled |                 |         |  |  |  |

|                  |                                                                                |                                                                                                | abled                                                           |                   |                                    |                 |         |  |  |  |

| pit 7            | 000 <b>= Interru</b>                                                           |                                                                                                |                                                                 |                   |                                    |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen                                                    | ot source is dis<br>ted: Read as '                                                             |                                                                 | ity bits          |                                    |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                     | pt source is dis<br>ted: Read as '<br>: UART1 Error                                            | כ'                                                              | -                 |                                    |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0>                                     | pt source is dis<br>ted: Read as '<br>: UART1 Error                                            | o'<br>· Interrupt Priori                                        | -                 |                                    |                 |         |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru                    | ot source is dis<br>ted: Read as '<br>UART1 Error<br>ot is Priority 7 (                        | o'<br>· Interrupt Priori                                        | -                 |                                    |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru                    | ot source is dis<br>ted: Read as '<br>•: UART1 Error<br>ot is Priority 7 (<br>ot is Priority 1 | o'<br>Interrupt Priori<br>highest priority                      | -                 |                                    |                 |         |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>U1ERIP<2:0><br>111 = Interru                    | ot source is dis<br>ted: Read as '<br>UART1 Error<br>ot is Priority 7 (                        | <sub>D</sub> ,<br>Interrupt Priori<br>highest priority<br>abled | -                 |                                    |                 |         |  |  |  |

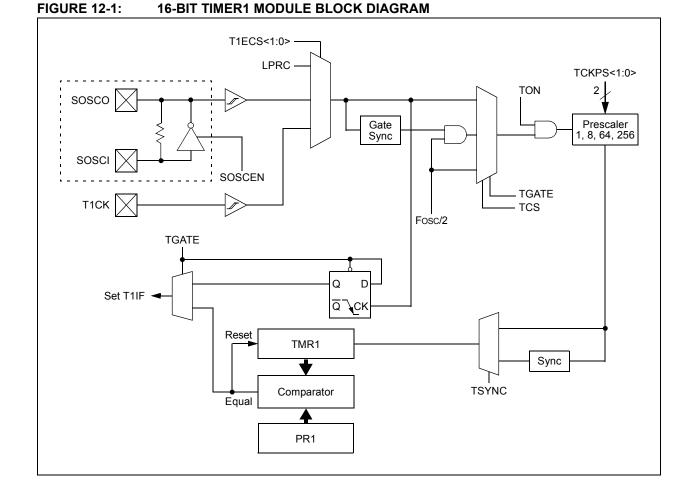

#### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

HS = Hardware Settable bit

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | R/W-0               | R/W-0               | R/W-0 |

|--------|--------|----------|-------|-----|---------------------|---------------------|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | —   | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32  |

| bit 15 |        |          |       |     |                     |                     | bit 8 |

| R/W-0  | R/W-0, HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|-----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT  | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |        |          |          |          |          | bit 0    |

| Legenu.    |                                                                                                               |                                             |                                   |

|------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|

| R = Read   | able bit W = Writable bit                                                                                     | U = Unimplemented bit,                      | read as '0'                       |

| -n = Value | e at POR '1' = Bit is set                                                                                     | '0' = Bit is cleared                        | x = Bit is unknown                |

|            |                                                                                                               |                                             |                                   |

| bit 15     | FLTMD: Fault Mode Select bit                                                                                  |                                             |                                   |

|            | 1 = Fault mode is maintained until the                                                                        | Fault source is removed and                 | I the corresponding OCFLTx bit is |

|            | cleared in software<br>0 = Fault mode is maintained until the                                                 | Fault source is removed and                 | a new PWM period starts           |

| bit 14     | FLTOUT: Fault Out bit                                                                                         |                                             |                                   |

|            | 1 = PWM output is driven high on a Fa                                                                         | ault                                        |                                   |

|            | 0 = PWM output is driven low on a Fai                                                                         | ult                                         |                                   |

| bit 13     | FLTTRIEN: Fault Output State Select b                                                                         |                                             |                                   |

|            | <ul> <li>1 = Pin is forced to an output on a Fau</li> <li>0 = Pin I/O condition is unaffected by a</li> </ul> |                                             |                                   |

| bit 12     | OCINV: Output Compare x Invert bit                                                                            | a Fault                                     |                                   |

|            | 1 = OCx output is inverted                                                                                    |                                             |                                   |

|            | 0 = OCx output is not inverted                                                                                |                                             |                                   |

| bit 11     | Unimplemented: Read as '0'                                                                                    |                                             |                                   |

| bit 10-9   | DCB<1:0>: Output Compare x Pulse-V                                                                            | Vidth Least Significant bits <sup>(3)</sup> |                                   |

|            | 11 = Delays OCx falling edge by $3/4$ of                                                                      | •                                           |                                   |

|            | 10 = Delays OCx falling edge by 1/2 of<br>01 = Delays OCx falling edge by 1/4 of                              | -                                           |                                   |

|            | 00 = OCx falling edge occurs at the sta                                                                       | 2                                           |                                   |

| bit 8      | OC32: Cascade Two Output Compare                                                                              | Modules Enable bit (32-bit op               | peration)                         |

|            | 1 = Cascade module operation is enal                                                                          |                                             |                                   |

| h:+ 7      | 0 = Cascade module operation is disa                                                                          |                                             |                                   |

| bit 7      | OCTRIG: Output Compare x Sync/Trig<br>1 = Triggers OCx from source designa                                    | -                                           |                                   |

|            | 0 = Synchronizes OCx with source designation                                                                  |                                             | its                               |

| bit 6      | TRIGSTAT: Timer Trigger Status bit                                                                            |                                             |                                   |

|            | 1 = Timer source has been triggered a                                                                         |                                             |                                   |

|            | 0 = Timer source has not been trigger                                                                         | -                                           |                                   |

| bit 5      | <b>OCTRIS:</b> Output Compare x Output Pi                                                                     | n Direction Select bit                      |                                   |

|            | <ul> <li>1 = OCx pin is tri-stated</li> <li>0 = Output Compare x peripheral is con</li> </ul>                 | anected to the OCx nin                      |                                   |

|            |                                                                                                               |                                             |                                   |

| Note 1:    | Do not use an output compare module as i equivalent SYNCSELx setting.                                         | ts own trigger source, either t             | by selecting this mode or another |

| 2:         | Use these inputs as trigger sources only ar                                                                   | nd never as Sync sources.                   |                                   |

| 3:         | These bits affect the rising edge when OCI                                                                    | NV = 1. The bits have no effe               | ct when the OCMx bits             |

|            | (OCxCON1<2:0>) = 001.                                                                                         |                                             |                                   |

Legend:

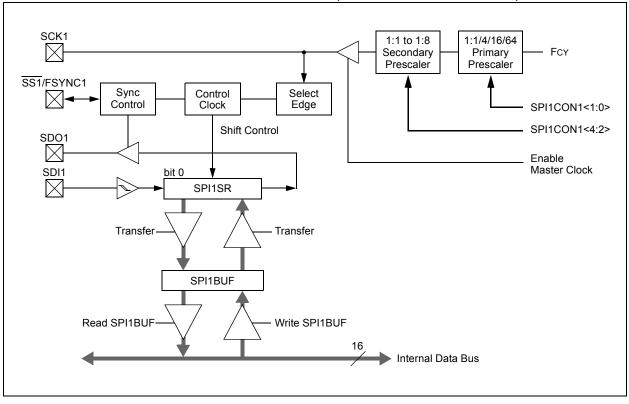

#### FIGURE 16-1: SPI1 MODULE BLOCK DIAGRAM (STANDARD BUFFER MODE)

#### 19.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

#### 19.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value Register Window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 19-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 19-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |

|-------------|----------------------------|-------------|--|--|--|

| RICPIRSI.02 | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |

| 11          | —                          | YEAR        |  |  |  |

The Alarm Value Register Window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 19-2).

By writing the ALRMVALH byte, the Alarm Pointer value (ALRMPTR<1:0> bits) decrements by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL, until the pointer value is manually changed.

#### TABLE 19-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |

|---------|-----------------------------|--------------|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |

| 11      | PWCSTAB                     | PWCSAMP      |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

#### 19.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RTCPWC<13>) must be set (see Example 19-1).

Note: To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only one instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN. Therefore, it is recommended that code follow the procedure in Example 19-1.

### 19.2.3 SELECTING RTCC CLOCK SOURCE

There are four reference source clock options that can be selected for the RTCC using the RTCCSEL<1:0> bits: 00 = Secondary Oscillator, 01 = LPRC, 10 = 50 Hz External Clock and 11 = 60 Hz External Clock.

| <br> |          |                                              |

|------|----------|----------------------------------------------|

| asm  | volatile | ("push w7");                                 |

| asm  | volatile | ("push w8");                                 |

| asm  | volatile | ("disi #5");                                 |

| asm  | volatile | ("mov #0x55, w7");                           |

| asm  | volatile | ("mov w7, NVMKEY");                          |

| asm  | volatile | ("mov #0xAA, w8");                           |

| asm  | volatile | ("mov w8, NVMKEY");                          |

| asm  | volatile | ("bset RCFGCAL, #13"); //set the RTCWREN bit |

| asm  | volatile | ("pop w8");                                  |

| asm  | volatile | ("pop w7");                                  |

|      |          |                                              |

#### 19.2.5 RTCVAL REGISTER MAPPINGS

#### REGISTER 19-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | —      | —      | —      | —      | —      | —      |

| bit 15 |        |        | •      | •      |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-x  |

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

#### Legend:

| Legenu.                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

#### REGISTER 19-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12    | <b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'. |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits                                   |

|           | Contains a value from 0 to 9.                                                                        |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits                                     |

|           | Contains a value from 0 to 3.                                                                        |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits                                     |

|           | Contains a value from 0 to 9.                                                                        |

|           |                                                                                                      |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### 20.1 User Interface

#### 20.1.1 POLYNOMIAL INTERFACE

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation. Functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing this bit disables the XOR.

For example, consider two CRC polynomials, one is a 16-bit equation and the other is a 32-bit equation:

To program these polynomials into the CRC generator, set the register bits, as shown in Table 20-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length, N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCXOR register.

#### 20.1.2 DATA INTERFACE

The module incorporates a FIFO that works with a variable data width. Input data width can be configured to any value, between 1 and 32 bits, using the DWIDTH<4:0> bits (CRCCON2<12:8>). When the data width is greater than 15, the FIFO is 4 words deep. When the DWIDTHx value is between 15 and 8, the FIFO is 8 words deep. When the DWIDTHx value is less than 8, the FIFO is 16 words deep.

The data for which the CRC is to be calculated must first be written into the FIFO. Even if the data width is less than 8, the smallest data element that can be written into the FIFO is one byte. For example, if the DWIDTHx value is 5, then the size of the data is DWIDTHx + 1 or 6. The data is written as a whole byte; the two unused upper bits are ignored by the module.

Once data is written into the MSb of the CRCDAT registers (that is, MSb as defined by the data width), the value of the VWORD<4:0> bits (CRCCON1<12:8>) increments by one. For example, if the DWIDTHx value is 24, the VWORDx bits will increment when bit 7 of CRCDATH is written. Therefore, CRCDATL must always be written before CRCDATH.

The CRC engine starts shifting data when the CRCGO bit is set and the value of the VWORDx bits is greater than zero. Each word is copied out of the FIFO into a buffer register, which decrements VWORDx. The data is then shifted out of the buffer. The CRC engine continues shifting at a rate of two bits per instruction cycle until the VWORDx value reaches zero. This means that for a given data width, it takes half that number of instructions for each word to complete the calculation. For example, it takes 16 cycles to calculate the CRC for a single word of 32-bit data.

When the VWORDx value reaches the maximum value for the configured value of DWIDTHx (4, 8 or 16), the CRCFUL bit becomes set. When the VWORDx value reaches zero, the CRCMPT bit becomes set. The FIFO is emptied and the VWORD<4:0> bits are set to '00000' whenever CRCEN is '0'.

At least one instruction cycle must pass, after a write to CRCDAT, before a read of the VWORDx bits is done.

| CRC Control | Bit Values           |                     |  |  |  |

|-------------|----------------------|---------------------|--|--|--|

| Bits        | 16-Bit Polynomial    | 32-Bit Polynomial   |  |  |  |

| PLEN<4:0>   | 01111                | 11111               |  |  |  |

| X<31:16>    | x000 0000 0000 0000x | 0000 0100 1100 0001 |  |  |  |

| X<15:0>     | 0001 0000 0010 000x  | 0001 1101 1011 011x |  |  |  |

TABLE 20-1: CRC SETUP EXAMPLES FOR 16 AND 32-BIT POLYNOMIAL

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs and/or select band gap reference inputs (ANS<12:10>, ANS<5:0>).

- b) Select voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select the interrupt rate (AD1CON2<6:2>).

- g) Turn on the A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

To perform an A/D sample and conversion using Threshold Detect scanning:

- 1. Configure the A/D module:

- a) Configure the port pins as analog inputs (ANS<12:10>, ANS<5,0>).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:4>, AD1CON3<12:8>).

- e) Select how the conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select the interrupt rate (AD1CON2<6:2>).

- 2. Configure the threshold compare channels:

- a) Enable auto-scan ASEN bit (AD1CON5<15>).

- b) Select the Compare mode, "Greater Than, Less Than or Windowed" – CMx bits (AD1CON5<1:0>).

- c) Select the threshold compare channels to be scanned (ADCSSH, ADCSSL).

- d) If the CTMU is required as a current source for a threshold compare channel, enable the corresponding CTMU channel (ADCCTMUENH, ADCCTMUENL).

- e) Write the threshold values into the corresponding ADC1BUFn registers.

- f) Turn on the A/D module (AD1CON1<15>).

Note: If performing an A/D sample and conversion using Threshold Detect in Sleep Mode, the RC A/D clock source must be selected before entering into Sleep mode.

- 3. Configure the A/D interrupt (OPTIONAL):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

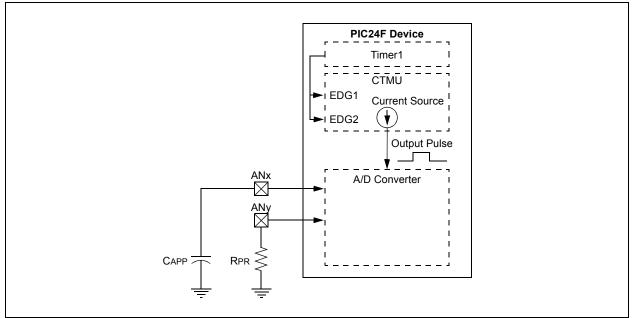

### FIGURE 25-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

#### 25.2 Measuring Time

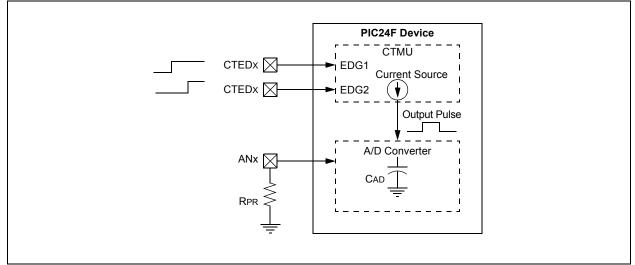

Time measurements on the pulse width can be similarly performed using the A/D module's Internal Capacitor (CAD) and a precision resistor for current calibration. Figure 25-2 displays the external connections used for time measurements, and how the CTMU and A/D modules are related in this application. This example also shows both edge events coming from the external CTEDx pins, but other configurations using internal edge sources are possible.

### FIGURE 25-2: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

#### REGISTER 25-2: CTMUCON2: CTMU CONTROL REGISTER 2 (CONTINUED)

- bit 6 EDG2POL: Edge 2 Polarity Select bit 1 = Edge 2 is programmed for a positive edge 0 = Edge 2 is programmed for a negative edge bit 5-2 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = Edge 2 source is Comparator 3 output 1110 = Edge 2 source is Comparator 2 output 1101 = Edge 2 source is Comparator 1 output 1100 = Unimplemented; do not use 1011 = Edge 2 source is IC3 1010 = Edge 2 source is IC2 1001 = Edge 2 source is IC1 1000 = Edge 2 source is CTED13<sup>(2)</sup> 0111 = Edge 2 source is CTED12<sup>(1,2)</sup> 0110 = Edge 2 source is CTED11<sup>(1,2)</sup> 0101 = Edge 2 source is CTED10 0100 = Edge 2 source is CTED9 0011 = Edge 2 source is CTED1 0010 = Edge 2 source is CTED2 0001 = Edge 2 source is OC1 0000 = Edge 2 source is Timer1

- bit 1-0 Unimplemented: Read as '0'

- Note 1: Edge sources, CTED11 and CTED12, are not available on PIC24FV32KA302 devices.

- 2: Edge sources, CTED3, CTED11, CTED12 and CTED13, are not available on PIC24FV32KA301 devices.

| R/P-1      | R/P-1                                                                                                                                                                                                                                                                   | R/P-1                                                                          | R/P-1                            | R/P-1                                  | R/P-1            | R/P-1          | R/P-1         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------|----------------------------------------|------------------|----------------|---------------|

| FWDTEN     | 1 WINDIS                                                                                                                                                                                                                                                                | FWDTEN0                                                                        | FWPSA                            | WDTPS3                                 | WDTPS2           | WDTPS1         | WDTPS0        |

| bit 7      | 4                                                                                                                                                                                                                                                                       |                                                                                |                                  |                                        |                  |                | bit           |

|            |                                                                                                                                                                                                                                                                         |                                                                                |                                  |                                        |                  |                |               |

| Legend:    |                                                                                                                                                                                                                                                                         |                                                                                |                                  |                                        |                  |                |               |

| R = Reada  | ble bit                                                                                                                                                                                                                                                                 | P = Programm                                                                   | nable bit                        | U = Unimplem                           | nented bit, read | d as '0'       |               |

| -n = Value | at POR                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                               |                                  | '0' = Bit is clea                      | ared             | x = Bit is unk | nown          |

| bit 7,5    | 11 = WDT is $\epsilon$                                                                                                                                                                                                                                                  | I>: Watchdog Tir<br>enabled in hardw<br>controlled with th                     | vare                             |                                        |                  |                |               |

|            | 01 = WDT is e<br>00 = WDT is c                                                                                                                                                                                                                                          | enabled only whi<br>disabled in hardw                                          | ile device is a<br>vare; SWDTE   | ctive; WDT is dis<br>N bit is disabled |                  | o, SWDTEN bi   | t is disabled |

| bit 6      | 1 = Standard<br>0 = Windowe                                                                                                                                                                                                                                             | dowed Watchdog<br>WDT is selected<br>d WDT is enable<br>and software (<br>eset | d; windowed V<br>ed; note that e | NDT is disabled<br>executing a CLRW    |                  |                |               |

| bit 4      | •                                                                                                                                                                                                                                                                       | F Prescaler bit<br>scaler ratio of 1:1<br>scaler ratio of 1:3                  |                                  |                                        |                  |                |               |

| bit 3-0    | WDTPS<3:0><br>1111 = 1:32,7<br>1110 = 1:16,3<br>1101 = 1:8,19<br>1000 = 1:4,09<br>1011 = 1:2,04<br>1010 = 1:1,02<br>1001 = 1:512<br>1000 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0100 = 1:64<br>0101 = 1:32<br>0100 = 1:16<br>0011 = 1:8<br>0010 = 1:4<br>0001 = 1:2 | 884<br>92<br>96<br>88<br>24                                                    | er Postscale \$                  | Select bits                            |                  |                |               |

#### REGISTER 26-10: DEVREV: DEVICE REVISION REGISTER

| U-0                               | U-0 | U-0 | U-0 | U-0                                | U-0  | U-0                | U-0    |  |  |

|-----------------------------------|-----|-----|-----|------------------------------------|------|--------------------|--------|--|--|

| —                                 | _   | —   |     | —                                  | -    | —                  | —      |  |  |

| bit 23                            |     |     |     |                                    |      |                    | bit 16 |  |  |

|                                   |     |     |     |                                    |      |                    |        |  |  |

| U-0                               | U-0 | U-0 | U-0 | U-0                                | U-0  | U-0                | U-0    |  |  |

| —                                 | _   | —   | —   | —                                  | —    | —                  | —      |  |  |

| bit 15                            |     | -   |     |                                    |      | •                  | bit 8  |  |  |

|                                   |     |     |     |                                    |      |                    |        |  |  |

| U-0                               | U-0 | U-0 | U-0 | R                                  | R    | R                  | R      |  |  |

| —                                 | —   | —   | —   | REV3                               | REV2 | REV1               | REV0   |  |  |

| bit 7                             |     | -   |     |                                    |      | •                  | bit 0  |  |  |

|                                   |     |     |     |                                    |      |                    |        |  |  |

| Legend:                           |     |     |     |                                    |      |                    |        |  |  |

| R = Readable bit W = Writable bit |     |     | oit | U = Unimplemented bit, read as '0' |      |                    |        |  |  |

| -n = Value at F                   | POR |     |     | '0' = Bit is cleared               |      | x = Bit is unknown |        |  |  |

|                                   |     |     |     |                                    |      |                    |        |  |  |

bit 23-4 Unimplemented: Read as '0'

bit 3-0 **REV<3:0>:** Minor Revision Identifier bits

#### 28.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |  |  |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |  |  |  |  |  |

|       | reference source.                          |  |  |  |  |  |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

#### TABLE 29-24: COMPARATOR TIMINGS

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Мах | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | _   | —   | 10  | μS    |          |

\* Parameters are characterized but not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 29-25: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> | _   |     | 10  | μS    |          |

**Note 1:** Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

### FIGURE 29-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

NOTES:

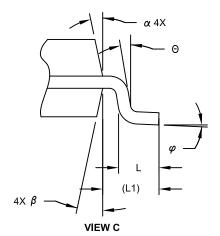

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |  |

|--------------------------|-------------|-----------|-----|------|--|--|

| Dimension Lin            | nits        | MIN       | NOM | MAX  |  |  |

| Number of Pins           | N           | 20        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |  |

| Overall Length           | D           | 12.80 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.20      | -   | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

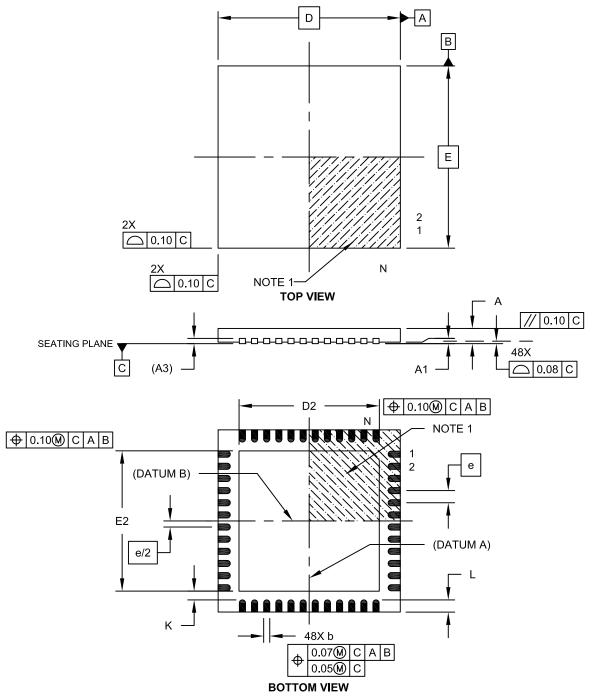

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2