#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 20-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka301t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

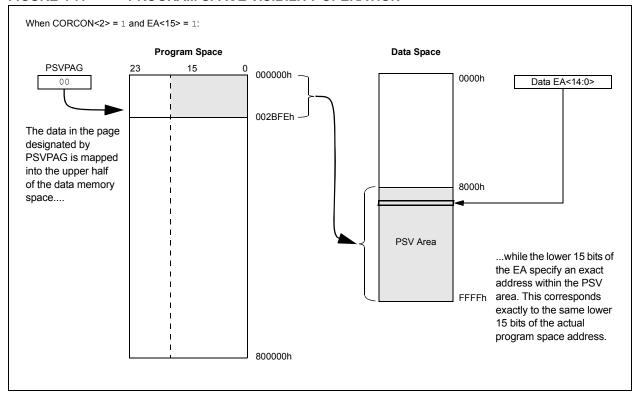

The upper 32 Kbytes of data space may optionally be mapped into a 16K word page (in PIC24FV16KA3XX devices) and a 32K word page (in PIC24FV32KA3XX devices) of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space EA is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

## 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | intended to be a comprehensive reference                                           |  |  |  |  |  |  |  |  |  |

|       | source. For more information on Flash pro-                                         |  |  |  |  |  |  |  |  |  |

|       | gramming, refer to the "PIC24F Family                                              |  |  |  |  |  |  |  |  |  |

|       | Reference Manual", Section 4. "Program                                             |  |  |  |  |  |  |  |  |  |

|       | Memory" (DS39715).                                                                 |  |  |  |  |  |  |  |  |  |

The PIC24FV32KA304 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FV32KA304 device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program mode Entry voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

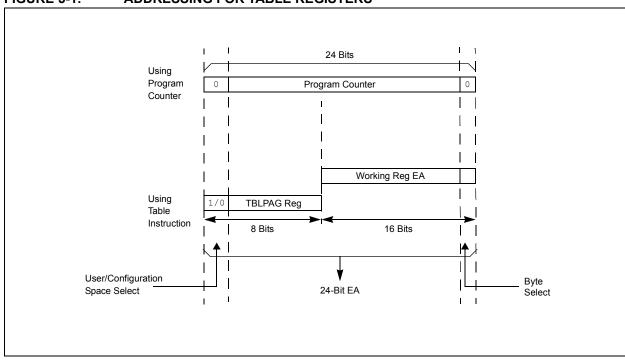

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, Flash memory programming is done with the table read and write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

## **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 5 | SWDTEN: Software Enable/Disable of WDT bit <sup>(2)</sup>                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = WDT is enabled</li><li>0 = WDT is disabled</li></ul>                                                                                       |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-up Reset has occurred<br>0 = A Power-up Reset has not occurred                                      |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTENx Configuration bit is '1' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV32KA3XX parts only; not used on PIC24F32KA3XX devices.

#### TABLE 7-1:RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                       | Clearing Event          |

|-------------------|-----------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                                 | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access   | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                        | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                          | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                   | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                        | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                           | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                            | POR                     |

| BOR (RCON<1>)     | POR, BOR                                            | —                       |

| POR (RCON<0>)     | POR                                                 | —                       |

| DPSLP (RCON<10>)  | PWRSAV #SLEEP Instruction with DSEN (DSCON<15>) Set | POR                     |

Note: All Reset flag bits may be set or cleared by the user software.

| U-0          | R/W-1                                                  | R/W-0                                 | R/W-0            | U-0               | U-0              | U-0             | U-0     |  |

|--------------|--------------------------------------------------------|---------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|

|              | NVMIP2                                                 | NVMIP1                                | NVMIP0           |                   |                  |                 |         |  |

| bit 15       |                                                        |                                       |                  |                   |                  |                 | bit     |  |

|              |                                                        |                                       |                  |                   |                  |                 |         |  |

| U-0          | R/W-1                                                  | R/W-0                                 | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |

|              | AD1IP2                                                 | AD1IP1                                | AD1IP0           | —                 | U1TXIP2          | U1TXIP1         | U1TXIP0 |  |

| bit 7        |                                                        |                                       |                  |                   |                  |                 | bit     |  |

| Legend:      |                                                        |                                       |                  |                   |                  |                 |         |  |

| R = Readal   | ble bit                                                | W = Writable                          | bit              | U = Unimplei      | mented bit, read | d as '0'        |         |  |

| -n = Value a | at POR                                                 | '1' = Bit is set                      |                  | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |  |

|              |                                                        |                                       |                  |                   |                  |                 |         |  |

| bit 15       | -                                                      | ted: Read as '                        |                  |                   |                  |                 |         |  |

| bit 14-12    |                                                        | : NVM Interrup                        |                  |                   |                  |                 |         |  |

|              | 111 = Interru                                          | pt is Priority 7 (                    | highest priority | y interrupt)      |                  |                 |         |  |

|              | •                                                      |                                       |                  |                   |                  |                 |         |  |

|              | •<br>001 = Interru                                     | pt is Priority 1                      |                  |                   |                  |                 |         |  |

|              |                                                        | pt source is dis                      | abled            |                   |                  |                 |         |  |

| bit 11-7     |                                                        | ,<br>ited: Read as '                  |                  |                   |                  |                 |         |  |

| bit 6-4      | AD1IP<2:0>:                                            | A/D Conversio                         | n Complete In    | nterrupt Priority | bits             |                 |         |  |

|              |                                                        | pt is Priority 7 (                    |                  |                   |                  |                 |         |  |

|              | •                                                      | . ,                                   | 0 1 .            | , ,               |                  |                 |         |  |

|              | •                                                      |                                       |                  |                   |                  |                 |         |  |

|              |                                                        | pt is Priority 1                      |                  |                   |                  |                 |         |  |

|              |                                                        | pt source is dis                      |                  |                   |                  |                 |         |  |

| bit 3        | Unimplemen                                             | ted: Read as '                        | 0'               |                   |                  |                 |         |  |

|              | U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits |                                       |                  |                   |                  |                 |         |  |

| bit 2-0      |                                                        |                                       |                  | (intermed)        |                  |                 |         |  |

| bit 2-0      | 111 = Interru                                          | pt is Priority 7 (                    | highest priority | y interrupt)      |                  |                 |         |  |

| bit 2-0      | 111 = Interru<br>•                                     | pt is Priority 7(                     | highest priority | y interrupt)      |                  |                 |         |  |

| bit 2-0      |                                                        | pt is Priority 7(<br>pt is Priority 1 | highest priority | y interrupt)      |                  |                 |         |  |

#### REGISTER 8-20: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

#### REGISTER 8-32: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0      | U-0      | U-0      |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | —   | —        | —        | —        |

| bit 15 |     |     |     |     |          |          | bit 8    |

|        |     |     |     |     |          |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

| —      | —   | —   | —   | —   | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 |

| bit 7  |     |     |     |     |          | •        | bit 0    |

|        |     |     |     |     |          |          |          |

## Legend:

| Logona.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

bit 6-4 ULPWUIP<2:0>: Ultra Low-Power Wake-up Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- :

• 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

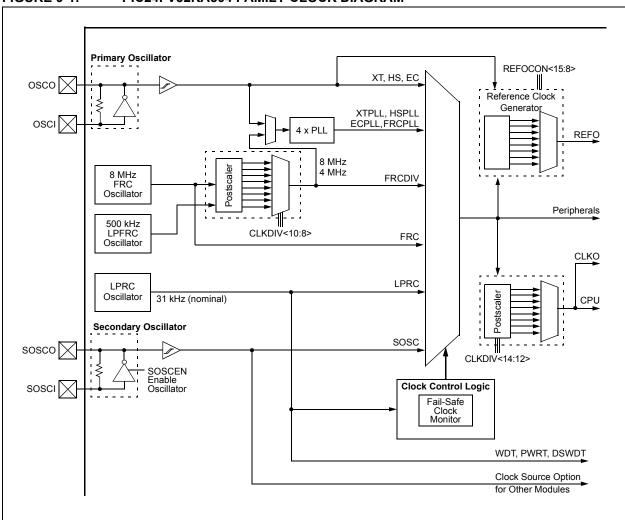

## 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Oscillator Configuration, refer to the "PIC24F Family Reference Manual", Section 38. "Oscillator with 500 kHz Low-Power FRC" (DS39726).

The oscillator system for the PIC24FV32KA304 family of devices has the following features:

- A total of five external and internal oscillator options as clock sources, providing 11 different clock modes.

- On-chip 4x Phase Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources.

- Software-controllable switching between various clock sources.

- Software-controllable postscaler for selective clocking of CPU for system power savings.

- System frequency range declaration bits for EC mode. When using an external clock source, the current consumption is reduced by setting the declaration bits to the expected frequency range.

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown.

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24FV32KA304 FAMILY CLOCK DIAGRAM

### 10.4 Voltage Regulator-Based Power-Saving Features

The PIC24FV32KA304 series devices have a Voltage Regulator that has the ability to alter functionality to provide power savings. The on-board regulator is made up of two basic modules: the Voltage Regulator (VREG) and the Retention Regulator (RETREG). With the combination of VREG and RETREG, the following power modes are available:

#### 10.4.1 RUN MODE

In Run mode, the main VREG is providing a regulated voltage with enough current to supply a device running at full speed, and the device is not in Sleep or Deep Sleep Mode. The Retention Regulator may or may not be running, but is unused.

#### 10.4.2 SLEEP (STANDBY) MODE

In Sleep mode, the device is in Sleep and the main VREG is providing a regulated voltage at a reduced (standby) supply current. This mode provides for limited functionality due to the reduced supply current. It requires a longer time to wake-up from Sleep.

#### 10.4.3 RETENTION SLEEP MODE

In Retention Sleep mode, the device is in Sleep and all regulated voltage is provided solely by the Retention Regulator. Consequently, this mode has lower power consumption than regular Sleep mode, but is also limited in terms of how much functionality can be enabled. Retention Sleep wake-up time is longer than Sleep mode due to the extra time required to raise the VCORE supply rail back to normal regulated levels.

Note: PIC24F32KA30X family devices do not use an On-Chip Voltage Regulator, so they do not support Retention Sleep mode.

#### 10.4.4 DEEP SLEEP MODE

In Deep Sleep mode, both the main Voltage Regulator and Retention Regulator are shut down, providing the lowest possible device power consumption. However, this mode provides no retention or functionality of the device and has the longest wake-up time.

|                         | FAMILY DE              | VICES                  |                            |                                                                                    |

|-------------------------|------------------------|------------------------|----------------------------|------------------------------------------------------------------------------------|

| RETCGF Bit<br>(FPOR<2>) | RETEN Bit<br>(RCON<12> | PMSLP Bit<br>(RCON<8>) | Power Mode<br>During Sleep | Description                                                                        |

| 0                       | 0                      | 1                      | Sleep                      | VREG mode (normal) is unchanged during Sleep.<br>RETREG is unused.                 |

| 0                       | 0                      | 0                      | Sleep<br>(Standby)         | VREG goes to Low-Power Standby mode during Sleep. RETREG is unused.                |

| 0                       | 1                      | 0                      | Retention<br>Sleep         | VREG is off during Sleep. RETREG is enabled and provides Sleep voltage regulation. |

| 1                       | х                      | 1                      | Sleep                      | VREG mode (normal) is unchanged during Sleep.<br>RETREG is disabled at all times.  |

| 1                       | Х                      | 0                      | Sleep<br>(Standby)         | VREG goes to Low-Power Standby mode during Sleep. RETREG is disabled at all times  |

## TABLE 10-1:VOLTAGE REGULATION CONFIGURATION SETTINGS FOR PIC24FV32KA304<br/>FAMILY DEVICES

| R/W-0         | U-0                                              | R/W-0                            | U-0            | U-0                                  | U-0              | U-0              | U-0 |  |  |

|---------------|--------------------------------------------------|----------------------------------|----------------|--------------------------------------|------------------|------------------|-----|--|--|

| TON           | _                                                | TSIDL                            |                |                                      |                  | _                | _   |  |  |

| bit 15        |                                                  | 1                                |                |                                      |                  |                  | bit |  |  |

|               |                                                  |                                  |                |                                      |                  |                  |     |  |  |

| U-0           | R/W-0                                            | R/W-0                            | R/W-0          | R/W-0                                | U-0              | R/W-0            | U-0 |  |  |

|               | TGATE                                            | TCKPS1                           | TCKPS0         | T32 <sup>(1)</sup>                   | _                | TCS              | —   |  |  |

| bit 7         |                                                  |                                  |                |                                      |                  |                  | bit |  |  |

| Legend:       |                                                  |                                  |                |                                      |                  |                  |     |  |  |

| R = Readable  | e bit                                            | W = Writable                     | bit            | U = Unimplen                         | nented bit, read | d as '0'         |     |  |  |

| -n = Value at | POR                                              | '1' = Bit is set                 |                | '0' = Bit is clea                    | ared             | x = Bit is unkno | own |  |  |

| bit 15        | TON: Timerx                                      | On hit                           |                |                                      |                  |                  |     |  |  |

|               | When TxCON                                       |                                  |                |                                      |                  |                  |     |  |  |

|               | 1 = Starts 32                                    | -bit Timerx/y                    |                |                                      |                  |                  |     |  |  |

|               | 0 = Stops 32                                     | -                                |                |                                      |                  |                  |     |  |  |

|               | <u>When TxCON</u><br>1 = Starts 16               |                                  |                |                                      |                  |                  |     |  |  |

|               | 0 = Stops 16                                     |                                  |                |                                      |                  |                  |     |  |  |

| bit 14        | Unimplemen                                       | ted: Read as '                   | 0'             |                                      |                  |                  |     |  |  |

| bit 13        | TSIDL: Timerx Stop in Idle Mode bit              |                                  |                |                                      |                  |                  |     |  |  |

|               |                                                  | ues module op<br>s module opera  |                | evice enters Id<br>de                | le mode          |                  |     |  |  |

| bit 12-7      | Unimplemen                                       | ted: Read as '                   | 0'             |                                      |                  |                  |     |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit |                                  |                |                                      |                  |                  |     |  |  |

|               | When TCS =                                       |                                  |                |                                      |                  |                  |     |  |  |

|               | This bit is igno<br>When TCS =                   |                                  |                |                                      |                  |                  |     |  |  |

|               |                                                  | <u>o.</u><br>ne accumulatio      | n is enabled   |                                      |                  |                  |     |  |  |

|               | 0 = Gated tin                                    | ne accumulatio                   | n is disabled  |                                      |                  |                  |     |  |  |

| bit 5-4       | TCKPS<1:0>                                       | : Timerx Input                   | Clock Prescale | e Select bits                        |                  |                  |     |  |  |

|               | 11 = 1:256                                       |                                  |                |                                      |                  |                  |     |  |  |

|               | 10 = 1:64<br>01 = 1:8                            |                                  |                |                                      |                  |                  |     |  |  |

|               | 00 = 1:1                                         |                                  |                |                                      |                  |                  |     |  |  |

| bit 3         |                                                  | mer Mode Sele                    |                |                                      |                  |                  |     |  |  |

|               |                                                  |                                  |                | er5 form a singl<br>er5 act as two 1 |                  |                  |     |  |  |

| bit 2         | Unimplemen                                       | ted: Read as '                   | 0'             |                                      |                  |                  |     |  |  |

| bit 1         | TCS: Timerx                                      | Clock Source S                   | Select bit     |                                      |                  |                  |     |  |  |

|               |                                                  | clock from pin<br>clock (Fosc/2) | , TxCK (on the | rising edge)                         |                  |                  |     |  |  |

|               |                                                  |                                  | 0'             |                                      |                  |                  |     |  |  |

| bit 0         | Unimplemen                                       | ted: Read as '                   | 0              |                                      |                  |                  |     |  |  |

## 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even numbered module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bit (ICxCON2<8>) for both modules.

## 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. If Synchronous mode is to be used, disable the Sync source before proceeding.

- 2. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 3. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired Sync/trigger source.

- Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSELx bits before the input capture module is enabled, for proper synchronization with the desired clock source.

- 5. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- 6. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 7. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 8. Enable the selected Sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same Sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bit settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the Sync source as the last step. Both input capture modules are held in Reset until the Sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the Sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

## 15.4 Subcycle Resolution

The DCBx bits (OCxCON2<10:9>) provide for resolution better than one instruction cycle. When used, they delay the falling edge generated from a match event by a portion of an instruction cycle.

For example, setting DCB<1:0> = 10 causes the falling edge to occur halfway through the instruction cycle in which the match event occurs, instead of at the beginning. These bits cannot be used when OCM<2:0> = 001. When operating the module in PWM mode (OCM<2:0> = 110 or 111), the DCBx bits will be double-buffered. The DCBx bits are intended for use with a clock source identical to the system clock. When an OCx module with enabled prescaler is used, the falling edge delay caused by the DCBx bits will be referenced to the system clock period, rather than the OCx module's period.

| TABLE 15-1: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz) <sup>(1)</sup> |

|-------------|--------------------------------------------------------------------------------|

|-------------|--------------------------------------------------------------------------------|

| PWM Frequency     | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-------------------|--------|-------|--------|--------|---------|----------|---------|

| Prescaler Ratio   | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Value      | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits) | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

| TADLE 13-2. EXAMPLE PWW FREQUENCIES AND RESULUTIONS AT 10 MIPS (FCY = 10 MID) | TABLE 15-2: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz) <sup>(1)</sup> |

|-------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|

| PWM Frequency     | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-------------------|---------|--------|--------|---------|----------|---------|---------|

| Prescaler Ratio   | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Value      | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits) | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

## REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                 |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                          |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                         |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                     |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                    |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                               |

|       | 1 = Receive buffer has overflowed                                                                                                                                             |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the RSR to the empty state)    |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                    |

|       | <ul> <li>1 = Receive buffer has data; at least one more characters can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                |

© 2011-2013 Microchip Technology Inc.

#### REGISTER 18-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x                                | U-x  | U-x  | U-x                                | U-x                                     | U-x  | U-x  | W-x   |  |

|------------------------------------|------|------|------------------------------------|-----------------------------------------|------|------|-------|--|

| —                                  | _    | —    | —                                  |                                         |      | —    | UTX8  |  |

| bit 15                             |      |      |                                    | •                                       |      |      | bit 8 |  |

| W-x                                | W-x  | W-x  | W-x                                | W-x                                     | W-x  | W-x  | W-x   |  |

| UTX7                               | UTX6 | UTX5 | UTX4                               | UTX3                                    | UTX2 | UTX1 | UTX0  |  |

| bit 7                              |      |      |                                    |                                         |      |      | bit 0 |  |

| •                                  |      |      |                                    |                                         |      |      |       |  |

| Legend:                            |      |      |                                    |                                         |      |      |       |  |

| R = Readable bit W = Writable bit  |      |      | U = Unimplemented bit, read as '0' |                                         |      |      |       |  |

| -n = Value at POR '1' = Bit is set |      |      |                                    | '0' = Bit is cleared x = Bit is unknown |      |      |       |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 UTX8: UARTx Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: UARTx Data of the Transmitted Character bits

#### **REGISTER 18-4: UXRXREG: UARTX RECEIVE REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|----------|

|        | —   | —   | —   | —   | —   | —   | URX8     |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R-0, HSC |

|----------|----------|----------|----------|----------|----------|----------|----------|

| URX7     | URX6     | URX5     | URX4     | URX3     | URX2     | URX1     | URX0     |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: UARTx Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: UARTx Data of the Received Character bits

## REGISTER 19-11: RTCCSWT: CONTROL/SAMPLE WINDOW TIMER REGISTER<sup>(1)</sup>

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSAMP7 | PWCSAMP6 | PWCSAMP5 | PWCSAMP4 | PWCSAMP3 | PWCSAMP2 | PWCSAMP1 | PWCSAMP0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | PWCSTAB<7:0>: PWM Stability Window Timer bits<br>11111111 = Stability window is 255 TPWCCLK clock periods                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 00000000 = Stability window is 0 TPWCCLK clock periods<br>The sample window starts when the alarm event triggers. The stability window timer starts counting<br>from every alarm event when PWCEN = 1.                               |

| bit 7-0  | <pre>PWCSAMP&lt;7:0&gt;: PWM Sample Window Timer bits 1111111 = Sample window is always enabled, even when PWCEN = 0 11111110 = Sample window is 254 TPWCCLK clock periods 00000000 = Sample window is 0 TPWCCLK clock periods</pre> |

|          | The sample window timer starts counting at the end of the stability window when PWCEN = 1. If PWCSTAB<7:0> = $00000000$ , the sample window timer starts counting from every alarm event when PWCEN = 1.                             |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### 26.4 Deep Sleep Watchdog Timer (DSWDT)

In PIC24FV32KA304 family devices, in addition to the WDT module, a DSWDT module is present which runs while the device is in Deep Sleep, if enabled. It is driven by either the SOSC or LPRC oscillator. The clock source is selected by the Configuration bit, DSWDTOSC (FDS<4>).

The DSWDT can be configured to generate a time-out, at 2.1 ms to 25.7 days, by selecting the respective postscaler. The postscaler can be selected by the Configuration bits, DSWDTPS<3:0> (FDS<3:0>). When the DSWDT is enabled, the clock source is also enabled.

DSWDT is one of the sources that can wake-up the device from Deep Sleep mode.

## 26.5 Program Verification and Code Protection

For all devices in the PIC24FV32KA304 family, code protection for the boot segment is controlled by the Configuration bit, BSS0, and the general segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the boot segment and bit, GWRP, for the general segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

## 26.6 In-Circuit Serial Programming

PIC24FV32KA304 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 26.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

## 27.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 27.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 27.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 27.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| AC CHARACTERISTICS |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                    |     |       |                                                            |  |

|--------------------|-------|------------------------------------------------------|-----|--------------------|-----|-------|------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic <sup>(1)</sup>                        | Min | Тур <sup>(2)</sup> | Max | Units | Conditions                                                 |  |

| OS50               | Fplli | PLL Input Frequency<br>Range                         | 4   | —                  | 8   | MHz   | ECPLL, HSPLL modes, $-40^{\circ}C \le TA \le +85^{\circ}C$ |  |

| OS51               | Fsys  | PLL Output Frequency<br>Range                        | 16  | —                  | 32  | MHz   | $-40^{\circ}C \le TA \le +85^{\circ}C$                     |  |

| OS52               | TLOCK | PLL Start-up Time<br>(Lock Time)                     | _   | 1                  | 2   | ms    |                                                            |  |

| OS53               | DCLK  | CLKO Stability (Jitter)                              | -2  | 1                  | 2   | %     | Measured over a 100 ms<br>period                           |  |

## TABLE 29-20: PLL CLOCK TIMING SPECIFICATIONS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 29-21: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICS |                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                        |                                                                                                                                                                        |  |  |  |

|--------------------|----------------------------------------------|------------------------------------------------------|-----|-----|-------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Characteristic                               | Min                                                  | Тур | Max | Units | c                                      | onditions                                                                                                                                                              |  |  |  |

| F20                | Internal FRC Accuracy @ 8 MHz <sup>(1)</sup> |                                                      |     |     |       |                                        |                                                                                                                                                                        |  |  |  |

|                    | FRC                                          | -2                                                   | _   | +2  | %     | +25°C                                  | $\begin{array}{l} 3.0V \leq V\text{DD} \leq 3.6\text{V}, \mbox{ F device} \\ 3.2V \leq V\text{DD} \leq 5.5\text{V}, \mbox{ FV device} \end{array}$                     |  |  |  |

|                    |                                              | -5                                                   | —   | +5  | %     | $-40^{\circ}C \le TA \le +85^{\circ}C$ | $\begin{array}{l} 1.8V \leq V\text{DD} \leq 3.6\text{V}, \ \text{F} \ \text{device} \\ 2.0V \leq V\text{DD} \leq 5.5\text{V}, \ \text{FV} \ \text{device} \end{array}$ |  |  |  |

|                    | LPRC @ 31 kHz <sup>(2)</sup>                 | •                                                    | •   | •   | •     |                                        |                                                                                                                                                                        |  |  |  |

| F21                |                                              | -15                                                  | _   | 15  | %     |                                        |                                                                                                                                                                        |  |  |  |

**Note 1:** Frequency is calibrated at +25°C and 3.3V. The OSCTUN bits can be used to compensate for temperature drift.

2: The change of LPRC frequency as VDD changes.

### TABLE 29-22: INTERNAL RC OSCILLATOR SPECIFICATIONS

|              |       |                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |            |  |  |

|--------------|-------|-------------------------------|------------------------------------------------------|-----|-----|-------|------------|--|--|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup> | Min                                                  | Тур | Мах | Units | Conditions |  |  |

|              | TFRC  | FRC Start-up Time             | —                                                    | 5   | _   | μS    |            |  |  |

|              | TLPRC | LPRC Start-up Time            | —                                                    | 70  | —   | μS    |            |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

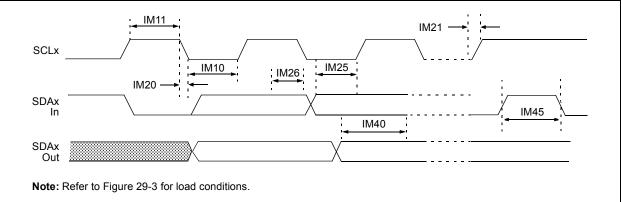

### TABLE 29-32: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |         |                               |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |                        |  |

|--------------------|---------|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|

| Param<br>No.       | Symbol  | Characteristic                |                           | Min <sup>(1)</sup>                                                                                                                                                                                                                                                                | Мах  | Units | Conditions             |  |

| IM10               | TLO:SCL | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                   | _    | μs    |                        |  |

|                    |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                   | _    | μS    |                        |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                   |      | μS    |                        |  |

| IM11               | THI:SCL | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                   |      | μS    |                        |  |

|                    |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                   |      | μS    |                        |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                   |      | μS    |                        |  |

| IM20               | TF:SCL  | SDAx and SCLx<br>Fall Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                 | 300  | ns    | CB is specified to be  |  |

|                    |         |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | from 10 to 400 pF      |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                 | 100  | ns    |                        |  |

| IM21               | TR:SCL  | SDAx and SCLx<br>Rise Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                 | 1000 | ns    | CB is specified to be  |  |

|                    |         |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | from 10 to 400 pF      |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                 | 300  | ns    |                        |  |

| IM25               | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                                                                                                                                               | _    | ns    |                        |  |

|                    |         |                               | 400 kHz mode              | 100                                                                                                                                                                                                                                                                               | _    | ns    |                        |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | 100                                                                                                                                                                                                                                                                               | _    | ns    |                        |  |

| IM26               | Thd:dat | D:DAT Data Input<br>Hold Time | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                 | _    | ns    |                        |  |

|                    |         |                               | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                 | 0.9  | μS    |                        |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | 0                                                                                                                                                                                                                                                                                 | _    | ns    |                        |  |

| IM40               | TAA:SCL | Output Valid<br>from Clock    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                 | 3500 | ns    |                        |  |

|                    |         |                               | 400 kHz mode              | —                                                                                                                                                                                                                                                                                 | 1000 | ns    |                        |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                 |      | ns    |                        |  |

| IM45               | TBF:SDA |                               | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                               |      | μs    | Time the bus must be   |  |

|                    |         |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                               | _    | μS    | free before a new      |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                               | —    | μS    | transmission can start |  |

| IM50               | Св      | Bus Capacitive Lo             | bading                    | —                                                                                                                                                                                                                                                                                 | 400  | pF    |                        |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to **Section 17.3 "Setting Baud Rate When Operating as a Bus Master**" for details.

2: Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

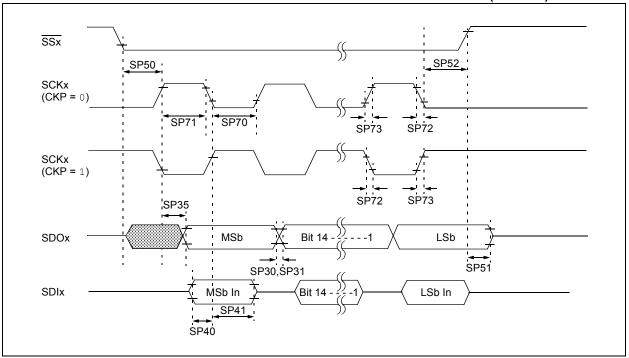

#### FIGURE 29-20: SPIX MODULE SLAVE MODE TIMING CHARACTERISTICS (CKE = 0)

#### TABLE 29-38: SPIX MODULE SLAVE MODE TIMING REQUIREMENTS (CKE = 0)

| AC CHARACTERISTICS |                       |                                                                                 | $\label{eq:conditions: 2.0V to 3.6V} Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated) \\ Operating temperature & -40^\circ C \leq T_A \leq +85^\circ C \text{ for Industrial} \\ -40^\circ C \leq T_A \leq +125^\circ C \text{ for Extended} \end{cases}$ |                    |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic                                                                  | Min                                                                                                                                                                                                                                                                            | Typ <sup>(1)</sup> | Max | Units | Conditions |  |

| SP70               | TscL                  | SCKx Input Low Time                                                             | 30                                                                                                                                                                                                                                                                             |                    | _   | ns    |            |  |

| SP71               | TscH                  | SCKx Input High Time                                                            | 30                                                                                                                                                                                                                                                                             | _                  | _   | ns    |            |  |

| SP72               | TscF                  | SCKx Input Fall Time <sup>(2)</sup>                                             |                                                                                                                                                                                                                                                                                | 10                 | 25  | ns    |            |  |

| SP73               | TscR                  | SCKx Input Rise Time <sup>(2)</sup>                                             |                                                                                                                                                                                                                                                                                | 10                 | 25  | ns    |            |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(2)</sup>                                       |                                                                                                                                                                                                                                                                                | 10                 | 25  | ns    |            |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(2)</sup>                                       |                                                                                                                                                                                                                                                                                | 10                 | 25  | ns    |            |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                       | —                                                                                                                                                                                                                                                                              | —                  | 30  | ns    |            |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input<br>to SCKx Edge                                   | 20                                                                                                                                                                                                                                                                             | —                  | _   | ns    |            |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                                    | 20                                                                                                                                                                                                                                                                             | _                  | _   | ns    |            |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx to SCKx ↑ or SCKx Input                                                     | 120                                                                                                                                                                                                                                                                            | —                  | _   | ns    |            |  |

| SP51               | TssH2doZ              | $\overline{\text{SSx}}$ $\uparrow$ to SDOx Output High-Impedance <sup>(3)</sup> | 10                                                                                                                                                                                                                                                                             | —                  | 50  | ns    |            |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                             | 1.5 Tcy + 40                                                                                                                                                                                                                                                                   | —                  | —   | ns    |            |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.