Welcome to E-XFL.COM

Microchip Technology - PIC24FV16KA301T-I/SS Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

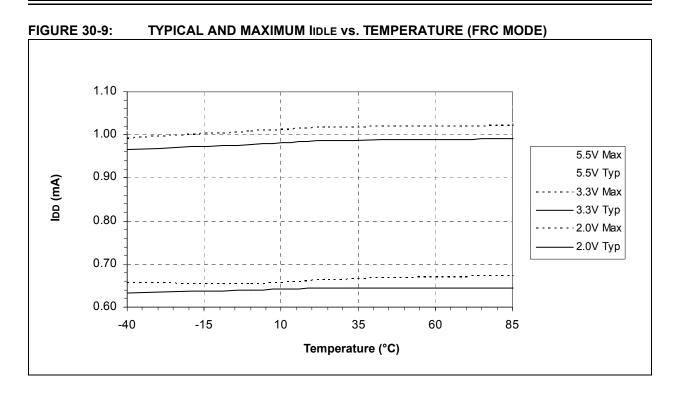

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 20-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka301t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                             |  |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|--|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |                                             |  |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |  |

| CN23     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs                  |  |

| CN24     |                                  | 15                                | 12            | 42                     | 46             | -                                | 15                                | 12            | 42                     | 46             | 1   | ST     |                                             |  |

| CN25     |                                  | _                                 | _             | 37                     | 40             | -                                |                                   |               | 37                     | 40             | 1   | ST     |                                             |  |

| CN26     |                                  | _                                 | _             | 38                     | 41             |                                  |                                   |               | 38                     | 41             | I   | ST     |                                             |  |

| CN27     |                                  | 14                                | 11            | 41                     | 45             |                                  | 14                                | 11            | 41                     | 45             | I   | ST     |                                             |  |

| CN28     |                                  | _                                 | _             | 36                     | 39             |                                  |                                   |               | 36                     | 39             | I   | ST     |                                             |  |

| CN29     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ST     |                                             |  |

| CN30     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ST     |                                             |  |

| CN31     |                                  | _                                 | _             | 26                     | 28             | —                                | _                                 | —             | 26                     | 28             | I   | ST     |                                             |  |

| CN32     |                                  | _                                 | —             | 25                     | 27             | —                                | —                                 | —             | 25                     | 27             | 1   | ST     |                                             |  |

| CN33     |                                  | _                                 | —             | 32                     | 35             | —                                | —                                 | —             | 32                     | 35             | 1   | ST     |                                             |  |

| CN34     |                                  | _                                 | —             | 35                     | 38             | —                                | —                                 | —             | 35                     | 38             | I   | ST     |                                             |  |

| CN35     |                                  | _                                 | _             | 12                     | 13             | —                                | _                                 | —             | 12                     | 13             | I   | ST     |                                             |  |

| CN36     |                                  | _                                 | _             | 13                     | 14             | —                                | _                                 | —             | 13                     | 14             | I   | ST     |                                             |  |

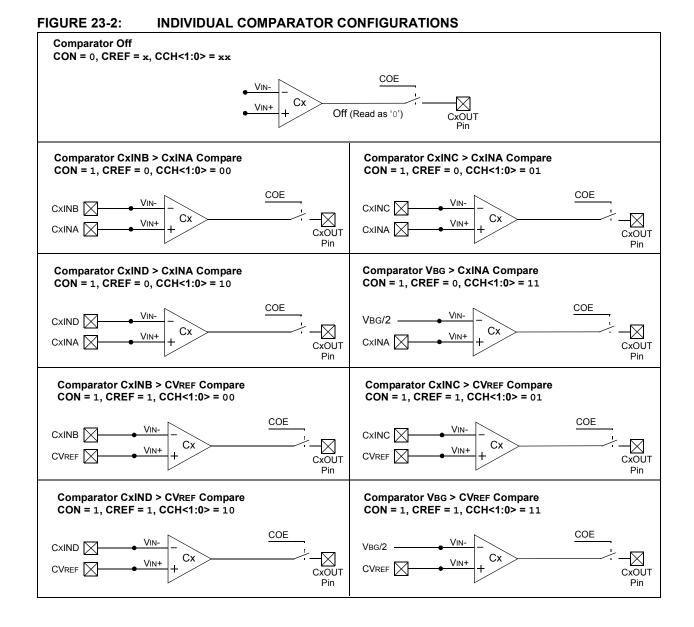

| CVREF    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator Voltage Reference Output         |  |

| CVREF+   | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA    | Comparator Reference Positive Input Voltage |  |

| CVREF-   | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA    | Comparator Reference Negative Input Voltage |  |

| CTCMP    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input                       |  |

| CTED1    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 2                                 | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |  |

| CTED2    | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     |                                             |  |

| CTED3    | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I   | ST     |                                             |  |

| CTED4    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 1   | ST     |                                             |  |

| CTED5    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ST     |                                             |  |

| CTED6    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     |                                             |  |

| CTED7    | _                                | _                                 | _             | 5                      | 5              | _                                | —                                 | _             | 5                      | 5              | I   | ST     |                                             |  |

| CTED8    | _                                | _                                 | —             | 13                     | 14             | —                                | —                                 | —             | 13                     | 14             | I   | ST     |                                             |  |

| CTED9    | _                                | 22                                | 19            | 9                      | 10             | —                                | 22                                | 19            | 9                      | 10             | I   | ST     |                                             |  |

| CTED10   | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I   | ST     | ]                                           |  |

| CTED11   | _                                | 21                                | 18            | 8                      | 9              | —                                | 21                                | 18            | 8                      | 9              | I   | ST     | ]                                           |  |

| CTED12   | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | ]                                           |  |

| CTED13   | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | 1   | ST     | 1                                           |  |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   |     |     | IPL3 <sup>(1)</sup> | PSV   | —   | _     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/0 | Clearable bit              |                    |

|-------------------|---------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in data space                                                                                    |

|          | 0 = Program space is not visible in data space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

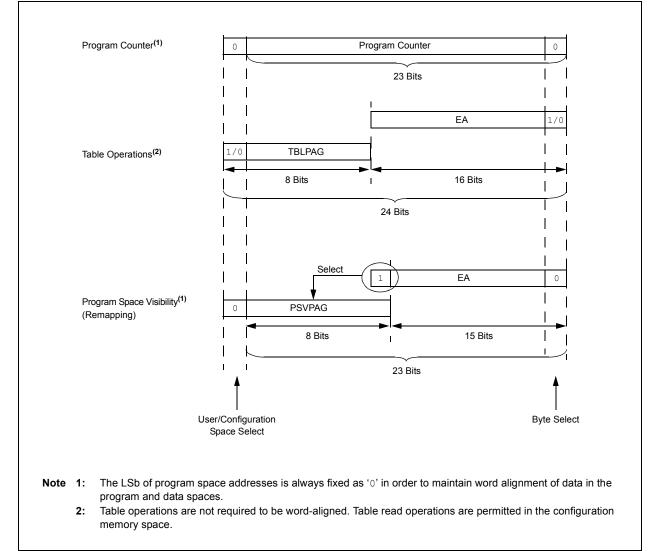

|                                       | Access        | Program Space Address |                              |                      |                         |     |  |  |  |

|---------------------------------------|---------------|-----------------------|------------------------------|----------------------|-------------------------|-----|--|--|--|

| Access Type                           | Space         | <23>                  | <22:16>                      | <15>                 | <14:1>                  | <0> |  |  |  |

| Instruction Access                    | User          | 0                     |                              | PC<22:1>             |                         |     |  |  |  |

| (Code Execution)                      |               |                       | 0xx xxxx xxxx xxxx xxxx xxx0 |                      |                         |     |  |  |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TBL                   | _PAG<7:0>                    | Data EA<15:0>        |                         |     |  |  |  |

|                                       |               | 0 x                   | XXX XXXX                     | XXXX XXXX XXXX XXXX  |                         |     |  |  |  |

|                                       | Configuration | TBL                   | TBLPAG<7:0>                  |                      | Data EA<15:0>           |     |  |  |  |

|                                       |               | 1x                    | XXX XXXX                     | XXXX XXXX XXXX XXXX  |                         |     |  |  |  |

| Program Space Visibility              | User          | 0                     | 0 PSVPAG<7:                  |                      | 7:0>(2) Data EA<14:0>(1 |     |  |  |  |

| (Block Remap/Read)                    |               | 0                     | XXXX XX                      | XX XXX XXXX XXXX XXX |                         |     |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) in the PIC24FV32KA304 family.

|               |                                                                                            |                                                                                |                                         | AT CONTRO        |                |                |                |

|---------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------|------------------|----------------|----------------|----------------|

| R/S-0, HC     | R/W-0                                                                                      | R/W-0                                                                          | R/W-0                                   | U-0              | U-0            | U-0            | U-0            |

| WR            | WREN                                                                                       | WRERR                                                                          | PGMONLY                                 |                  | _              | —              | _              |

| bit 15        |                                                                                            |                                                                                |                                         |                  |                |                | bit 8          |

|               | Dates                                                                                      | <b>D</b> # 44 0                                                                | <b>D</b> 444 0                          | <b>D</b> 444 0   | DAMA           | <b>D</b> 444 0 | <b>D</b> 444 0 |

| U-0           | R/W-0                                                                                      | R/W-0                                                                          | R/W-0                                   | R/W-0            | R/W-0          | R/W-0          | R/W-0          |

|               | ERASE                                                                                      | NVMOP5                                                                         | NVMOP4                                  | NVMOP3           | NVMOP2         | NVMOP1         | NVMOP0         |

| bit 7         |                                                                                            |                                                                                |                                         |                  |                |                | bit 0          |

| Legend:       |                                                                                            | HC = Hardware                                                                  | Clearable bit                           | U = Unimple      | mented bit, re | ead as '0'     |                |

| R = Readable  | e bit                                                                                      | W = Writable bit                                                               |                                         | S = Settable     |                |                |                |

| -n = Value at | POR                                                                                        | '1' = Bit is set                                                               |                                         | '0' = Bit is cle | eared          | x = Bit is unk | nown           |

| bit 15        | 1 = Initiates a<br>0 = Write cyc                                                           | ntrol bit (program<br>data EEPROM e<br>le is complete (cle                     | erase or write cyce<br>eared automatica |                  |                | red in softwar | e)             |

| bit 14        | 1 = Enables a                                                                              | Enable bit (erase<br>n erase or progra<br>ion allowed (device                  | m operation                             | on completion    | of the write/e | erase operatio | n)             |

| bit 13        | 1 = A write on operation                                                                   | e Flash Error Flag<br>operation is prem<br>)<br>operation comple               | aturely terminat                        |                  | R or WDT F     | Reset during   | programming    |

| bit 12        | 1 = Write ope<br>0 = Automatie                                                             | rogram Only Ena<br>eration is executed<br>c erase-before-wr<br>ns are preceded | l without erasing<br>ite                |                  | . ,            | ess(es).       |                |

| bit 11-7      | Unimplement                                                                                | ted: Read as '0'                                                               |                                         |                  |                |                |                |

| bit 6         | <b>ERASE:</b> Erase Operation Select bit<br>1 = Performs an erase operation when WR is set |                                                                                |                                         |                  |                |                |                |

|               |                                                                                            | a write operation                                                              |                                         |                  |                |                |                |

| bit 5-0       | Erase Operati<br>011010 = Era<br>011001 = Era<br>011000 = Era<br>0100xx = Era              | ases 4 words<br>ases 1 word<br>ases entire data E<br><u>Operations (when</u>   | E bit is '1'):<br>EPROM                 |                  |                |                |                |

### REGISTER 6-1: NVMCON: NONVOLATILE MEMORY CONTROL REGISTER

### 6.4.3 READING THE DATA EEPROM

To read a word from data EEPROM, the table read instruction is used. Since the EEPROM array is only 16 bits wide, only the TBLRDL instruction is needed. The read operation is performed by loading TBLPAG and WREG with the address of the EEPROM location, followed by a TBLRDL instruction.

A typical read sequence, using the Table Pointer management (builtin\_tblpage and builtin\_tbloffset) and table read procedures (builtin\_tblrdl) from the C30 compiler library, is provided in Example 6-5.

Program Space Visibility (PSV) can also be used to read locations in the data EEPROM.

### EXAMPLE 6-5: READING THE DATA EEPROM USING THE TBLRD COMMAND

```

int attribute ((space(eedata))) eeData = 0x1234;

// Data read from EEPROM

int data;

/*_____

_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the read

_____

*/

unsigned int offset;

\ensuremath{//} Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData);

// Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

data = __builtin_tblrdl(offset);

// Initizlize lower word of address

// Write EEPROM data to write latch

```

# **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 5 | SWDTEN: Software Enable/Disable of WDT bit <sup>(2)</sup>                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = WDT is enabled</li><li>0 = WDT is disabled</li></ul>                                                                                       |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-up Reset has occurred<br>0 = A Power-up Reset has not occurred                                      |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTENx Configuration bit is '1' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV32KA3XX parts only; not used on PIC24F32KA3XX devices.

### TABLE 7-1:RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                       | Clearing Event          |

|-------------------|-----------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                                 | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access   | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                        | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                          | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                   | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                        | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                           | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                            | POR                     |

| BOR (RCON<1>)     | POR, BOR                                            | —                       |

| POR (RCON<0>)     | POR                                                 | —                       |

| DPSLP (RCON<10>)  | PWRSAV #SLEEP Instruction with DSEN (DSCON<15>) Set | POR                     |

Note: All Reset flag bits may be set or cleared by the user software.

#### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE Reset - GOTO Instruction 000000h Reset - GOTO Address 000002h Reserved 000004h Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000014h Interrupt Vector 1 \_ Interrupt Vector 52 00007Ch Interrupt Vector Table (IVT)<sup>(1)</sup> Decreasing Natural Order Priority Interrupt Vector 53 00007Eh Interrupt Vector 54 000080h \_ Interrupt Vector 116 0000FCh Interrupt Vector 117 0000FEh Reserved 000100h Reserved 000102h Reserved Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000114h Interrupt Vector 1 Alternate Interrupt Vector Table (AIVT)<sup>(1)</sup> 00017Ch Interrupt Vector 52 00017Eh Interrupt Vector 53 Interrupt Vector 54 000180h \_\_\_\_\_ Interrupt Vector 116 Interrupt Vector 117 0001FEh Start of Code 000200h

Note 1: See Table 8-2 for the interrupt vector list.

### 8.3 Interrupt Control and Status Registers

The PIC24FV32KA304 family of devices implements a total of 23 registers for the interrupt controller:

- INTCON1

- INTCON2

- · IFS0, IFS1, IFS3 and IFS4

- · IEC0, IEC1, IEC3 and IEC4

- IPC0 through IPC5, IPC7 and IPC15 through IPC19

- INTTREG

Global Interrupt Enable (GIE) control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIVT.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. The INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits are in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user may change the current CPU Interrupt Priority Level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All Interrupt registers are described in Register 8-1 through Register 8-33, in the following sections.

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

|                                           |

# 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FV32KA304 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This output compare module<sup>(1)</sup>

- 11110 = **Reserved** 11101 = Reserved 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 100xx = Reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1

- 01010 = Input Capture 5<sup>(2)</sup>

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Output Compare 5<sup>(1)</sup>

- 00100 = Output Compare 4<sup>(1)</sup>

- 00011 = Output Compare 3<sup>(1)</sup>

- 00010 = Output Compare 2<sup>(1)</sup>

- 00001 = Output Compare 1<sup>(1)</sup>

- 00000 = Not synchronized to any other module

- Note 1: Do not use an output compare module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as trigger sources only and never as Sync sources.

- 3: These bits affect the rising edge when OCINV = 1. The bits have no effect when the OCMx bits (OCxCON1<2:0>) = 001.

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC     | R-0, HSC                                                                                                                           | U-0                            | U-0              | U-0                          | R/C-0, HS        | R-0, HSC                         | R-0, HSC              |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|------------------------------|------------------|----------------------------------|-----------------------|--|--|

| ACKSTAT      | TRSTAT                                                                                                                             | —                              |                  | —                            | BCL              | GCSTAT                           | ADD10                 |  |  |

| bit 15       |                                                                                                                                    |                                |                  |                              |                  |                                  | bit 8                 |  |  |

|              | <b>B</b> / <b>B A HB</b>                                                                                                           |                                |                  |                              | <b>D</b> A 1100  | <b>D</b> 0 1100                  | <b>D</b> 0 1100       |  |  |

| R/C-0, HS    | R/C-0, HS                                                                                                                          | R-0, HSC                       | R/C-0, HSC       | R/C-0, HSC                   | R-0, HSC         | R-0, HSC                         | R-0, HSC              |  |  |

| IWCOL        | I2COV                                                                                                                              | D/A                            | Р                | S                            | R/W              | RBF                              | TBF                   |  |  |

| bit 7        |                                                                                                                                    |                                |                  |                              |                  |                                  | bit C                 |  |  |

| Legend:      |                                                                                                                                    | C = Clearab                    | e bit            | HS = Hardwar                 | e Settable bit   | HSC = Hardware S                 | Settable/Clearable bi |  |  |

| R = Readab   | ole bit                                                                                                                            | W = Writable                   | e bit            | U = Unimplem                 | ented bit, read  | as '0'                           |                       |  |  |

| -n = Value a | at POR                                                                                                                             | '1' = Bit is se                | t                | '0' = Bit is clea            |                  | x = Bit is unknown               |                       |  |  |

|              |                                                                                                                                    |                                |                  |                              |                  |                                  |                       |  |  |

| bit 15       | ACKSTAT:                                                                                                                           | Acknowledge                    | e Status bit     |                              |                  |                                  |                       |  |  |

|              |                                                                                                                                    | was detected                   |                  |                              |                  |                                  |                       |  |  |

|              |                                                                                                                                    | as detected la                 |                  |                              |                  |                                  |                       |  |  |

| bit 14       |                                                                                                                                    | ransmit Statu                  |                  | Acknowledge.                 |                  |                                  |                       |  |  |

| DIL 14       |                                                                                                                                    |                                |                  | cable to master              | transmit oper    | ration)                          |                       |  |  |

|              |                                                                                                                                    | transmit is in                 |                  |                              |                  |                                  |                       |  |  |

|              | 0 = Master                                                                                                                         | transmit is no                 | ot in progress   | 5                            |                  |                                  |                       |  |  |

|              | Hardware is                                                                                                                        | s set at the beg               | jinning of the r | master transmis              | sion; hardware   | is clear at the end of           | f slave Acknowledge   |  |  |

| bit 13-11    | -                                                                                                                                  | ented: Read                    |                  |                              |                  |                                  |                       |  |  |

| bit 10       |                                                                                                                                    | er Bus Collisi                 |                  |                              |                  |                                  |                       |  |  |

|              | 1 = A bus c<br>0 = No coll                                                                                                         |                                | een detected     | d during a mast              | er operation     |                                  |                       |  |  |

|              |                                                                                                                                    |                                | etection of a    | bus collision.               |                  |                                  |                       |  |  |

| bit 9        | GCSTAT: (                                                                                                                          | General Call S                 | Status bit       |                              |                  |                                  |                       |  |  |

|              | 1 = Genera                                                                                                                         | al call address                | s was receive    | d                            |                  |                                  |                       |  |  |

|              |                                                                                                                                    | al call address                |                  |                              |                  |                                  |                       |  |  |

|              |                                                                                                                                    |                                |                  | tches the gene               | eral call addres | ss; hardware is clea             | ar at Stop detection. |  |  |

| bit 8        |                                                                                                                                    | -Bit Address                   |                  |                              |                  |                                  |                       |  |  |

|              |                                                                                                                                    | address was r<br>address was r |                  |                              |                  |                                  |                       |  |  |

|              |                                                                                                                                    |                                |                  | yte of the match             | ned 10-bit addr  | ess; hardware is cle             | ar at Stop detection  |  |  |

| bit 7        | IWCOL: 12                                                                                                                          | Cx Write Coll                  | ision Detect b   | bit                          |                  |                                  |                       |  |  |

|              | 1 = An atte                                                                                                                        | mpt to write t                 | o the I2CxTR     | RN register faile            | d because the    | e l <sup>2</sup> C module is bus | у                     |  |  |

|              | 0 = No coll                                                                                                                        |                                |                  | 10 10 10 0 T                 |                  | (                                |                       |  |  |

| L:1 0        |                                                                                                                                    |                                |                  |                              | RN While bus     | y (cleared by softwa             | are).                 |  |  |

| bit 6        |                                                                                                                                    | X Receive O                    | •                |                              | in still holding | the providue byte                |                       |  |  |

|              | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul> |                                |                  |                              |                  |                                  |                       |  |  |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                |                                |                  |                              |                  |                                  |                       |  |  |

|              | D/A: Data/                                                                                                                         | Address bit (w                 | vhen operatir    | ng as I <sup>2</sup> C slave | )                |                                  |                       |  |  |

| bit 5        |                                                                                                                                    |                                |                  |                              |                  |                                  |                       |  |  |

| bit 5        |                                                                                                                                    | es that the las                |                  |                              |                  |                                  |                       |  |  |

| bit 5        | 0 = Indicate                                                                                                                       | es that the las                | st byte receiv   | ed was the dev               | ice address      |                                  | or by reception of a  |  |  |

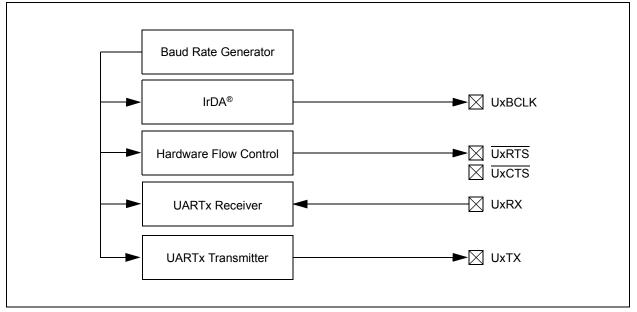

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | this group of PIC24F devices. It is not     |  |  |  |  |  |

|       | intended to be a comprehensive reference    |  |  |  |  |  |

|       | source. For more information on the Univer- |  |  |  |  |  |

|       | sal Asynchronous Receiver Transmitter,      |  |  |  |  |  |

|       | refer to the "PIC24F Family Reference       |  |  |  |  |  |

|       | Manual", Section 21. "UART" (DS39708).      |  |  |  |  |  |

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx is shown in Figure 18-1. The UARTx module consists of these important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

- Note: Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

### FIGURE 18-1: UARTX SIMPLIFIED BLOCK DIAGRAM

# 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

### 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 18.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 18.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

# 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

# REGISTER 22-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   | U-0   |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   | —   | —   | —   | _   |       | —     |

| bit 15 |     |     |     |     |     |       | bit 8 |

|        |     |     |     |     |     |       |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|        |     | —   | —   | —   |     | CHH17 | CHH16 |

| bit 7  |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'.

bit 1-0 CHH<17:16>: A/D Compare Hit bits

If CM<1:0> = 11:

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For All Other Values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

# REGISTER 22-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| CHH15  | CHH14 | CHH13 | CHH12 | CHH11 | CHH10 | CHH9  | CHH8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CHH7   | CHH6  | CHH5  | CHH4  | CHH3  | CHH2  | CHH1  | CHH0  |

| bit 7  | •     | •     | •     |       | •     | •     | bit 0 |

|        |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CHH<15:0>: A/D Compare Hit bits

<u>If CM<1:0> = 11:</u>

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For all other values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

### REGISTER 26-10: DEVREV: DEVICE REVISION REGISTER

| U-0                                | U-0 | U-0 | U-0          | U-0               | U-0      | U-0             | U-0    |

|------------------------------------|-----|-----|--------------|-------------------|----------|-----------------|--------|

| —                                  | _   | —   |              | —                 | -        | —               | —      |

| bit 23                             |     |     |              |                   |          |                 | bit 16 |

|                                    |     |     |              |                   |          |                 |        |

| U-0                                | U-0 | U-0 | U-0          | U-0               | U-0      | U-0             | U-0    |

| —                                  | _   | —   | —            | —                 | —        | —               | —      |

| bit 15                             |     | -   |              |                   |          | •               | bit 8  |

|                                    |     |     |              |                   |          |                 |        |

| U-0                                | U-0 | U-0 | U-0          | R                 | R        | R               | R      |

| —                                  | —   | —   | —            | REV3              | REV2     | REV1            | REV0   |

| bit 7                              |     | -   |              |                   |          | •               | bit 0  |

|                                    |     |     |              |                   |          |                 |        |

| Legend:                            |     |     |              |                   |          |                 |        |

| R = Readable bit W = Writable bit  |     |     | U = Unimplem | nented bit, read  | l as '0' |                 |        |

| -n = Value at POR '1' = Bit is set |     |     |              | '0' = Bit is clea | ared     | x = Bit is unkr | nown   |

|                                    |     |     |              |                   |          |                 |        |

bit 23-4 Unimplemented: Read as '0'

bit 3-0 **REV<3:0>:** Minor Revision Identifier bits

### TABLE 29-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| <b>Operating Conditions:</b> -40°C < TA < +125°C (unless otherwise stated) |        |                                       |       |       |       |       |                                                                   |

|----------------------------------------------------------------------------|--------|---------------------------------------|-------|-------|-------|-------|-------------------------------------------------------------------|

| Param<br>No.                                                               | Symbol | Characteristics                       | Min   | Тур   | Max   | Units | Comments                                                          |

| DVR10                                                                      | Vbg    | Band Gap Reference Voltage            | 0.973 | 1.024 | 1.075 | V     |                                                                   |

| DVR11                                                                      | Tbg    | Band Gap Reference Start-up<br>Time   | —     | 1     | —     | ms    |                                                                   |

| DVR20                                                                      | Vrgout | Regulator Output Voltage              | 3.1   | 3.3   | 3.6   | V     | -40°C < TA < +85°C                                                |

|                                                                            |        |                                       | 3.0   | 3.19  | 3.6   | V     | -40°C < TA < +125°C                                               |

| DVR21                                                                      | Cefc   | External Filter Capacitor Value       | 4.7   | 10    | _     | μF    | Series resistance < 3 Ohm<br>recommended;<br>< 5 Ohm is required. |

| DVR30                                                                      | Vlvr   | Retention Regulator Output<br>Voltage | _     | 2.6   | _     | V     |                                                                   |

### TABLE 29-16: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS |       |                                      | $ \begin{array}{ll} \mbox{Standard Operating Conditions:} & 1.8V \ to \ 3.6V \ PIC24F32KA3XX \\ & 2.0V \ to \ 5.5V \ PIC24FV32KA3XX \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ for \ Industrial \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \ for \ Extended \\ \end{array} $ |                    |     |       |                                |                      |  |

|--------------------|-------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------|----------------------|--|

| Param<br>No.       | Sym   | Characteristic                       | Min                                                                                                                                                                                                                                                                                                            | Typ <sup>(1)</sup> | Max | Units | Comments                       | Conditions           |  |

| DCT10              | IOUT1 | CTMU Current<br>Source, Base Range   | —                                                                                                                                                                                                                                                                                                              | 550                | —   | nA    | CTMUICON<9:8> = 01             |                      |  |

| DCT11              | IOUT2 | CTMU Current<br>Source, 10x Range    | _                                                                                                                                                                                                                                                                                                              | 5.5                | —   | μA    | CTMUICON<9:8> = 10             | 2.5V < VDD < VDDMAX  |  |

| DCT12              | IOUT3 | CTMU Current<br>Source, 100x Range   | -                                                                                                                                                                                                                                                                                                              | 55                 | —   | μA    | CTMUICON<9:8> = 11             | 2.5V < VDD < VDDIWAX |  |

| DCT13              | Iout4 | CTMU Current<br>Source, 1000x Range  | _                                                                                                                                                                                                                                                                                                              | 550                | —   | μA    | CTMUICON<9:8> = 00<br>(Note 2) |                      |  |

| DCT20              | VF    | Temperature Diode<br>Forward Voltage | —                                                                                                                                                                                                                                                                                                              | .76                | —   | V     |                                |                      |  |

| DCT21              | VΔ    | Voltage Change per<br>Degree Celsius | _                                                                                                                                                                                                                                                                                                              | 1.6                | _   | mV/°C |                                |                      |  |

**Note 1:** Nominal value at the center point of the current trim range (CTMUICON<7:2> = 000000). On PIC24F32KA parts, the current output is limited to the typical current value when IOUT4 is chosen.

**2:** Do not use this current range with a temperature sensing diode.

# FIGURE 30-51: VIL/VIH vs. VDD (GENERAL PURPOSE I/O, TEMPERATURES AS NOTED)

# FIGURE 30-52: VIL/VIH vs. VDD (I<sup>2</sup>C<sup>™</sup>, TEMPERATURES AS NOTED)

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Product Group<br>Pin Count<br>Tape and Reel Fl |                                                                                                                                                                                          | <ul> <li>Examples:</li> <li>a) PIC24FV32KA304-I/ML: Wide voltage range,<br/>General Purpose, 32-Kbyte program memory,<br/>44-pin, Industrial temp., QFN package</li> <li>b) PIC24F16KA302-I/SS: Standard voltage range,<br/>General Purpose, 16-Kbyte program memory,<br/>28-pin, Industrial temp., SSOP package</li> </ul> |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                                   | 24 = 16-bit modified Harvard without DSP                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                             |

| Flash Memory Family                            | <ul><li>F = Standard voltage range Flash program memory</li><li>FV = Wide voltage range Flash program memory</li></ul>                                                                   |                                                                                                                                                                                                                                                                                                                             |

| Product Group                                  | KA3 = General purpose microcontrollers                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                             |

| Pin Count                                      | 01 = 20-pin<br>02 = 28-pin<br>04 = 44-pin                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |

| Temperature Range                              | $I = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Industrial)}$<br>E = -40^{\circ}C to +125^{\circ}C (Industrial)                                                                       |                                                                                                                                                                                                                                                                                                                             |

| Package                                        | SP         = SPDIP           SO         = SOIC           SS         = SSOP           ML         = QFN           P         = PDIP           PT         = TQFP           MV         = UQFN |                                                                                                                                                                                                                                                                                                                             |

| Pattern                                        | Three-digit QTP, SQTP, Code or Special Requirements<br>(blank otherwise)<br>ES = Engineering Sample                                                                                      |                                                                                                                                                                                                                                                                                                                             |