Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 13x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka302t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

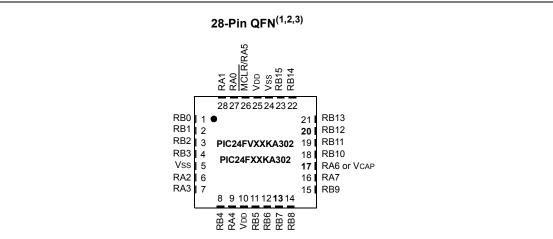

### **Pin Diagrams**

| D:  | Pin Features                                              |                                                           |  |  |  |  |  |  |  |

|-----|-----------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|--|

| Pin | PIC24FVXXKA302                                            | PIC24FXXKA302                                             |  |  |  |  |  |  |  |

| 1   | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      |  |  |  |  |  |  |  |

| 2   | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 |  |  |  |  |  |  |  |

| 3   | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        |  |  |  |  |  |  |  |

| 4   | AN5/C1INA/C2INC/SCL2/CN7/RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RB3                              |  |  |  |  |  |  |  |

| 5   | Vss                                                       | Vss                                                       |  |  |  |  |  |  |  |

| 6   | OSCI/AN13/CLKI/CN30/RA2                                   | OSCI/AN13/CLKI/CN30/RA2                                   |  |  |  |  |  |  |  |

| 7   | OSCO/AN14/CLKO/CN29/RA3                                   | OSCO/AN14/CLKO/CN29/RA3                                   |  |  |  |  |  |  |  |

| 8   | SOSCI/AN15/U2RTS/CN1/RB4                                  | SOSCI/AN15/U2RTS/CN1/RB4                                  |  |  |  |  |  |  |  |

| 9   | SOSCO/SCLKI/U2CTS/CN0/RA4                                 | SOSCO/SCLKI/U2CTS/CN0/RA4                                 |  |  |  |  |  |  |  |

| 10  | Vdd                                                       | VDD                                                       |  |  |  |  |  |  |  |

| 11  | PGED3/ASDA1 <sup>(2)</sup> /SCK2/CN27/RB5                 | PGED3/ASDA1 <sup>(2)</sup> /SCK2/CN27/RB5                 |  |  |  |  |  |  |  |

| 12  | PGEC3/ASCL1 <sup>(2)</sup> /SDO2/CN24/RB6                 | PGEC3/ASCL1 <sup>(2)</sup> /SDO2/CN24/RB6                 |  |  |  |  |  |  |  |

| 13  | U1TX/C2OUT/OC1/INT0/CN23/RB7                              | U1TX/INT0/CN23/RB7                                        |  |  |  |  |  |  |  |

| 14  | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          |  |  |  |  |  |  |  |

| 15  | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        |  |  |  |  |  |  |  |

| 16  | SDI2/IC1/CTED3/CN9/RA7                                    | SDI2/IC1/CTED3/CN9/RA7                                    |  |  |  |  |  |  |  |

| 17  | VCAP                                                      | C2OUT/OC1/CTED1/INT2/CN8/RA6                              |  |  |  |  |  |  |  |

| 18  | PGED2/SDI1/OC3/CTED11/CN16/RB10                           | PGED2/SDI1/OC3/CTED11/CN16/RB10                           |  |  |  |  |  |  |  |

| 19  | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            |  |  |  |  |  |  |  |

| 20  | AN12/HLVDIN/SS2/IC3/CTED2/INT2/CN14/RB12                  | AN12/HLVDIN/SS2/IC3/CTED2/CN14/RB12                       |  |  |  |  |  |  |  |

| 21  | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            |  |  |  |  |  |  |  |

| 22  | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |  |  |  |  |  |  |  |

| 23  | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              |  |  |  |  |  |  |  |

| 24  | Vss/AVss                                                  | Vss/AVss                                                  |  |  |  |  |  |  |  |

| 25  | Vdd/AVdd                                                  | Vdd/AVdd                                                  |  |  |  |  |  |  |  |

| 26  | MCLR/Vpp/RA5                                              | MCLR/Vpp/RA5                                              |  |  |  |  |  |  |  |

| 27  | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                      | VREF+/CVREF+/AN0/C3INC/CN2/RA0                            |  |  |  |  |  |  |  |

| 28  | CVREF-/VREF-/AN1/CN3/RA1                                  | CVREF-/VREF-/AN1/CN3/RA1                                  |  |  |  |  |  |  |  |

Legend: Pin numbers in **bold** indicate pin function differences between PIC24FV and PIC24F devices.

**Note 1:** Exposed pad on underside of device is connected to Vss.

2: Alternative multiplexing for SDA1 (ASDA1) and SCL1 (ASCL1) when the I2CSEL Configuration bit is set.

3: PIC24F32KA304 device pins have a maximum voltage of 3.6V and are not 5V tolerant.

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE Reset - GOTO Instruction 000000h Reset - GOTO Address 000002h Reserved 000004h Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000014h Interrupt Vector 1 \_ Interrupt Vector 52 00007Ch Interrupt Vector Table (IVT)<sup>(1)</sup> Decreasing Natural Order Priority Interrupt Vector 53 00007Eh Interrupt Vector 54 000080h \_ Interrupt Vector 116 0000FCh Interrupt Vector 117 0000FEh Reserved 000100h Reserved 000102h Reserved Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000114h Interrupt Vector 1 Alternate Interrupt Vector Table (AIVT)<sup>(1)</sup> 00017Ch Interrupt Vector 52 00017Eh Interrupt Vector 53 Interrupt Vector 54 000180h \_\_\_\_\_ Interrupt Vector 116 Interrupt Vector 117 0001FEh Start of Code 000200h

Note 1: See Table 8-2 for the interrupt vector list.

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0                                                                  | U-0                                                                | U-0 | U-0 | U-0 | U-0 | U-0  | U-0     |

|----------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|-----|------|---------|

| _                                                                    | —                                                                  | —   | _   | —   |     | _    | —       |

| bit 15                                                               |                                                                    |     |     |     |     |      | bit 8   |

|                                                                      |                                                                    |     |     |     |     |      |         |

| U-0                                                                  | U-0                                                                | U-0 | U-0 | U-0 | U-0 | U-0  | R/W-0   |

| —                                                                    | —                                                                  | —   | —   | —   | —   | —    | ULPWUIE |

| bit 7                                                                |                                                                    |     |     |     |     |      | bit 0   |

|                                                                      |                                                                    |     |     |     |     |      |         |

| Legend:                                                              |                                                                    |     |     |     |     |      |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                    |     |     |     |     |      |         |

| -n = Value at                                                        | ue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     |     |     | nown |         |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                                                               | R/W-0              | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|------------------|---------------------------------------------------------------------|--------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| _                | U1RXIP2                                                             | U1RXIP1            | U1RXIP0          | _                | SPI1IP2          | SPI1IP1         | SPI1IP0 |  |  |  |  |  |

| bit 15           |                                                                     |                    |                  |                  |                  |                 | bit 8   |  |  |  |  |  |

| U-0              | R/W-1                                                               | R/W-0              | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

| _                | SPF1IP2                                                             | SPF1IP1            | SPF1IP0          |                  | T3IP2            | T3IP1           | T3IP0   |  |  |  |  |  |

| bit 7            |                                                                     | 1                  |                  |                  |                  | 1               | bit (   |  |  |  |  |  |

| Legend:          |                                                                     |                    |                  |                  |                  |                 |         |  |  |  |  |  |

| R = Readat       | ole bit                                                             | W = Writable       | bit              | U = Unimpler     | nented bit, read | l as '0'        |         |  |  |  |  |  |

| -n = Value a     | at POR                                                              | '1' = Bit is set   |                  | '0' = Bit is cle |                  | x = Bit is unkn | iown    |  |  |  |  |  |

|                  |                                                                     |                    |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 15           | Unimplemen                                                          | ted: Read as '     | )'               |                  |                  |                 |         |  |  |  |  |  |

| bit 14-12        | -                                                                   | : UART1 Rece       |                  | riority bits     |                  |                 |         |  |  |  |  |  |

|                  |                                                                     | pt is Priority 7 ( | =                | -                |                  |                 |         |  |  |  |  |  |

|                  | •                                                                   |                    | 0 . ,            | • /              |                  |                 |         |  |  |  |  |  |

|                  | •                                                                   |                    |                  |                  |                  |                 |         |  |  |  |  |  |

|                  | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |                    |                  |                  |                  |                 |         |  |  |  |  |  |

|                  | -                                                                   |                    |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 11           | -                                                                   | ted: Read as '     |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 10-8         |                                                                     | SPI1 Event Int     | , ,              |                  |                  |                 |         |  |  |  |  |  |

|                  | 111 = Interru                                                       | ot is Priority 7 ( | highest priority | interrupt)       |                  |                 |         |  |  |  |  |  |

|                  | •                                                                   |                    |                  |                  |                  |                 |         |  |  |  |  |  |

|                  | •<br>001 = Interru                                                  | pt is Priority 1   |                  |                  |                  |                 |         |  |  |  |  |  |

|                  | 000 = Interru                                                       | pt source is dis   | abled            |                  |                  |                 |         |  |  |  |  |  |

| bit 7            | Unimplemen                                                          | ted: Read as '     | )'               |                  |                  |                 |         |  |  |  |  |  |

| bit 6-4          | SPF1IP<2:0>                                                         | : SPI1 Fault Inf   | errupt Priority  | oits             |                  |                 |         |  |  |  |  |  |

|                  | 111 = Interru                                                       | pt is Priority 7 ( | highest priority | interrupt)       |                  |                 |         |  |  |  |  |  |

|                  | •                                                                   |                    |                  |                  |                  |                 |         |  |  |  |  |  |

|                  |                                                                     |                    |                  |                  |                  |                 |         |  |  |  |  |  |

|                  | 001 = Interru                                                       | ot is Priority 1   | abled            |                  |                  |                 |         |  |  |  |  |  |

|                  | -                                                                   | ted: Read as '     |                  |                  |                  |                 |         |  |  |  |  |  |

| hit 3            |                                                                     | imer3 Interrupt    |                  |                  |                  |                 |         |  |  |  |  |  |

|                  |                                                                     |                    | •                | interrunt)       |                  |                 |         |  |  |  |  |  |

|                  | 111 = Interru                                                       | nt is Priority 7 ( |                  |                  |                  |                 |         |  |  |  |  |  |

|                  | 111 = Interruj<br>•                                                 | pt is Priority 7 ( | nignest priority | interrupt)       |                  |                 |         |  |  |  |  |  |

| bit 3<br>bit 2-0 | 111 = Interruj<br>•                                                 | pt is Priority 7 ( | nignest priority | interrupt)       |                  |                 |         |  |  |  |  |  |

|                  | •<br>•<br>001 = Interru                                             |                    |                  | interrupt)       |                  |                 |         |  |  |  |  |  |

#### 10.2.4.2 Exiting Deep Sleep Mode

Deep Sleep mode exits on any one of the following events:

- A POR event on VDD supply. If there is no DSBOR circuit to re-arm the VDD supply POR circuit, the external VDD supply must be lowered to the natural arming voltage of the POR circuit.

- A DSWDT time-out. When the DSWDT timer times out, the device exits Deep Sleep.

- An RTCC alarm (if RTCEN = 1).

- An assertion ('0') of the MCLR pin.

- An assertion of the INT0 pin (if the interrupt was enabled before Deep Sleep mode was entered). The polarity configuration is used to determine the assertion level ('0' or '1') of the pin that will cause an exit from Deep Sleep mode. Exiting from Deep Sleep mode requires a change on the INT0 pin while in Deep Sleep mode.

Note: Any interrupt pending when entering Deep Sleep mode is cleared.

Exiting Deep Sleep mode generally does not retain the state of the device and is equivalent to a Power-on Reset (POR) of the device. Exceptions to this include the RTCC (if present), which remains operational through the wake-up, the DSGPRx registers and DSWDT.

Wake-up events that occur after Deep Sleep exits, but before the POR sequence completes, are ignored and are not be captured in the DSWAKE register.

The sequence for exiting Deep Sleep mode is:

- 1. After a wake-up event, the device exits Deep Sleep and performs a POR. The DSEN bit is cleared automatically. Code execution resumes at the Reset vector.

- To determine if the device exited Deep Sleep, read the Deep Sleep bit, DPSLP (RCON<10>). This bit will be set if there was an exit from Deep Sleep mode; if the bit is set, clear it.

- 3. Determine the wake-up source by reading the DSWAKE register.

- Determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR bit (DSCON<1>).

- 5. If application context data has been saved, read it back from the DSGPR0 and DSGPR1 registers.

- 6. Clear the RELEASE bit (DSCON<0>).

## 10.2.4.3 Saving Context Data with the DSGPR0/DSGPR1 Registers

As exiting Deep Sleep mode causes a POR, most Special Function Registers reset to their default POR values. In addition, because VCORE power is not supplied in Deep Sleep mode, information in data RAM may be lost when exiting this mode. Applications which require critical data to be saved prior to Deep Sleep may use the Deep Sleep General Purpose registers, DSGPR0 and DSGPR1 or data EEPROM (if available). Unlike other SFRs, the contents of these registers are preserved while the device is in Deep Sleep mode. After exiting Deep Sleep, software can restore the data by reading the registers and clearing the RELEASE bit (DSCON<0>).

#### 10.2.4.4 I/O Pins During Deep Sleep

During Deep Sleep, the general purpose I/O pins retain their previous states and the Secondary Oscillator (SOSC) will remain running, if enabled. Pins that are configured as inputs (TRISx bit is set), prior to entry into Deep Sleep, remain high-impedance during Deep Sleep. Pins that are configured as outputs (TRISx bit is clear), prior to entry into Deep Sleep, remain as output pins during Deep Sleep. While in this mode, they continue to drive the output level determined by their corresponding LATx bit at the time of entry into Deep Sleep.

Once the device wakes back up, all I/O pins continue to maintain their previous states, even after the device has finished the POR sequence and is executing application code again. Pins configured as inputs during Deep Sleep remain high-impedance and pins configured as outputs continue to drive their previous value. After waking up, the TRIS and LAT registers, and the SOSCEN bit (OSCCON<1>) are reset. If firmware modifies any of these bits or registers, the I/O will not immediately go to the newly configured states. Once the firmware clears the RELEASE bit (DSCON<0>), the I/O pins are "released". This causes the I/O pins to take the states configured by their respective TRISx and LATx bit values.

This means that keeping the SOSC running after waking up requires the SOSCEN bit to be set before clearing RELEASE.

If the Deep Sleep BOR (DSBOR) is enabled, and a DSBOR or a true POR event occurs during Deep Sleep, the I/O pins will be immediately released, similar to clearing the RELEASE bit. All previous state information will be lost, including the general purpose DSGPR0 and DSGPR1 contents.

If a MCLR Reset event occurs during Deep Sleep, the DSGPRx, DSCON and DSWAKE registers will remain valid, and the RELEASE bit will remain set. The state of the SOSC will also be retained. The I/O pins, however, will be reset to their MCLR Reset state. Since RELEASE is still set, changes to the SOSCEN bit (OSCCON<1>) cannot take effect until the RELEASE bit is cleared.

In all other Deep Sleep wake-up cases, application firmware must clear the RELEASE bit in order to reconfigure the I/O pins.

### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Serial Peripheral Interface, refer to the *"PIC24F Family Reference Manual"*, Section 23. *"Serial Peripheral Interface (SPI)"* (DS39699).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial data EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

**Note:** Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPI1BUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- SDI1: Serial Data Input

- SDO1: Serial Data Output

- · SCK1: Shift Clock Input or Output

- SS1: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SS1}$  is not used. In the 2-pin mode, both SDO1 and  $\overline{SS1}$  are not used.

Block diagrams of the module, in Standard and Enhanced Buffer modes, are shown in Figure 16-1 and Figure 16-2.

The devices of the PIC24FV32KA304 family offer two SPI modules on a device.

Note: In this section, the SPI modules are referred to as SPIx. Special Function Registers (SFRs) will follow a similar notation. For example, SPI1CON1 or SPI1CON2 refers to the control register for the SPI1 module. To set up the SPI1 module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 1.

- 3. Clear the SPIROV bit (SPI1STAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

- 5. Write the data to be transmitted to the SPI1BUF register. Transmission (and reception) will start as soon as data is written to the SPI1BUF register.

To set up the SPI1 module for the Standard Slave mode of operation:

- 1. Clear the SPI1BUF register.

- 2. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit (SPI1CON1<7>) must be set to enable the SS1 pin.

- 6. Clear the SPIROV bit (SPI1STAT<6>).

- 7. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

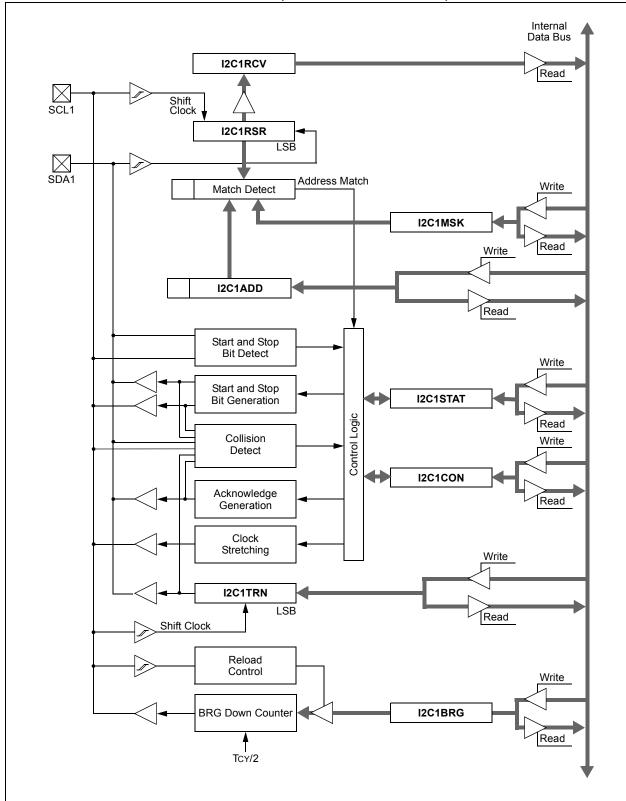

### FIGURE 17-1: I<sup>2</sup>C<sup>™</sup> BLOCK DIAGRAM (I2C1 MODULE IS SHOWN)

| R/W-0         | U-0                                         | R/W-0                                          | R-0              | R-0               | R-0             | R-0             | R-0           |  |  |  |  |

|---------------|---------------------------------------------|------------------------------------------------|------------------|-------------------|-----------------|-----------------|---------------|--|--|--|--|

| CRCEN         | <u> </u>                                    | CSIDL                                          | VWORD4           | VWORD3            | VWORD2          | VWORD1          | VWORD0        |  |  |  |  |

| bit 15        |                                             | COIDE                                          |                  |                   | V V U U U U     |                 | bit 8         |  |  |  |  |

| bit 10        |                                             |                                                |                  |                   |                 |                 | bit 0         |  |  |  |  |

| R-0, HSC      | R-1, HSC                                    | R/W-0                                          | R/W-0, HC        | R/W-0             | U-0             | U-0             | U-0           |  |  |  |  |

| CRCFUL        | CRCMPT                                      | CRCISEL                                        | CRCGO            | LENDIAN           | —               | —               | —             |  |  |  |  |

| bit 7         |                                             |                                                | •                |                   |                 |                 | bit 0         |  |  |  |  |

|               |                                             |                                                |                  |                   |                 |                 |               |  |  |  |  |

| Legend:       |                                             | HC = Hardware                                  | Clearable bit    | HSC = Hardw       | are Settable/C  | Clearable bit   |               |  |  |  |  |

| R = Readabl   | e bit                                       | W = Writable bit                               |                  | U = Unimplen      | nented bit, rea | ad as '0'       |               |  |  |  |  |

| -n = Value at | POR                                         | '1' = Bit is set                               |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown          |  |  |  |  |

|               |                                             |                                                |                  |                   |                 |                 |               |  |  |  |  |

| bit 15        | CRCEN: CR                                   | C Enable bit                                   |                  |                   |                 |                 |               |  |  |  |  |

|               | 1 = Module<br>0 = Module                    |                                                |                  |                   |                 |                 |               |  |  |  |  |

|               |                                             | chines, pointers a                             | nd CRCWDAT/      | CRCDAT regist     | ers are reset:  | other SERs an   | e NOT reset.  |  |  |  |  |

| bit 14        |                                             | nted: Read as '0'                              |                  |                   |                 |                 |               |  |  |  |  |

| bit 13        | -                                           | C Stop in Idle Mod                             | e bit            |                   |                 |                 |               |  |  |  |  |

|               |                                             | inues module ope                               |                  | vice enters Idle  | mode            |                 |               |  |  |  |  |

|               | 0 = Continues module operation in Idle mode |                                                |                  |                   |                 |                 |               |  |  |  |  |

| bit 12-8      | VWORD<4:0                                   | 0>: Pointer Value                              | bits             |                   |                 |                 |               |  |  |  |  |

|               |                                             | e number of valid v<br>PLEN<4:0> $\leq$ 7.     | vords in the FIF | O, which has a    | maximum val     | ue of 8 when P  | PLEN<4:0> > 7 |  |  |  |  |

| bit 7         | CRCFUL: C                                   | RC FIFO Full bit                               |                  |                   |                 |                 |               |  |  |  |  |

|               | 1 = FIFO is<br>0 = FIFO is                  |                                                |                  |                   |                 |                 |               |  |  |  |  |

| bit 6         | CRCMPT: C                                   | RC FIFO Empty E                                | Bit              |                   |                 |                 |               |  |  |  |  |

|               | 1 = FIFO is empty                           |                                                |                  |                   |                 |                 |               |  |  |  |  |

|               | 0 = FIFO is                                 |                                                |                  |                   |                 |                 |               |  |  |  |  |

| bit 5         | CRCISEL: CRC interrupt Selection bit        |                                                |                  |                   |                 |                 |               |  |  |  |  |

|               | •                                           | t on FIFO is empt<br>t on shift is compl       | •                |                   |                 |                 |               |  |  |  |  |

| bit 4         | CRCGO: Sta                                  | -                                              |                  | DATTCSULTSTC      | auy             |                 |               |  |  |  |  |

|               |                                             | RC serial shifter                              |                  |                   |                 |                 |               |  |  |  |  |

|               |                                             | rial shifter is turne                          | ed off           |                   |                 |                 |               |  |  |  |  |

| bit 3         | LENDIAN: D                                  | Data Shift Directio                            | n Select bit     |                   |                 |                 |               |  |  |  |  |

|               |                                             | ord is shifted into t<br>ord is shifted into t |                  |                   |                 |                 |               |  |  |  |  |

| bit 2-0       | Unimplemer                                  | nted: Read as '0'                              |                  |                   |                 |                 |               |  |  |  |  |

|               |                                             |                                                |                  |                   |                 |                 |               |  |  |  |  |

#### REGISTER 20-1: CRCCON1: CRC CONTROL REGISTER 1

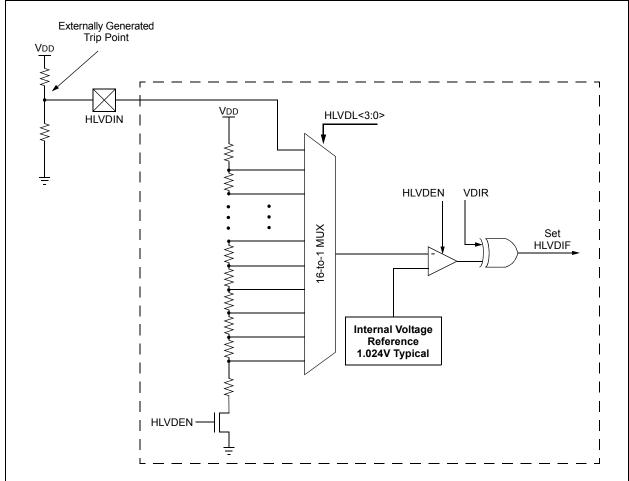

### 21.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the High/Low-Voltage Detect, refer to the "PIC24F Family Reference Manual", Section 36. "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725).

The High/Low-Voltage Detect module (HLVD) is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 21-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

### FIGURE 21-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

NOTES:

| U-0                                | U-0   | U-0 | U-0                                | U-0 | U-0             | R/C-1 | R/C-1 |  |  |

|------------------------------------|-------|-----|------------------------------------|-----|-----------------|-------|-------|--|--|

| —                                  |       | —   | _                                  | —   |                 | GSS0  | GWRP  |  |  |

| bit 7 bit 0                        |       |     |                                    |     |                 |       |       |  |  |

|                                    |       |     |                                    |     |                 |       |       |  |  |

| Legend:                            |       |     |                                    |     |                 |       |       |  |  |

| R = Readable bit C = Clearable bit |       | hit | U = Unimplemented bit, read as '0' |     |                 |       |       |  |  |

| R = Readable                       | , DIL |     | , DIL                              |     | chica bit, icac |       |       |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                          |

|---------|-----------------------------------------------------------------------------------------------------|

| bit 1   | GSS0: General Segment Code Flash Code Protection bit                                                |

|         | <ul><li>1 = No protection</li><li>0 = Standard security is enabled</li></ul>                        |

| bit 0   | GWRP: General Segment Code Flash Write Protection bit                                               |

|         | <ul><li>1 = General segment may be written</li><li>0 = General segment is write-protected</li></ul> |

**REGISTER 26-2: FGS: GENERAL SEGMENT CONFIGURATION REGISTER**

#### **REGISTER 26-3:** FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| R/P-1 | R/P-1   | R/P-1   | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  |

|-------|---------|---------|-----|-----|--------|--------|--------|

| IESO  | LPRCSEL | SOSCSRC | —   | —   | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7 |         |         |     |     |        |        | bit 0  |

| Legend:                                                                                                                                                                                          |                  |                                                                                                                                                                                      |                          |                    |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|--|--|--|--|--|

| R = Reada                                                                                                                                                                                        | ble bit          | P = Programmable bit                                                                                                                                                                 | U = Unimplemented bit    | , read as '0'      |  |  |  |  |  |

| -n = Value                                                                                                                                                                                       | at POR           | '1' = Bit is set                                                                                                                                                                     | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |  |

|                                                                                                                                                                                                  |                  |                                                                                                                                                                                      |                          |                    |  |  |  |  |  |

| bit 7                                                                                                                                                                                            | IESO: Inte       | ernal External Switchover bit                                                                                                                                                        |                          |                    |  |  |  |  |  |

| <ul> <li>1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)</li> <li>0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)</li> </ul> |                  |                                                                                                                                                                                      |                          |                    |  |  |  |  |  |

| bit 6                                                                                                                                                                                            | LPRCSEL          | .: Internal LPRC Oscillator Pov                                                                                                                                                      | ver Select bit           |                    |  |  |  |  |  |

|                                                                                                                                                                                                  | 0                | Power/High-Accuracy mode<br>Power/Low-Accuracy mode                                                                                                                                  |                          |                    |  |  |  |  |  |

| bit 5                                                                                                                                                                                            | SOSCSR           | C: Secondary Oscillator Clock                                                                                                                                                        | Source Configuration bit |                    |  |  |  |  |  |

|                                                                                                                                                                                                  |                  | <ul> <li>1 = SOSC analog crystal function is available on the SOSCI/SOSCO pins</li> <li>0 = SOSC crystal is disabled; digital SCLKI function is selected on the SOSCO pin</li> </ul> |                          |                    |  |  |  |  |  |

| bit 4-3                                                                                                                                                                                          | Unimplen         | nented: Read as '0'                                                                                                                                                                  |                          |                    |  |  |  |  |  |

| bit 2-0                                                                                                                                                                                          | FNOSC<2          | ::0>: Oscillator Selection bits                                                                                                                                                      |                          |                    |  |  |  |  |  |

|                                                                                                                                                                                                  | 000 <b>= Fas</b> | t RC Oscillator (FRC)                                                                                                                                                                |                          |                    |  |  |  |  |  |

|                                                                                                                                                                                                  |                  | t RC Oscillator with Divide-by-                                                                                                                                                      | N with PLL module (FRCDI | V+PLL)             |  |  |  |  |  |

- 010 = Primary Oscillator (XT, HS, EC)

- 011 = Primary Oscillator with PLL module (HS+PLL, EC+PLL)

- 100 = Secondary Oscillator (SOSC)

- 101 = Low-Power RC Oscillator (LPRC)

- 110 = 500 kHz Low-Power FRC Oscillator with Divide-by-N (LPFRCDIV)

- 111 = 8 MHz FRC Oscillator with Divide-by-N (FRCDIV)

### 27.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 27.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 27.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta A/D, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 28.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |  |  |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |  |  |  |  |  |

|       | reference source.                          |  |  |  |  |  |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

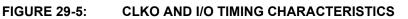

#### TABLE 29-23: CLKO AND I/O TIMING REQUIREMENTS

|              |      |                                       | Standard C |                    | -40°C ≤ T | <b>2.0V to 5</b> .9<br>A ≤ +85°C f | 6V PIC24F32KA3XX<br>5V PIC24FV32KA3XX<br>or Industrial<br>for Extended |

|--------------|------|---------------------------------------|------------|--------------------|-----------|------------------------------------|------------------------------------------------------------------------|

| Param<br>No. | Sym  | Characteristic                        | Min        | Typ <sup>(1)</sup> | Мах       | Units                              | Conditions                                                             |

| DO31         | TIOR | Port Output Rise Time                 | —          | 10                 | 25        | ns                                 |                                                                        |

| DO32         | TIOF | Port Output Fall Time                 | _          | 10                 | 25        | ns                                 |                                                                        |

| DI35         | TINP | INTx Pin High or Low<br>Time (output) | 20         | _                  | _         | ns                                 |                                                                        |

| DI40         | Trbp | CNx High or Low Time<br>(input)       | 2          | —                  | —         | Тсү                                |                                                                        |

Note 1: Data in "Typ" column is at 3.3V, +25°C (PIC24F32KA3XX); 5.0V, +25°C (PIC24FV32KA3XX), unless otherwise stated.

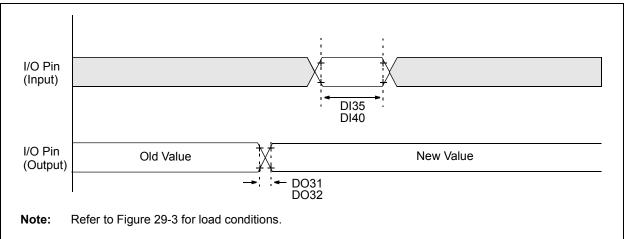

#### FIGURE 29-22: A/D CONVERSION TIMING

2: This is a minimal RC delay (typically 100 ns) which also disconnects the holding capacitor from the analog input.

|              |        |                                                      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |          |            |                                       |  |

|--------------|--------|------------------------------------------------------|-------------------------------------------------------|----------|----------|------------|---------------------------------------|--|

| Param<br>No. | Symbol | mbol Characteristic                                  |                                                       | Тур      | Max.     | Units      | Conditions                            |  |

|              |        | (                                                    | Clock Pa                                              | rameter  | s        |            |                                       |  |

| AD50         | Tad    | A/D Clock Period                                     | 600                                                   | —        | —        | ns         | Tcy = 75 ns, AD1CON3 in default state |  |

| AD51         | TRC    | A/D Internal RC Oscillator<br>Period                 | _                                                     | 1.67     | —        | μs         |                                       |  |

|              |        |                                                      | Convers                                               | ion Rate | )        |            |                                       |  |

| AD55         | TCONV  | Conversion Time                                      | _                                                     | 12<br>14 | _        | Tad<br>Tad | 10-bit results<br>12-bit results      |  |

| AD56         | FCNV   | Throughput Rate                                      | _                                                     |          | 100      | ksps       |                                       |  |

| AD57         | TSAMP  | Sample Time                                          | _                                                     | 1        | _        | Tad        |                                       |  |

| AD58         | TACQ   | Acquisition Time                                     | 750                                                   |          | _        | ns         | (Note 2)                              |  |

| AD59         | Tswc   | Switching Time from Convert to Sample                | _                                                     | —        | (Note 3) |            |                                       |  |

| AD60         | TDIS   | Discharge Time                                       | 12                                                    |          | —        | Tad        |                                       |  |

|              |        | (                                                    | Clock Pa                                              | rameter  | s        |            |                                       |  |

| AD61         | TPSS   | Sample Start Delay from<br>Setting Sample bit (SAMP) | 2                                                     | _        | 3        | Tad        |                                       |  |

### TABLE 29-41: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

2: The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD).

**3:** On the following cycle of the device clock.

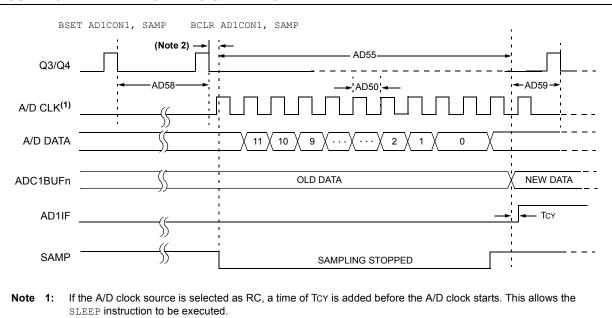

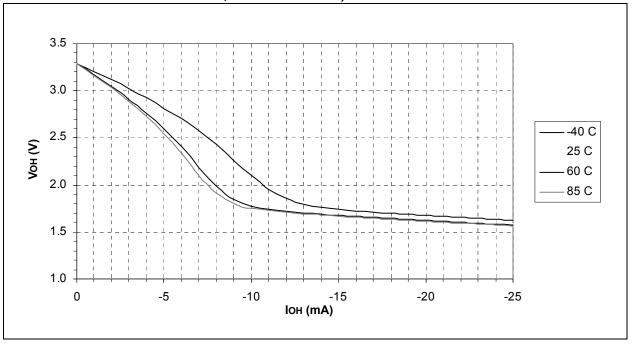

FIGURE 30-25: TYPICAL VOH vs. IOH (GENERAL PURPOSE I/O, AS A FUNCTION OF TEMPERATURE,  $2.0V \le VDD \le 5.5V$ )

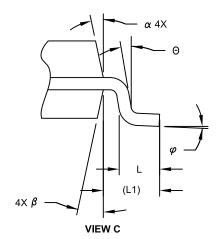

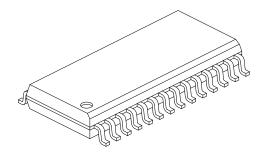

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |     |      |  |

|--------------------------|----|-------------|-----|------|--|

| Dimension Limits         |    | MIN         | NOM | MAX  |  |

| Number of Pins           | N  | 28          |     |      |  |

| Pitch                    | е  | 1.27 BSC    |     |      |  |

| Overall Height           | Α  | -           | -   | 2.65 |  |

| Molded Package Thickness | A2 | 2.05        | -   | -    |  |

| Standoff §               | A1 | 0.10        | -   | 0.30 |  |

| Overall Width            | E  | 10.30 BSC   |     |      |  |

| Molded Package Width     | E1 | 7.50 BSC    |     |      |  |

| Overall Length           | D  | 17.90 BSC   |     |      |  |

| Chamfer (Optional)       | h  | 0.25        | -   | 0.75 |  |

| Foot Length              | L  | 0.40        | -   | 1.27 |  |

| Footprint                | L1 | 1.40 REF    |     |      |  |

| Lead Angle               | Θ  | 0°          | -   | -    |  |

| Foot Angle               | φ  | 0°          | -   | 8°   |  |

| Lead Thickness           | С  | 0.18        | -   | 0.33 |  |

| Lead Width               | b  | 0.31        | -   | 0.51 |  |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

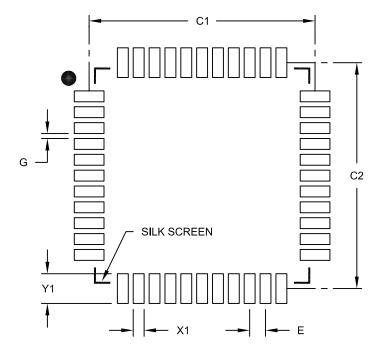

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units | MILLIMETERS |          |      |  |

|--------------------------|-------|-------------|----------|------|--|

| Dimension Limits         |       | MIN         | NOM      | MAX  |  |

| Contact Pitch            | E     |             | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1    |             | 11.40    |      |  |

| Contact Pad Spacing      | C2    |             | 11.40    |      |  |

| Contact Pad Width (X44)  | X1    |             |          | 0.55 |  |

| Contact Pad Length (X44) | Y1    |             |          | 1.50 |  |

| Distance Between Pads    | G     | 0.25        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62077-076-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.