#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 13x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka302t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all the devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex.

# 1.2 Other Special Features

- Communications: The PIC24FV32KA304 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an I<sup>2</sup>C<sup>™</sup> module that supports both the Master and Slave modes of operation. It also comprises UARTs with built-in IrDA<sup>®</sup> encoders/decoders and an SPI module.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- **12-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV32KA304 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation.

# 1.3 Details on Individual Family Members

Devices in the PIC24FV32KA304 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are different from each other in four ways:

- Flash program memory (16 Kbytes for PIC24FV16KA devices, 32 Kbytes for PIC24FV32KA devices).

- Available I/O pins and ports (18 pins on two ports for 20-pin devices, 22 pins on two ports for 28-pin devices and 38 pins on three ports for 44/48-pin devices).

- 3. Alternate SCLx and SDAx pins are available only in 28-pin, 44-pin and 48-pin devices and not in 20-pin devices.

- 4. Members of the PIC24FV32KA301 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV32KA304), accommodate an operating VDD range of 2.0V to 5.5V, and have an on-board Voltage Regulator that powers the core. Peripherals operate at VDD. Standard devices, designated by "F" (such as PIC24F32KA304), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

All other features for devices in this family are identical; these are summarized in Table 1-1.

A list of the pin features available on the PIC24FV32KA304 family devices, sorted by function, is provided in Table 1-3.

Note: Table 1-1 provides the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams on pages 3, 4, 5, 6 and 7 of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |                  |                                 |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|------------------|---------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |                  |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer           | Description                     |

| RC0      | —                                | _                                 | _             | 25                     | 27             | _                                | —                                 | _             | 25                     | 27             | I/O | ST               | PORTC Pins                      |

| RC1      | _                                | _                                 | _             | 26                     | 28             | _                                | _                                 | _             | 26                     | 28             | I/O | ST               |                                 |

| RC2      | _                                | _                                 | _             | 27                     | 29             | _                                | _                                 | _             | 27                     | 29             | I/O | ST               |                                 |

| RC3      | _                                | _                                 |               | 36                     | 39             |                                  | _                                 |               | 36                     | 39             | I/O | ST               |                                 |

| RC4      | _                                | _                                 | _             | 37                     | 40             | _                                | _                                 | _             | 37                     | 40             | I/O | ST               |                                 |

| RC5      | _                                | _                                 | _             | 38                     | 41             | _                                | _                                 | _             | 38                     | 41             | I/O | ST               |                                 |

| RC6      | _                                | _                                 | _             | 2                      | 2              | _                                | _                                 | _             | 2                      | 2              | I/O | ST               |                                 |

| RC7      | _                                | _                                 | _             | 3                      | 3              | _                                | _                                 | _             | 3                      | 3              | I/O | ST               |                                 |

| RC8      | _                                | _                                 | _             | 4                      | 4              | _                                | _                                 | _             | 4                      | 4              | I/O | ST               |                                 |

| RC9      | _                                | _                                 | _             | 5                      | 5              | _                                | _                                 | _             | 5                      | 5              | I/O | ST               |                                 |

| REFO     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 0   | _                | Reference Clock Output          |

| RTCC     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | 0   | _                | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                                | 19            | 9                      | 10             | 15                               | 22                                | 19            | 9                      | 10             | I/O | ST               | SPI1 Serial Input/Output Clock  |

| SCK2     | 2                                | 14                                | 11            | 38                     | 41             | 2                                | 14                                | 11            | 38                     | 41             | I/O | ST               | SPI2 Serial Input/Output Clock  |

| SCL1     | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I/O | l <sup>2</sup> C | I2C1 Clock Input/Output         |

| SCL2     | 18                               | 7                                 | 4             | 24                     | 26             | 18                               | 7                                 | 4             | 24                     | 26             | I/O | l <sup>2</sup> C | I2C2 Clock Input/Output         |

| SCLKI    | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | Ι   | ST               | Digital Secondary Clock Input   |

| SDA1     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I/O | l <sup>2</sup> C | I2C1 Data Input/Output          |

| SDA2     | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I/O | l <sup>2</sup> C | I2C2 Data Input/Output          |

| SDI1     | 17                               | 21                                | 18            | 8                      | 9              | 17                               | 21                                | 18            | 8                      | 9              | Ι   | ST               | SPI1 Serial Data Input          |

| SDI2     | 4                                | 19                                | 16            | 36                     | 39             | 4                                | 19                                | 16            | 36                     | 39             | I   | ST               | SPI2 Serial Data Input          |

| SDO1     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | 0   | _                | SPI1 Serial Data Output         |

| SDO2     | 3                                | 15                                | 12            | 37                     | 40             | 3                                | 15                                | 12            | 37                     | 40             | 0   | —                | SPI2 Serial Data Output         |

| SOSCI    | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I   | ANA              | Secondary Oscillator Input      |

| SOSCO    | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | 0   | ANA              | Secondary Oscillator Output     |

| SS1      | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | 0   | _                | SPI1 Slave Select               |

| SS2      | 15                               | 23                                | 20            | 35                     | 38             | 15                               | 23                                | 20            | 35                     | 38             | 0   | _                | SPI2 Slave Select               |

### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

#### TABLE 4-24: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets <sup>(1)</sup> |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|------------------------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY | _      | _      | —     | _     | _     | ERASE | NVMOP5 | NVMOP4 | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000                         |

| NVMKEY    | 0766 | —      | —      | _      |         | _      | _      | —     | _     |       |       |        | NVMK   | KEY    |        |        |        | 0000                         |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1: Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

### TABLE 4-25: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 0768 | ULPEN  | -      | ULPSIDL | _      | _      | —      | _     | ULPSINK | _     | _     | _     | —     | _     | _     | —     | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-26: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|---------|-------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _      | _     | I2C1MD  | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | ADC1MD | 0000          |

| PMD2      | 0772 |        |        | _      | _      |        | IC3MD  | IC2MD  | IC1MD | _       | _     | _     | _      | _      | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3      | 0774 |        |        | _      | _      |        | CMPMD  | RTCCMD | _     | CRCPMD  | _     | _     | _      | _      | _      | I2C2MD | _      | 0000          |

| PMD4      | 0776 | _      | —      | _      | _      | _      |        |        | -     | ULPWUMD | —     | -     | EEMD   | REFOMD | CTMUMD | HLVDMD |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

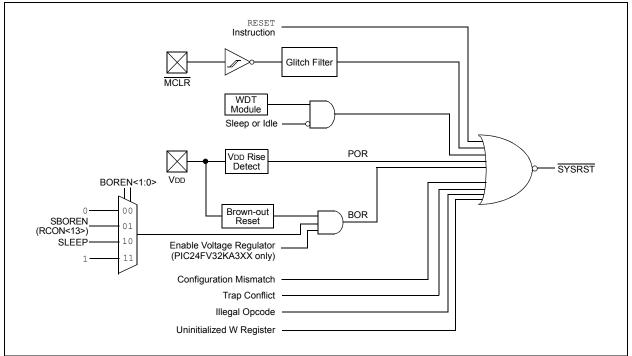

# 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "PIC24F Family Reference Manual", Section 40. "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- Low-Power BOR/Deep Sleep BOR

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on Power-on Reset (POR) and unchanged by all other Resets.

Note: Refer to the specific peripheral or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

## FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

| REGISTER 8      | B-11: IEC0:     | INTERRUP                            | FENABLE C        | ONTROL REC        | GISTER 0         |                 |        |

|-----------------|-----------------|-------------------------------------|------------------|-------------------|------------------|-----------------|--------|

| R/W-0           | U-0             | R/W-0                               | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| NVMIE           | —               | AD1IE                               | U1TXIE           | U1RXIE            | SPI1IE           | SPF1IE          | T3IE   |

| bit 15          |                 |                                     |                  |                   |                  |                 | bit 8  |

| R/W-0           | R/W-0           | R/W-0                               | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IE            | OC2IE           | IC2IE                               | _                | T1IE              | OC1IE            | IC1IE           | INTOIE |

| bit 7           |                 |                                     |                  |                   |                  |                 | bit C  |

| Legend:         |                 |                                     |                  |                   |                  |                 |        |

| R = Readable    | e bit           | W = Writable                        | bit              | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at I | POR             | '1' = Bit is set                    | t                | '0' = Bit is clea |                  | x = Bit is unkn | own    |

| bit 15          | NVMIE: NVM      | Interrupt Enal                      | ole bit          |                   |                  |                 |        |

|                 |                 | request is enat<br>request is not e |                  |                   |                  |                 |        |

| bit 14          | Unimplemen      | ted: Read as '                      | 0'               |                   |                  |                 |        |

| bit 13          | AD1IE: A/D C    | Conversion Co                       | mplete Interrup  | ot Enable bit     |                  |                 |        |

|                 |                 | request is enab<br>request is not e |                  |                   |                  |                 |        |

| bit 12          | •               | •                                   | r Interrupt Ena  | ble bit           |                  |                 |        |

|                 | 1 = Interrupt r | request is enat<br>request is not e | bled             |                   |                  |                 |        |

| bit 11          | •               | •                                   | nterrupt Enable  | e bit             |                  |                 |        |

|                 | 1 = Interrupt r | request is enal                     | bled             |                   |                  |                 |        |

| bit 10          | -               | -                                   | plete Interrupt  | Enable bit        |                  |                 |        |

|                 | 1 = Interrupt r | request is enal                     | bled             |                   |                  |                 |        |

| bit 9           | -               | Fault Interrup                      |                  |                   |                  |                 |        |

|                 | 1 = Interrupt r | request is enal                     | bled             |                   |                  |                 |        |

| bit 8           | -               | Interrupt Enab                      |                  |                   |                  |                 |        |

| bit o           | 1 = Interrupt r | request is enal                     | bled             |                   |                  |                 |        |

| bit 7           |                 | Interrupt Enab                      |                  |                   |                  |                 |        |

| bit /           | 1 = Interrupt r | request is enal                     | bled             |                   |                  |                 |        |

| bit 6           | •               | •                                   | nannel 2 Interru | int Enable hit    |                  |                 |        |

| bit 0           |                 | request is enat                     |                  |                   |                  |                 |        |

|                 |                 | request is not e                    |                  |                   |                  |                 |        |

| bit 5           | •               | •                                   | el 2 Interrupt E | Enable bit        |                  |                 |        |

|                 | 1 = Interrupt r | equest is enab                      | bled             |                   |                  |                 |        |

|                 | •               | request is not e                    |                  |                   |                  |                 |        |

| bit 4           | -               | ted: Read as '                      |                  |                   |                  |                 |        |

| bit 3           |                 | Interrupt Enab                      |                  |                   |                  |                 |        |

|                 |                 | request is enat<br>request is not e |                  |                   |                  |                 |        |

| bit 2           | OC1IE: Output   | ut Compare Ch                       | nannel 1 Interru | upt Enable bit    |                  |                 |        |

|                 |                 |                                     |                  |                   |                  |                 |        |

|                 | 1 = Interrupt r | equest is enat                      | bled             | -                 |                  |                 |        |

# REGISTER 8-11: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

#### R-0 U-0 R/W-0 U-0 R-0 R-0 R-0 R-0 **CPUIRQ** VHOLD ILR3 ILR2 ILR1 ILR0 bit 15 bit 8 U-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 VECNUM6 VECNUM5 VECNUM4 **VECNUM3** VECNUM2 **VECNUM0** VECNUM1 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 CPUIRQ: Interrupt Request from Interrupt Controller CPU bit 1 = An interrupt request has occurred but has not yet been Acknowledged by the CPU (this will happen when the CPU priority is higher than the interrupt priority) 0 = No interrupt request is left unacknowledged bit 14 Unimplemented: Read as '0' bit 13 VHOLD: Vector Hold bit Allows Vector Number Capture and Changes which Interrupt is Stored in the VECNUM bit: 1 = VECNUM will contain the value of the highest priority pending interrupt, instead of the current interrupt 0 = VECNUM will contain the value of the last Acknowledged interrupt (last interrupt that has occurred with higher priority than the CPU, even if other interrupts are pending) bit 12 Unimplemented: Read as '0' bit 11-8 ILR<3:0>: New CPU Interrupt Priority Level bits 1111 = CPU Interrupt Priority Level is 15 0001 = CPU Interrupt Priority Level is 1 0000 = CPU Interrupt Priority Level is 0 bit 7 Unimplemented: Read as '0' bit 6-0 VECNUM<6:0>: Vector Number of Pending Interrupt bits 0111111 = Interrupt vector pending is Number 135 0000001 = Interrupt vector pending is Number 9 0000000 = Interrupt vector pending is Number 8

### REGISTER 8-33: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| R/W-0         | U-0                                | R/W-0                            | U-0            | U-0                                  | U-0              | U-0              | U-0 |

|---------------|------------------------------------|----------------------------------|----------------|--------------------------------------|------------------|------------------|-----|

| TON           | _                                  | TSIDL                            |                |                                      |                  | _                | _   |

| bit 15        |                                    | 1                                |                |                                      |                  |                  | bit |

|               |                                    |                                  |                |                                      |                  |                  |     |

| U-0           | R/W-0                              | R/W-0                            | R/W-0          | R/W-0                                | U-0              | R/W-0            | U-0 |

|               | TGATE                              | TCKPS1                           | TCKPS0         | T32 <sup>(1)</sup>                   | _                | TCS              | —   |

| bit 7         |                                    |                                  |                |                                      |                  |                  | bit |

| Legend:       |                                    |                                  |                |                                      |                  |                  |     |

| R = Readable  | e bit                              | W = Writable                     | bit            | U = Unimplen                         | nented bit, read | d as '0'         |     |

| -n = Value at | POR                                | '1' = Bit is set                 |                | '0' = Bit is clea                    | ared             | x = Bit is unkno | own |

| bit 15        | TON: Timerx                        | On hit                           |                |                                      |                  |                  |     |

|               | When TxCON                         |                                  |                |                                      |                  |                  |     |

|               | 1 = Starts 32                      | -bit Timerx/y                    |                |                                      |                  |                  |     |

|               | 0 = Stops 32                       | -                                |                |                                      |                  |                  |     |

|               | <u>When TxCON</u><br>1 = Starts 16 |                                  |                |                                      |                  |                  |     |

|               | 0 = Stops 16                       |                                  |                |                                      |                  |                  |     |

| bit 14        | Unimplemen                         | ted: Read as '                   | 0'             |                                      |                  |                  |     |

| bit 13        | TSIDL: Timer                       | x Stop in Idle N                 | /lode bit      |                                      |                  |                  |     |

|               |                                    | ues module op<br>s module opera  |                | evice enters Id<br>de                | le mode          |                  |     |

| bit 12-7      | Unimplemen                         | ted: Read as '                   | 0'             |                                      |                  |                  |     |

| bit 6         | TGATE: Time                        | erx Gated Time                   | Accumulation   | Enable bit                           |                  |                  |     |

|               | When TCS =                         |                                  |                |                                      |                  |                  |     |

|               | This bit is igno<br>When TCS =     |                                  |                |                                      |                  |                  |     |

|               |                                    | <u>o.</u><br>ne accumulatio      | n is enabled   |                                      |                  |                  |     |

|               | 0 = Gated tin                      | ne accumulatio                   | n is disabled  |                                      |                  |                  |     |

| bit 5-4       | TCKPS<1:0>                         | : Timerx Input                   | Clock Prescale | e Select bits                        |                  |                  |     |

|               | 11 = 1:256                         |                                  |                |                                      |                  |                  |     |

|               | 10 = 1:64<br>01 = 1:8              |                                  |                |                                      |                  |                  |     |

|               | 00 = 1:1                           |                                  |                |                                      |                  |                  |     |

| bit 3         |                                    | mer Mode Sele                    |                |                                      |                  |                  |     |

|               |                                    |                                  |                | er5 form a singl<br>er5 act as two 1 |                  |                  |     |

| bit 2         | Unimplemen                         | ted: Read as '                   | 0'             |                                      |                  |                  |     |

| bit 1         | TCS: Timerx                        | Clock Source S                   | Select bit     |                                      |                  |                  |     |

|               |                                    | clock from pin<br>clock (Fosc/2) | , TxCK (on the | rising edge)                         |                  |                  |     |

|               |                                    |                                  | 0'             |                                      |                  |                  |     |

| bit 0         | Unimplemen                         | ted: Read as '                   | 0              |                                      |                  |                  |     |

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

HS = Hardware Settable bit

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | R/W-0               | R/W-0               | R/W-0 |

|--------|--------|----------|-------|-----|---------------------|---------------------|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | —   | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32  |

| bit 15 |        |          |       |     |                     |                     | bit 8 |

| R/W-0  | R/W-0, HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|-----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT  | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |        |          |          |          |          | bit 0    |

| Legenu.    |                                                                                                               |                                             |                                   |

|------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|

| R = Read   | able bit W = Writable bit                                                                                     | U = Unimplemented bit,                      | read as '0'                       |

| -n = Value | e at POR '1' = Bit is set                                                                                     | '0' = Bit is cleared                        | x = Bit is unknown                |

|            |                                                                                                               |                                             |                                   |

| bit 15     | FLTMD: Fault Mode Select bit                                                                                  |                                             |                                   |

|            | 1 = Fault mode is maintained until the                                                                        | Fault source is removed and                 | I the corresponding OCFLTx bit is |

|            | cleared in software<br>0 = Fault mode is maintained until the                                                 | Fault source is removed and                 | a new PWM period starts           |

| bit 14     | FLTOUT: Fault Out bit                                                                                         |                                             |                                   |

|            | 1 = PWM output is driven high on a Fa                                                                         | ault                                        |                                   |

|            | 0 = PWM output is driven low on a Fai                                                                         | ult                                         |                                   |

| bit 13     | FLTTRIEN: Fault Output State Select b                                                                         |                                             |                                   |

|            | <ul> <li>1 = Pin is forced to an output on a Fau</li> <li>0 = Pin I/O condition is unaffected by a</li> </ul> |                                             |                                   |

| bit 12     | OCINV: Output Compare x Invert bit                                                                            | a Fault                                     |                                   |

|            | 1 = OCx output is inverted                                                                                    |                                             |                                   |

|            | 0 = OCx output is not inverted                                                                                |                                             |                                   |

| bit 11     | Unimplemented: Read as '0'                                                                                    |                                             |                                   |

| bit 10-9   | DCB<1:0>: Output Compare x Pulse-V                                                                            | Vidth Least Significant bits <sup>(3)</sup> |                                   |

|            | 11 = Delays OCx falling edge by $3/4$ of                                                                      | •                                           |                                   |

|            | 10 = Delays OCx falling edge by 1/2 of<br>01 = Delays OCx falling edge by 1/4 of                              | -                                           |                                   |

|            | 00 = OCx falling edge occurs at the sta                                                                       | 2                                           |                                   |

| bit 8      | OC32: Cascade Two Output Compare                                                                              | Modules Enable bit (32-bit op               | peration)                         |

|            | 1 = Cascade module operation is enal                                                                          |                                             |                                   |

| h:+ 7      | 0 = Cascade module operation is disa                                                                          |                                             |                                   |

| bit 7      | OCTRIG: Output Compare x Sync/Trig<br>1 = Triggers OCx from source designa                                    | -                                           |                                   |

|            | 0 = Synchronizes OCx with source designation                                                                  |                                             | its                               |

| bit 6      | TRIGSTAT: Timer Trigger Status bit                                                                            |                                             |                                   |

|            | 1 = Timer source has been triggered a                                                                         |                                             |                                   |

|            | 0 = Timer source has not been trigger                                                                         | -                                           |                                   |

| bit 5      | <b>OCTRIS:</b> Output Compare x Output Pi                                                                     | n Direction Select bit                      |                                   |

|            | <ul> <li>1 = OCx pin is tri-stated</li> <li>0 = Output Compare x peripheral is con</li> </ul>                 | anected to the OCx nin                      |                                   |

|            |                                                                                                               |                                             |                                   |

| Note 1:    | Do not use an output compare module as i equivalent SYNCSELx setting.                                         | ts own trigger source, either t             | by selecting this mode or another |

| 2:         | Use these inputs as trigger sources only ar                                                                   | nd never as Sync sources.                   |                                   |

| 3:         | These bits affect the rising edge when OCI                                                                    | NV = 1. The bits have no effe               | ct when the OCMx bits             |

|            | (OCxCON1<2:0>) = 001.                                                                                         |                                             |                                   |

Legend:

REGISTER 16-1:

#### R/W-0 U-0 R/W-0 U-0 U-0 R-0, HSC R-0, HSC R-0, HSC SPIEN SPIBEC0 SPISIDL SPIBEC2 SPIBEC1 bit 15 bit 8 R-0, HSC R/C-0, HS R/W-0, HSC R/W-0 R/W-0 R/W-0 R-0, HSC R-0, HSC SPIROV SPIRBF SRMPT SRXMPT SISEL2 SISEL1 SISEL0 SPITBF bit 7 bit 0 HS = Hardware Settable bit HSC = Hardware Settable/Clearable bit Legend: C = Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set -n = Value at POR '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPI transfers pending. Slave mode: Number of SPI transfers unread. bit 7 SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) 1 = SPIx Shift register is empty and ready to send or receive 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit 1 = A new byte/word is completely received and discarded (the user software has not read the previous data in the SPI1BUF register) 0 = No overflow has occurred bit 5 **SRXMPT:** SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode) 1 = Receive FIFO is empty 0 = Receive FIFO is not empty bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode) 111 = Interrupt when SPIx transmit buffer is full (SPITBF bit is set) 110 = Interrupt when last bit is shifted into SPIxSR; as a result, the TX FIFO is empty 101 = Interrupt when the last bit is shifted out of SPIxSR; now the transmit is complete 100 = Interrupt when one data byte is shifted into the SPIxSR: as a result, the TX FIFO has one open spot 011 = Interrupt when SPIx receive buffer is full (SPIRBF bit is set) 010 = Interrupt when SPIx receive buffer is 3/4 or more full 001 = Interrupt when data is available in receive buffer (SRMPT bit is set) 000 = Interrupt when the last data in the receive buffer is read; as a result, the buffer is empty (SRXMPT bit is set)

SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC     | R-0, HSC         | U-0                                           | U-0              | U-0                           | R/C-0, HS        | R-0, HSC                         | R-0, HSC               |

|--------------|------------------|-----------------------------------------------|------------------|-------------------------------|------------------|----------------------------------|------------------------|

| ACKSTAT      | TRSTAT           | —                                             |                  | —                             | BCL              | GCSTAT                           | ADD10                  |

| bit 15       |                  |                                               |                  |                               |                  |                                  | bit 8                  |

|              |                  |                                               |                  |                               |                  |                                  |                        |

| R/C-0, HS    | R/C-0, HS        | R-0, HSC                                      | R/C-0, HSC       | R/C-0, HSC                    | R-0, HSC         | R-0, HSC                         | R-0, HSC               |

| IWCOL        | I2COV            | D/A                                           | Р                | S                             | R/W              | RBF                              | TBF                    |

| bit 7        |                  |                                               |                  |                               |                  |                                  | bit C                  |

| Legend:      |                  | C = Clearabl                                  | e hit            | HS = Hardwar                  | e Settable bit   | HSC = Hardware S                 | Settable/Clearable bit |

| R = Readat   | ole hit          | W = Writable                                  |                  | U = Unimplem                  |                  |                                  |                        |

| -n = Value a |                  | '1' = Bit is se                               |                  | '0' = Bit is clear            |                  | x = Bit is unknown               |                        |

|              |                  | 1 - Dit 13 30                                 |                  |                               |                  |                                  |                        |

| bit 15       | ACKSTAT:         | Acknowledge                                   | e Status bit     |                               |                  |                                  |                        |

|              |                  | was detected                                  |                  |                               |                  |                                  |                        |

|              |                  | as detected la                                |                  |                               |                  |                                  |                        |

|              |                  |                                               |                  | Acknowledge.                  |                  |                                  |                        |

| bit 14       |                  | ransmit Statu<br>rating as I <sup>2</sup> C I |                  | cable to master               | transmit oner    | ration)                          |                        |

|              |                  | transmit is in                                |                  |                               | transmit oper    |                                  |                        |

|              |                  | transmit is no                                | · • ·            | ,                             |                  |                                  |                        |

|              | Hardware is      | s set at the beg                              | jinning of the r | master transmis               | sion; hardware   | is clear at the end of           | slave Acknowledge      |

| bit 13-11    | Unimplem         | ented: Read                                   | <b>as</b> '0'    |                               |                  |                                  |                        |

| bit 10       | BCL: Mast        | er Bus Collisi                                | on Detect bit    |                               |                  |                                  |                        |

|              |                  |                                               | een detected     | d during a mast               | er operation     |                                  |                        |

|              | 0 = No coll      | ision<br>s set at the d                       | otoption of a    | hua colligion                 |                  |                                  |                        |

| bit 9        |                  | Seneral Call S                                |                  |                               |                  |                                  |                        |

| DIL 9        |                  | al call address                               |                  | d                             |                  |                                  |                        |

|              |                  | al call address                               |                  |                               |                  |                                  |                        |

|              | Hardware i       | s set when a                                  | n address ma     | atches the gene               | eral call addres | s; hardware is clea              | ar at Stop detection.  |

| bit 8        | <b>ADD10:</b> 10 | -Bit Address                                  | Status bit       |                               |                  |                                  |                        |

|              |                  | address was r                                 |                  |                               |                  |                                  |                        |

|              |                  | address was r                                 |                  | uto of the motok              | ad 10 bit addr   | ana hardwara ia ala              | ar at Stop detection   |

| bit 7        |                  | Cx Write Coll                                 |                  | •                             |                  | ess, naioware is cle             | ar at Stop detection   |

| DIL 7        |                  |                                               |                  |                               | d because the    | e I <sup>2</sup> C module is bus | M                      |

|              | 0 = No coll      |                                               |                  | in register falle             |                  |                                  | y                      |

|              |                  |                                               | currence of a    | a write to I2CxT              | RN while bus     | y (cleared by softwa             | are).                  |

| bit 6        | 12COV: 12C       | Cx Receive O                                  | verflow Flag     | bit                           |                  |                                  |                        |

|              | -                |                                               | while the I20    | CxRCV register                | is still holding | the previous byte                |                        |

|              | 0 = No ove       |                                               | lomat to tran    |                               |                  | laarad by aaffwara)              |                        |

| bit 5        |                  |                                               |                  | ng as I <sup>2</sup> C slave  |                  | leared by software)              |                        |

| bit 5        |                  | es that the las                               |                  |                               | )                |                                  |                        |

|              |                  |                                               |                  | ed was data<br>ed was the dev | vice address     |                                  |                        |

|              |                  |                                               |                  |                               |                  | a write to I2CxTRN               | or by reception of a   |

|              | slave byte.      |                                               |                  |                               |                  |                                  |                        |

# REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

| R/W-0               | R/W-0                                                                                                                                      | R/W-0                                                                                                                      | R/W-0                                            | r-0                                                    | U-0                     | R/W-0           | R/W-0          |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|-------------------------|-----------------|----------------|--|

| ASEN <sup>(1)</sup> | LPEN                                                                                                                                       | CTMREQ                                                                                                                     | BGREQ                                            | r                                                      |                         | ASINT1          | ASINT0         |  |

| bit 15              |                                                                                                                                            |                                                                                                                            |                                                  |                                                        |                         |                 | bit            |  |

| U-0                 | U-0                                                                                                                                        | U-0                                                                                                                        | U-0                                              | R/W-0                                                  | R/W-0                   | R/W-0           | R/W-0          |  |

| _                   | —                                                                                                                                          | —                                                                                                                          |                                                  | WM1                                                    | WM0                     | CM1             | CM0            |  |

| bit 7               |                                                                                                                                            |                                                                                                                            |                                                  |                                                        |                         |                 | bit            |  |

| Legend:             |                                                                                                                                            | r = Reserved                                                                                                               | bit                                              |                                                        |                         |                 |                |  |

| R = Readabl         | e bit                                                                                                                                      | W = Writable bit U = Unimplemented bit, read as '0'                                                                        |                                                  |                                                        |                         |                 |                |  |

| -n = Value at       | POR                                                                                                                                        | '1' = Bit is set                                                                                                           |                                                  | '0' = Bit is clea                                      | ared                    | x = Bit is unkr | nown           |  |

| bit 15              | <b>ASEN:</b> Auto-<br>1 = Auto-sca<br>0 = Auto-sca                                                                                         |                                                                                                                            | <sub>(</sub> (1)                                 |                                                        |                         |                 |                |  |

| bit 14              | LPEN: Low-Power Enable bit<br>1 = Returns to Low-Power mode after scan<br>0 = Remains in Full-Power mode after scan                        |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

| bit 13              | 1 = CTMU is                                                                                                                                | TMU Request b<br>s enabled when<br>s not enabled by                                                                        | the A/D is ena                                   | abled and active                                       |                         |                 |                |  |

| bit 12              | <b>BGREQ:</b> Band Gap Request bit<br>1 = Band gap is enabled when the A/D is enabled and active<br>0 = Band gap is not enabled by the A/D |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

| bit 11              | Reserved: Maintain as '0'                                                                                                                  |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

| bit 10              | Unimplemented: Read as '0'                                                                                                                 |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

| bit 9-8             | ASINT<1:0>: Auto-Scan (Threshold Detect) Interrupt Mode bits                                                                               |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

|                     | 10 = Interru                                                                                                                               | pt after a Thresh<br>pt after a valid c<br>pt after a Thresh<br>errupt                                                     | ompare has o                                     | ccurred                                                |                         | compare has c   | occurred       |  |

| bit 7-4             | Unimplemer                                                                                                                                 | nted: Read as '                                                                                                            | )'                                               |                                                        |                         |                 |                |  |

| bit 3-2             | 11 = Reserv<br>10 = Auto-co<br>match,<br>01 = Conver<br>when a                                                                             | Vrite Mode bits<br>ved<br>ompare only (co<br>as defined by th<br>rt and save (cor<br>a match, as defin<br>v operation (con | ne CMx and A<br>oversion result<br>ned by the CM | SINTx bits, occu<br>s are saved to<br>lx bits, occurs) | urs)<br>locations as de | etermined by th | ne register bi |  |

| bit 1-0             | CM<1:0>: Compare Mode bits                                                                                                                 |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

|                     | by the of<br>10 = Inside V<br>corresp<br>01 = Greate                                                                                       | Window mode<br>corresponding bu<br>Window mode (v<br>ponding buffer pa<br>r Than mode (va<br>egister)                      | uffer pair)<br>alid match occ<br>ir)             | urs if the convers                                     | sion result is ins      | side the window | defined by th  |  |

|                     | 00 = Less Than mode (valid match occurs if the result is less than the value in the corresponding buffer register)                         |                                                                                                                            |                                                  |                                                        |                         |                 |                |  |

#### Note 1: When using auto-scan with Threshold Detect (ASEN = 1), do not configure the sample clock source to Auto-Convert mode (SSRCx = 7). Any other available SSRCx selection is valid. To use auto-convert as the sample clock source (SSRCx = 7), make sure ASEN is cleared.

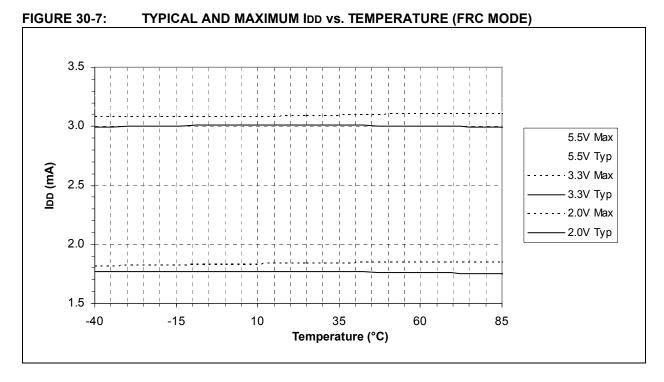

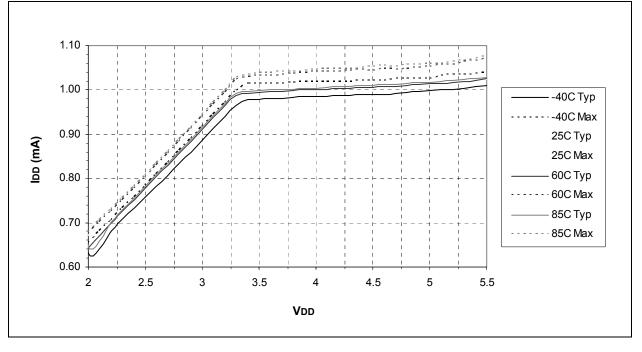

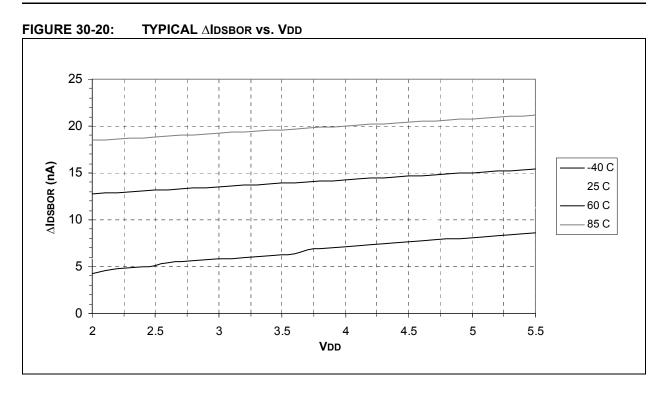

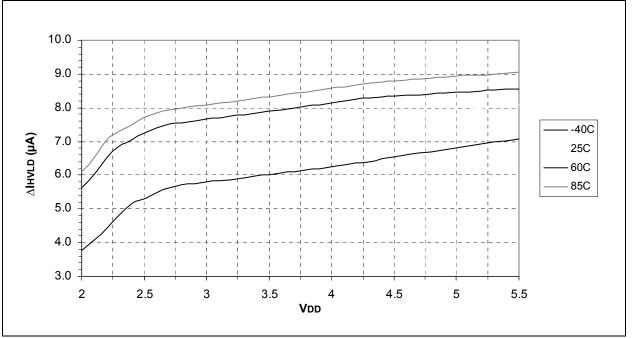

FIGURE 30-8: TYPICAL AND MAXIMUM lidle vs. Vdd (FRC MODE)

NOTES:

# 31.0 PACKAGING INFORMATION

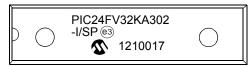

# 31.1 Package Marking Information

### 20-Lead PDIP (300 mil)

### 28-Lead SPDIP (.300")

### Example

### 20-Lead SSOP (5.30 mm)

28-Lead SSOP (5.30 mm)

Example

## Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3                                                                                                                                                | Product-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ()<br>can be found on the outer packaging for this package. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:   | In the event the full Microchip part number cannot be marked on will be carried over to the next line, thus limiting the number of characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                           |

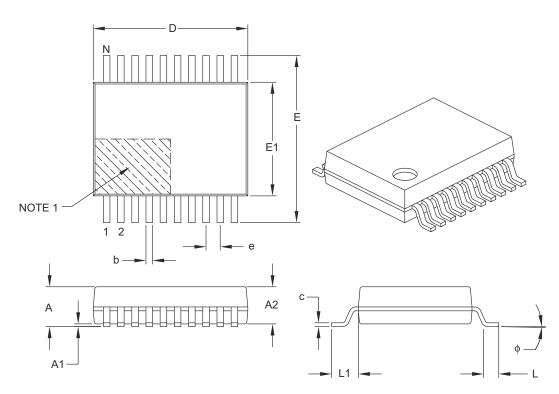

## 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 5    |

|--------------------------|------------------|----------|-------------|------|

| Dimer                    | Dimension Limits |          | NOM         | MAX  |

| Number of Pins           | Ν                |          | 20          |      |

| Pitch                    | е                | 0.65 BSC |             |      |

| Overall Height           | А                | -        | -           | 2.00 |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85 |

| Standoff                 | A1               | 0.05     | -           | -    |

| Overall Width            | E                | 7.40     | 7.80        | 8.20 |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60 |

| Overall Length           | D                | 6.90     | 7.20        | 7.50 |

| Foot Length              | L                | 0.55     | 0.75        | 0.95 |

| Footprint                | L1               | 1.25 REF |             |      |

| Lead Thickness           | С                | 0.09     | -           | 0.25 |

| Foot Angle               | φ                | 0°       | 4°          | 8°   |

| Lead Width               | b                | 0.22     | _           | 0.38 |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

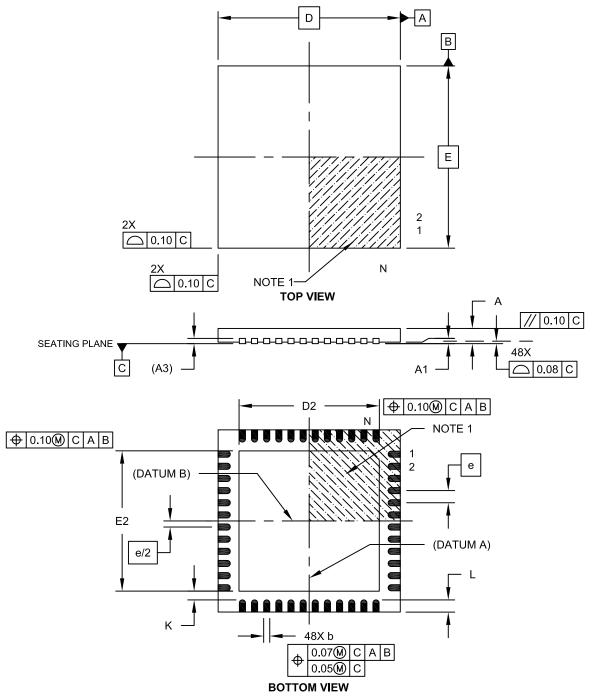

# 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

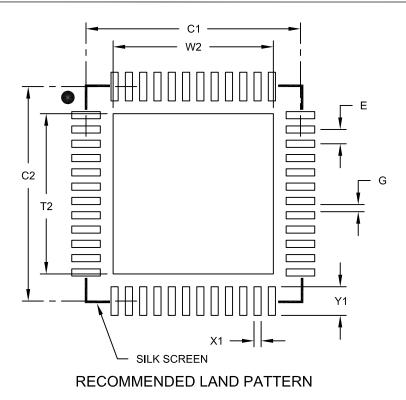

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

|                            | Units      |      | MILLIMETER | S    |

|----------------------------|------------|------|------------|------|

| Dimensio                   | MIN        | NOM  | MAX        |      |

| Contact Pitch              | E 0.40 BSC |      |            |      |

| Optional Center Pad Width  | W2         |      |            | 4.45 |

| Optional Center Pad Length | T2         |      |            | 4.45 |

| Contact Pad Spacing        | C1         |      | 6.00       |      |

| Contact Pad Spacing        | C2         |      | 6.00       |      |

| Contact Pad Width (X28)    | X1         |      |            | 0.20 |

| Contact Pad Length (X28)   | Y1         |      |            | 0.80 |

| Distance Between Pads      | G          | 0.20 |            |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A