Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka304-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

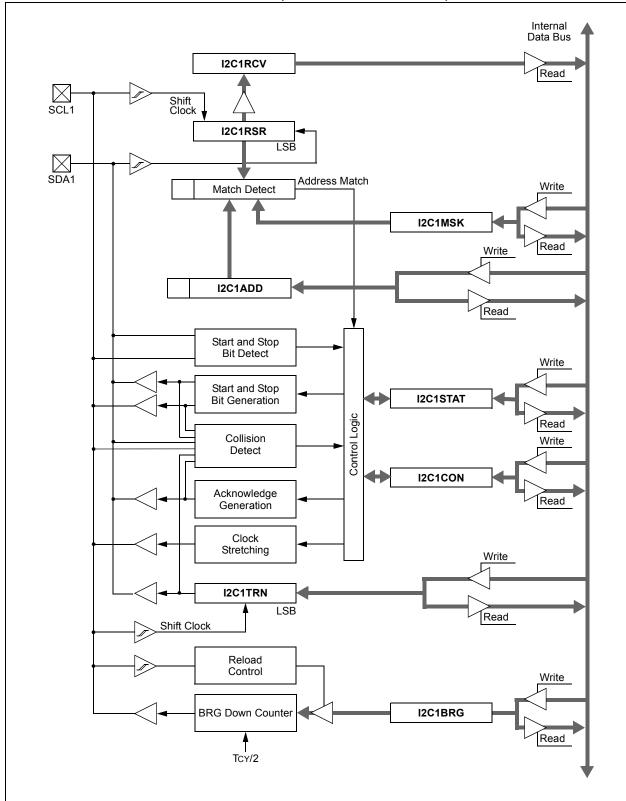

#### TABLE 4-9: I2Cx REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 | —       | _      | _       | _      | _      | _      | —      | _     |       |       |       | I2CF  | RCV   |       |       |       | 0000          |

| I2C1TRN   | 0202 | _       | _      | _       | —      | _      | _      | _      | _     |       |       |       | I2CT  | RN    |       |       |       | OOFF          |

| I2C1BRG   | 0204 | _       | _      | _       | —      | _      | _      | _      | _     |       |       |       | I2CE  | BRG   |       |       |       | 0000          |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | _       | _      | _       | —      | _      | _      | I2CADD |       |       |       |       |       | 0000  |       |       |       |               |

| I2C1MSK   | 020C | —       | _      | _       | —      | —      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

| I2C2RCV   | 0210 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CF  | RCV   |       |       |       | 0000          |

| I2C2TRN   | 0212 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CT  | RN    |       |       |       | OOFF          |

| I2C2BRG   | 0214 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CE  | BRG   |       |       |       | 0000          |

| I2C2CON   | 0216 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT  | 0218 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD   | 021A | _       |        | _       | _      |        | _      | I2CADD |       |       |       |       |       | 0000  |       |       |       |               |

| I2C2MSK   | 021C | _       |        | _       | _      | _      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: UARTx REGISTER MAP

|              |      | 0/11/1/  |        |          |        |        |        |       |           |          |          |       |       |       |        |        |       |               |

|--------------|------|----------|--------|----------|--------|--------|--------|-------|-----------|----------|----------|-------|-------|-------|--------|--------|-------|---------------|

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE       | 0220 | UARTEN   | _      | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0      | WAKE     | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT      | URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | U1TXREG  |        |          |        |        |        |       | XXXX      |          |          |       |       |       |        |        |       |               |

| U1RXREG      | 0226 | —        |        | —        |        | _      |        | _     | U1RXREG   |          |          |       |       |       | 0000   |        |       |               |

| U1BRG        | 0228 |          |        |          |        |        |        |       | I         | BRG      |          |       |       |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0      | WAKE     | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF | TRMT      | URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _        | _      | _        | —      | _      | _      | _     | – U2TXREG |          |          |       |       |       |        | XXXX   |       |               |

| U2RXREG      | 0236 | —        |        | —        |        | _      |        | _     | U2RXREG   |          |          |       |       |       | 0000   |        |       |               |

| U2BRG        | 0238 |          | BRG    |          |        |        |        |       |           |          | 0000     |       |       |       |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

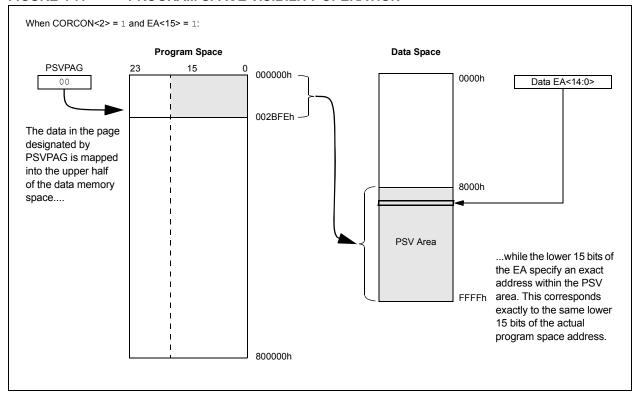

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into a 16K word page (in PIC24FV16KA3XX devices) and a 32K word page (in PIC24FV32KA3XX devices) of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space EA is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

#### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|       | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearabl   | e bit            |

|----------------------|------------------------|--------------------------|------------------|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit         | W = Writable bit |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, I | read as '0'      |

| bit 15   | WR: Write Control bit                                                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once the operation is complete.</li> <li>0 = Program or erase operation is complete and inactive</li> </ul>               |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                                                     |

|          | <ul><li>1 = Enables Flash program/erase operations</li><li>0 = Inhibits Flash program/erase operations</li></ul>                                                                                                                                           |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                                                                                                                                                                       |

|          | <ul> <li>1 = An improper program or erase sequence attempt, or termination, has occurred (bit is set automatically on any set attempt of the WR bit)</li> <li>0 = The program or erase operation completed normally</li> </ul>                             |

| bit 12   | PGMONLY: Program Only Enable bit <sup>(4)</sup>                                                                                                                                                                                                            |

| bit 11-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                 |

| bit 6    | ERASE: Erase/Program Enable bit                                                                                                                                                                                                                            |

|          | <ul> <li>1 = Performs the erase operation specified by NVMOP&lt;5:0&gt; on the next WR command</li> <li>0 = Performs the program operation specified by NVMOP&lt;5:0&gt; on the next WR command</li> </ul>                                                 |

| bit 5-0  | NVMOP<5:0>: Programming Operation Command Byte bits <sup>(1)</sup>                                                                                                                                                                                         |

|          | Erase Operations (when ERASE bit is '1'):                                                                                                                                                                                                                  |

|          | 1010xx = Erases entire boot block (including code-protected boot block) <sup>(2)</sup><br>1001xx = Erases entire memory (including boot block, configuration block, general block) <sup>(2)</sup><br>011010 = Erases 4 rows of Flash memory <sup>(3)</sup> |

|          | 011001 = Erases 2 rows of Flash memory <sup>(3)</sup>                                                                                                                                                                                                      |

|          | 011000 = Erases 1 row of Flash memory <sup>(3)</sup>                                                                                                                                                                                                       |

|          | 0101xx = Erases entire configuration block (except code protection bits)                                                                                                                                                                                   |

|          | 0100xx = Erases entire data EEPROM <sup>(4)</sup><br>0011xx = Erases entire general memory block programming operations                                                                                                                                    |

|          | 0011xx = Erases entire general memory block programming operations<br>$0001xx = \text{Writes 1 row of Flash memory (when ERASE bit is '0')^{(3)}$                                                                                                          |

| Note 1:  | All other combinations of NVMOP<5:0> are no operation.                                                                                                                                                                                                     |

| 2:       | These values are available in ICSP <sup>™</sup> mode only. Refer to the device programming specification.                                                                                                                                                  |

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM.

#### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INT0IF: External Interrupt 0 Flag Status bit              |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | R/W-0, HS | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----------|-----|-----|-----|-----------|-----------|

| —     | —   | IC3IF     | —   | —   |     | SPI2IF    | SPF2IF    |

| bit 7 |     |           |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-6 | Unimplemented: Read as '0'                               |

|----------|----------------------------------------------------------|

| bit 5    | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                       |

|          | 0 = Interrupt request has not occurred                   |

| bit 4-2  | Unimplemented: Read as '0'                               |

| bit 1    | SPI2IF: SPI2 Event Interrupt Flag Status bit             |

|          | 1 = Interrupt request has occurred                       |

|          | 0 = Interrupt request has not occurred                   |

| bit 0    | SPF2IF: SPI2 Fault Interrupt Flag Status bit             |

|          | 1 = Interrupt request has occurred                       |

|          | 0 = Interrupt request has not occurred                   |

| U-0           | U-0           | U-0                | U-0              | U-0               | U-0              | U-0                | U-0   |  |

|---------------|---------------|--------------------|------------------|-------------------|------------------|--------------------|-------|--|

| _             | —             | —                  | _                | —                 | —                | —                  | —     |  |

| bit 15        |               |                    |                  |                   |                  |                    | bit 8 |  |

|               |               |                    |                  |                   |                  |                    |       |  |

| U-0           | R/W-1         | R/W-0              | R/W-0            | U-0               | U-0              | U-0                | U-0   |  |

| —             | IC3IP2        | IC3IP1             | IC3IP0           | —                 | —                | —                  | —     |  |

| bit 7         |               |                    | •                |                   |                  | •                  | bit 0 |  |

|               |               |                    |                  |                   |                  |                    |       |  |

| Legend:       |               |                    |                  |                   |                  |                    |       |  |

| R = Readable  | e bit         | W = Writable       | bit              | U = Unimplen      | nented bit, read | l as '0'           |       |  |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

| bit 15-7      | Unimplemen    | ted: Read as '     | )'               |                   |                  |                    |       |  |

| bit 6-4       | -             |                    |                  | nt Interrupt Prio | rity bite        |                    |       |  |

| DIL 0-4       |               |                    |                  | -                 | They bits        |                    |       |  |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | (interrupt)       |                  |                    |       |  |

|               | •             |                    |                  |                   |                  |                    |       |  |

|               | •             |                    |                  |                   |                  |                    |       |  |

|               | 001 = Interru |                    |                  |                   |                  |                    |       |  |

|               | 000 = Interru | pt source is dis   | abled            |                   |                  |                    |       |  |

|               |               |                    |                  |                   |                  |                    |       |  |

#### REGISTER 8-26: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

bit 3-0 Unimplemented: Read as '0'

NOTES:

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

|                                           |

#### 9.5 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FV32KA304 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 9-4). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIVx bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the ROSEL bit is not also set, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

NOTES:

#### FIGURE 17-1: I<sup>2</sup>C<sup>™</sup> BLOCK DIAGRAM (I2C1 MODULE IS SHOWN)

| R/W-0        | U-0                  | R/W-0                                                               | R/W-1, HC         | R/W-0                         | R/W-0                     | R/W-0             | R/W-0          |  |  |  |  |

|--------------|----------------------|---------------------------------------------------------------------|-------------------|-------------------------------|---------------------------|-------------------|----------------|--|--|--|--|

| I2CEN        |                      | I2CSIDL                                                             | SCLREL            | IPMIEN                        | A10M                      | DISSLW            | SMEN           |  |  |  |  |

| bit 15       |                      | -                                                                   | •                 |                               | ·                         |                   | bit 8          |  |  |  |  |

| R/W-0        | R/W-0                | R/W-0                                                               | R/W-0, HC         | R/W-0, HC                     | R/W-0, HC                 | R/W-0, HC         | R/W-0, HC      |  |  |  |  |

| GCEN         | STREN                | ACKDT                                                               | ACKEN             | RCEN                          | PEN                       | RSEN              | SEN            |  |  |  |  |

| bit 7        |                      |                                                                     |                   |                               |                           |                   | bit C          |  |  |  |  |

| Legend:      |                      | HC = Hardwa                                                         | re Clearable bit  |                               |                           |                   |                |  |  |  |  |

| R = Readat   | le hit               | W = Writable                                                        |                   |                               | nented bit, read          | as '0'            |                |  |  |  |  |

| -n = Value a |                      | 1' = Bit is set                                                     | JIL               | '0' = Bit is clea             |                           | x = Bit is unkn   |                |  |  |  |  |

|              | al FUR               | I - DILIS SEL                                                       |                   |                               | areu                      |                   | OWIT           |  |  |  |  |

| bit 15       | <b>12CEN:</b> 12Cx   | Enable bit                                                          |                   |                               |                           |                   |                |  |  |  |  |

|              |                      | he I2Cx module<br>the I2Cx module                                   |                   |                               |                           |                   | 3              |  |  |  |  |

| bit 14       |                      | ited: Read as '0                                                    |                   | are controlled                | by port functio           | 10                |                |  |  |  |  |

| bit 13       | -                    | x Stop in Idle M                                                    |                   |                               |                           |                   |                |  |  |  |  |

|              |                      | ues module ope                                                      |                   | e device enters               | an Idle mode              |                   |                |  |  |  |  |

|              |                      | s module opera                                                      |                   |                               |                           |                   |                |  |  |  |  |

| bit 12       | SCLREL: SC           | Lx Release Co                                                       | ntrol bit (when c | operating as I <sup>2</sup> 0 | C slave)                  |                   |                |  |  |  |  |

|              |                      | 1 = Releases SCLx clock<br>0 = Holds SCLx clock low (clock stretch) |                   |                               |                           |                   |                |  |  |  |  |

|              | <u>If STREN = 1:</u> |                                                                     |                   |                               |                           |                   |                |  |  |  |  |

|              |                      | V (i.e., software                                                   |                   |                               |                           |                   |                |  |  |  |  |

|              | lf STREN = 0         | eginning of the                                                     | slave transmiss   | ion. Hardware                 | is clear at the e         | end of slave rec  | eption.        |  |  |  |  |

|              |                      | <u>.</u><br>6 (i.e., software                                       | may only write    | '1' to release                | clock). Hardwa            | re is clear at th | e beainnina o  |  |  |  |  |

|              | slave transmi        |                                                                     |                   |                               |                           |                   | 5              |  |  |  |  |

| bit 11       | IPMIEN: Intel        | lligent Periphera                                                   | al Management     | Interface (IPM                | I) Enable bit             |                   |                |  |  |  |  |

|              |                      | port mode is en<br>port mode is dis                                 |                   | esses are Ackn                | owledged                  |                   |                |  |  |  |  |

| bit 10       | A10M: 10-Bit         | Slave Address                                                       | ing bit           |                               |                           |                   |                |  |  |  |  |

|              | -                    | is a 10-bit slav                                                    |                   |                               |                           |                   |                |  |  |  |  |

|              | 0 = I2CxADD          | is a 7-bit slave                                                    | address           |                               |                           |                   |                |  |  |  |  |

| bit 9        |                      | able Slew Rate                                                      |                   |                               |                           |                   |                |  |  |  |  |

|              |                      | control is disab                                                    |                   |                               |                           |                   |                |  |  |  |  |

| bit 8        | SMEN: SMBI           | SMEN: SMBus Input Levels bit                                        |                   |                               |                           |                   |                |  |  |  |  |

|              |                      | /O pin threshold                                                    |                   | h the SMBus s                 | pecification              |                   |                |  |  |  |  |

|              |                      | the SMBus inpu                                                      |                   | _                             |                           |                   |                |  |  |  |  |

| bit 7        |                      | ral Call Enable                                                     | · ·               | •                             | ,                         |                   |                |  |  |  |  |

|              |                      | interrupt when                                                      | a general call a  | address is rece               | ived in the I2C           | xRSR (module      | is enabled for |  |  |  |  |

|              | 0 = General          | i)<br>call address is o                                             | disabled          |                               |                           |                   |                |  |  |  |  |

| bit 6        |                      | x Clock Stretch                                                     |                   | en operating as               | s I <sup>2</sup> C slave) |                   |                |  |  |  |  |

|              |                      | Inction with the                                                    | -                 | on operating at               |                           |                   |                |  |  |  |  |

|              | 1 = Enables s        | software or rece                                                    | ives clock strete | •                             |                           |                   |                |  |  |  |  |

|              |                      | -                                                                   | eives clock stret |                               |                           |                   |                |  |  |  |  |

#### 20.1.3 DATA SHIFT DIRECTION

The LENDIAN bit (CRCCON1<3>) is used to control the shift direction. By default, the CRC will shift data through the engine, MSb first. Setting LENDIAN (= 1) causes the CRC to shift data, LSb first. This setting allows better integration with various communication schemes and removes the overhead of reversing the bit order in software. Note that this only changes the direction of the data that is shifted into the engine. The result of the CRC calculation will still be a normal CRC result, not a reverse CRC result.

#### 20.1.4 INTERRUPT OPERATION

The module generates an interrupt that is configurable by the user for either of two conditions. If CRCISEL is '0', an interrupt is generated when the VWORD<4:0> bits make a transition from a value of '1' to '0'. If CRCISEL is '1', an interrupt will be generated after the CRC operation finishes and the module sets the CRCGO bit to '0'. Manually setting CRCGO to '0' will not generate an interrupt.

#### 20.1.5 TYPICAL OPERATION

To use the module for a typical CRC calculation:

- 1. Set the CRCEN bit to enable the module.

- 2. Configure the module for the desired operation:

- a) Program the desired polynomial using the CRCXORL and CRCXORH registers, and the PLEN<4:0> bits.

- b) Configure the data width and shift direction using the DWIDTHx and LENDIAN bits.

- c) Select the desired interrupt mode using the CRCISEL bit.

- 3. Preload the FIFO by writing to the CRCDATL and CRCDATH registers until the CRCFUL bit is set or no data is left.

- 4. Clear old results by writing 00h to CRCWDATL and CRCWDATH. CRCWDAT can also be left unchanged to resume a previously halted calculation.

- 5. Set the CRCGO bit to start calculation.

- 6. Write the remaining data into the FIFO as space becomes available.

- When the calculation completes, CRCGO is automatically cleared. An interrupt will be generated if CRCISEL = 1.

- 8. Read CRCWDATL and CRCWDATH for the result of the calculation.

#### 20.2 Registers

There are eight registers associated with the module:

- CRCCON1

- CRCCON2

- CRCXORL

- CRCXORH

- CRCDATL

- CRCDATH

- CRCWDATL

- CRCWDATH

The CRCCON1 and CRCCON2 registers (Register 20-1 and Register 20-2) control the operation of the module, and configure the various settings. The CRCXOR registers (Register 20-3 and Register 20-4) select the polynomial terms to be used in the CRC equation. The CRCDAT and CRCWDAT registers are each register pairs that serve as buffers for the double-word, input data and CRC processed output, respectively.

#### REGISTER 20-2: CRCCON2: CRC CONTROL REGISTER 2

| U-0           | U-0                                                                       | U-0              | R/W-0       | R/W-0             | R/W-0            | R/W-0              | R/W-0   |  |  |

|---------------|---------------------------------------------------------------------------|------------------|-------------|-------------------|------------------|--------------------|---------|--|--|

| —             | —                                                                         | —                | DWIDTH4     | DWIDTH3           | DWIDTH2          | DWIDTH1            | DWIDTH0 |  |  |

| bit 15        |                                                                           |                  |             |                   |                  | •                  | bit 8   |  |  |

|               |                                                                           |                  |             |                   |                  |                    |         |  |  |

| U-0           | U-0                                                                       | U-0              | R/W-0       | R/W-0             | R/W-0            | R/W-0              | R/W-0   |  |  |

| _             |                                                                           |                  | PLEN4       | PLEN3             | PLEN2            | PLEN1              | PLEN0   |  |  |

| bit 7         |                                                                           |                  |             |                   |                  | •                  | bit 0   |  |  |

|               |                                                                           |                  |             |                   |                  |                    |         |  |  |

| Legend:       |                                                                           |                  |             |                   |                  |                    |         |  |  |

| R = Readable  | e bit                                                                     | W = Writable     | bit         | U = Unimplem      | nented bit, read | l as '0'           |         |  |  |

| -n = Value at | POR                                                                       | '1' = Bit is set |             | '0' = Bit is clea | ared             | x = Bit is unknown |         |  |  |

|               |                                                                           |                  |             |                   |                  |                    |         |  |  |

| bit 15-13     | Unimplemen                                                                | ted: Read as '   | 0'          |                   |                  |                    |         |  |  |

| bit 12-8      | DWIDTH<4:0                                                                | >: Data Width    | Select bits |                   |                  |                    |         |  |  |

|               | Defines the width of the data word (Data Word Width = (DWIDTH<4:0>) + 1). |                  |             |                   |                  |                    |         |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits Defines the length of the CRC polynomial (Polynomial Length = (PLEN<4:0>) + 1).

#### REGISTER 23-1: CMxCON: COMPARATOR x CONTROL REGISTERS (CONTINUED)

| bit 4   | CREF: Comparator x Reference Select bits (non-inverting input)                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Non-inverting input connects to the internal CVREF voltage</li> <li>0 = Non-inverting input connects to the CxINA pin</li> </ul> |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                    |

| bit 1-0 | CCH<1:0>: Comparator x Channel Select bits                                                                                                    |

|         | 11 = Inverting input of the comparator connects to VBG                                                                                        |

|         | 10 = Inverting input of the comparator connects to the CxIND pin                                                                              |

|         |                                                                                                                                               |

|         | 01 = Inverting input of the comparator connects to the CxINC pin                                                                              |

00 = Inverting input of the comparator connects to the CxINB pin

#### REGISTER 23-2: CMSTAT: COMPARATOR x MODULE STATUS REGISTER

| R/W-0        | U-0 | U-0 | U-0 | U-0 | R-0, HSC | R-0, HSC | R-0, HSC |  |

|--------------|-----|-----|-----|-----|----------|----------|----------|--|

| CMIDL        | —   | —   | —   | _   | C3EVT    | C2EVT    | C1EVT    |  |

| bit 15 bit 8 |     |     |     |     |          |          |          |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0, HSC | R-0, HSC | R-0, HSC |

|-------|-----|-----|-----|-----|----------|----------|----------|

| —     | —   | —   | —   | —   | C3OUT    | C2OUT    | C1OUT    |

| bit 7 |     |     |     |     |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15    | <ul> <li>CMIDL: Comparator x Stop in Idle Mode bit</li> <li>1 = Comparator interrupts are disabled in Idle mode; enabled comparators remain operational</li> <li>0 = Continues operation of all enabled comparators in Idle mode</li> </ul> |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-11 | Unimplemented: Read as '0'                                                                                                                                                                                                                  |

| bit 10    | C3EVT: Comparator 3 Event Status bit (read-only)                                                                                                                                                                                            |

|           | Shows the current event status of Comparator 3 (CM3CON<9>).                                                                                                                                                                                 |

| bit 9     | C2EVT: Comparator 2 Event Status bit (read-only)                                                                                                                                                                                            |

|           | Shows the current event status of Comparator 2 (CM2CON<9>).                                                                                                                                                                                 |

| bit 8     | C1EVT: Comparator 1 Event Status bit (read-only)                                                                                                                                                                                            |

|           | Shows the current event status of Comparator 1 (CM1CON<9>).                                                                                                                                                                                 |

| bit 7-3   | Unimplemented: Read as '0'                                                                                                                                                                                                                  |

| bit 2     | C3OUT: Comparator 3 Output Status bit (read-only)                                                                                                                                                                                           |

|           | Shows the current output of Comparator 3 (CM3CON<8>).                                                                                                                                                                                       |

| bit 1     | C2OUT: Comparator 2 Output Status bit (read-only)                                                                                                                                                                                           |

|           | Shows the current output of Comparator 2 (CM2CON<8>).                                                                                                                                                                                       |

| bit 0     | C1OUT: Comparator 1 Output Status bit (read-only)                                                                                                                                                                                           |

|           | Shows the current output of Comparator 1 (CM1CON<8>).                                                                                                                                                                                       |

|           |                                                                                                                                                                                                                                             |

| R/P-1                | R/P-1                             | R/P-1                                | R/P-1                  | R/P-1                | R/P-1                 | R/P-1                     | R/P-1             |

|----------------------|-----------------------------------|--------------------------------------|------------------------|----------------------|-----------------------|---------------------------|-------------------|

| MCLRE <sup>(2)</sup> | BORV1 <sup>(3)</sup>              | BORV0 <sup>(3)</sup>                 | I2C1SEL <sup>(1)</sup> | PWRTEN               | RETCFG <sup>(1)</sup> | BOREN1                    | BOREN0            |

| bit 7                |                                   |                                      |                        |                      |                       |                           | bit (             |

|                      |                                   |                                      |                        |                      |                       |                           |                   |

| Legend:              |                                   |                                      |                        |                      |                       |                           |                   |

| R = Reada            | able bit                          | P = Programr                         | nable bit              | U = Unimplen         | nented bit, read      | as '0'                    |                   |

| -n = Value           | at POR                            | '1' = Bit is set                     |                        | '0' = Bit is clea    | ared                  | x = Bit is unkr           | nown              |

|                      |                                   |                                      | ··(2)                  |                      |                       |                           |                   |

| bit 7                |                                   | R Pin Enable b                       |                        | iaablad              |                       |                           |                   |

|                      |                                   | is enabled; RA pin is enabled;       |                        |                      |                       |                           |                   |

| bit 6-5              |                                   | Brown-out Rese                       |                        |                      |                       |                           |                   |

|                      |                                   | ut Reset is set t                    |                        |                      |                       |                           |                   |

|                      | 10 <b>= Brown-o</b>               |                                      |                        | 0                    |                       |                           |                   |

|                      |                                   | ut Reset is set t                    | •                      | •                    | »••••••••••           |                           |                   |

|                      |                                   | e protection on                      |                        | a – "zero powe       | r" is selected        |                           |                   |

| bit 4                |                                   | ernate I2C1 Pin                      |                        |                      |                       |                           |                   |

|                      |                                   | cation for SCL1,<br>ocation for SCL  |                        |                      |                       |                           |                   |

| bit 3                |                                   | wer-up Timer E                       | •                      |                      |                       |                           |                   |

|                      | 1 = PWRT is e                     | enabled                              |                        |                      |                       |                           |                   |

|                      | 0 = PWRT is c                     | disabled                             |                        |                      |                       |                           |                   |

| bit 2                |                                   | ention Regulate                      |                        | ו bit <sup>(1)</sup> |                       |                           |                   |

|                      |                                   | Regulator is no                      |                        |                      |                       |                           | 0                 |

|                      |                                   | •                                    |                        | -                    | RETEN bit (RCO        | N<12>) during             | Sleep             |

| oit 1-0              |                                   | : Brown-out Re                       |                        |                      | tio dia abla d        |                           |                   |

|                      |                                   | ut Reset is enab<br>it Reset is enab |                        |                      | and disabled in S     | Sleep <sup>,</sup> SBOREN | l bit is disabled |

|                      |                                   | ut Reset is cont                     |                        |                      |                       |                           |                   |

|                      | 00 <b>= Brown-o</b>               | ut Reset is disa                     | bled in hardwa         | re; SBOREN bi        | t is disabled         |                           |                   |

| Note 1:              | This setting only devices.        | / applies to the                     | "FV" devices. 1        | This bit is reser    | ved and should        | be maintained a           | as '1' on "F"     |

| 2:                   | The MCLRE fus<br>user from accide | entally locking o                    | out the device f       | rom the low-vo       | ltage test entry.     | ode entry. This           | prevents a        |

| 3:                   | Refer to Sectio                   |                                      |                        |                      |                       |                           |                   |

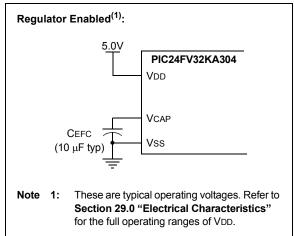

#### 26.2 On-Chip Voltage Regulator

All of the PIC24FV32KA304 family devices power their core digital logic at a nominal 3.0V. This may create an issue for designs that are required to operate at a higher typical voltage, as high as 5.0V. To simplify system design, all devices in the "FV" family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator is always enabled and provides power to the core from the other VDD pins. A low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 26-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is discussed in Section 2.4 "Voltage Regulator Pin (VCAP)", and in Section 29.1 "DC Characteristics".

For "F" devices, the regulator is disabled. Instead, core logic is powered directly from VDD. This allows the devices to operate at an overall lower allowable voltage range (1.8V-3.6V).

#### 26.2.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

For all PIC24FV32KA304 devices, the on-chip regulator provides a constant voltage of 3.2V nominal to the digital core logic. The regulator can provide this level from a VDD of about 3.2V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 3.2V. In order to prevent "brown-out" conditions when the voltage drops too low for the regulator, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD with a typical voltage drop of 150 mV.

When the device enters Tracking mode, it is no longer possible to operate at full speed. To provide information about when the device enters Tracking mode, the on-chip regulator includes a simple, High/Low-Voltage Detect (HLVD) circuit. When VDD drops below full-speed operating voltage, the circuit sets the High/Low-Voltage Detect Interrupt Flag, HLVDIF (IFS4<8>). This can be used to generate an interrupt and put the application into a low-power operational mode or trigger an orderly shutdown. Maximum device speeds as a function of VDD are shown in **Section 29.1 "DC Characteristics"**, in Figure 29-1 and Figure 29-1.

#### 26.2.2 ON-CHIP REGULATOR AND POR

For PIC24FV32KA304 devices, it takes a brief time, designated as TPM, for the Voltage Regulator to generate a stable output. During this time, code execution is disabled. TPM (DC Specification SY71) is applied every time the device resumes operation after any power-down, including Sleep mode.

### FIGURE 26-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

#### 26.3 Watchdog Timer (WDT)

For the PIC24FV32KA304 family of devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranging from 1 ms to 131 seconds, can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

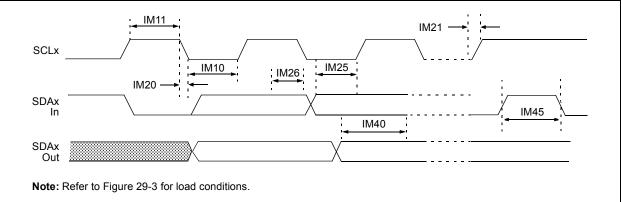

#### TABLE 29-32: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| АС СНА       |         | STICS                          |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                        |  |

|--------------|---------|--------------------------------|---------------------------|-------------------------------------------------------|------|-------|------------------------|--|

| Param<br>No. | Symbol  | Charac                         | teristic                  | Min <sup>(1)</sup>                                    | Max  | Units | Conditions             |  |

| IM10         | TLO:SCL | Clock Low Time                 | 100 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μs    |                        |  |

|              |         |                                | 400 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μS    |                        |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       |      | μS    |                        |  |

| IM11         | THI:SCL | Clock High Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                       |      | μS    |                        |  |

|              |         |                                | 400 kHz mode              | Tcy/2 (BRG + 1)                                       | _    | μS    |                        |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                       | _    | μS    |                        |  |

| IM20         | TF:SCL  | SCL SDAx and SCLx<br>Fall Time | 100 kHz mode              | —                                                     | 300  | ns    | CB is specified to be  |  |

|              |         |                                | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | from 10 to 400 pF      |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | —                                                     | 100  | ns    |                        |  |

| IM21         | TR:SCL  | SDAx and SCLx<br>Rise Time     | 100 kHz mode              | —                                                     | 1000 | ns    | CB is specified to be  |  |

|              |         |                                | 400 kHz mode              | 20 + 0.1 Св                                           | 300  | ns    | from 10 to 400 pF      |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | —                                                     | 300  | ns    |                        |  |

| IM25         | TSU:DAT | Data Input                     | 100 kHz mode              | 250                                                   |      | ns    |                        |  |

|              |         | Setup Time                     | 400 kHz mode              | 100                                                   | _    | ns    |                        |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | 100                                                   | _    | ns    |                        |  |

| IM26         | THD:DAT | Data Input                     | 100 kHz mode              | 0                                                     |      | ns    |                        |  |

|              |         | Hold Time                      | 400 kHz mode              | 0                                                     | 0.9  | μS    |                        |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | 0                                                     | _    | ns    |                        |  |

| IM40         | TAA:SCL | Output Valid                   | 100 kHz mode              | —                                                     | 3500 | ns    |                        |  |

|              |         | from Clock                     | 400 kHz mode              | —                                                     | 1000 | ns    |                        |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | —                                                     |      | ns    |                        |  |

| IM45         | TBF:SDA | Bus Free Time                  | 100 kHz mode              | 4.7                                                   | _    | μS    | Time the bus must be   |  |

|              |         |                                | 400 kHz mode              | 1.3                                                   | _    | μS    | free before a new      |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | 0.5                                                   | —    | μS    | transmission can start |  |

| IM50         | Св      | Bus Capacitive Lo              | bading                    | —                                                     | 400  | pF    |                        |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to **Section 17.3 "Setting Baud Rate When Operating as a Bus Master**" for details.

2: Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

FIGURE 30-46: TYPICAL AlwDT vs. VDD

**∆IWDT (µA)**

Vdd

FIGURE 30-47: TYPICAL AIDSBOR vs. VDD

Aldsbor (nA)

Vdd

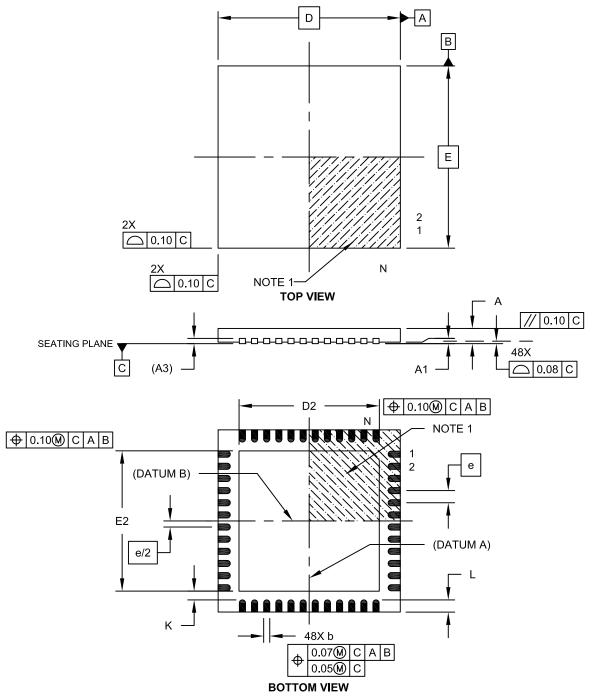

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12