Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka304t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0          | U-0           | R/W-0                                      | U-0            | U-0               | U-0              | U-0             | R/W-0  |  |

|--------------|---------------|--------------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|

|              |               | CTMUIE                                     | _              | _                 | _                | _               | HLVDIE |  |

| bit 15       |               |                                            |                |                   |                  |                 | bit 8  |  |

|              |               |                                            |                |                   |                  |                 |        |  |

| U-0          | U-0           | U-0                                        | U-0            | R/W-0             | R/W-0            | R/W-0           | U-0    |  |

| —            |               | _                                          | —              | CRCIE             | <b>U2ERIE</b>    | U1ERIE          | —      |  |

| bit 7        |               |                                            |                |                   |                  |                 | bit C  |  |

|              |               |                                            |                |                   |                  |                 |        |  |

| Legend:      |               |                                            |                |                   |                  |                 |        |  |

| R = Readab   | le bit        | W = Writable b                             | oit            | U = Unimplem      | nented bit, read | d as '0'        |        |  |

| -n = Value a | It POR        | '1' = Bit is set                           |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |

|              |               |                                            |                |                   |                  |                 |        |  |

| bit 15-14    | Unimpleme     | nted: Read as '0                           | 3              |                   |                  |                 |        |  |

| bit 13       | CTMUIE: C     | TMU Interrupt En                           | able bit       |                   |                  |                 |        |  |

|              |               | t request is enable                        |                |                   |                  |                 |        |  |

| L:400        | •             | t request is not er                        |                |                   |                  |                 |        |  |

| bit 12-9     | •             | nted: Read as '0                           |                |                   |                  |                 |        |  |

| bit 8        |               | gh/Low-Voltage D<br>t request is enable    |                | t Enable bit      |                  |                 |        |  |

|              |               | t request is enable                        |                |                   |                  |                 |        |  |

| bit 7-4      | -             | nted: Read as '0                           |                |                   |                  |                 |        |  |

| bit 3        | -             | C Generator Inter                          |                | it                |                  |                 |        |  |

|              |               | t request is enable                        | •              |                   |                  |                 |        |  |

|              | 0 = Interrupt | t request is not er                        | abled          |                   |                  |                 |        |  |

| bit 2        | U2ERIE: UA    | ART2 Error Interru                         | ipt Enable bit |                   |                  |                 |        |  |

|              |               | t request is enable                        |                |                   |                  |                 |        |  |

|              | •             | t request is not er                        |                |                   |                  |                 |        |  |

|              |               | U1ERIE: UART1 Error Interrupt Enable bit   |                |                   |                  |                 |        |  |

| bit 1        |               |                                            | •              |                   |                  |                 |        |  |

| bit 1        | 1 = Interrupt | t request is enable<br>t request is not er | ed             |                   |                  |                 |        |  |

| U-0          | R/W-1                                                                                                                | R/W-0                                  | R/W-0        | U-0                 | R/W-1            | R/W-0           | R/W-0  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|---------------------|------------------|-----------------|--------|--|--|--|

| _            | T2IP2                                                                                                                | T2IP1                                  | T2IP0        | —                   | OC2IP2           | OC2IP1          | OC2IP0 |  |  |  |

| it 15        |                                                                                                                      |                                        |              |                     |                  |                 | bit    |  |  |  |

| U-0          | R/W-1                                                                                                                | R/W-0                                  | R/W-0        | U-0                 | U-0              | U-0             | U-0    |  |  |  |

|              | IC2IP2                                                                                                               | IC2IP1                                 | IC2IP0       | _                   |                  | _               | _      |  |  |  |

| it 7         |                                                                                                                      |                                        |              |                     |                  |                 | bit    |  |  |  |

| .egend:      |                                                                                                                      |                                        |              |                     |                  |                 |        |  |  |  |

| R = Readable | e bit                                                                                                                | W = Writable                           | bit          | U = Unimplei        | mented bit, read | d as '0'        |        |  |  |  |

| n = Value at | POR                                                                                                                  | '1' = Bit is set                       |              | '0' = Bit is cle    | eared            | x = Bit is unkr | nown   |  |  |  |

| it 15        | Unimplemer                                                                                                           | nted: Read as '                        | )'           |                     |                  |                 |        |  |  |  |

| oit 14-12    | -                                                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              | <b>T2IP&lt;2:0&gt;:</b> Timer2 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                        |              |                     |                  |                 |        |  |  |  |

|              | •                                                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              | •                                                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              |                                                                                                                      | upt is Priority 1<br>upt source is dis | abled        |                     |                  |                 |        |  |  |  |

| it 11        | Unimplemer                                                                                                           | nted: Read as '                        | )'           |                     |                  |                 |        |  |  |  |

| it 10-8      | OC2IP<2:0>                                                                                                           | : Output Compa                         | re Channel 2 | Interrupt Priorit   | ty bits          |                 |        |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                           |                                        |              |                     |                  |                 |        |  |  |  |

|              | •                                                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              | •<br>001 – Interruptic Drierity 1                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                  |                                        |              |                     |                  |                 |        |  |  |  |

| oit 7        |                                                                                                                      | nted: Read as '                        |              |                     |                  |                 |        |  |  |  |

| oit 6-4      | -                                                                                                                    | Input Capture C                        |              | errupt Priority bit | ts               |                 |        |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                           |                                        |              |                     |                  |                 |        |  |  |  |

|              | •                                                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              | •                                                                                                                    |                                        |              |                     |                  |                 |        |  |  |  |

|              |                                                                                                                      | upt is Priority 1                      | abled        |                     |                  |                 |        |  |  |  |

| it 3_0       |                                                                                                                      | -                                      |              |                     |                  |                 |        |  |  |  |

| it 3-0       |                                                                                                                      | upt source is dis<br>nted: Read as '   |              |                     |                  |                 |        |  |  |  |

## REGISTER 8-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

#### REGISTER 8-32: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0      | U-0      | U-0      |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | —   | —        | —        | —        |

| bit 15 |     |     |     |     |          |          | bit 8    |

|        |     |     |     |     |          |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

| —      | —   | —   | —   | —   | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 |

| bit 7  |     |     |     |     |          | •        | bit 0    |

|        |     |     |     |     |          |          |          |

# Legend:

| Logona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

bit 6-4 ULPWUIP<2:0>: Ultra Low-Power Wake-up Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- :

• 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0                               | U-0                                                                                                                                                                                                                                                                                          | U-0                 | U-0                                | U-0                                     | U-0                 | U-0                 | U-0                 |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|-----------------------------------------|---------------------|---------------------|---------------------|

| —                                 | —                                                                                                                                                                                                                                                                                            | —                   | —                                  | —                                       |                     | —                   |                     |

| bit 15                            |                                                                                                                                                                                                                                                                                              |                     |                                    |                                         |                     |                     | bit 8               |

|                                   |                                                                                                                                                                                                                                                                                              |                     |                                    |                                         |                     |                     |                     |

| U-0                               | U-0                                                                                                                                                                                                                                                                                          | R/W-0               | R/W-0                              | R/W-0                                   | R/W-0               | R/W-0               | R/W-0               |

| —                                 | —                                                                                                                                                                                                                                                                                            | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>                | TUN3 <sup>(1)</sup>                     | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7                             |                                                                                                                                                                                                                                                                                              |                     |                                    |                                         |                     |                     | bit 0               |

|                                   |                                                                                                                                                                                                                                                                                              |                     |                                    |                                         |                     |                     |                     |

| Legend:                           |                                                                                                                                                                                                                                                                                              |                     |                                    |                                         |                     |                     |                     |

| R = Readable bit W = Writable bit |                                                                                                                                                                                                                                                                                              | bit                 | U = Unimplemented bit, read as '0' |                                         |                     |                     |                     |

| -n = Value at                     | POR                                                                                                                                                                                                                                                                                          | '1' = Bit is set    |                                    | '0' = Bit is cleared x = Bit is unknown |                     |                     | iown                |

| bit 15-6<br>bit 5-0               | Unimplemented: Read as '0'<br>TUN<5:0>: FRC Oscillator Tuning bits <sup>(1)</sup><br>011111 = Maximum frequency deviation<br>011110<br>000001<br>000000 = Center frequency, oscillator is running at factory calibrated frequency<br>11111<br>100001<br>100000 = Minimum frequency deviation |                     |                                    |                                         |                     |                     |                     |

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

| REGISTER     | (9-4: REFU                                                                                                                                                                                      | CON: REFE                                                                                                                                                                                                                                                                                 | KENCE USC                                                                                                                                                                                                                     |                                          | INTROL REG       | DISTER            |           |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-------------------|-----------|

| R/W-0        | U-0                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                         | R/W-0                                    | R/W-0            | R/W-0             | R/W-0     |

| ROEN         | —                                                                                                                                                                                               | ROSSLP                                                                                                                                                                                                                                                                                    | ROSEL                                                                                                                                                                                                                         | RODIV3                                   | RODIV2           | RODIV1            | RODIV0    |

| bit 15       |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |                                          |                  |                   | bit 8     |

| 11.0         |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               | 11.0                                     | 11.0             |                   |           |

| U-0          | U-0                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                                                                                           | U-0                                      | U-0              | U-0               | U-0       |

| bit 7        |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |                                          | _                |                   | bit (     |

|              |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |                                          |                  |                   |           |

| Legend:      |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |                                          |                  |                   |           |

| R = Readat   | ole bit                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                                              | bit                                                                                                                                                                                                                           | U = Unimplen                             | nented bit, read | d as '0'          |           |

| -n = Value a | at POR                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                               | '0' = Bit is clea                        | ared             | x = Bit is unkr   | nown      |

| bit 15       | 1 = Reference                                                                                                                                                                                   | ence Oscillator<br>e oscillator is ei<br>e oscillator is di                                                                                                                                                                                                                               | nabled on REF                                                                                                                                                                                                                 |                                          |                  |                   |           |

| bit 14       | Unimplemen                                                                                                                                                                                      | ted: Read as '                                                                                                                                                                                                                                                                            | )'                                                                                                                                                                                                                            |                                          |                  |                   |           |

| bit 13       | ROSSLP: Re                                                                                                                                                                                      | ference Oscilla                                                                                                                                                                                                                                                                           | tor Output Sto                                                                                                                                                                                                                | p in Sleep bit                           |                  |                   |           |

|              |                                                                                                                                                                                                 | e oscillator cont<br>e oscillator is di                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                               |                                          |                  |                   |           |

| bit 12       |                                                                                                                                                                                                 | erence Oscillato                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                          |                  |                   |           |

|              |                                                                                                                                                                                                 | oscillator is use                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               | clock <sup>(1)</sup><br>k; base clock re | eflects any cloc | k switching of t  | he device |

| bit 11-8     |                                                                                                                                                                                                 | Reference Os                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                               |                                          |                  | it ownorming of t |           |

|              | 1110 = Base<br>1101 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0111 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0011 = Base<br>0011 = Base | clock value div<br>clock value div | ided by $16,384$<br>ided by $8,192$<br>ided by $4,096$<br>ided by $2,048$<br>ided by $1,024$<br>ided by $512$<br>ided by $256$<br>ided by $128$<br>ided by $64$<br>ided by $32$<br>ided by $16$<br>ided by $8$<br>ided by $4$ |                                          |                  |                   |           |

| hit 7-0      | 0000 = Base                                                                                                                                                                                     | tod: Pead as '                                                                                                                                                                                                                                                                            | ۰ <b>۲</b>                                                                                                                                                                                                                    |                                          |                  |                   |           |

# REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 7-0 Unimplemented: Read as '0'

- **Note 1:** The crystal oscillator must be enabled using the FOSC<2:0> bits; the crystal maintains the operation in Sleep mode.

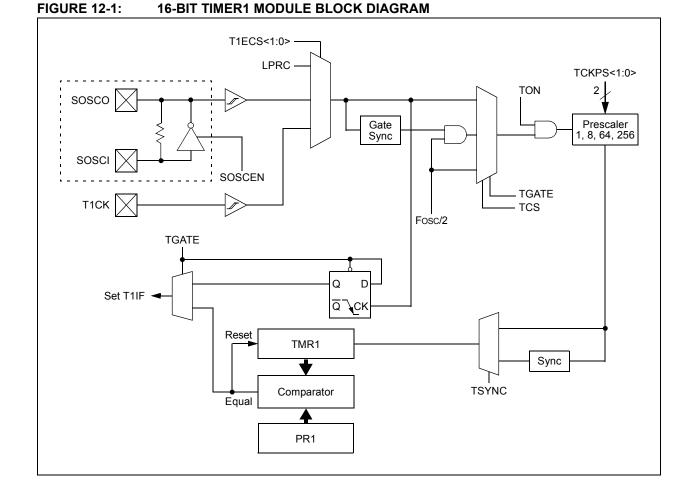

# 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This output compare module<sup>(1)</sup>

- 11110 = **Reserved** 11101 = Reserved 11100 = CTMU<sup>(2)</sup> 11011 = A/D<sup>(2)</sup> 11010 = Comparator 3<sup>(2)</sup> 11001 = Comparator 2<sup>(2)</sup> 11000 = Comparator 1<sup>(2)</sup> 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup> 10101 = Input Capture 2<sup>(2)</sup> 10100 = Input Capture 1<sup>(2)</sup> 100xx = Reserved 01111 = Timer5 01110 = Timer4 01101 = Timer3 01100 = Timer2 01011 = Timer1

- 01010 = Input Capture 5<sup>(2)</sup>

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Output Compare 5<sup>(1)</sup>

- 00100 = Output Compare 4<sup>(1)</sup>

- 00011 = Output Compare 3<sup>(1)</sup>

- 00010 = Output Compare 2<sup>(1)</sup>

- 00001 = Output Compare 1<sup>(1)</sup>

- 00000 = Not synchronized to any other module

- Note 1: Do not use an output compare module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as trigger sources only and never as Sync sources.

- 3: These bits affect the rising edge when OCINV = 1. The bits have no effect when the OCMx bits (OCxCON1<2:0>) = 001.

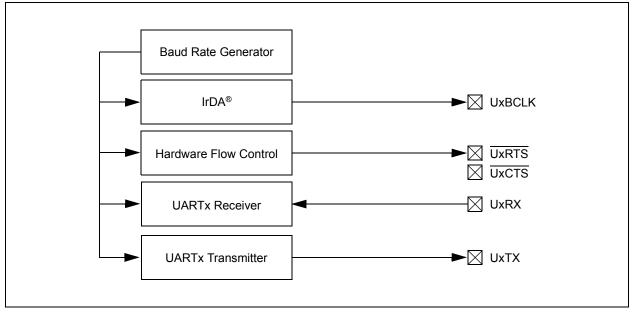

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of  |

|-------|---------------------------------------------|

|       | this group of PIC24F devices. It is not     |

|       | intended to be a comprehensive reference    |

|       | source. For more information on the Univer- |

|       | sal Asynchronous Receiver Transmitter,      |

|       | refer to the "PIC24F Family Reference       |

|       | Manual", Section 21. "UART" (DS39708).      |

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx is shown in Figure 18-1. The UARTx module consists of these important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

- Note: Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

### FIGURE 18-1: UARTX SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 22-2: AD1CON2: A/D CONTROL REGISTER 2 (CONTINUED)

ALTS: Alternate Input Sample Mode Select bit

bit 0

- 1 = Uses channel input selects for Sample A on the first sample and Sample B on the next sample

- 0 = Always uses channel input selects for Sample A

- **Note 1:** This is only applicable when the buffer is used in FIFO mode (BUFREGEN = 0). In addition, BUFS is only used when BUFM = 1.

- 2: The voltage reference setting will not be within the specification with VDD below 4.5V.

- 3: The voltage reference setting will not be within the specification with VDD below 2.3V.

#### REGISTER 22-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0  | R-0    | r-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | r   | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 |        |     |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCS7 | ADCS6 | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | ADRC: A/D Conversion Clock Source bit<br>1 = RC clock<br>0 = Clock is derived from the system clock                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | <b>EXTSAM:</b> Extended Sampling Time bit<br>1 = A/D is still sampling after SAMP = 0<br>0 = A/D is finished sampling                                        |

| bit 13   | Reserved: Maintain as '0'                                                                                                                                    |

| bit 12-8 | SAMC<4:0>: Auto-Sample Time Select bits<br>11111 = 31 TAD<br>00001 = 1 TAD<br>00000 = 0 TAD                                                                  |

| bit 7-0  | ADCS<7:0>: A/D Conversion Clock Select bits<br>11111111-01000000 = Reserved<br>00111111 = 64 · TCY = TAD<br>00000001 = 2 · TCY = TAD<br>00000000 = TCY = TAD |

| <b>TABLE 22-4</b> : | NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES: |

|---------------------|------------------------------------------------|

|                     | 10-BIT FRACTIONAL FORMATS                      |

| VIN/VREF   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Fractional Format<br>Equivalent Decimal Value | •     | 16-Bit Signed Fractional Fo<br>Equivalent Decimal Val |        |  |  |

|------------|-------------------------------------------------------|------------------------------------------------------|-------|-------------------------------------------------------|--------|--|--|

| +1023/1024 | 011 1111 1111                                         | 1111 1111 1100 0000                                  | 0.999 | 0111 1111 1110 0000                                   | 0.999  |  |  |

| +1022/1024 | 011 1111 1110                                         | 1111 1111 1000 0000                                  | 0.998 | 0111 1111 1000 0000                                   | 0.998  |  |  |

|            | •••                                                   |                                                      |       |                                                       |        |  |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0100 0000                                  | 0.001 | 0000 0000 0010 0000                                   | 0.001  |  |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                  | 0.000 | 0000 0000 0000 0000                                   | 0.000  |  |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                  | 0.000 | 1111 1111 1110 0000                                   | -0.001 |  |  |

| •••        |                                                       |                                                      |       |                                                       |        |  |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                  | 0.000 | 1000 0000 0010 0000                                   | -0.999 |  |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                  | 0.000 | 1000 0000 0000 0000                                   | -1.000 |  |  |

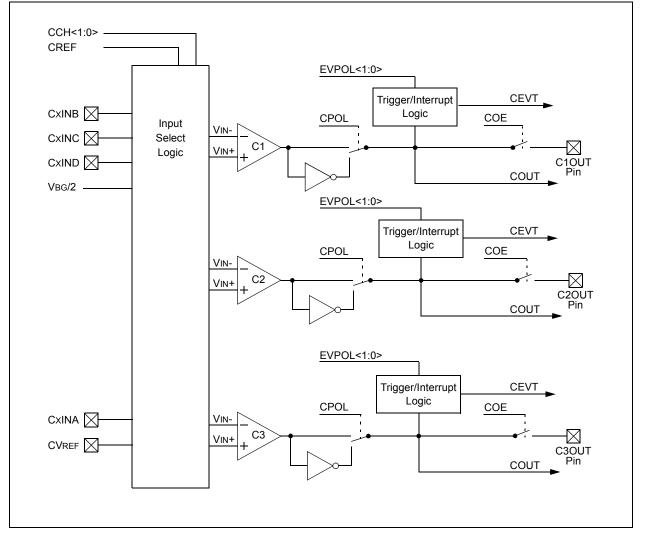

# 23.0 COMPARATOR MODULE

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on the   |

|       | Comparator module, refer to the "PIC24F    |

|       | Family Reference Manual", Section 46.      |

|       | "Scalable Comparator Module"               |

|       | (DS39734).                                 |

The comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as a voltage reference input from either the internal band gap reference, divided by 2 (VBG/2), or the comparator voltage reference generator.

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is shown in Figure 23-1. Diagrams of the possible individual comparator configurations are shown in Figure 23-2.

Each comparator has its own control register, CMxCON (Register 23-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 23-2).

### FIGURE 23-1: COMPARATOR x MODULE BLOCK DIAGRAM

# 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Charge Measurement Unit, refer to the "PIC24F Family Reference Manual", Section 53. "Charge Time Measurement Unit (CTMU) with Threshold Detect" (DS39743).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides charge measurement, accurate differential time measurement between pulse sources and asynchronous pulse generation. Its key features include:

- Thirteen external edge input trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- Control of response to edge levels or edge transitions

- · Time measurement resolution of one nanosecond

- Accurate current source suitable for capacitive measurement

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock. The CTMU module is ideal for interfacing with capacitive-based touch sensors.

The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module and controls the mode of operation of the CTMU, as well as controlling edge sequencing. CTMUCON2 controls edge source selection and edge source polarity selection. The CTMUICON register selects the current range of current source and trims the current.

## 25.1 Measuring Capacitance

The CTMU module measures capacitance by generating an output pulse, with a width equal to the time between edge events, on two separate input channels. The pulse edge events to both input channels can be selected from several internal peripheral modules (OC1, Timer1, any input capture or comparator module) and up to 13 external pins (CTED1 through CTED13). This pulse is used with the module's precision current source to calculate capacitance according to the relationship:

#### EQUATION 25-1:

$$I = C \cdot \frac{dV}{dT}$$

For capacitance measurements, the A/D Converter samples an external capacitor (CAPP) on one of its input channels after the CTMU output's pulse. A Precision Resistor (RPR) provides current source calibration on a second A/D channel. After the pulse ends, the converter determines the voltage on the capacitor. The actual calculation of capacitance is performed in software by the application.

Figure 25-1 illustrates the external connections used for capacitance measurements, and how the CTMU and A/D modules are related in this application. This example also shows the edge events coming from Timer1, but other configurations using external edge sources are possible. A detailed discussion on measuring capacitance and time with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

| R/P-1      | R/P-1                                                                                                                                                                                                                                     | R/P-1                                                                          | R/P-1                           | R/P-1                                  | R/P-1            | R/P-1          | R/P-1         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------|----------------------------------------|------------------|----------------|---------------|

| FWDTEN     | 1 WINDIS                                                                                                                                                                                                                                  | FWDTEN0                                                                        | FWPSA                           | WDTPS3                                 | WDTPS2           | WDTPS1         | WDTPS0        |

| bit 7      | ł                                                                                                                                                                                                                                         |                                                                                |                                 |                                        |                  |                | bit           |

|            |                                                                                                                                                                                                                                           |                                                                                |                                 |                                        |                  |                |               |

| Legend:    |                                                                                                                                                                                                                                           |                                                                                |                                 |                                        |                  |                |               |

| R = Reada  | ble bit                                                                                                                                                                                                                                   | P = Programm                                                                   | nable bit                       | U = Unimplem                           | nented bit, read | d as '0'       |               |

| -n = Value | at POR                                                                                                                                                                                                                                    | '1' = Bit is set                                                               |                                 | '0' = Bit is clea                      | ared             | x = Bit is unk | nown          |

| bit 7,5    | 11 = WDT is e                                                                                                                                                                                                                             | I>: Watchdog Tir<br>enabled in hardw<br>controlled with th                     | vare                            |                                        |                  |                |               |

|            | 01 = WDT is e<br>00 = WDT is c                                                                                                                                                                                                            | enabled only whi<br>disabled in hardw                                          | ile device is a<br>vare; SWDTE  | ctive; WDT is dis<br>N bit is disabled |                  | o, SWDTEN bi   | t is disabled |

| bit 6      | 1 = Standard<br>0 = Windowe                                                                                                                                                                                                               | dowed Watchdog<br>WDT is selected<br>d WDT is enable<br>and software (<br>eset | d; windowed V<br>d; note that e | VDT is disabled<br>executing a CLRW    |                  |                |               |

| bit 4      |                                                                                                                                                                                                                                           | F Prescaler bit<br>scaler ratio of 1:1<br>scaler ratio of 1:3                  |                                 |                                        |                  |                |               |

| bit 3-0    | WDTPS<3:0><br>1111 = 1:32,7<br>1110 = 1:16,3<br>1101 = 1:8,19<br>1100 = 1:4,09<br>1011 = 1:2,04<br>1010 = 1:1,02<br>1001 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0110 = 1:64<br>0101 = 1:32<br>0100 = 1:16<br>0011 = 1:8<br>0010 = 1:4 | 884<br>92<br>96<br>48<br>24                                                    | er Postscale \$                 | Select bits                            |                  |                |               |

If the WDT is enabled in hardware (FWDTEN<1:0> = 11), it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) will need to be cleared in software after the device wakes up.

The WDT Flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## 26.3.1 WINDOWED OPERATION

The Watchdog Timer has an optional Fixed Window mode of operation. In this Windowed mode, CLRWDT instructions can only reset the WDT during the last 1/4 of the programmed WDT period. A CLRWDT instruction executed before that window causes a WDT Reset, similar to a WDT time-out.

Windowed WDT mode is enabled by programming the Configuration bit, WINDIS (FWDT<6>), to '0'.

### 26.3.2 CONTROL REGISTER

The WDT is enabled or disabled by the FWDTEN<1:0> Configuration bits. When both the FWDTEN<1:0> Configuration bits are set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN<1:0> Configuration bits have been programmed to '10'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments, and disable the WDT during non-critical segments, for maximum power savings. When the FWTEN<1:0> bits are set to '01', the WDT is only enabled in Run and Idle modes, and is disabled in Sleep. Software control of the SWDTEN bit (RCON<5>) is disabled with this setting.

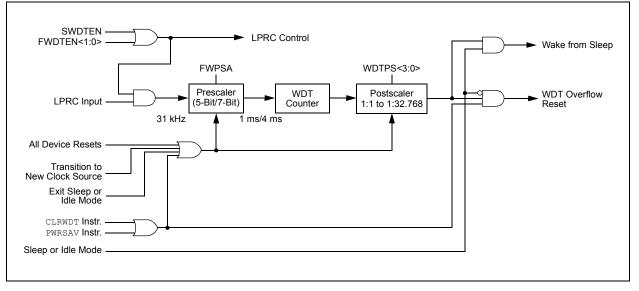

### FIGURE 26-2: WDT BLOCK DIAGRAM

### 26.4 Deep Sleep Watchdog Timer (DSWDT)

In PIC24FV32KA304 family devices, in addition to the WDT module, a DSWDT module is present which runs while the device is in Deep Sleep, if enabled. It is driven by either the SOSC or LPRC oscillator. The clock source is selected by the Configuration bit, DSWDTOSC (FDS<4>).

The DSWDT can be configured to generate a time-out, at 2.1 ms to 25.7 days, by selecting the respective postscaler. The postscaler can be selected by the Configuration bits, DSWDTPS<3:0> (FDS<3:0>). When the DSWDT is enabled, the clock source is also enabled.

DSWDT is one of the sources that can wake-up the device from Deep Sleep mode.

# 26.5 Program Verification and Code Protection

For all devices in the PIC24FV32KA304 family, code protection for the boot segment is controlled by the Configuration bit, BSS0, and the general segment by the Configuration bit, GSS0. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the boot segment and bit, GWRP, for the general segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

# 26.6 In-Circuit Serial Programming

PIC24FV32KA304 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 26.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

### TABLE 29-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| <b>Operating Conditions:</b> -40°C < TA < +125°C (unless otherwise stated) |        |                                       |       |       |       |       |                                                                   |

|----------------------------------------------------------------------------|--------|---------------------------------------|-------|-------|-------|-------|-------------------------------------------------------------------|

| Param<br>No.                                                               | Symbol | Characteristics                       | Min   | Тур   | Max   | Units | Comments                                                          |

| DVR10                                                                      | Vbg    | Band Gap Reference Voltage            | 0.973 | 1.024 | 1.075 | V     |                                                                   |

| DVR11                                                                      | Tbg    | Band Gap Reference Start-up<br>Time   | —     | 1     | —     | ms    |                                                                   |

| DVR20                                                                      | Vrgout | Regulator Output Voltage              | 3.1   | 3.3   | 3.6   | V     | -40°C < TA < +85°C                                                |

|                                                                            |        |                                       | 3.0   | 3.19  | 3.6   | V     | -40°C < TA < +125°C                                               |

| DVR21                                                                      | Cefc   | External Filter Capacitor Value       | 4.7   | 10    | _     | μF    | Series resistance < 3 Ohm<br>recommended;<br>< 5 Ohm is required. |

| DVR30                                                                      | Vlvr   | Retention Regulator Output<br>Voltage | _     | 2.6   | _     | V     |                                                                   |

### TABLE 29-16: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS |       |                                      |     | ard Ope            | •   | re -4 | ons: 1.8V to 3.6V PIC24<br>2.0V to 5.5V PIC24<br>$0^{\circ}C \le TA \le +85^{\circ}C$ for Indus<br>$0^{\circ}C \le TA \le +125^{\circ}C$ for Ext | IFV32KA3XX<br>strial |

|--------------------|-------|--------------------------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Param<br>No.       | Sym   | Characteristic                       | Min | Typ <sup>(1)</sup> | Max | Units | Comments                                                                                                                                         | Conditions           |

| DCT10              | IOUT1 | CTMU Current<br>Source, Base Range   | —   | 550                | —   | nA    | CTMUICON<9:8> = 01                                                                                                                               |                      |

| DCT11              | IOUT2 | CTMU Current<br>Source, 10x Range    | _   | 5.5                | —   | μA    | CTMUICON<9:8> = 10                                                                                                                               | 2.5V < VDD < VDDMAX  |

| DCT12              | IOUT3 | CTMU Current<br>Source, 100x Range   | -   | 55                 | —   | μA    | CTMUICON<9:8> = 11                                                                                                                               | 2.5V < VDD < VDDIWAX |

| DCT13              | Iout4 | CTMU Current<br>Source, 1000x Range  | _   | 550                | —   | μA    | CTMUICON<9:8> = 00<br>(Note 2)                                                                                                                   |                      |

| DCT20              | VF    | Temperature Diode<br>Forward Voltage | —   | .76                | —   | V     |                                                                                                                                                  |                      |

| DCT21              | VΔ    | Voltage Change per<br>Degree Celsius | _   | 1.6                | _   | mV/°C |                                                                                                                                                  |                      |

**Note 1:** Nominal value at the center point of the current trim range (CTMUICON<7:2> = 000000). On PIC24F32KA parts, the current output is limited to the typical current value when IOUT4 is chosen.

**2:** Do not use this current range with a temperature sensing diode.

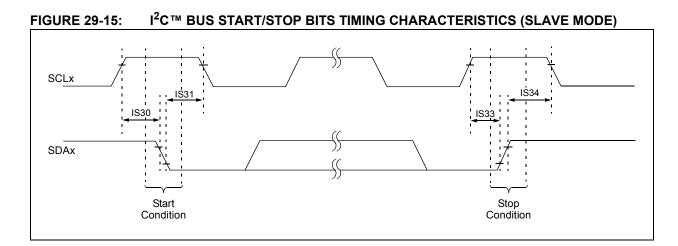

# TABLE 29-34: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING REQUIREMENTS (SLAVE MODE)

| АС СНА       | RACTERIS |                                    | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |              |     |       |                              |                 |

|--------------|----------|------------------------------------|----------------------------------------------------------|--------------|-----|-------|------------------------------|-----------------|

| Param<br>No. | Symbol   | Charao                             | cteristic                                                | Min          | Max | Units | Conditions                   |                 |

| IS30         | TSU:STA  | Start Condition                    | 100 kHz mode                                             | 4.7          | —   | μs    | Only relevant for Repeated   |                 |

|              |          | Setup Time                         | Setup Time                                               | 400 kHz mode | 0.6 | _     | μS                           | Start condition |

|              |          |                                    | 1 MHz mode <sup>(1)</sup>                                | 0.25         |     | μs    |                              |                 |

| IS31 THD:ST  | THD:STA  | D:STA Start Condition<br>Hold Time | 100 kHz mode                                             | 4.0          |     | μs    | After this period, the first |                 |

|              |          |                                    | 400 kHz mode                                             | 0.6          | _   | μs    | clock pulse is generated     |                 |

|              |          |                                    | 1 MHz mode <sup>(1)</sup>                                | 0.25         | —   | μs    |                              |                 |

| IS33         | Tsu:sto  | Stop Condition                     | 100 kHz mode                                             | 4.7          | _   | μs    |                              |                 |

|              |          | Setup Time                         | 400 kHz mode                                             | 0.6          | _   | μs    |                              |                 |

|              |          |                                    | 1 MHz mode <sup>(1)</sup>                                | 0.6          | —   | μs    |                              |                 |

| IS34         | THD:STO  | Stop Condition                     | 100 kHz mode                                             | 4000         | _   | ns    |                              |                 |

|              |          | Hold Time                          | 400 kHz mode                                             | 600          |     | ns    |                              |                 |

|              |          |                                    | 1 MHz mode <sup>(1)</sup>                                | 250          |     | ns    |                              |                 |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

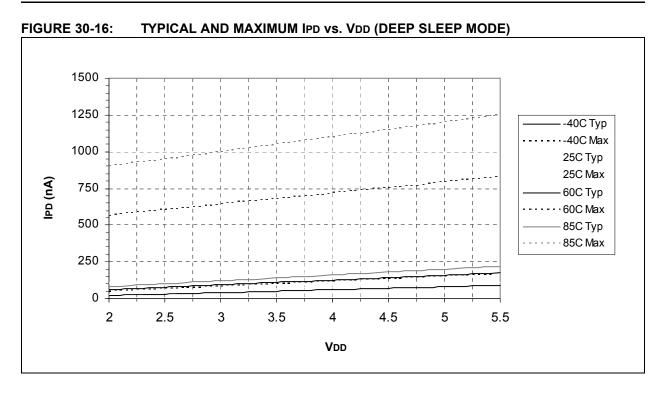

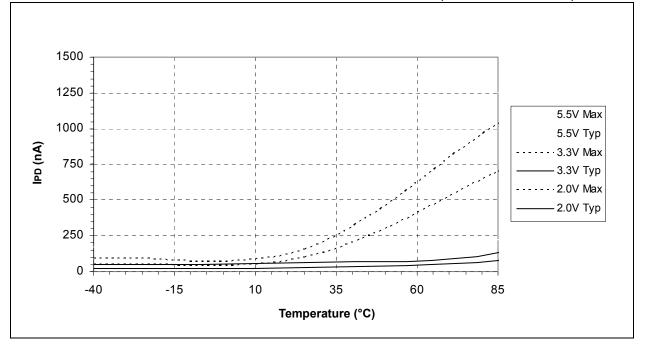

FIGURE 30-17: TYPICAL AND MAXIMUM IPD vs. TEMPERATURE (DEEP SLEEP MODE)

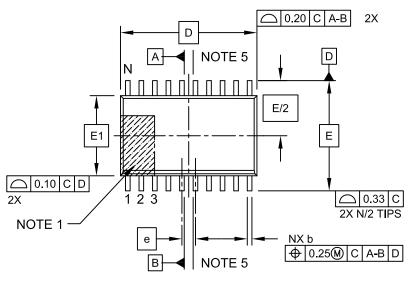

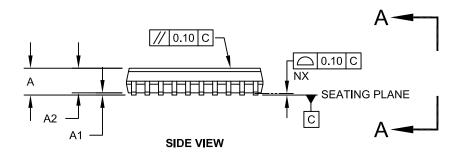

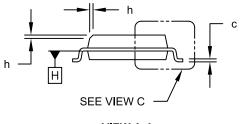

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

| Timing Requirements                               |          |

|---------------------------------------------------|----------|

| A/D Conversion                                    |          |

| CLKO and I/O                                      |          |

| External Clock                                    |          |

| I <sup>2</sup> C Bus Data (Master Mode)           | 284, 285 |

| I <sup>2</sup> C Bus Data (Slave Mode)            |          |

| I <sup>2</sup> C Bus Start/Stop Bits (Slave Mode) |          |

| Input Capture x                                   |          |

| Output Capture                                    |          |

| PLL Clock Specifications                          |          |

| PWM                                               |          |

| SPIx Master Mode (CKE = 0)                        |          |

| SPIx Master Mode (CKE = 1)                        |          |

| SPIx Slave Mode (CKE = 0)                         |          |

| SPIx Slave Mode (CKE = 1)                         |          |

| Timer1/2/3/4/5 External Clock Input               |          |

| UARTx                                             |          |

### U

| UART 177   Baud Rate Generator (BRG) 178   Break and Sync Transmit Sequence 179   IrDA Support 179   Operation of UxCTS and UxRTS Control Pins 179   Receiving in 8-Bit or 9-Bit Data Mode 179   Transmitting in 8-Bit Data Mode 179   Transmitting in 9-Bit Data Mode 179 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# W

| Watchdog Timer       |     |

|----------------------|-----|

| Deep Sleep (DSWDT)   | 250 |

| Watchdog Timer (WDT) | 248 |

| Windowed Operation   | 249 |

| WWW Address          | 358 |

| WWW, On-Line Support | 9   |