Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16ka304t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 23  |

| 3.0   | СРИ                                                         |     |

| 4.0   | Memory Organization                                         | 35  |

| 5.0   | Flash Program Memory                                        | 57  |

| 6.0   | Data EEPROM Memory                                          | 63  |

| 7.0   | Resets                                                      | 69  |

| 8.0   | Interrupt Controller                                        |     |

| 9.0   | Oscillator Configuration                                    | 115 |

| 10.0  | Power-Saving Features                                       | 125 |

| 11.0  | I/O Ports                                                   | 135 |

| 12.0  | Timer1                                                      | 139 |

| 13.0  | Timer2/3 and Timer4/5                                       | 141 |

| 14.0  | Input Capture with Dedicated Timers                         | 147 |

| 15.0  | Output Compare with Dedicated Timers                        | 151 |

| 16.0  | Serial Peripheral Interface (SPI)                           |     |

| 17.0  |                                                             |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)          | 177 |

| 19.0  | Real-Time Clock and Calendar (RTCC)                         |     |

| 20.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator | 199 |

| 21.0  | High/Low-Voltage Detect (HLVD)                              | 205 |

| 22.0  | 12-Bit A/D Converter with Threshold Detect                  |     |

| 23.0  | Comparator Module                                           | 225 |

| 24.0  | Comparator Voltage Reference                                | 229 |

| 25.0  | Charge Time Measurement Unit (CTMU)                         |     |

| 26.0  | Special Features                                            | 239 |

| 27.0  | Development Support                                         | 251 |

|       | Instruction Set Summary                                     |     |

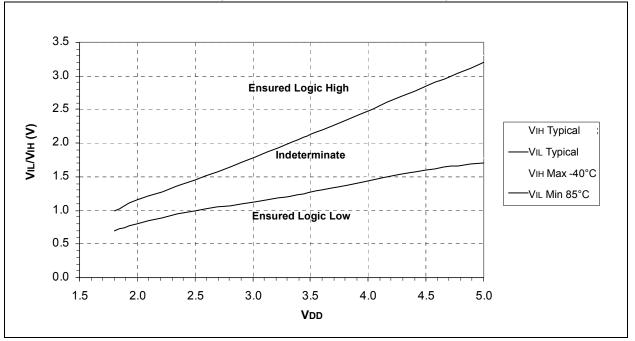

|       | Electrical Characteristics                                  |     |

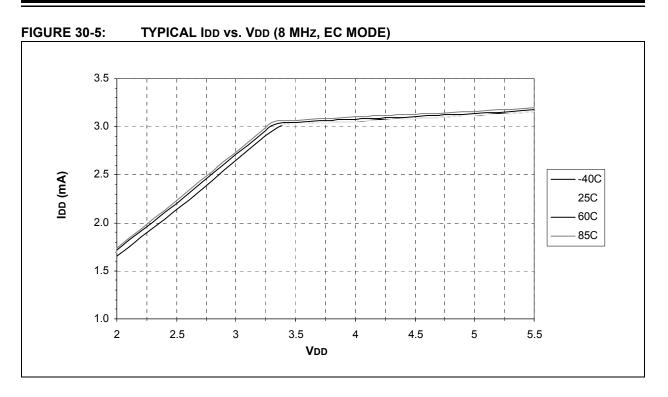

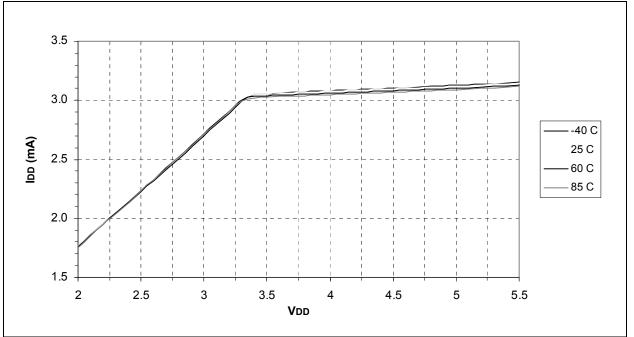

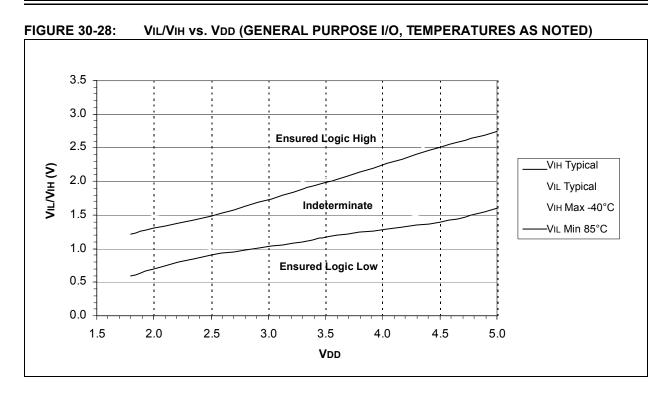

| 30.0  | DC and AC Characteristics Graphs and Tables                 | 295 |

| 31.0  | Packaging Information                                       | 325 |

| Appe  | endix A: Revision History                                   | 351 |

| Index | κ                                                           | 353 |

| The I | Microchip Web Site                                          | 359 |

|       | omer Change Notification Service                            |     |

| Cust  | omer Support                                                | 359 |

| Read  | der Response                                                | 360 |

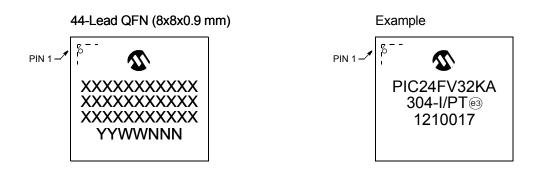

| Prod  | uct Identification System                                   |     |

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FV16KA301, PIC24F16KA301

- PIC24FV16KA302, PIC24F16KA302

- PIC24FV16KA304, PIC24F16KA304

- PIC24FV32KA301, PIC24F32KA301

- PIC24FV32KA302, PIC24F32KA302

- PIC24FV32KA304, PIC24F32KA304

The PIC24FV32KA304 family introduces a new line of extreme low-power Microchip devices. This is a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. This family also offers a new migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a digital signal processor.

#### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> digital signal controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 64 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- · Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FV32KA304 family incorporate a range of features that can significantly reduce power consumption during operation. Key features include:

- On-the-Fly Clock Switching: The device clock can be changed under software control to the Timer1 source or the internal, low-power RC oscillator during operation, allowing users to incorporate power-saving ideas into their software designs.

- Doze Mode Operation: When timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes: There are three instruction-based power-saving modes:

- Idle Mode: The core is shut down while leaving the peripherals active.

- Sleep Mode: The core and peripherals that require the system clock are shut down, leaving the peripherals that use their own clock, or the clock from other devices, active.

- Deep Sleep Mode: The core, peripherals (except RTCC and DSWDT), Flash and SRAM are shut down.

### 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24FV32KA304 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of a divide-by-2 clock output.

- Two Fast Internal oscillators (FRCs): One with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the external Oscillator modes and the 8 MHz FRC oscillator, which allows clock speeds of up to 32 MHz.

- A separate internal RC oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

#### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CN23     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs                  |

| CN24     |                                  | 15                                | 12            | 42                     | 46             | -                                | 15                                | 12            | 42                     | 46             | 1   | ST     |                                             |

| CN25     |                                  | _                                 | _             | 37                     | 40             | -                                |                                   |               | 37                     | 40             | 1   | ST     |                                             |

| CN26     |                                  | _                                 | _             | 38                     | 41             |                                  |                                   |               | 38                     | 41             | I   | ST     |                                             |

| CN27     |                                  | 14                                | 11            | 41                     | 45             |                                  | 14                                | 11            | 41                     | 45             | I   | ST     |                                             |

| CN28     |                                  | _                                 | _             | 36                     | 39             |                                  |                                   |               | 36                     | 39             | I   | ST     |                                             |

| CN29     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ST     |                                             |

| CN30     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ST     |                                             |

| CN31     |                                  | _                                 | _             | 26                     | 28             | —                                | _                                 | —             | 26                     | 28             | I   | ST     |                                             |

| CN32     |                                  | _                                 | —             | 25                     | 27             | —                                | —                                 | —             | 25                     | 27             | 1   | ST     |                                             |

| CN33     |                                  | _                                 | —             | 32                     | 35             | —                                | —                                 | —             | 32                     | 35             | 1   | ST     |                                             |

| CN34     |                                  | _                                 | —             | 35                     | 38             | —                                | —                                 | —             | 35                     | 38             | I   | ST     |                                             |

| CN35     |                                  | _                                 | _             | 12                     | 13             | —                                | _                                 | —             | 12                     | 13             | I   | ST     |                                             |

| CN36     |                                  | _                                 | _             | 13                     | 14             | —                                | _                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CVREF    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA    | Comparator Reference Positive Input Voltage |

| CVREF-   | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA    | Comparator Reference Negative Input Voltage |

| CTCMP    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input                       |

| CTED1    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 2                                 | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     |                                             |

| CTED3    | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I   | ST     |                                             |

| CTED4    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 1   | ST     |                                             |

| CTED5    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ST     |                                             |

| CTED6    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     |                                             |

| CTED7    | _                                | _                                 | _             | 5                      | 5              | _                                | —                                 | _             | 5                      | 5              | I   | ST     |                                             |

| CTED8    | _                                | _                                 | —             | 13                     | 14             | —                                | —                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CTED9    | _                                | 22                                | 19            | 9                      | 10             | —                                | 22                                | 19            | 9                      | 10             | I   | ST     |                                             |

| CTED10   | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I   | ST     | ]                                           |

| CTED11   | _                                | 21                                | 18            | 8                      | 9              | —                                | 21                                | 18            | 8                      | 9              | I   | ST     | ]                                           |

| CTED12   | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | ]                                           |

| CTED13   | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | 1   | ST     | 1                                           |

### 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                       | U-0                                          | U-0                                    | U-0             | U-0              | U-0                                   | U-0              | R/W-0, HSC    |  |  |  |  |  |

|---------------------------|----------------------------------------------|----------------------------------------|-----------------|------------------|---------------------------------------|------------------|---------------|--|--|--|--|--|

| _                         | _                                            | _                                      | —               | —                | —                                     | —                | DC            |  |  |  |  |  |

| bit 15                    |                                              |                                        |                 |                  |                                       |                  | bit 8         |  |  |  |  |  |

|                           |                                              |                                        |                 |                  |                                       |                  |               |  |  |  |  |  |

| R/W-0, HSC <sup>(1)</sup> |                                              | R/W-0, HSC <sup>(1)</sup>              | R-0, HSC        | R/W-0, HSC       | R/W-0, HSC                            | R/W-0, HSC       | R/W-0, HSC    |  |  |  |  |  |

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>                          | IPL0 <sup>(2)</sup>                    | RA              | Ν                | OV                                    | Z                | С             |  |  |  |  |  |

| bit 7                     |                                              |                                        |                 |                  |                                       |                  | bit (         |  |  |  |  |  |

| Lagandi                   |                                              | HSC = Hardwa                           | ra Cattabla/    | Nooroblo hit     |                                       |                  |               |  |  |  |  |  |

| Legend:<br>R = Readable   | hit                                          | W = Writable bi                        |                 |                  | mented bit, rea                       | ad as 'O'        |               |  |  |  |  |  |

| -n = Value at P           |                                              | '1' = Bit is set                       | ι               | '0' = Bit is cle |                                       | x = Bit is unk   | nown          |  |  |  |  |  |

|                           | OR                                           |                                        |                 |                  | arca                                  |                  |               |  |  |  |  |  |

| bit 15-9                  | Unimplemente                                 | d: Read as '0'                         |                 |                  |                                       |                  |               |  |  |  |  |  |

| bit 8                     | DC: ALU Half C                               |                                        |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | from the 4 <sup>th</sup> low-          | -order bit (foi | byte-sized da    | ta) or 8 <sup>th</sup> Iow-o          | rder bit (for wo | rd-sized data |  |  |  |  |  |

|                           | of the resul                                 |                                        | oth .           |                  |                                       |                  |               |  |  |  |  |  |

|                           | -                                            | ut from the 4 <sup>th</sup> or         |                 |                  | sult has occurr                       | ed               |               |  |  |  |  |  |

| bit 7-5                   |                                              | Interrupt Priority                     |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | errupt Priority Leverrupt Priority Lev |                 | user interrupts  | s are disabled                        |                  |               |  |  |  |  |  |

|                           |                                              | errupt Priority Lev                    |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           | 100 = CPU Interrupt Priority Level is 4 (12) |                                        |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | errupt Priority Lev                    |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | errupt Priority Lev                    |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | errupt Priority Lev                    |                 |                  |                                       |                  |               |  |  |  |  |  |

| bit 4                     | RA: REPEAT LC                                | errupt Priority Lev                    |                 |                  |                                       |                  |               |  |  |  |  |  |

| bit 4                     | $1 = \text{REPEAT} \log 1$                   | -                                      |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | p not in progress                      | S               |                  |                                       |                  |               |  |  |  |  |  |

| bit 3                     | N: ALU Negativ                               | e bit                                  |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           | 1 = Result was                               | •                                      |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           |                                              | non-negative (ze                       | ero or positiv  | ve)              |                                       |                  |               |  |  |  |  |  |

| bit 2                     | OV: ALU Overfl                               |                                        |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           | 1 = Overflow or<br>0 = No overflow           | curred for signe                       | d (2's compl    | ement) arithme   | etic in this arith                    | nmetic operatio  | on            |  |  |  |  |  |

| bit 1                     | <b>Z:</b> ALU Zero bit                       |                                        |                 |                  |                                       |                  |               |  |  |  |  |  |

|                           | 1 = An operatio                              | n, which effects                       |                 |                  |                                       |                  | esult)        |  |  |  |  |  |

| bit 0                     | <b>C:</b> ALU Carry/B                        |                                        |                 |                  | , , , , , , , , , , , , , , , , , , , | ,                | ,             |  |  |  |  |  |

|                           | 1 = A carry-out                              | from the Most S<br>at from the Most    |                 |                  |                                       |                  |               |  |  |  |  |  |

| Note 1: The               | IPLx Status bits                             | are read-onlv wh                       | en NSTDIS       | (INTCON1<1       | 5>) = 1.                              |                  |               |  |  |  |  |  |

|                           | IPL<2:0> Status                              | •                                      |                 |                  |                                       | o form the CPL   | J Interrupt   |  |  |  |  |  |

|                           | rity I aval (IPI ) T                         |                                        |                 |                  |                                       |                  |               |  |  |  |  |  |

Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

#### TABLE 4-14: PORTC REGISTER MAP<sup>(1)</sup>

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 02D0 | _      | _      |        | _      |        |        | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | O3FF          |

| PORTC        | 02D2 | -      | _      | _      | _      | _      | _      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | XXXX          |

| LATC         | 02D4 | -      | _      | _      | _      | _      | _      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | XXXX          |

| ODCC         | 02D6 | —      | —      | —      | —      | _      | -      | ODC9   | ODC8   | ODC7   | ODC6   | ODC5   | ODC4   | ODC3   | ODC2   | ODC1   | ODC0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: PORTC is not implemented in 20-pin devices or 28-pin devices.

#### TABLE 4-15: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-----------|-----------|-------|-------|-------|-------|------------|

| PADCFG1      | 02FC | _      | —      |        | _      | _      | _      |       | _     |       |       | SMBUSDEL2 | SMBUSDEL1 |       | _     | —     | _     | 0000       |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | R/W-0         | U-0                               | U-0              | U-0                  | U-0              | U-0      | U-0   |

|--------------|---------------|-----------------------------------|------------------|----------------------|------------------|----------|-------|

| _            | RTCIE         |                                   | _                | —                    | —                | —        | —     |

| bit 15       |               |                                   |                  |                      |                  |          | bit 8 |

|              |               |                                   |                  |                      |                  |          |       |

| U-0          | U-0           | U-0                               | U-0              | U-0                  | R/W-0            | R/W-0    | U-0   |

|              |               |                                   |                  |                      | MI2C2IE          | SI2C2IE  | —     |

| bit 7        |               |                                   |                  |                      |                  |          | bit 0 |

|              |               |                                   |                  |                      |                  |          |       |

| Legend:      |               |                                   |                  |                      |                  |          |       |

| R = Readat   | ole bit       | W = Writable                      | bit              | U = Unimplem         | nented bit, read | l as '0' |       |

| -n = Value a | at POR        | '1' = Bit is set                  |                  | '0' = Bit is cleared |                  |          | iown  |

|              |               |                                   |                  |                      |                  |          |       |

| bit 15       | Unimplemen    | ted: Read as '                    | 0'               |                      |                  |          |       |

| bit 14       | RTCIE: Real-  | Time Clock and                    | d Calendar Inte  | errupt Enable bi     | it               |          |       |

|              |               | equest is enab<br>equest is not e |                  |                      |                  |          |       |

| bit 13-3     | Unimplemen    | ted: Read as '                    | 0'               |                      |                  |          |       |

| bit 2        | MI2C2IE: Mas  | ster I2C2 Even                    | t Interrupt Enal | ble bit              |                  |          |       |

|              |               | equest is enab<br>equest is not e |                  |                      |                  |          |       |

| bit 1        | SI2C2IE: Slav | ve I2C2 Event                     | Interrupt Enabl  | e bit                |                  |          |       |

|              |               | equest is enab<br>equest is not e |                  |                      |                  |          |       |

| 1.11.0       |               |                                   | - •              |                      |                  |          |       |

#### REGISTER 8-14: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

bit 0 Unimplemented: Read as '0'

| U-0          | R/W-1              | R/W-0                                 | R/W-0            | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

|--------------|--------------------|---------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

|              | NVMIP2             | NVMIP1                                | NVMIP0           |                   |                  |                 |         |  |  |  |  |  |

| bit 15       |                    |                                       |                  |                   |                  |                 | bit     |  |  |  |  |  |

|              |                    |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

| U-0          | R/W-1              | R/W-0                                 | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|              | AD1IP2             | AD1IP1                                | AD1IP0           | —                 | U1TXIP2          | U1TXIP1         | U1TXIP0 |  |  |  |  |  |

| bit 7        |                    |                                       |                  |                   |                  |                 | bit     |  |  |  |  |  |

| Legend:      |                    |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

| R = Readal   | ble bit            | W = Writable                          | bit              | U = Unimplei      | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a | at POR             | '1' = Bit is set                      |                  | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                    |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 15       | -                  | ited: Read as '<br>: NVM Interrupt    |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12    |                    |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interru      | pt is Priority 7 (                    | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

|              | •                  |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •<br>001 = Interru | pt is Priority 1                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              |                    | pt source is dis                      | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 11-7     |                    | ,<br>ited: Read as '                  |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4      | AD1IP<2:0>:        | A/D Conversio                         | n Complete In    | nterrupt Priority | bits             |                 |         |  |  |  |  |  |

|              |                    | pt is Priority 7 (                    |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                  | . ,                                   |                  | , ,               |                  |                 |         |  |  |  |  |  |

|              | •                  |                                       |                  |                   |                  |                 |         |  |  |  |  |  |

|              |                    | pt is Priority 1                      |                  |                   |                  |                 |         |  |  |  |  |  |

|              |                    | pt source is dis                      |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 3        | Unimplemen         | ted: Read as '                        | 0'               |                   |                  |                 |         |  |  |  |  |  |

|              |                    | : UART1 Trans                         |                  | •                 |                  |                 |         |  |  |  |  |  |

| bit 2-0      |                    |                                       |                  | (intermed)        |                  |                 |         |  |  |  |  |  |

| bit 2-0      | 111 = Interru      | pt is Priority 7 (                    | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

| bit 2-0      | 111 = Interru<br>• | pt is Priority 7(                     | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

| bit 2-0      |                    | pt is Priority 7(<br>pt is Priority 1 | highest priority | y interrupt)      |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-20: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

#### REGISTER 8-22: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| —       | —   | —   | —   | _   | —       | —       | _       |

| bit 15  |     | •   |     |     |         |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —       |     | —   | —   | —   | INT1IP2 | INT1IP1 | INT1IP0 |

| bit 7   |     |     |     |     |         | •       | bit 0   |

|         |     |     |     |     |         |         |         |

| Legend: |     |     |     |     |         |         |         |

|         |     |     |     |     |         |         |         |

| R = Readable bit  | = Readable bit W = Writable bit |                      | d as '0'           |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- :

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| R/W-0         | R/W-0                      | R/W-1                                                   | R/W-1          | R/W-0                | R/W-0            | R/W-0            | R/W-1  |

|---------------|----------------------------|---------------------------------------------------------|----------------|----------------------|------------------|------------------|--------|

| ROI           | DOZE2                      | DOZE1                                                   | DOZE0          | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |

| 5             |                            |                                                         |                |                      |                  |                  | bit    |

|               |                            |                                                         |                |                      |                  |                  |        |

| U-0           | U-0                        | U-0                                                     | U-0            | U-0                  | U-0              | U-0              | U-0    |

| _             | _                          | _                                                       | _              | _                    | _                | _                | _      |

| I             |                            |                                                         |                |                      |                  |                  | bit    |

|               |                            |                                                         |                |                      |                  |                  |        |

| end:          |                            |                                                         |                |                      |                  |                  |        |

| Readable bi   | it                         | W = Writable                                            | bit            | U = Unimplem         | nented bit, read | d as '0'         |        |

| Value at PC   | )R                         | '1' = Bit is set                                        |                | '0' = Bit is clea    | ared             | x = Bit is unkr  | nown   |

|               |                            |                                                         |                |                      |                  |                  |        |

| 5 <b>R</b>    | OI: Recove                 | r on Interrupt bi                                       | t              |                      |                  |                  |        |

| 1             | = Interrupt                | s clear the DOZ                                         | EN bit, and re | set the CPU an       | d peripheral cl  | ock ratio to 1:1 |        |

| 0             | = Interrupt                | s have no effec                                         | t on the DOZE  | N bit                |                  |                  |        |

| 4-12 <b>D</b> | OZE<2:0>:                  | CPU and Perip                                           | heral Clock R  | atio Select bits     |                  |                  |        |

|               | 11 = 1:128                 |                                                         |                |                      |                  |                  |        |

|               | 10 = 1:64                  |                                                         |                |                      |                  |                  |        |

| _             | 01 = 1:32<br>00 = 1:16     |                                                         |                |                      |                  |                  |        |

|               | 11 = <b>1</b> :8           |                                                         |                |                      |                  |                  |        |

|               | 10 = 1:4                   |                                                         |                |                      |                  |                  |        |

|               | 01 = <b>1:2</b>            |                                                         |                |                      |                  |                  |        |

|               | 00 = 1:1                   |                                                         |                |                      |                  |                  |        |

|               |                            | e Enable bit <sup>(1)</sup>                             |                |                      |                  |                  |        |

|               |                            |                                                         |                | peripheral clock     | ratio            |                  |        |

|               |                            | d peripheral clo                                        |                | t to 1:1             |                  |                  |        |

|               |                            | : FRC Postscal                                          |                |                      |                  |                  |        |

|               |                            | <2:0> (OSCCO                                            |                | <u>111:</u>          |                  |                  |        |

|               |                            | kHz (divide-by-                                         | ,              |                      |                  |                  |        |

|               |                            | Hz (divide-by-64<br>Hz (divide-by-32                    |                |                      |                  |                  |        |

|               |                            | Hz (divide-by-16                                        |                |                      |                  |                  |        |

|               |                            | (divide-by-8)                                           |                |                      |                  |                  |        |

|               |                            | (divide-by-4)                                           |                |                      |                  |                  |        |

|               |                            | (divide-by-2) (                                         | default)       |                      |                  |                  |        |

|               |                            | (divide-by-1)                                           |                |                      |                  |                  |        |

|               |                            | < <u>2:0&gt; (OSCCO</u>                                 |                | <u>110:</u>          |                  |                  |        |

|               |                            | Hz (divide-by-2<br>Hz (divide-by-64                     |                |                      |                  |                  |        |

|               |                            | kHz (divide-by-                                         |                |                      |                  |                  |        |

|               |                            | kHz (divide-by-                                         |                |                      |                  |                  |        |

| 0             | 11 <b>= 62.5 k</b>         | Hz (divide-by-8)                                        | )              |                      |                  |                  |        |

|               |                            | Hz (divide-by-4)                                        |                |                      |                  |                  |        |

|               |                            |                                                         | (default)      |                      |                  |                  |        |

|               |                            |                                                         |                |                      |                  |                  |        |

| 0             | 01 = 250 kH<br>00 = 500 kH | Hz (divide-by-2)<br>Hz (divide-by-1)<br>hted: Read as ' | (default)      |                      |                  |                  |        |

#### bit 7-0 Unimplemented: Read as '0'

**Note 1:** This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

#### **REGISTER 15-1:** OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)

#### bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: Initialize OCx pin low; toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize OCx pin low; toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- **Note 1:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

#### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   |     | —   | —   | —   | AMSK9 | AMSK8 |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enables masking for bit x of an incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

#### REGISTER 17-4: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0     | R/W-0     | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----------|-----------|-----|-----|-----|-------|

| _     | —   | SMBUSDEL2 | SMBUSDEL1 |     | —   | —   | —     |

| bit 7 |     |           |           |     |     |     | bit 0 |

| Legend:           |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

| bit 5   | SMBUSDEL2: SMBus SDA2 Input Delay Select bit                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The I2C2 module is configured for a longer SMBus input delay (nominal 300 ns delay)</li> <li>0 = The I2C2 module is configured for a legacy input delay (nominal 150 ns delay)</li> </ul> |

| bit 4   | SMBUSDEL1: SMBus SDA1 Input Delay Select bit                                                                                                                                                           |

|         | <ul> <li>1 = The I2C1 module is configured for a longer SMBus input delay (nominal 300 ns delay)</li> <li>0 = The I2C1 module is configured for a legacy input delay (nominal 150 ns delay)</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                             |

#### 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

#### 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 18.2 "Transmitting in 8-Bit Data Mode"**).

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

### 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

#### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

#### 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

#### 18.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

### 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

#### 20.1.3 DATA SHIFT DIRECTION

The LENDIAN bit (CRCCON1<3>) is used to control the shift direction. By default, the CRC will shift data through the engine, MSb first. Setting LENDIAN (= 1) causes the CRC to shift data, LSb first. This setting allows better integration with various communication schemes and removes the overhead of reversing the bit order in software. Note that this only changes the direction of the data that is shifted into the engine. The result of the CRC calculation will still be a normal CRC result, not a reverse CRC result.

#### 20.1.4 INTERRUPT OPERATION

The module generates an interrupt that is configurable by the user for either of two conditions. If CRCISEL is '0', an interrupt is generated when the VWORD<4:0> bits make a transition from a value of '1' to '0'. If CRCISEL is '1', an interrupt will be generated after the CRC operation finishes and the module sets the CRCGO bit to '0'. Manually setting CRCGO to '0' will not generate an interrupt.

#### 20.1.5 TYPICAL OPERATION

To use the module for a typical CRC calculation:

- 1. Set the CRCEN bit to enable the module.

- 2. Configure the module for the desired operation:

- a) Program the desired polynomial using the CRCXORL and CRCXORH registers, and the PLEN<4:0> bits.

- b) Configure the data width and shift direction using the DWIDTHx and LENDIAN bits.

- c) Select the desired interrupt mode using the CRCISEL bit.

- 3. Preload the FIFO by writing to the CRCDATL and CRCDATH registers until the CRCFUL bit is set or no data is left.

- 4. Clear old results by writing 00h to CRCWDATL and CRCWDATH. CRCWDAT can also be left unchanged to resume a previously halted calculation.

- 5. Set the CRCGO bit to start calculation.

- 6. Write the remaining data into the FIFO as space becomes available.

- When the calculation completes, CRCGO is automatically cleared. An interrupt will be generated if CRCISEL = 1.

- 8. Read CRCWDATL and CRCWDATH for the result of the calculation.

#### 20.2 Registers

There are eight registers associated with the module:

- CRCCON1

- CRCCON2

- CRCXORL

- CRCXORH

- CRCDATL

- CRCDATH

- CRCWDATL

- CRCWDATH

The CRCCON1 and CRCCON2 registers (Register 20-1 and Register 20-2) control the operation of the module, and configure the various settings. The CRCXOR registers (Register 20-3 and Register 20-4) select the polynomial terms to be used in the CRC equation. The CRCDAT and CRCWDAT registers are each register pairs that serve as buffers for the double-word, input data and CRC processed output, respectively.

| R/W-0                        | R/W-0                                                                                     | R/W-0                                              | R/W-0                  | R/W-0                                       | R/W-0          | U-0                 | U-0         |

|------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------|---------------------------------------------|----------------|---------------------|-------------|

| PVCFG <sup>2</sup>           | 1 PVCFG0                                                                                  | NVCFG0                                             | OFFCAL                 | BUFREGEN                                    | CSCNA          | _                   | _           |

| bit 15                       |                                                                                           |                                                    |                        |                                             |                |                     | bit 8       |

|                              |                                                                                           | DAALO                                              | DAMA                   |                                             | DAMA           |                     |             |

| R/W-0                        | R/W-0                                                                                     | R/W-0                                              | R/W-0                  | R/W-0                                       | R/W-0          | R/W-0               | R/W-0       |

| BUFS <sup>(1)</sup><br>bit 7 | SMPI4                                                                                     | SMPI3                                              | SMPI2                  | SMPI1                                       | SMPI0          | BUFM <sup>(1)</sup> | ALTS<br>bit |

|                              |                                                                                           |                                                    |                        |                                             |                |                     |             |

| Legend:                      |                                                                                           |                                                    |                        |                                             |                |                     |             |

| R = Reada                    | able bit                                                                                  | W = Writable                                       | bit                    | U = Unimplem                                | ented bit, rea | d as '0'            |             |

| -n = Value                   | at POR                                                                                    | '1' = Bit is set                                   |                        | '0' = Bit is clea                           | red            | x = Bit is unkno    | own         |

| bit 15-14                    | <b>PVCFG&lt;1:0&gt;</b><br>11 = 4 * Inter<br>10 = 2 * Inter<br>01 = External<br>00 = AVDD | nal V <sub>BG</sub> (2)<br>mal V <sub>BG</sub> (3) | sitive Voltage         | Reference Confi                             | guration bits  |                     |             |

| bit 13                       | <b>NVCFG0:</b> Co<br>1 = External<br>0 = AVss                                             | •                                                  | e Voltage Re           | ference Configura                           | ation bits     |                     |             |

| bit 12                       | 1 = Inverting                                                                             |                                                    | ing inputs of c        | bit<br>channel Sample-a<br>channel Sample-a |                |                     |             |

| bit 11                       | 1 = Conversi                                                                              | A/D Buffer Reg<br>on result is load                | ded into a buf         | bit<br>fer location deter                   | mined by the   | converted chanr     | nel         |

| bit 10                       | CSCNA: Sca<br>1 = Scans in<br>0 = Does not                                                | puts                                               | ons for CH0+           | S/H Input for MU                            | X A Setting b  | it                  |             |

| bit 9-8                      |                                                                                           | ted: Read as '                                     | )'                     |                                             |                |                     |             |

| bit 7                        | -                                                                                         | Fill Status bit <sup>(1</sup>                      |                        |                                             |                |                     |             |

|                              | 1 = A/D is fill                                                                           | ing the upper h                                    | alf of the buff        | er; user should ac<br>er; user should ac    |                |                     |             |

| bit 6-2                      |                                                                                           | Sample Rate In                                     | •                      |                                             |                |                     |             |

|                              |                                                                                           |                                                    |                        | ne conversion for<br>ne conversion for      |                |                     |             |

|                              |                                                                                           |                                                    |                        | ne conversion for<br>ne conversion for      |                |                     |             |

| bit 1                        | BUFM: Buffer                                                                              | r Fill Mode Sele                                   | ect bit <sup>(1)</sup> |                                             |                |                     |             |

|                              | interrupt<br>0 = Starts fill                                                              | (Split Buffer mo                                   | ode)                   | 01BUF0, on the fi<br>ADCBUF0, and           | -              |                     |             |

| Note 1:                      | This is only applicused when BUFM                                                         |                                                    | buffer is used         | l in FIFO mode (E                           | UFREGEN =      | 0). In addition,    | BUFS is onl |

| 2:                           | The voltage refer                                                                         | ence setting wil                                   | I not be withir        | n the specificatior                         | with VDD be    | low 4.5V.           |             |

#### REGISTER 22-2: AD1CON2: A/D CONTROL REGISTER 2

3: The voltage reference setting will not be within the specification with VDD below 2.3V.

#### REGISTER 22-2: AD1CON2: A/D CONTROL REGISTER 2 (CONTINUED)

ALTS: Alternate Input Sample Mode Select bit

bit 0

- 1 = Uses channel input selects for Sample A on the first sample and Sample B on the next sample

- 0 = Always uses channel input selects for Sample A

- **Note 1:** This is only applicable when the buffer is used in FIFO mode (BUFREGEN = 0). In addition, BUFS is only used when BUFM = 1.

- 2: The voltage reference setting will not be within the specification with VDD below 4.5V.

- 3: The voltage reference setting will not be within the specification with VDD below 2.3V.

#### REGISTER 22-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0  | R-0    | r-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | r   | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 |        |     |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCS7 | ADCS6 | ADCS5 | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | ADRC: A/D Conversion Clock Source bit<br>1 = RC clock<br>0 = Clock is derived from the system clock                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | <b>EXTSAM:</b> Extended Sampling Time bit<br>1 = A/D is still sampling after SAMP = 0<br>0 = A/D is finished sampling                                        |

| bit 13   | Reserved: Maintain as '0'                                                                                                                                    |

| bit 12-8 | SAMC<4:0>: Auto-Sample Time Select bits<br>11111 = 31 TAD<br>00001 = 1 TAD<br>00000 = 0 TAD                                                                  |

| bit 7-0  | ADCS<7:0>: A/D Conversion Clock Select bits<br>11111111-01000000 = Reserved<br>00111111 = 64 · TCY = TAD<br>00000001 = 2 · TCY = TAD<br>00000000 = TCY = TAD |

#### CTMUCONO, CTMU CONTROL DECISTER 2

| REGISTER 2    |                                                                                                                                          | JCON2: CTM       |                 |                   |                   |                 |          |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|-------------------|-----------------|----------|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                                    | R/W-0            | R/W-0           | R/W-0             | R/W-0             | R/W-0           | R/W-0    |  |  |  |  |

| EDG1MOD       | EDG1POL                                                                                                                                  | EDG1SEL3         | EDG1SEL2        | EDG1SEL1          | EDG1SEL0          | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                                                                          |                  |                 |                   |                   |                 | bit      |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0            | R/W-0           | R/W-0             | R/W-0             | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                                                  | EDG2SEL3         | EDG2SEL2        |                   |                   | 0-0             | 0-0      |  |  |  |  |

|               | EDG2POL                                                                                                                                  | EDG25EL3         | EDG25EL2        | EDG2SEL1          | EDG2SEL0          |                 |          |  |  |  |  |

| bit 7         |                                                                                                                                          |                  |                 |                   |                   |                 | bit      |  |  |  |  |

| Legend:       |                                                                                                                                          |                  |                 |                   |                   |                 |          |  |  |  |  |

| R = Readable  | e bit                                                                                                                                    | W = Writable     | bit             | U = Unimplem      | nented bit, read  | l as '0'        |          |  |  |  |  |