Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 17                                                                           |

| Program Memory Size        | 32KB (11K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | A/D 12x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 20-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka301-i-p |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

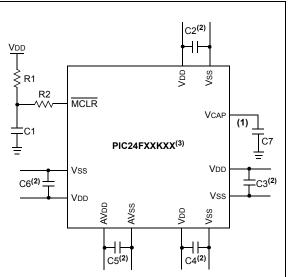

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC24FV32KA304 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED

#### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

**<sup>3:</sup>** Some PIC24F K parts do not have a regulator.

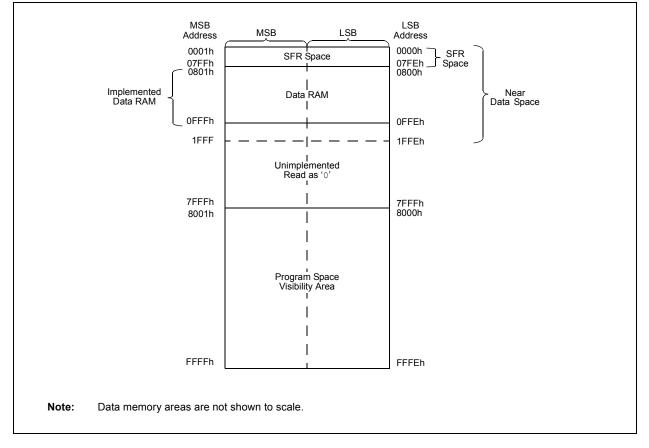

# 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility"). PIC24FV32KA304 family devices implement a total of 1024 words of data memory. If an EA points to a location outside of this area, an all zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### FIGURE 4-3: DATA SPACE MEMORY MAP FOR PIC24FV32KA304 FAMILY DEVICES

### TABLE 4-3: CPU CORE REGISTERS MAP

| IADEE -   | т-∪.          |        | OOKE   |            |                               |        |        |       |       |       |       |       |       |       |       |       |       |               |

|-----------|---------------|--------|--------|------------|-------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Start<br>Addr | Bit 15 | Bit 14 | Bit 13     | Bit 12                        | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| WREG0     | 0000          |        | WREG0  |            |                               |        |        |       |       |       |       | 0000  |       |       |       |       |       |               |

| WREG1     | 0002          |        |        |            |                               |        |        |       | WF    | REG1  |       |       |       |       |       |       |       | 0000          |

| WREG2     | 0004          |        |        |            |                               |        |        |       | WF    | REG2  |       |       |       |       |       |       |       | 0000          |

| WREG3     | 0006          |        |        |            |                               |        |        |       | WF    | REG3  |       |       |       |       |       |       |       | 0000          |

| WREG4     | 0008          |        |        |            |                               |        |        |       | WF    | REG4  |       |       |       |       |       |       |       | 0000          |

| WREG5     | 000A          |        |        |            |                               |        |        |       | WF    | REG5  |       |       |       |       |       |       |       | 0000          |

| WREG6     | 000C          |        |        |            |                               |        |        |       | WF    | REG6  |       |       |       |       |       |       |       | 0000          |

| WREG7     | 000E          |        |        |            |                               |        |        |       | WF    | REG7  |       |       |       |       |       |       |       | 0000          |

| WREG8     | 0010          |        |        |            |                               |        |        |       | WF    | REG8  |       |       |       |       |       |       |       | 0000          |

| WREG9     | 0012          |        |        |            |                               |        |        |       | WF    | REG9  |       |       |       |       |       |       |       | 0000          |

| WREG10    | 0014          |        |        |            |                               |        |        |       | WR    | EG10  |       |       |       |       |       |       |       | 0000          |

| WREG11    | 0016          |        |        |            |                               |        |        |       | WR    | EG11  |       |       |       |       |       |       |       | 0000          |

| WREG12    | 0018          |        |        |            |                               |        |        |       | WR    | EG12  |       |       |       |       |       |       |       | 0000          |

| WREG13    | 001A          |        |        |            |                               |        |        |       | WR    | EG13  |       |       |       |       |       |       |       | 0000          |

| WREG14    | 001C          |        |        |            |                               |        |        |       | WR    | EG14  |       |       |       |       |       |       |       | 0000          |

| WREG15    | 001E          |        |        |            |                               |        |        |       | WR    | EG15  |       |       |       |       |       |       |       | 0000          |

| SPLIM     | 0020          |        |        |            |                               |        |        |       | SF    | PLIM  |       |       |       |       |       |       |       | XXXX          |

| PCL       | 002E          |        |        |            |                               |        |        |       | F     | PCL   |       |       |       |       |       |       |       | 0000          |

| PCH       | 0030          | _      | _      | _          | _                             | _      | _      | _     | _     | _     |       |       |       | PCH   |       |       |       | 0000          |

| TBLPAG    | 0032          |        | _      | TBLPAG     |                               |        |        |       |       |       | 0000  |       |       |       |       |       |       |               |

| PSVPAG    | 0034          |        |        |            | —                             | —      |        | —     | —     |       |       |       | PS    | /PAG  |       |       |       | 0000          |

| RCOUNT    | 0036          |        |        | RCOUNT     |                               |        |        |       |       |       | XXXXX |       |       |       |       |       |       |               |

| SR        | 0042          | _      | _      |            | DC IPL2 IPL1 IPL0 RA N OV Z C |        |        |       |       | 0000  |       |       |       |       |       |       |       |               |

| CORCON    | 0044          |        | _      | IPL3 PSV 0 |                               |        |        |       |       | 0000  |       |       |       |       |       |       |       |               |

| DISICNT   | 0052          |        | _      |            |                               |        |        |       |       | DISIC | NT    |       |       |       |       |       |       | XXXX          |

|           |               |        |        |            |                               |        |        |       |       |       |       |       |       |       |       |       |       |               |

DS39995D-page 39

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

int attribute ((space(auto psv))) progAddr = 0x1234; // Global variable located in Pgm Memory

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

builtin tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5

// instructions

builtin write NVM();

// C30 function to perform unlock

// sequence and set WR

```

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| ;  | Set up NVMCO        | N for row programming operatio        | ns                                          |

|----|---------------------|---------------------------------------|---------------------------------------------|

|    | MOV                 | #0x4004, W0                           | ;                                           |

|    | MOV                 | W0, NVMCON                            | ; Initialize NVMCON                         |

| ;  | Set up a poi        | nter to the first program memo        | ry location to be written                   |

| ;  | program memo        | ry selected, and writes enable        | d                                           |

|    | MOV                 | #0x0000, W0                           | ;                                           |

|    | MOV                 | W0, TBLPAG                            | ; Initialize PM Page Boundary SFR           |

|    | MOV                 | #0x6000, W0                           | ; An example program memory address         |

| ;  | Perform the         | TBLWT instructions to write th        | e latches                                   |

| ;  | Oth_program_        |                                       |                                             |

|    | MOV                 | #LOW_WORD_0, W2                       | ;                                           |

|    | MOV                 | #HIGH_BYTE_0, W3                      | ;                                           |

|    |                     | W2, [W0]                              | ; Write PM low word into program latch      |

|    | TBLWTH              | W3, [W0++]                            | ; Write PM high byte into program latch     |

| ;  | lst_program_        |                                       |                                             |

|    | MOV                 | #LOW_WORD_1, W2                       | ;                                           |

|    |                     | #HIGH_BYTE_1, W3                      | ;                                           |

|    |                     | W2, [W0]                              | ; Write PM low word into program latch      |

|    |                     | W3, [W0++]                            | ; Write PM high byte into program latch     |

| ;  | 2nd_program         | —                                     |                                             |

|    | MOV                 | #LOW_WORD_2, W2                       | ;                                           |

|    | MOV                 | <pre>#HIGH_BYTE_2, W3</pre>           |                                             |

|    |                     | W2, [W0]                              | ; Write PM low word into program latch      |

|    | TBLWTH              | W3, [W0++]                            | ; Write PM high byte into program latch     |

|    | •                   |                                       |                                             |

|    | •                   |                                       |                                             |

| Ι. | -                   | trand                                 |                                             |

| '  | 32nd_program<br>MOV |                                       |                                             |

|    | MOV                 | #LOW_WORD_31, W2<br>#HIGH BYTE 31, W3 | ;                                           |

|    |                     | W2, [W0]                              | ;<br>; Write PM low word into program latch |

|    |                     | W2, [W0]<br>W3, [W0]                  | ; Write PM high byte into program latch     |

|    | חואתמו              | M2, [M0]                              | , write in high byte into program fatch     |

# 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Data EEPROM, refer to the *"PIC24F Family Reference Manual"*, Section 5. "Data EEPROM" (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFFh. The size of the data EEPROM is 256 words in the PIC24FV32KA304 family devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

### 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

| //Disable Interr | upts For 5 instruc | ctions |

|------------------|--------------------|--------|

| asm volatile (   | "disi #5");        |        |

| //Issue Unlock S | equence            |        |

| asm volatile (   | "mov #0x55, W0     | \n"    |

| "                | mov W0, NVMKEY     | \n"    |

| "                | mov #0xAA, W1      | \n"    |

| "                | mov W1, NVMKEY     | \n");  |

| // Perform Write | /Erase operations  |        |

| asm volatile (   | "bset NVMCON, #WR  | \n"    |

| "                | nop                | \n"    |

| "                | nop                | \n");  |

|                  |                    |        |

#### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing a bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- 2. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin the erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3.

#### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in the previous section) if the PGMONLY bit (NVMCON<12>) is set to '1'.

- 2. Write the data word into the data EEPROM latch.

- 3. Program the data word into the EEPROM:

- Configure the NVMCON register to program one EEPROM word (NVMCON<5:0> = 0001xx).

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin the erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4.

#### EXAMPLE 6-3: DATA EEPROM BULK ERASE

// Set up NVMCON to bulk erase the data EEPROM NVMCON =  $0 \times 4050;$

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

```

// Issue Unlock Sequence and Start Erase Cycle

__builtin_write_NVM();

```

### EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

```

int attribute ((space(eedata))) eeData = 0x1234;

// New data to write to EEPROM

int newData;

/*_____

_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the write

-------

*/

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4004;

\ensuremath{//} Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData);

// Initialize EE Data page pointer

// Initizlize lower word of address

offset = __builtin_tbloffset(&eeData);

builtin tblwtl(offset, newData);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

builtin write NVM();

// Issue Unlock Sequence & Start Write Cycle

while (NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

| R/W-0, HS   | S R/W-0, HS                       | R/W-0                                                                 | R/W-0                        | U-0               | R/C-0, HS          | R/W-0             | R/W-0          |  |  |

|-------------|-----------------------------------|-----------------------------------------------------------------------|------------------------------|-------------------|--------------------|-------------------|----------------|--|--|

| TRAPR       | IOPUWR                            | SBOREN                                                                | RETEN <sup>(3)</sup>         | —                 | DPSLP              | CM                | PMSLP          |  |  |

| bit 15      |                                   |                                                                       |                              |                   |                    |                   | bit 8          |  |  |

| R/W-0, H    | S R/W-0, HS                       | R/W-0, HS                                                             | R/W-0, HS                    | R/W-0, HS         | R/W-0, HS          | R/W-1, HS         | R/W-1, HS      |  |  |

| EXTR        | SWR                               | SWDTEN <sup>(2)</sup>                                                 | WDTO                         | SLEEP             | IDLE               | BOR               | POR            |  |  |

| bit 7       |                                   |                                                                       |                              |                   |                    |                   | bit 0          |  |  |

| <del></del> |                                   | <u> </u>                                                              |                              |                   | <u> </u>           |                   |                |  |  |

| Legend:     |                                   | C = Clearable                                                         |                              |                   | re Settable bit    |                   |                |  |  |

| R = Reada   |                                   | W = Writable b                                                        | bit                          | •                 | nented bit, read   | as '0'            |                |  |  |

| -n = Value  | at POR                            | '1' = Bit is set                                                      |                              | '0' = Bit is cle  | ared               | x = Bit is unkn   | iown           |  |  |

| bit 15      | TRAPR: Tran                       | Reset Flag bit                                                        |                              |                   |                    |                   |                |  |  |

|             | =                                 | onflict Reset has                                                     | occurred                     |                   |                    |                   |                |  |  |

|             |                                   | onflict Reset has                                                     |                              |                   |                    |                   |                |  |  |

| bit 14      | IOPUWR: Ille                      | gal Opcode or l                                                       | Jninitialized W              | Access Reset      | Flag bit           |                   |                |  |  |

|             | 1 = An illegal<br>Pointer c       | l opcode detecti<br>aused a Reset                                     | on, an illegal a             | ddress mode o     | or Uninitialized V | V register used   | as an Address  |  |  |

|             | 0 = An illegal                    | I opcode or Unir                                                      | nitialized W Re              | set has not oc    | curred             |                   |                |  |  |

| bit 13      | SBOREN: So                        | oftware Enable/E                                                      | Disable of BOF               | R bit             |                    |                   |                |  |  |

|             |                                   | 1 = BOR is turned on in software<br>0 = BOR is turned off in software |                              |                   |                    |                   |                |  |  |

| bit 12      | RETEN: Rete                       | ention Sleep Mo                                                       | de control bit <sup>(3</sup> | 6)                |                    |                   |                |  |  |

|             |                                   | d voltage supply                                                      |                              |                   |                    |                   |                |  |  |

| bit 11      | Unimplemen                        | ted: Read as '0                                                       | 3                            |                   |                    |                   |                |  |  |

| bit 10      | DPSLP: Deep                       | p Sleep Mode F                                                        | lag bit                      |                   |                    |                   |                |  |  |

|             | •                                 | ep has occurred<br>ep has not occu                                    |                              |                   |                    |                   |                |  |  |

| bit 9       | CM: Configur                      | ation Word Misr                                                       | natch Reset F                | lag bit           |                    |                   |                |  |  |

|             | Ų                                 | uration Word Mis<br>uration Word Mis                                  |                              |                   | ed                 |                   |                |  |  |

| bit 8       | PMSLP: Proc                       | gram Memory Po                                                        | ower During S                | leep bit          |                    |                   |                |  |  |

|             |                                   | memory bias vo<br>memory bias v<br>mode                               |                              |                   |                    | the Voltage Re    | gulator enters |  |  |

| bit 7       | -                                 | nal Reset (MCLF                                                       | R) Pin bit                   |                   |                    |                   |                |  |  |

| Sit 7       | 1 = A Master                      | Clear (pin) Reso<br>Clear (pin) Reso                                  | et has occurre               |                   |                    |                   |                |  |  |

| bit 6       |                                   | ire Reset (Instru                                                     |                              |                   |                    |                   |                |  |  |

|             | 1 <b>= A</b> reset                | instruction has I<br>instruction has I                                | peen executed                |                   |                    |                   |                |  |  |

| Note 1:     | All of the Reset a cause a device |                                                                       | be set or clear              | ed in software.   | Setting one of the | nese bits in soft | ware does not  |  |  |

| 2:          | If the FWDTEN SWDTEN bit se       | x Configuration I                                                     | bit is '1' (unpro            | ogrammed), the    | e WDT is always    | enabled regar     | dless of the   |  |  |

| 3:          | This is implement                 | -                                                                     | V32KA3XX pa                  | arts only; not us | sed on PIC24F3     | 2KA3XX device     | es.            |  |  |

|             |                                   |                                                                       |                              |                   |                    |                   |                |  |  |

# REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0           | R/W-0                                    | R/W-0          | R/W-0             | U-0              | R/W-0           | U-0     |  |  |  |

|----------------|-----------------|------------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|--|

| U2TXIE         | U2RXIE          | INT2IE                                   | T5IE           | T4IE              |                  | OC3IE           |         |  |  |  |

| bit 15         | 1               |                                          |                |                   |                  |                 | bit 8   |  |  |  |

|                |                 |                                          |                |                   |                  |                 |         |  |  |  |

| U-0            | U-0             | U-0                                      | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| _              | —               |                                          | INT1IE         | CNIE              | CMIE             | MI2C1IE         | SI2C1IE |  |  |  |

| bit 7          |                 |                                          |                |                   |                  |                 | bit (   |  |  |  |

| Legend:        |                 |                                          |                |                   |                  |                 |         |  |  |  |

| R = Readable   | e bit           | W = Writable                             | bit            | U = Unimplem      | nented bit, read | d as '0'        |         |  |  |  |

| -n = Value at  | POR             | '1' = Bit is set                         |                | '0' = Bit is clea |                  | x = Bit is unkn | own     |  |  |  |

|                |                 |                                          |                |                   |                  |                 |         |  |  |  |

| bit 15         | U2TXIE: UAR     | RT2 Transmitter                          | Interrupt Ena  | ble bit           |                  |                 |         |  |  |  |

|                |                 | equest is enab                           |                |                   |                  |                 |         |  |  |  |

|                | •               | equest is not e                          |                |                   |                  |                 |         |  |  |  |

| bit 14         |                 | RT2 Receiver Ir                          | •              | e bit             |                  |                 |         |  |  |  |

|                | •               | equest is enab                           |                |                   |                  |                 |         |  |  |  |

| <b>h</b> it 40 |                 | equest is not e                          |                |                   |                  |                 |         |  |  |  |

| bit 13         |                 | nal Interrupt 2<br>equest is enab        |                |                   |                  |                 |         |  |  |  |

|                |                 | equest is enab                           |                |                   |                  |                 |         |  |  |  |

| bit 12         |                 | Interrupt Enabl                          |                |                   |                  |                 |         |  |  |  |

|                |                 | equest is enab                           |                |                   |                  |                 |         |  |  |  |

|                |                 | equest is not e                          |                |                   |                  |                 |         |  |  |  |

| bit 11         | T4IE: Timer4    | Fimer4 Interrupt Enable bit              |                |                   |                  |                 |         |  |  |  |

|                | •               | equest is enab                           |                |                   |                  |                 |         |  |  |  |

|                | -               | equest is not e                          |                |                   |                  |                 |         |  |  |  |

| bit 10         | -               | ted: Read as '                           |                |                   |                  |                 |         |  |  |  |

| bit 9          | -               | ut Compare 3 Ir                          | -              | e bit             |                  |                 |         |  |  |  |

|                |                 | equest is enab                           |                |                   |                  |                 |         |  |  |  |

| bit 8-5        | -               | equest is not e<br><b>ted:</b> Read as ' |                |                   |                  |                 |         |  |  |  |

| bit 4          | -               | nal Interrupt 1                          |                |                   |                  |                 |         |  |  |  |

|                |                 | request is enab                          |                |                   |                  |                 |         |  |  |  |

|                |                 | request is not e                         |                |                   |                  |                 |         |  |  |  |

| bit 3          | CNIE: Input C   | Change Notifica                          | tion Interrupt | Enable bit        |                  |                 |         |  |  |  |

|                | -               | equest is enab                           | =              |                   |                  |                 |         |  |  |  |

|                | 0 = Interrupt r | equest is not e                          | nabled         |                   |                  |                 |         |  |  |  |

| bit 2          | CMIE: Compa     | arator Interrupt                         | Enable bit     |                   |                  |                 |         |  |  |  |

|                | •               | equest is enab                           |                |                   |                  |                 |         |  |  |  |

|                |                 | equest is not e                          |                |                   |                  |                 |         |  |  |  |

| bit 1          |                 | ster I2C1 Even                           | -              | able bit          |                  |                 |         |  |  |  |

|                | •               | equest is enab                           |                |                   |                  |                 |         |  |  |  |

| hit 0          |                 | equest is not e                          |                | lo hit            |                  |                 |         |  |  |  |

| bit 0          |                 | ve I2C1 Event I                          |                |                   |                  |                 |         |  |  |  |

|                | ⊥ – menupt r    | equest is enab                           | nabled         |                   |                  |                 |         |  |  |  |

### REGISTER 8-12: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

#### REGISTER 8-30: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|--------|-----|-----|-----|-----|---------|---------|---------|

| —      | —   | —   | —   | —   | _       |         | —       |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _      | _   | _   | _   | _   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7 |

|-------|

|       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

#### REGISTER 8-31: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CTMUIP2 | CTMUIP1 | CTMUIP0 | —   | —   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-4 **CTMUIP<2:0>:** CTMU Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

•

bit 0

NOTES:

# **10.0 POWER-SAVING FEATURES**

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | intended to be a comprehensive refer-                                              |  |  |  |  |  |  |

|       | ence source. For more information, refer                                           |  |  |  |  |  |  |

|       | to the "PIC24F Family Reference                                                    |  |  |  |  |  |  |

|       | Manual", "Section 39. Power-Saving                                                 |  |  |  |  |  |  |

|       | Features with Deep Sleep" (DS39727).                                               |  |  |  |  |  |  |

The PIC24FV32KA304 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep, Idle and Deep Sleep modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

#### 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals, except RTCC and DSWDT. It also freezes I/O states and removes power to SRAM and Flash memory. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as the clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE  | ; | Put the device into SLEEP mode      |

|--------|--------------|---|-------------------------------------|

| PWRSAV | #IDLE_MODE   | ; | Put the device into IDLE mode       |

| BSET   | DSCON, #DSEN | ; | Enable Deep Sleep                   |

| PWRSAV | #SLEEP_MODE  | ; | Put the device into Deep SLEEP mode |

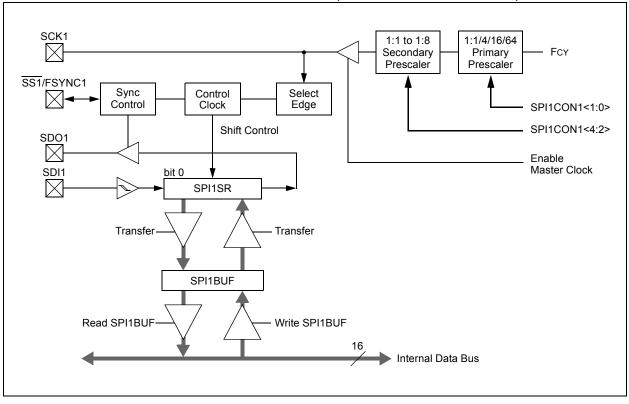

#### FIGURE 16-1: SPI1 MODULE BLOCK DIAGRAM (STANDARD BUFFER MODE)

# REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                 |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                          |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                         |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                     |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                    |

|       | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                               |

|       | 1 = Receive buffer has overflowed                                                                                                                                             |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the RSR to the empty state)    |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                    |

|       | <ul> <li>1 = Receive buffer has data; at least one more characters can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                |

© 2011-2013 Microchip Technology Inc.

# 19.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

### 19.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value Register Window (RTCVALH and RTCVALL) uses the RTCPTR bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 19-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 19-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |

|-------------|----------------------------|-------------|--|--|--|

| RICPIRSI.02 | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |

| 11          | —                          | YEAR        |  |  |  |

The Alarm Value Register Window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 19-2).

By writing the ALRMVALH byte, the Alarm Pointer value (ALRMPTR<1:0> bits) decrements by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL, until the pointer value is manually changed.

#### TABLE 19-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |

|---------|-----------------------------|--------------|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |

| 11      | PWCSTAB                     | PWCSAMP      |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

# 19.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RTCPWC<13>) must be set (see Example 19-1).

Note: To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only one instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN. Therefore, it is recommended that code follow the procedure in Example 19-1.

# 19.2.3 SELECTING RTCC CLOCK SOURCE

There are four reference source clock options that can be selected for the RTCC using the RTCCSEL<1:0> bits: 00 = Secondary Oscillator, 01 = LPRC, 10 = 50 Hz External Clock and 11 = 60 Hz External Clock.

| <br> |          |                                              |

|------|----------|----------------------------------------------|

| asm  | volatile | ("push w7");                                 |

| asm  | volatile | ("push w8");                                 |

| asm  | volatile | ("disi #5");                                 |

| asm  | volatile | ("mov #0x55, w7");                           |

| asm  | volatile | ("mov w7, NVMKEY");                          |

| asm  | volatile | ("mov #0xAA, w8");                           |

| asm  | volatile | ("mov w8, NVMKEY");                          |

| asm  | volatile | ("bset RCFGCAL, #13"); //set the RTCWREN bit |

| asm  | volatile | ("pop w8");                                  |

| asm  | volatile | ("pop w7");                                  |

|      |          |                                              |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL  | Expr            | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL  | Wn              | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET  |                 | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE |                 | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW  | #lit10,Wn       | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC    | f               | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC    | f               | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE     | Ws,Wnd          | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM   | f               | f = FFFFh                               | 1             | 1              | None                     |

|                      | SETM   | WREG            | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM   | Ws              | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL     | f               | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

|                      | SL     | f,WREG          | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Ws,Wd           | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB    | f               | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | f,WREG          | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | #lit10,Wn       | Wn = Wn – lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR   | f               | f = WREG – f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | f,WREG          | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | f,WREG          | $WREG = WREG - f - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  |                 | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      |        | Wb,Ws,Wd        |                                         |               |                |                          |

| CHA D                | SUBBR  | Wb,#lit5,Wd     | Wd = lit5 – Wb – (C)                    | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b | Wn              | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP   | Wn              | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

| TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>             | 1             | 2              | None                     |

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR    | f               | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 29-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min         | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                    | TJ     | -40         | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40         |             | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O |             | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                       | PDMAX  | (           | TJ — ΤΑ)/θJ | JA   | W    |

#### TABLE 29-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур  | Max | Unit | Notes |

|------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 20-Pin SPDIP | θJA    | 62.4 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 60   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SSOP  | θJA    | 108  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θJA    | 71   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SOIC  | θJA    | 75   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 80.2 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN   | θJA    | 32   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN   | θJA    | 29   | _   | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN  | θJA    | _    | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 29-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                   |  |  |

|--------------------|--------|------------------------------------------------------------------|------------------------------------------------------|--------------------|-----|-------|-----------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                                   | Min                                                  | Typ <sup>(1)</sup> | Max | Units | Conditions                        |  |  |

| DC10               | Vdd    | Supply Voltage                                                   | 1.8                                                  | _                  | 3.6 | V     | For F devices                     |  |  |

|                    |        |                                                                  | 2.0                                                  |                    | 5.5 | V     | For FV devices                    |  |  |

| DC12 V             | Vdr    | RAM Data Retention<br>Voltage <sup>(2)</sup>                     | 1.5                                                  |                    | _   | V     | For F devices                     |  |  |

|                    |        |                                                                  | 1.7                                                  |                    | _   | V     | For FV devices                    |  |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | Vss                                                  | —                  | 0.7 | V     |                                   |  |  |

| DC17               | SVDD   | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                 | —                  | _   | V/ms  | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** This is the limit to which VDD can be lowered without losing RAM data.

| DC CHARACTERISTICS |                        | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |            |      |                                |  |  |

|--------------------|------------------------|-------------------------------------------------------|------|-------|------------|------|--------------------------------|--|--|

| Parameter<br>No.   | Device                 | Typical <sup>(1)</sup>                                | Max  | Units | Conditions |      |                                |  |  |

| Module Diffe       | erential Current (∆IPD | ) <sup>(3)</sup>                                      |      |       |            |      |                                |  |  |

| DC78               | PIC24FV32KA3XX         | 0.03                                                  | _    | μA    | -40°C      | 2.0V |                                |  |  |

|                    |                        | 0.05                                                  | 0.20 | μA    | +85°C      | 5.0V |                                |  |  |

|                    |                        |                                                       | 0.30 | μA    | +125°C     | 5.0V | Deep Sleep BOR:                |  |  |

|                    | PIC24F32KA3XX          | 0.03                                                  | _    | μA    | -40°C      | 1.8V | $\Delta$ ILPBOR <sup>(5)</sup> |  |  |

|                    |                        | 0.05                                                  | 0.20 | μA    | +85°C      | 3.3V |                                |  |  |

|                    |                        | _                                                     | 0.30 | μA    | +125°C     | 3.3V |                                |  |  |

| DC80               | PIC24FV32KA3XX         | 0.20                                                  | _    | μA    | -40°C      | 2.0V |                                |  |  |

|                    |                        | 0.70                                                  | 1.5  | μA    | +85°C      | 5.0V |                                |  |  |

|                    |                        | _                                                     | 1.5  | μA    | +125°C     | 5.0V | Deep Sleep WDT:                |  |  |

|                    | PIC24F32KA3XX          | 0.20                                                  |      | μA    | -40°C      | 1.8V | ∆ldswdt (LPRC) <sup>(6)</sup>  |  |  |

|                    |                        | 0.35                                                  | 0.8  | μA    | +85°C      | 3.3V |                                |  |  |

|                    |                        | _                                                     | 1.5  | μA    | +125°C     | 3.3V |                                |  |  |

#### TABLE 29-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

Legend: Unshaded rows represent PIC24F32KA3XX devices and shaded rows represent PIC24FV32KA3XX devices. Note 1: Data in the Typical column is at 3.3V, +25°C (PIC24F32KA3XX) or 5.0V, +25°C (PIC24FV32KA3XX) unless

otherwise stated. Parameters are for design guidance only and are not tested.

Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and set low, 2: PMSLP is set to '0' and WDT, etc., are all switched off.

3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

4: This current applies to Sleep only.

5: This current applies to Sleep and Deep Sleep.6: This current applies to Deep Sleep only.

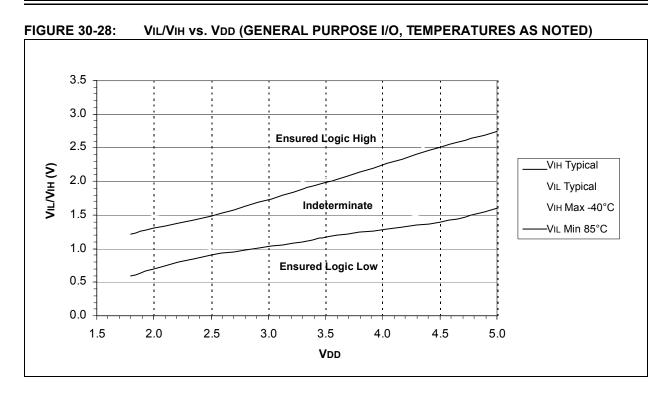

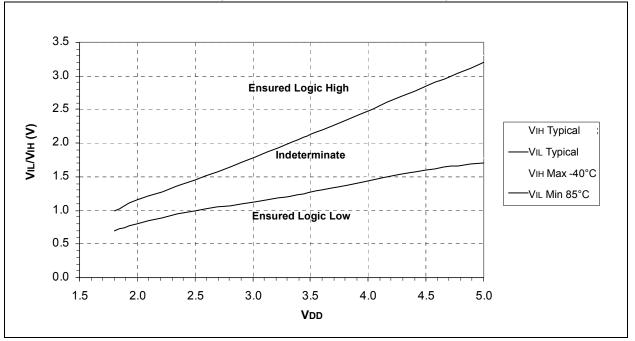

FIGURE 30-29: VIL/VIH vs. VDD (I<sup>2</sup>C<sup>™</sup>, TEMPERATURES AS NOTED)

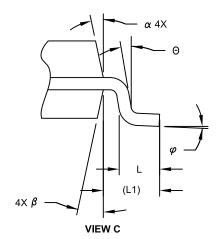

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |  |

|--------------------------|-------------|-----------|-----|------|--|--|

| Dimension                | Limits      | MIN       | NOM | MAX  |  |  |

| Number of Pins           | N           | 28        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |  |

| Overall Length           | D           | 17.90 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |  |

| Foot Length              | L           | 0.40 -    |     | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2