Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 20-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka301t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CN23     | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I   | ST     | Interrupt-on-Change Inputs                  |

| CN24     |                                  | 15                                | 12            | 42                     | 46             | -                                | 15                                | 12            | 42                     | 46             | 1   | ST     |                                             |

| CN25     |                                  | _                                 | _             | 37                     | 40             | -                                |                                   |               | 37                     | 40             | 1   | ST     |                                             |

| CN26     |                                  | _                                 | _             | 38                     | 41             |                                  |                                   |               | 38                     | 41             | I   | ST     |                                             |

| CN27     |                                  | 14                                | 11            | 41                     | 45             |                                  | 14                                | 11            | 41                     | 45             | I   | ST     |                                             |

| CN28     |                                  | _                                 | _             | 36                     | 39             |                                  |                                   |               | 36                     | 39             | I   | ST     |                                             |

| CN29     | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I   | ST     |                                             |

| CN30     | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I   | ST     |                                             |

| CN31     |                                  | _                                 | _             | 26                     | 28             | —                                | _                                 | —             | 26                     | 28             | I   | ST     |                                             |

| CN32     |                                  | _                                 | —             | 25                     | 27             | —                                | —                                 | —             | 25                     | 27             | 1   | ST     |                                             |

| CN33     |                                  | _                                 | —             | 32                     | 35             | —                                | —                                 | —             | 32                     | 35             | 1   | ST     |                                             |

| CN34     |                                  | _                                 | —             | 35                     | 38             | —                                | —                                 | —             | 35                     | 38             | I   | ST     |                                             |

| CN35     |                                  | _                                 | _             | 12                     | 13             | —                                | _                                 | —             | 12                     | 13             | I   | ST     |                                             |

| CN36     |                                  | _                                 | _             | 13                     | 14             | —                                | _                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CVREF    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I   | ANA    | Comparator Reference Positive Input Voltage |

| CVREF-   | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I   | ANA    | Comparator Reference Negative Input Voltage |

| CTCMP    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | CTMU Comparator Input                       |

| CTED1    | 14                               | 20                                | 17            | 7                      | 7              | 11                               | 2                                 | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I   | ST     |                                             |

| CTED3    | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I   | ST     |                                             |

| CTED4    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 1   | ST     |                                             |

| CTED5    | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I   | ST     |                                             |

| CTED6    | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     |                                             |

| CTED7    | _                                | _                                 | _             | 5                      | 5              | _                                | —                                 | _             | 5                      | 5              | I   | ST     |                                             |

| CTED8    | _                                | _                                 | —             | 13                     | 14             | —                                | —                                 | —             | 13                     | 14             | I   | ST     |                                             |

| CTED9    | _                                | 22                                | 19            | 9                      | 10             | —                                | 22                                | 19            | 9                      | 10             | I   | ST     |                                             |

| CTED10   | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I   | ST     | ]                                           |

| CTED11   | _                                | 21                                | 18            | 8                      | 9              | —                                | 21                                | 18            | 8                      | 9              | I   | ST     | ]                                           |

| CTED12   | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | ]                                           |

| CTED13   | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | 1   | ST     | 1                                           |

#### TABLE 4-9: I2Cx REGISTER MAP

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 | —       | _      | _       | _      | _      | _      | —      | _     |       |       |       | I2CF  | RCV   |       |       |       | 0000          |

| I2C1TRN   | 0202 | _       | _      | _       | —      | _      | _      | _      | _     |       |       |       | I2CT  | RN    |       |       |       | OOFF          |

| I2C1BRG   | 0204 | _       | _      | _       | —      | _      | _      | _      | _     |       |       |       | I2CE  | BRG   |       |       |       | 0000          |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | _       | _      | _       | —      | _      | _      |        |       |       |       | I2CA  | DD    |       |       |       |       | 0000          |

| I2C1MSK   | 020C | —       | _      | _       | —      | —      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

| I2C2RCV   | 0210 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CF  | RCV   |       |       |       | 0000          |

| I2C2TRN   | 0212 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CT  | RN    |       |       |       | OOFF          |

| I2C2BRG   | 0214 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |       | I2CE  | BRG   |       |       |       | 0000          |

| I2C2CON   | 0216 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT  | 0218 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD   | 021A | _       |        | _       | _      |        | _      |        |       |       | •     | I2CA  | DD    | •     | •     | •     | •     | 0000          |

| I2C2MSK   | 021C | _       |        | _       | _      | _      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: UARTx REGISTER MAP

|              |      | 0/11/1/  |        |          |        |        |        |       |       |          |          |       |       |       |        |        |       |               |

|--------------|------|----------|--------|----------|--------|--------|--------|-------|-------|----------|----------|-------|-------|-------|--------|--------|-------|---------------|

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE       | 0220 | UARTEN   | _      | USIDL    | IREN   | RTSMD  |        | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | —        |        | —        |        | _      |        | _     |       |          |          | U1T   | XREG  |       |        |        |       | XXXX          |

| U1RXREG      | 0226 | —        |        | —        |        | _      |        | _     |       |          |          | U1F   | RXREG |       |        |        |       | 0000          |

| U1BRG        | 0228 |          |        |          |        |        |        |       | I     | BRG      |          |       |       |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _        | _      | _        | —      | _      | _      | _     |       |          |          | U2T   | XREG  |       |        |        |       | XXXX          |

| U2RXREG      | 0236 | —        |        | —        |        | _      |        | _     |       |          |          | U2F   | RXREG |       |        |        |       | 0000          |

| U2BRG        | 0238 | BRG      |        |          |        |        |        |       | 0000  |          |          |       |       |       |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: SPIx REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|---------|--------|--------|---------|---------|---------|-------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN  |        | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0 | SRMPT | SPIROV | SR1MPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 | _      | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE     | SSEN  | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN  | SPIFSD | SPIFPOL | -      | _      | _       | _       | _       |       | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 |        |        |         |        |        |         |         | SPI1    | BUF   |        |        |        |        |        |        |        | 0000          |

| SPI2STAT     | 0260 | SPIEN  | _      | SPISIDL | -      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0 | SRMPT | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1     | 0262 | _      | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE     | SSEN  | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2     | 0264 | FRMEN  | SPIFSD | SPIFPOL | -      | _      | _       | _       | _       |       | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI2BUF      | 0268 |        |        |         |        |        |         |         | SPI2    | BUF   |        |        |        |        |        |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(2,3)</sup> | Bit 10 <sup>(2,3)</sup> | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2)</sup> | Bit 6 <sup>(4)</sup> | Bit 5 <sup>(1)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 02C0 |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               |                      | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | OODF          |

| PORTA        | 02C2 | _      |        | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA         | 02C4 |        | _      | _      | _      | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA         | 02C6 | _      |        | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This bit is available only when MCLRE = 1.

2: These bits are not implemented in 20-pin devices.

**3:** These bits are not implemented in 28-pin devices.

4: These bits are not implemented in FV devices.

#### TABLE 4-13: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(1)</sup> | Bit 10 <sup>(1)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(1)</sup> | Bit 5 <sup>(1)</sup> | Bit 4  | Bit 3 <sup>(1)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | XXXX          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | XXXX          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not implemented in 20-pin devices.

# 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |

|-------|------------------------------------------------------------------------------------|

|       | intended to be a comprehensive reference                                           |

|       | source. For more information on Flash pro-                                         |

|       | gramming, refer to the "PIC24F Family                                              |

|       | Reference Manual", Section 4. "Program                                             |

|       | Memory" (DS39715).                                                                 |

The PIC24FV32KA304 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FV32KA304 device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program mode Entry voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

# 5.1 Table Instructions and Flash Programming

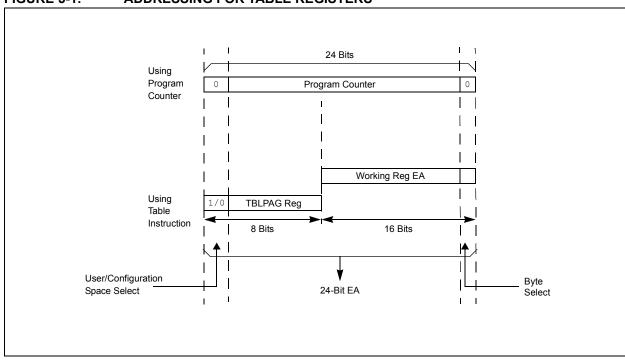

Regardless of the method used, Flash memory programming is done with the table read and write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

# 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Data EEPROM, refer to the *"PIC24F Family Reference Manual"*, Section 5. "Data EEPROM" (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFFh. The size of the data EEPROM is 256 words in the PIC24FV32KA304 family devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

# 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

#### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

| //Disable Interr | upts For 5 instruc | ctions |

|------------------|--------------------|--------|

| asm volatile (   | "disi #5");        |        |

| //Issue Unlock S | equence            |        |

| asm volatile (   | "mov #0x55, W0     | \n"    |

| "                | mov W0, NVMKEY     | \n"    |

| "                | mov #0xAA, W1      | \n"    |

| "                | mov W1, NVMKEY     | \n");  |

| // Perform Write | /Erase operations  |        |

| asm volatile (   | "bset NVMCON, #WR  | \n"    |

| "                | nop                | \n"    |

| "                | nop                | \n");  |

|                  |                    |        |

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

# TABLE 8-1:TRAP VECTOR DETAILS

# TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

| la farmar f O anna a           |               |             | AIVT    | In       | terrupt Bit Loca | ations       |

|--------------------------------|---------------|-------------|---------|----------|------------------|--------------|

| Interrupt Source               | Vector Number | IVT Address | Address | Flag     | Enable           | Priority     |

| ADC1 Conversion Done           | 13            | 00002Eh     | 00012Eh | IFS0<13> | IEC0<13>         | IPC3<6:4>    |

| Comparator Event               | 18            | 000038h     | 000138h | IFS1<2>  | IEC1<2>          | IPC4<10:8>   |

| CRC Generator                  | 67            | 00009Ah     | 00019Ah | IFS4<3>  | IEC4<3>          | IPC16<14:12> |

| СТМИ                           | 77            | 0000AEh     | 0001AEh | IFS4<13> | IEC4<13>         | IPC19<6:4>   |

| External Interrupt 0           | 0             | 000014h     | 000114h | IFS0<0>  | IEC0<0>          | IPC0<2:0>    |

| External Interrupt 1           | 20            | 00003Ch     | 00013Ch | IFS1<4>  | IEC1<4>          | IPC5<2:0>    |

| External Interrupt 2           | 29            | 00004Eh     | 00014Eh | IFS1<13> | IEC1<13>         | IPC7<6:4>    |

| I2C1 Master Event              | 17            | 000036h     | 000136h | IFS1<1>  | IEC1<1>          | IPC4<6:4>    |

| I2C1 Slave Event               | 16            | 000034h     | 000134h | IFS1<0>  | IEC1<0>          | IPC4<2:0>    |

| I2C2 Master Event              | 50            | 000078h     | 000178h | IFS3<2>  | IEC3<2>          | IPC12<10:8>  |

| I2C2 Slave Event               | 49            | 000076h     | 000176h | IFS3<1>  | IEC3<1>          | IPC12<6:4>   |

| Input Capture 1                | 1             | 000016h     | 000116h | IFS0<1>  | IEC0<1>          | IPC0<6:4>    |

| Input Capture 2                | 5             | 00001Eh     | 00011Eh | IFS0<5>  | IEC0<5>          | IPC1<6:4>    |

| Input Capture 3                | 37            | 00005Eh     | 00015Eh | IFS2<5>  | IEC2<5>          | IPC9<6:4>    |

| Input Change Notification      | 19            | 00003Ah     | 00013Ah | IFS1<3>  | IEC1<3>          | IPC4<14:12>  |

| HLVD (High/Low-Voltage Detect) | 72            | 0000A4h     | 0001A4h | IFS4<8>  | IEC4<8>          | IPC17<2:0>   |

| NVM – NVM Write Complete       | 15            | 000032h     | 000132h | IFS0<15> | IEC0<15>         | IPC3<14:12>  |

| Output Compare 1               | 2             | 000018h     | 000118h | IFS0<2>  | IEC0<2>          | IPC0<10:8>   |

| Output Compare 2               | 6             | 000020h     | 000120h | IFS0<6>  | IEC0<6>          | IPC1<10:8>   |

| Output Compare 3               | 25            | 000046h     | 000146h | IFS1<9>  | IEC1<9>          | IPC6<6:4>    |

| Real-Time Clock/Calendar       | 62            | 000090h     | 000190h | IFS3<14> | IEC3<14>         | IPC15<10:8>  |

| SPI1 Error                     | 9             | 000026h     | 000126h | IFS0<9>  | IEC0<9>          | IPC2<6:4>    |

| SPI1 Event                     | 10            | 000028h     | 000128h | IFS0<10> | IEC0<10>         | IPC2<10:8>   |

| SPI2 Error                     | 32            | 000054h     | 000154h | IFS2<0>  | IEC2<2>          | IPC8<2:0>    |

| SPI2 Event                     | 33            | 000056h     | 000156h | IFS2<1>  | IEC2<1>          | IPC8<6:4>    |

| Timer1                         | 3             | 00001Ah     | 00011Ah | IFS0<3>  | IEC0<3>          | IPC0<14:12>  |

| Timer2                         | 7             | 000022h     | 000122h | IFS0<7>  | IEC0<7>          | IPC1<14:12>  |

| Timer3                         | 8             | 000024h     | 000124h | IFS0<8>  | IEC0<8>          | IPC2<2:0>    |

| Timer4                         | 27            | 00004Ah     | 00014Ah | IFS1<11> | IEC1<11>         | IPC6<14:12>  |

| Timer5                         | 28            | 00004Ch     | 00015Ch | IFS1<12> | IEC1<12>         | IPC7<2:0>    |

| UART1 Error                    | 65            | 000096h     | 000196h | IFS4<1>  | IEC4<1>          | IPC16<6:4>   |

| UART1 Receiver                 | 11            | 00002Ah     | 00012Ah | IFS0<11> | IEC0<11>         | IPC2<14:12>  |

| UART1 Transmitter              | 12            | 00002Ch     | 00012Ch | IFS0<12> | IEC0<12>         | IPC3<2:0>    |

| UART2 Error                    | 66            | 000098h     | 000198h | IFS4<2>  | IEC4<2>          | IPC16<10:8>  |

| UART2 Receiver                 | 30            | 000050h     | 000150h | IFS1<14> | IEC1<14>         | IPC7<10:8>   |

| UART2 Transmitter              | 31            | 000052h     | 000152h | IFS1<15> | IEC1<15>         | IPC7<14:12>  |

| Ultra Low-Power Wake-up        | 80            | 0000B4h     | 0001B4h | IFS5<0>  | IEC5<0>          | IPC20<2:0>   |

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0      | U-0 | U-0         | U-0             | U-0 | U-0 | U-0 | U-0       |

|----------|-----|-------------|-----------------|-----|-----|-----|-----------|

| _        | —   | —           | —               | —   | —   | _   | —         |

| bit 15   |     |             | •               |     | •   |     | bit 8     |

|          |     |             |                 |     |     |     |           |

| U-0      | U-0 | U-0         | U-0             | U-0 | U-0 | U-0 | R/W-0, HS |

| _        | _   | —           | —               | —   | —   | _   | ULPWUIF   |

| bit 7    |     |             |                 |     |     |     | bit 0     |

|          |     |             |                 |     |     |     |           |

| l edenq. |     | HS = Hardwa | re Settable bit |     |     |     |           |

| Legend:           | HS = Hardware Settable bit |                             |                    |  |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

## REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                   | R/W-0              | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------|-------------------------|--------------------|-------------------|------------------|------------------|-----------------|---------|

| _                | U1RXIP2                 | U1RXIP1            | U1RXIP0           | _                | SPI1IP2          | SPI1IP1         | SPI1IP0 |

| bit 15           |                         |                    |                   |                  |                  |                 | bit 8   |

| U-0              | R/W-1                   | R/W-0              | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                | SPF1IP2                 | SPF1IP1            | SPF1IP0           |                  | T3IP2            | T3IP1           | T3IP0   |

| bit 7            |                         | 1                  |                   |                  |                  | 1               | bit (   |

| Legend:          |                         |                    |                   |                  |                  |                 |         |

| R = Readat       | ole bit                 | W = Writable       | bit               | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value a     | at POR                  | '1' = Bit is set   |                   | '0' = Bit is cle |                  | x = Bit is unkn | iown    |

|                  |                         |                    |                   |                  |                  |                 |         |

| bit 15           | Unimplemen              | ted: Read as '     | )'                |                  |                  |                 |         |

| bit 14-12        | -                       | : UART1 Rece       |                   | riority bits     |                  |                 |         |

|                  |                         | pt is Priority 7 ( | =                 | -                |                  |                 |         |

|                  | •                       |                    | 0 . ,             | • /              |                  |                 |         |

|                  | •                       |                    |                   |                  |                  |                 |         |

|                  | 001 = Interru           |                    |                   |                  |                  |                 |         |

|                  | -                       | ot source is dis   |                   |                  |                  |                 |         |

| bit 11           | -                       | ted: Read as '     |                   |                  |                  |                 |         |

| bit 10-8         |                         | SPI1 Event Int     | , ,               |                  |                  |                 |         |

|                  | 111 = Interru           | ot is Priority 7 ( | highest priority  | interrupt)       |                  |                 |         |

|                  | •                       |                    |                   |                  |                  |                 |         |

|                  | •<br>001 = Interru      | pt is Priority 1   |                   |                  |                  |                 |         |

|                  | 000 = Interru           | pt source is dis   | abled             |                  |                  |                 |         |

| bit 7            | Unimplemen              | ted: Read as '     | )'                |                  |                  |                 |         |

| bit 6-4          | SPF1IP<2:0>             | : SPI1 Fault Inf   | errupt Priority I | oits             |                  |                 |         |

|                  | 111 = Interru           | pt is Priority 7 ( | highest priority  | interrupt)       |                  |                 |         |

|                  | •                       |                    |                   |                  |                  |                 |         |

|                  | •                       |                    |                   |                  |                  |                 |         |

|                  | 001 = Interru           | ot is Priority 1   | abled             |                  |                  |                 |         |

|                  | -                       | ted: Read as '     |                   |                  |                  |                 |         |

| hit 3            |                         | imer3 Interrupt    |                   |                  |                  |                 |         |

|                  |                         |                    | •                 | interrunt)       |                  |                 |         |

|                  | 111 = Interru           | nt is Priority 7 ( |                   |                  |                  |                 |         |

|                  | 111 = Interruj<br>•     | pt is Priority 7 ( | nignest priority  | interrupt)       |                  |                 |         |

| bit 3<br>bit 2-0 | 111 = Interruj<br>•     | pt is Priority 7 ( | nignest priority  | interrupt)       |                  |                 |         |

|                  | •<br>•<br>001 = Interru |                    |                   | interrupt)       |                  |                 |         |

| R/W-1                     | R/W-0                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T4IP2                     | T4IP1                                                                                                          | T4IP0                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           |                                                                                                                |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>D</b> 444 4            | <b>D</b> 444.0                                                                                                 | <b>D</b> 444 0                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | -                                                                                                              | -                                                                                                                                                                                                                                                                                                                         | 0-0                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OC3IP2                    | OC3IP1                                                                                                         | OC3IP0                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           |                                                                                                                |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           |                                                                                                                |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| hit.                      | VV - VVritabla                                                                                                 | <b></b> ;+                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                             | antad hit rac                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | d aa '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           |                                                                                                                | DIL                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| POR                       | "1" = Bit is set                                                                                               |                                                                                                                                                                                                                                                                                                                           | $0^{\circ} = Bit is clea$                                                                                                                                                                                                                                                                   | ired                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           |                                                                                                                |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |