#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka302-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

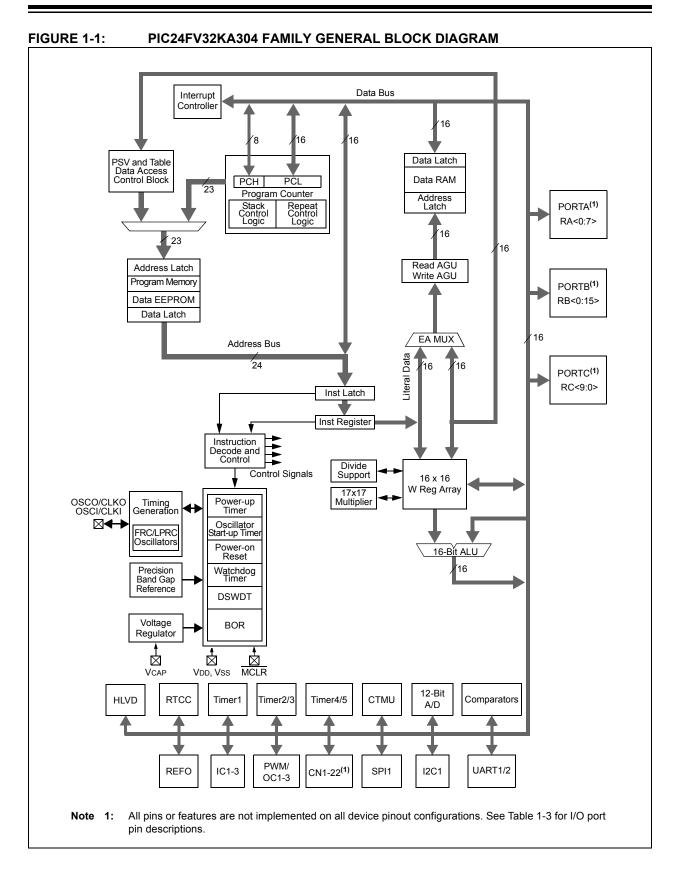

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 23  |

| 3.0   | СРИ                                                         |     |

| 4.0   | Memory Organization                                         | 35  |

| 5.0   | Flash Program Memory                                        | 57  |

| 6.0   | Data EEPROM Memory                                          | 63  |

| 7.0   | Resets                                                      | 69  |

| 8.0   | Interrupt Controller                                        |     |

| 9.0   | Oscillator Configuration                                    | 115 |

| 10.0  | Power-Saving Features                                       | 125 |

| 11.0  | I/O Ports                                                   | 135 |

| 12.0  | Timer1                                                      | 139 |

| 13.0  | Timer2/3 and Timer4/5                                       | 141 |

| 14.0  | Input Capture with Dedicated Timers                         | 147 |

| 15.0  | Output Compare with Dedicated Timers                        | 151 |

| 16.0  | Serial Peripheral Interface (SPI)                           |     |

| 17.0  |                                                             |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)          | 177 |

| 19.0  | Real-Time Clock and Calendar (RTCC)                         |     |

| 20.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator | 199 |

| 21.0  | High/Low-Voltage Detect (HLVD)                              | 205 |

| 22.0  | 12-Bit A/D Converter with Threshold Detect                  |     |

| 23.0  | Comparator Module                                           | 225 |

| 24.0  | Comparator Voltage Reference                                | 229 |

| 25.0  | Charge Time Measurement Unit (CTMU)                         |     |

| 26.0  | Special Features                                            | 239 |

| 27.0  | Development Support                                         | 251 |

|       | Instruction Set Summary                                     |     |

|       | Electrical Characteristics                                  |     |

| 30.0  | DC and AC Characteristics Graphs and Tables                 | 295 |

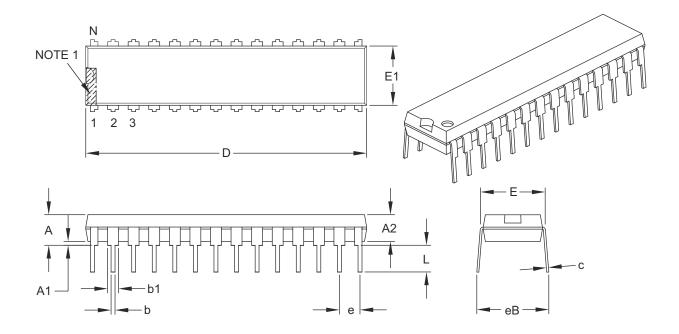

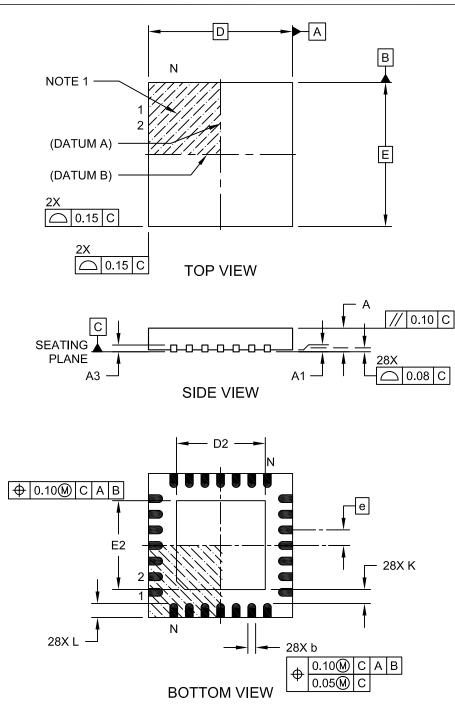

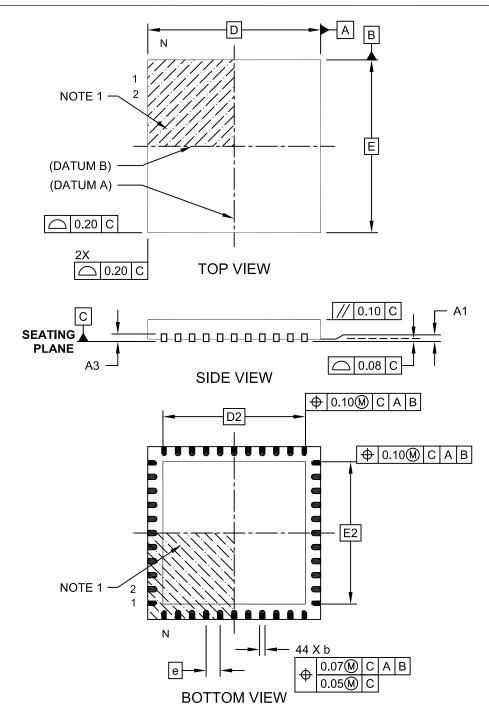

| 31.0  | Packaging Information                                       | 325 |

| Appe  | endix A: Revision History                                   | 351 |

| Index | κ                                                           | 353 |

| The I | Microchip Web Site                                          | 359 |

|       | omer Change Notification Service                            |     |

| Cust  | omer Support                                                | 359 |

| Read  | der Response                                                | 360 |

| Prod  | uct Identification System                                   |     |

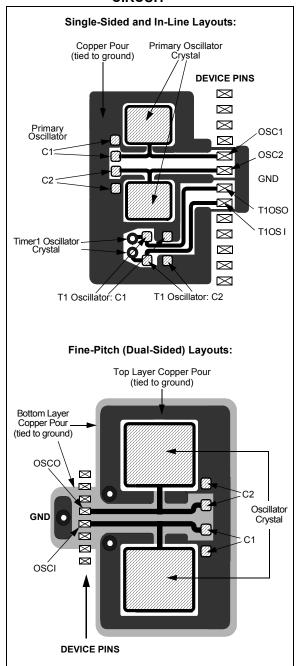

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

## 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

# FIGURE 2-5: SUGGESTED PLACEMENT

#### OF THE OSCILLATOR CIRCUIT

NOTES:

| R/W-0, HS   | S R/W-0, HS                       | R/W-0                                                                                                                                 | R/W-0                        | U-0               | R/C-0, HS          | R/W-0             | R/W-0          |  |

|-------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------|--------------------|-------------------|----------------|--|

| TRAPR       | IOPUWR                            | SBOREN                                                                                                                                | RETEN <sup>(3)</sup>         | —                 | DPSLP              | CM                | PMSLP          |  |

| bit 15      |                                   |                                                                                                                                       |                              |                   |                    |                   | bit 8          |  |

| R/W-0, H    | S R/W-0, HS                       | R/W-0, HS                                                                                                                             | R/W-0, HS                    | R/W-0, HS         | R/W-0, HS          | R/W-1, HS         | R/W-1, HS      |  |

| EXTR        | SWR                               | SWDTEN <sup>(2)</sup>                                                                                                                 | WDTO                         | SLEEP             | IDLE               | BOR               | POR            |  |

| bit 7       |                                   |                                                                                                                                       |                              |                   |                    |                   | bit 0          |  |

| <del></del> |                                   | <u> </u>                                                                                                                              |                              |                   | <u> </u>           |                   |                |  |

| Legend:     |                                   | C = Clearable                                                                                                                         |                              |                   | re Settable bit    |                   |                |  |

| R = Reada   |                                   | W = Writable b                                                                                                                        | bit                          | •                 | nented bit, read   | as '0'            |                |  |

| -n = Value  | at POR                            | '1' = Bit is set                                                                                                                      |                              | '0' = Bit is cle  | ared               | x = Bit is unkn   | iown           |  |

| bit 15      | TRAPR: Tran                       | Reset Flag bit                                                                                                                        |                              |                   |                    |                   |                |  |

|             | -                                 | onflict Reset has                                                                                                                     | occurred                     |                   |                    |                   |                |  |

|             |                                   | onflict Reset has                                                                                                                     |                              |                   |                    |                   |                |  |

| bit 14      | IOPUWR: Ille                      | gal Opcode or l                                                                                                                       | Jninitialized W              | Access Reset      | Flag bit           |                   |                |  |

|             | 1 = An illegal<br>Pointer c       | l opcode detecti<br>aused a Reset                                                                                                     | on, an illegal a             | ddress mode o     | or Uninitialized V | V register used   | as an Address  |  |

|             | 0 = An illegal                    | I opcode or Unir                                                                                                                      | nitialized W Re              | set has not oc    | curred             |                   |                |  |

| bit 13      | SBOREN: So                        | oftware Enable/E                                                                                                                      | Disable of BOF               | R bit             |                    |                   |                |  |

|             |                                   | irned on in softw<br>irned off in softw                                                                                               |                              |                   |                    |                   |                |  |

| bit 12      | RETEN: Rete                       | ention Sleep Mo                                                                                                                       | de control bit <sup>(3</sup> | 6)                |                    |                   |                |  |

|             |                                   | d voltage supply<br>d voltage supply                                                                                                  |                              |                   |                    |                   |                |  |

| bit 11      | Unimplemen                        | ted: Read as '0                                                                                                                       | 3                            |                   |                    |                   |                |  |

| bit 10      | DPSLP: Deep                       | p Sleep Mode F                                                                                                                        | lag bit                      |                   |                    |                   |                |  |

|             | •                                 | ep has occurred<br>ep has not occu                                                                                                    |                              |                   |                    |                   |                |  |

| bit 9       | CM: Configur                      | ation Word Misr                                                                                                                       | natch Reset F                | lag bit           |                    |                   |                |  |

|             | Ų                                 | uration Word Mis<br>uration Word Mis                                                                                                  |                              |                   | ed                 |                   |                |  |

| bit 8       | PMSLP: Proc                       | gram Memory Po                                                                                                                        | ower During S                | leep bit          |                    |                   |                |  |

|             |                                   | memory bias vo<br>memory bias v<br>mode                                                                                               |                              |                   |                    | the Voltage Re    | gulator enters |  |

| bit 7       | -                                 |                                                                                                                                       | R) Pin bit                   |                   |                    |                   |                |  |

| Sit 7       | 1 = A Master                      | EXTR: External Reset (MCLR) Pin bit<br>1 = A Master Clear (pin) Reset has occurred<br>0 = A Master Clear (pin) Reset has not occurred |                              |                   |                    |                   |                |  |

| bit 6       |                                   | ire Reset (Instru                                                                                                                     |                              |                   |                    |                   |                |  |

|             | 1 <b>= A</b> reset                | instruction has I<br>instruction has I                                                                                                | peen executed                |                   |                    |                   |                |  |

| Note 1:     | All of the Reset a cause a device |                                                                                                                                       | be set or clear              | ed in software.   | Setting one of the | nese bits in soft | ware does not  |  |

| 2:          | If the FWDTEN SWDTEN bit se       | x Configuration I                                                                                                                     | bit is '1' (unpro            | ogrammed), the    | e WDT is always    | enabled regar     | dless of the   |  |

| 3:          | This is implement                 | -                                                                                                                                     | V32KA3XX pa                  | arts only; not us | sed on PIC24F3     | 2KA3XX device     | es.            |  |

|             |                                   |                                                                                                                                       |                              |                   |                    |                   |                |  |

# REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

#### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |  |  |

|--------|--------------|-----|-----|-----|-----|-----|-------------------|--|--|

| —      | —            | —   | —   | —   | —   | —   | DC <sup>(1)</sup> |  |  |

| bit 15 | bit 15 bit 8 |     |     |     |     |     |                   |  |  |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-9 Unimplemented: Read as '0'

| bit 7 5 | IPL<2:0>: CPU Interrupt Priority Level              | Status hits (2,3) |

|---------|-----------------------------------------------------|-------------------|

| bit 7-5 | <b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level | Status Dits       |

- 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the Interrupt Priority Level if IPL3 = 1.

- **3:** The IPLx Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and bits 4 through 0 are described in Section 3.0 "CPU".

#### REGISTER 11-2: ANSB: ANALOG SELECTION (PORTB)

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|-----|-----|-----|-------|

| ANSB15 | ANSB14 | ANSB13 | ANSB12 | —   | —   | —   | —     |

| bit 15 |        |        |        |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|----------------------|-------|-------|-------|

| —     | —   | —   | ANSB4 | ANSB3 <sup>(1)</sup> | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |     |     |       |                      |       |       | bit 0 |

## Legend:

bit 7

| Legena:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-12 ANSB<15:12>: Analog Select Control bits

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- bit 11-5 Unimplemented: Read as '0'

- bit 4-0 ANSB<4:0>: Analog Select Control bits<sup>(1)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- Note 1: The ANSB3 bit is not available on 20-pin devices.

### REGISTER 11-3: ANSC ANALOG SELECTION (PORTC)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0                  | U-0                  | U-0                  |

|--------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

| —      | —   | —   | —   | —   | —                    | —                    | —                    |

| bit 15 |     |     |     |     |                      |                      | bit 8                |

|        |     |     |     |     |                      |                      |                      |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                | R/W-1                | R/W-1                |

| —      | —   | —   | —   | —   | ANSC2 <sup>(1)</sup> | ANSC1 <sup>(1)</sup> | ANSC0 <sup>(1)</sup> |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 ANSC<2:0>: Analog Select Control bits<sup>(1)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

Note 1: These bits are not available on 20-pin or 28-pin devices.

bit 0

| R/W-0              | U-0                                                                                                                         | R/W-0                                                                                                       | U-0                   | U-0                       | U-0             | U-0                  | U-0         |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------|----------------------|-------------|--|--|--|

| TON <sup>(1)</sup> | 0-0                                                                                                                         | TSIDL <sup>(1)</sup>                                                                                        | 0-0                   | 0-0                       | 0-0             | 0-0                  | 0-0         |  |  |  |

| bit 15             |                                                                                                                             | TSIDL                                                                                                       |                       | _                         |                 |                      | <br>bit 8   |  |  |  |

|                    |                                                                                                                             |                                                                                                             |                       |                           |                 |                      | bit c       |  |  |  |

| U-0                | R/W-0                                                                                                                       | R/W-0                                                                                                       | R/W-0                 | U-0                       | U-0             | R/W-0                | U-0         |  |  |  |

| _                  | TGATE <sup>(1)</sup>                                                                                                        | TCKPS1 <sup>(1)</sup>                                                                                       | TCKPS0 <sup>(1)</sup> |                           | _               | TCS <sup>(1)</sup>   |             |  |  |  |

| bit 7              |                                                                                                                             |                                                                                                             |                       |                           |                 |                      | bit 0       |  |  |  |

|                    |                                                                                                                             |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

| Legend:            |                                                                                                                             |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

| R = Reada          |                                                                                                                             | W = Writable                                                                                                | bit                   | -                         | nented bit, rea |                      |             |  |  |  |

| -n = Value         | at POR                                                                                                                      | '1' = Bit is set                                                                                            |                       | '0' = Bit is clea         | ared            | x = Bit is unknow    | <u>ו</u>    |  |  |  |

| 1.11.45            |                                                                                                                             | o                                                                                                           |                       |                           |                 |                      |             |  |  |  |

| bit 15             | TON: Timery                                                                                                                 |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    | 1 = Starts 16<br>0 = Stops 16                                                                                               |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

| bit 14             | -                                                                                                                           | ited: Read as '(                                                                                            | )'                    |                           |                 |                      |             |  |  |  |

| bit 13             | -                                                                                                                           |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    | <b>TSIDL:</b> Timery Stop in Idle Mode bit <sup>(1)</sup><br>1 = Discontinues module operation when device enters Idle mode |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    |                                                                                                                             | s module opera                                                                                              |                       |                           |                 |                      |             |  |  |  |

| bit 12-7           | Unimplemen                                                                                                                  | ted: Read as '0                                                                                             | )'                    |                           |                 |                      |             |  |  |  |

| bit 6              | TGATE: Time                                                                                                                 | ery Gated Time                                                                                              | Accumulation          | Enable bit <sup>(1)</sup> |                 |                      |             |  |  |  |

|                    | When TCS =                                                                                                                  |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    | This bit is ignored.                                                                                                        |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    | $\frac{\text{When TCS} = 0}{2}$                                                                                             |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    |                                                                                                                             | <ul> <li>1 = Gated time accumulation is enabled</li> <li>0 = Gated time accumulation is disabled</li> </ul> |                       |                           |                 |                      |             |  |  |  |

| bit 5-4            |                                                                                                                             | : Timery Input (                                                                                            |                       | Select hits(1)            |                 |                      |             |  |  |  |

| bit 0 4            | 11 = 1:256                                                                                                                  | . Thirdy input (                                                                                            |                       |                           |                 |                      |             |  |  |  |

|                    | 10 = 1:64                                                                                                                   |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    | 01 <b>= 1:8</b>                                                                                                             |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

|                    | 00 = 1:1                                                                                                                    |                                                                                                             |                       |                           |                 |                      |             |  |  |  |

| bit 3-2            | •                                                                                                                           | ted: Read as '0                                                                                             |                       |                           |                 |                      |             |  |  |  |

| bit 1              |                                                                                                                             | Clock Source S                                                                                              |                       |                           |                 |                      |             |  |  |  |

|                    |                                                                                                                             | clock is from th<br>clock (Fosc/2)                                                                          | e T3CK pin (o         | n the rising edg          | le)             |                      |             |  |  |  |

| bit 0              | Unimplemen                                                                                                                  | ted: Read as 'o                                                                                             | )'                    |                           |                 |                      |             |  |  |  |

| Note 1:            | When 22 hit ener                                                                                                            | ation is anabled                                                                                            |                       | - 1) those hite l         | have no affact  | on Timon ( operation | - All timer |  |  |  |

#### REGISTER 13-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER

**Note 1:** When 32-bit operation is enabled (TxCON<3> = 1), these bits have no effect on Timery operation. All timer functions are set through the TxCON register.

#### **REGISTER 15-1:** OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)

#### bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: Initialize OCx pin low; toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize OCx pin low; toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- **Note 1:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

HS = Hardware Settable bit

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | R/W-0               | R/W-0               | R/W-0 |

|--------|--------|----------|-------|-----|---------------------|---------------------|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | —   | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32  |

| bit 15 |        |          |       |     |                     |                     | bit 8 |

| R/W-0  | R/W-0, HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|-----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT  | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |        |          |          |          |          | bit 0    |

| Legenu.    |                                                                                                               |                                             |                                   |

|------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|

| R = Read   | able bit W = Writable bit                                                                                     | U = Unimplemented bit,                      | read as '0'                       |

| -n = Value | e at POR '1' = Bit is set                                                                                     | '0' = Bit is cleared                        | x = Bit is unknown                |

|            |                                                                                                               |                                             |                                   |

| bit 15     | FLTMD: Fault Mode Select bit                                                                                  |                                             |                                   |

|            | 1 = Fault mode is maintained until the                                                                        | Fault source is removed and                 | I the corresponding OCFLTx bit is |

|            | cleared in software<br>0 = Fault mode is maintained until the                                                 | Fault source is removed and                 | a new PWM period starts           |

| bit 14     | FLTOUT: Fault Out bit                                                                                         |                                             |                                   |

|            | 1 = PWM output is driven high on a Fa                                                                         | ault                                        |                                   |

|            | 0 = PWM output is driven low on a Fai                                                                         | ult                                         |                                   |

| bit 13     | FLTTRIEN: Fault Output State Select b                                                                         |                                             |                                   |

|            | <ul> <li>1 = Pin is forced to an output on a Fau</li> <li>0 = Pin I/O condition is unaffected by a</li> </ul> |                                             |                                   |

| bit 12     | OCINV: Output Compare x Invert bit                                                                            | a Fault                                     |                                   |

|            | 1 = OCx output is inverted                                                                                    |                                             |                                   |

|            | 0 = OCx output is not inverted                                                                                |                                             |                                   |

| bit 11     | Unimplemented: Read as '0'                                                                                    |                                             |                                   |

| bit 10-9   | DCB<1:0>: Output Compare x Pulse-V                                                                            | Vidth Least Significant bits <sup>(3)</sup> |                                   |

|            | 11 = Delays OCx falling edge by $3/4$ of                                                                      | •                                           |                                   |

|            | 10 = Delays OCx falling edge by 1/2 of<br>01 = Delays OCx falling edge by 1/4 of                              | -                                           |                                   |

|            | 00 = OCx falling edge occurs at the sta                                                                       | 2                                           |                                   |

| bit 8      | OC32: Cascade Two Output Compare                                                                              | Modules Enable bit (32-bit op               | peration)                         |

|            | 1 = Cascade module operation is enal                                                                          |                                             |                                   |

| h:+ 7      | 0 = Cascade module operation is disa                                                                          |                                             |                                   |

| bit 7      | OCTRIG: Output Compare x Sync/Trig<br>1 = Triggers OCx from source designa                                    | -                                           |                                   |

|            | 0 = Synchronizes OCx with source designed                                                                     |                                             | its                               |

| bit 6      | TRIGSTAT: Timer Trigger Status bit                                                                            |                                             |                                   |

|            | 1 = Timer source has been triggered a                                                                         |                                             |                                   |

|            | 0 = Timer source has not been trigger                                                                         | -                                           |                                   |

| bit 5      | <b>OCTRIS:</b> Output Compare x Output Pi                                                                     | n Direction Select bit                      |                                   |

|            | <ul> <li>1 = OCx pin is tri-stated</li> <li>0 = Output Compare x peripheral is con</li> </ul>                 | anected to the OCx nin                      |                                   |

|            |                                                                                                               |                                             |                                   |

| Note 1:    | Do not use an output compare module as i equivalent SYNCSELx setting.                                         | ts own trigger source, either t             | by selecting this mode or another |

| 2:         | Use these inputs as trigger sources only ar                                                                   | nd never as Sync sources.                   |                                   |

| 3:         | These bits affect the rising edge when OCI                                                                    | NV = 1. The bits have no effe               | ct when the OCMx bits             |

|            | (OCxCON1<2:0>) = 001.                                                                                         |                                             |                                   |

Legend:

# EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 16-1: SAMPLE SCKx FREQUENCIES<sup>(1,2)</sup>

|                            | Fcy = 16 MHz |         |      | Secondary Prescaler Settings |      |      |  |  |  |

|----------------------------|--------------|---------|------|------------------------------|------|------|--|--|--|

|                            |              | 1:1     | 2:1  | 4:1                          | 6:1  | 8:1  |  |  |  |

| Primary Prescaler Settings | 1:1          | Invalid | 8000 | 4000                         | 2667 | 2000 |  |  |  |

|                            | 4:1          | 4000    | 2000 | 1000                         | 667  | 500  |  |  |  |

|                            | 16:1         | 1000    | 500  | 250                          | 167  | 125  |  |  |  |

|                            | 64:1         | 250     | 125  | 63                           | 42   | 31   |  |  |  |

| Fcy <b>= 5 MHz</b>         |              |         |      |                              |      |      |  |  |  |

| Primary Prescaler Settings | 1:1          | 5000    | 2500 | 1250                         | 833  | 625  |  |  |  |

|                            | 4:1          | 1250    | 625  | 313                          | 208  | 156  |  |  |  |

|                            | 16:1         | 313     | 156  | 78                           | 52   | 39   |  |  |  |

|                            | 64:1         | 78      | 39   | 20                           | 13   | 10   |  |  |  |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: SCKx frequencies are indicated in kHz.

#### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   |     |     | —   | _   | AMSK9 | AMSK8 |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enables masking for bit x of an incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

### REGISTER 17-4: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0     | R/W-0     | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----------|-----------|-----|-----|-----|-------|

| —     | —   | SMBUSDEL2 | SMBUSDEL1 | _   | —   | —   | —     |

| bit 7 |     |           |           |     |     |     | bit 0 |

| Legend:           |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

| bit 5   | SMBUSDEL2: SMBus SDA2 Input Delay Select bit                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The I2C2 module is configured for a longer SMBus input delay (nominal 300 ns delay)</li> <li>0 = The I2C2 module is configured for a legacy input delay (nominal 150 ns delay)</li> </ul> |

| bit 4   | SMBUSDEL1: SMBus SDA1 Input Delay Select bit                                                                                                                                                           |

|         | <ul> <li>1 = The I2C1 module is configured for a longer SMBus input delay (nominal 300 ns delay)</li> <li>0 = The I2C1 module is configured for a legacy input delay (nominal 150 ns delay)</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                             |

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0        | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |  |  |

|--------------|--------|----------|-----|-----------|-------|----------|----------|--|--|

| UTXISEL1     | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |  |  |

| bit 15 bit 8 |        |          |     |           |       |          |          |  |  |

| R/W-0       | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |  |  |

|-------------|----------|-------|----------|----------|----------|-----------|----------|--|--|

| URXISEL1    | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |  |  |

| bit 7 bit 0 |          |       |          |          |          |           |          |  |  |

| Legend:                    | HC = Hardware Clearable bit |                             |                    |

|----------------------------|-----------------------------|-----------------------------|--------------------|

| HS = Hardware Settable bit | C = Clearable bit           | HSC = Hardware Settable/Cle | earable bit        |

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR          | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

| bit 14  | UTXINV: IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit                                                                                                                                                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                            |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                              |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                              |

|         | $\frac{\text{If IREN = 1:}}{\text{IREN = 1:}}$                                                                                                                                                                                                                                                                                                                 |

|         | 1 = UxTX Idle '1'<br>0 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                         |

| 1.11.40 |                                                                                                                                                                                                                                                                                                                                                                |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                     |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                                                                                                                                                          |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                                                                                                                                                           |

| bit 10  | UTXEN: UARTx Transmit Enable bit                                                                                                                                                                                                                                                                                                                               |

|         | 1 = Transmit is enabled; UxTX pin is controlled by UARTx                                                                                                                                                                                                                                                                                                       |

|         | 0 = Transmit is disabled; any pending transmission is aborted and the buffer is reset. UxTX pin is<br>controlled by the PORT register.                                                                                                                                                                                                                         |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                       |

|         | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                    |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                    |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Transmit Shift Register is empty and the transmit buffer is empty (the last transmission has<br/>completed)</li> </ul>                                                                                                                                                                                                                            |

|         | 0 = Transmit Shift Register is not empty; a transmission is in progress or queued                                                                                                                                                                                                                                                                              |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is set on a RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on a RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer;</li> </ul> |

|         | receive buffer has one or more characters.                                                                                                                                                                                                                                                                                                                     |

#### CTMUCONO, CTMU CONTROL DECISTER 2

| REGISTER 2    |                                                                                  | JCON2: CTM       |                 |                   |                  |                 |          |  |  |  |  |

|---------------|----------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|--|

| R/W-0         | R/W-0                                                                            | R/W-0            | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |  |

| EDG1MOD       | EDG1POL                                                                          | EDG1SEL3         | EDG1SEL2        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                  |                  |                 |                   |                  |                 | bit      |  |  |  |  |

| R/W-0         | R/W-0                                                                            | R/W-0            | R/W-0           | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                          | EDG2SEL3         | EDG2SEL2        |                   |                  | 0-0             | 0-0      |  |  |  |  |

|               | EDG2POL                                                                          | EDG25EL3         | EDG25EL2        | EDG2SEL1          | EDG2SEL0         |                 |          |  |  |  |  |

| bit 7         |                                                                                  |                  |                 |                   |                  |                 | bit      |  |  |  |  |

| Legend:       |                                                                                  |                  |                 |                   |                  |                 |          |  |  |  |  |

| R = Readable  | e bit                                                                            | W = Writable     | bit             | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                                              | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |  |

| bit 15        |                                                                                  | Edge 1 Edge-So   | ansitiva Salact | bit               |                  |                 |          |  |  |  |  |

|               |                                                                                  |                  |                 | DIL               |                  |                 |          |  |  |  |  |

|               | 1 = Input is edge-sensitive<br>0 = Input is level-sensitive                      |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 14        | EDG1POL: Edge 1 Polarity Select bit                                              |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1 = Edge 1 is programmed for a positive edge response                            |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = Edge 1 is programmed for a negative edge response                            |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 13-10     | EDG1SEL<3:0>: Edge 1 Source Select bits                                          |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1111 = Edge 1 source is Comparator 3 output                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1110 = Edge 1 source is Comparator 2 output                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1101 = Edge 1 source is Comparator 1 output                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1100 = Edge 1 source is IC3                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1011 = Edge 1 source is IC2                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1010 = Edge 1 source is IC1                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1001 = Edge 1 source is CTED8                                                    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1000 = Edge 1 source is CTED7                                                    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0111 = Edge 1 source is CTED6                                                    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0110 = Edge 1 source is CTED5                                                    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0101 = Edge 1 source is CTED4<br>0100 = Edge 1 source is CTED3 <sup>(2)</sup>    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0011 = Edge 1 source is CTED1                                                    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0010 = Edge 1 source is CTED2                                                    |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0001 = Edge 1 source is OC1                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0000 = Edge 1 source is Timer1                                                   |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 9         | EDG2STAT: Edge 2 Status bit                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | Indicates the status of Edge 2 and can be written to control the current source. |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1 = Edge 2 has occurred                                                          |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = Edge 2 has not occurred                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 8         | EDG1STAT: Edge 1 Status bit                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control the current source. |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1 = Edge 1 has occurred                                                          |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = Edge 1 has not occurred                                                      |                  |                 |                   |                  |                 |          |  |  |  |  |

|               | EDG2MOD: Edge 2 Edge-Sensitive Select bit                                        |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 7         | EDG2MOD: E                                                                       | Edge 2 Edge-Se   |                 | bit               |                  |                 |          |  |  |  |  |

| bit 7         | <b>EDG2MOD:</b> E                                                                |                  |                 | bit               |                  |                 |          |  |  |  |  |

- Note 1: Edge sources, CTED11 and CTED12, are not available on PIC24FV32KA302 devices.

- 2: Edge sources, CTED3, CTED11, CTED12 and CTED13, are not available on PIC24FV32KA301 devices.

| АС СНА                                         | ARACTE                           | RISTICS                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                                            |

|------------------------------------------------|----------------------------------|----------------------------------|------------------------------------------------------|--------------------|-----|-------|------------------------------------------------------------|

| Param<br>No. Sym Characteristic <sup>(1)</sup> |                                  | Characteristic <sup>(1)</sup>    | Min                                                  | Тур <sup>(2)</sup> | Max | Units | Conditions                                                 |

| OS50                                           | Fplli                            | PLL Input Frequency<br>Range     | 4                                                    | —                  | 8   | MHz   | ECPLL, HSPLL modes, $-40^{\circ}C \le TA \le +85^{\circ}C$ |

| OS51                                           | Fsys                             | PLL Output Frequency<br>Range    | 16                                                   | —                  | 32  | MHz   | $-40^{\circ}C \le TA \le +85^{\circ}C$                     |

| OS52                                           | TLOCK                            | PLL Start-up Time<br>(Lock Time) | _                                                    | 1                  | 2   | ms    |                                                            |

| OS53                                           | S53 DCLK CLKO Stability (Jitter) |                                  | -2                                                   | 1                  | 2   | %     | Measured over a 100 ms<br>period                           |

## TABLE 29-20: PLL CLOCK TIMING SPECIFICATIONS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 29-21: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| АС СНА                      | RACTERISTICS                                 |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                                        |                                                                                                                                                                        |  |  |  |  |

|-----------------------------|----------------------------------------------|-----|------------------------------------------------------|-----|-------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No. Characteristic |                                              | Min | Тур                                                  | Max | Units | Conditions                             |                                                                                                                                                                        |  |  |  |  |

| F20                         | Internal FRC Accuracy @ 8 MHz <sup>(1)</sup> |     |                                                      |     |       |                                        |                                                                                                                                                                        |  |  |  |  |