Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 13x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka302-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams**

|         |              |                                                                                              |          | Pin Feat                                                  | ures                                                     |

|---------|--------------|----------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------|----------------------------------------------------------|

|         |              | 48-Pin UQFN <sup>(1,2,3)</sup>                                                               | Pin      | PIC24FVXXKA304                                            | PIC24FXXKA304                                            |

|         |              |                                                                                              | 1        | SDA1/T1CK/U1RTS/CTED4/CN21/RB9                            | SDA1/T1CK/U1RTS/CTED4/CN21<br>RB9                        |

|         |              |                                                                                              | 2        | U1RX/CN18/RC6                                             | U1RX/CN18/RC6                                            |

|         |              |                                                                                              | 3        | U1TX/CN17/RC7                                             | U1TX/CN17/RC7                                            |

|         |              | RBS<br>V V V V V V V V V V V V V V V V V V V                                                 | 4        | OC2/CN20/RC8                                              | OC2/CN20/RC8                                             |

|         |              | <u> </u>                                                                                     | 5        | IC2/CTED7/CN19/RC9                                        | IC2/CTED7/CN19/RC9                                       |

|         | RB9          | JU 1604                                                                                      | 6        | IC1/CTED3/CN9/RA7                                         | IC1/CTED3/CN9/RA7                                        |

|         | RC6<br>RC7   | _2 35 □ RA8                                                                                  | 7        | VCAP                                                      | C20UT/OC1/CTED1/INT2CN8/R                                |

|         | RC8          |                                                                                              | 8        | N/C                                                       | N/C                                                      |

|         | RC9          | 5 32 N/C                                                                                     | 9        | PGED2/SDI1/CTED11/CN16/RB10                               | PGED2/SDI1/CTED11/CN16/RB1                               |

| A6 or \ | RA7<br>√CAP  |                                                                                              | 10       | PGEC2/SCK1/CTED9/CN15/RB11                                | PGEC2/SCK1/CTED9/CN15/RB1                                |

|         | N/C          | 3 <b>FIC24FAARA304</b> 29 <b>R</b> C2                                                        | 11       | AN12/HLVDIN/CTED2/INT2/CN14/RB12                          | AN12/HLVDIN/CTED2/CN14/RB1                               |

|         | RB10<br>RB11 |                                                                                              | 12       | AN11/SDO1/CTPLS/CN13/RB13                                 | AN11/SDO1/CTPLS/CN13/RB13                                |

| R       | RB12         | 11 26 RB3                                                                                    | 13       | OC3/CN35/RA10                                             | OC3/CN35/RA10                                            |

| R       | RB13         | 12<br>♀≠♀♀♀♀♀≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈≈                                                 | 14       | IC3/CTED8/CN36/RA11                                       | IC3/CTED8/CN36/RA11                                      |

|         |              |                                                                                              | 15       | CVREF/AN10/C3INB/RTCC/<br>C1OUT/OCFA/CTED5/INT1/CN12/RB14 | CVREF/AN10/C3INB/RTCC/C10UT<br>OCFA/CTED5/INT1/CN12/RB14 |

|         |              | Ra10<br>Ra11<br>RB14<br>VSS/AVSS<br>VDD/AVD5<br>NUCLR/RA5<br>RA0<br>RB0<br>RB0<br>RB1<br>RB1 | 16       | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15          | AN9/C3INA/T3CK/T2CK/REFO/<br>SS1/CTED6/CN11/RB15         |

|         |              | Z  ≥                                                                                         | 17       | Vss/AVss                                                  | Vss/AVss                                                 |

|         |              |                                                                                              | 18       | Vdd/AVdd                                                  | Vdd/AVdd                                                 |

|         |              |                                                                                              | 19       | MCLR/RA5                                                  | MCLR/RA5                                                 |

|         |              |                                                                                              | 20       | N/C                                                       | N/C                                                      |

|         |              |                                                                                              | 21       | VREF+/CVREF+/AN0/C3INC/<br>CTED1/CN2/RA0                  | VREF+/CVREF+/AN0/C3INC/CN2/<br>RA0                       |

|         |              |                                                                                              | 22       | CVREF-/VREF-/AN1/CN3/RA1                                  | CVREF-/VREF-/AN1/CN3/RA1                                 |

|         |              |                                                                                              | 23       | PGED1/AN2/ULPWU/CTCMP/C1IND/<br>C2INB/C3IND/U2TX/CN4/RB0  | PGED1/AN2/ULPWU/CTCMP/C1II<br>C2INB/C3IND/U2TX/CN4/RB0   |

|         |              |                                                                                              | 24       | PGEC1/AN3/C1INC/C2INA/U2RX/<br>CTED12/CN5/RB1             | PGEC1/AN3/C1INC/C2INA/U2R><br>CTED12/CN5/RB1             |

|         |              |                                                                                              | 25       | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2         | AN4/C1INB/C2IND/SDA2/T5CK/<br>T4CK/CTED13/CN6/RB2        |

|         |              |                                                                                              | 26       | AN5/C1INA/C2INC/SCL2/CN7/RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RE                              |

|         |              |                                                                                              | 27       | AN6/CN32/RC0                                              | AN6/CN32/RC0                                             |

|         |              |                                                                                              | 28       | AN7/CN31/RC1                                              | AN7/CN31/RC1                                             |

|         |              |                                                                                              | 29       | AN8/CN10/RC2                                              | AN8/CN10/RC2                                             |

|         |              |                                                                                              | 30       | VDD                                                       | VDD                                                      |

|         |              |                                                                                              | 31       | Vss                                                       | Vss                                                      |

|         |              |                                                                                              | 32       |                                                           |                                                          |

|         |              |                                                                                              | 33       | OSCI/AN13/CLKI/CN30/RA2                                   | OSCI/AN13/CLKI/CN30/RA2                                  |

|         |              |                                                                                              | 34       | OSCO/AN14/CLKO/CN29/RA3<br>OCFB/CN33/RA8                  | OSCO/AN14/CLKO/CN29/RA3                                  |

|         |              |                                                                                              | 35       | SOSCI/AN15/U2RTS/CN1/RB4                                  |                                                          |

|         |              |                                                                                              | 36       |                                                           | SOSCI/AN15/U2RTS/CN1/RB4                                 |

|         |              |                                                                                              | 37       | SOSCO/SCLKI/U2CTS/CN0/RA4                                 | SOSCO/SCLKI/U2CTS/CN0/RA4                                |

| egen    | nd:          | Pin numbers in <b>bold</b> indicate pin func-                                                | 38       | SS2/CN34/RA9                                              | SS2/CN34/RA9                                             |

|         |              | tion differences between PIC24FV and                                                         | 39       | SDI2/CN28/RC3                                             | SDI2/CN28/RC3                                            |

|         |              | PIC24F devices.                                                                              | 40       | SDO2/CN25/RC4                                             | SDO2/CN25/RC4                                            |

| lote    | 1:           | Exposed pad on underside of device is                                                        | 41<br>42 | SCK2/CN26/RC5<br>Vss                                      | SCK2/CN26/RC5<br>Vss                                     |

|         | ~            | connected to Vss.                                                                            | 42       | VDD                                                       | VDD                                                      |

|         | 2:           | Alternative multiplexing for SDA1                                                            | 43       | N/C                                                       | N/C                                                      |

|         |              | (ASDA1) and SCL1 (ASCL1) when the I2CSEL Configuration bit is set.                           | 44<br>45 | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                      | PGED3/ASDA1 <sup>(2)</sup> /CN27/RB5                     |

|         | 3:           | PIC24F32KA3XX device pins have a                                                             | 46       | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                      | PGEC3/ASCL1 <sup>(2)</sup> /CN24/RB6                     |

|         | •.           | maximum voltage of 3.6V and are not                                                          | 47       | C2OUT/OC1/INT0/CN23/RB7                                   | INT0/CN23/RB7                                            |

|         |              | 5V tolerant.                                                                                 | 48       | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                      | SCL1/U1CTS/C3OUT/CTED10/<br>CN22/RB8                     |

### TABLE 4-3: CPU CORE REGISTERS MAP

| IADEE -   | т-∪.          |        | OOKE          |            |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

|-----------|---------------|--------|---------------|------------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Start<br>Addr | Bit 15 | Bit 14        | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| WREG0     | 0000          |        |               |            |        |        |        |       | WF    | REG0  |       |       |       |       |       |       |       | 0000          |

| WREG1     | 0002          |        |               |            |        |        |        |       | WF    | REG1  |       |       |       |       |       |       |       | 0000          |

| WREG2     | 0004          |        |               |            |        |        |        |       | WF    | REG2  |       |       |       |       |       |       |       | 0000          |

| WREG3     | 0006          |        |               |            |        |        |        |       | WF    | REG3  |       |       |       |       |       |       |       | 0000          |

| WREG4     | 0008          |        |               |            |        |        |        |       | WF    | REG4  |       |       |       |       |       |       |       | 0000          |

| WREG5     | 000A          |        |               |            |        |        |        |       | WF    | REG5  |       |       |       |       |       |       |       | 0000          |

| WREG6     | 000C          |        |               |            |        |        |        |       | WF    | REG6  |       |       |       |       |       |       |       | 0000          |

| WREG7     | 000E          |        |               |            |        |        |        |       | WF    | REG7  |       |       |       |       |       |       |       | 0000          |

| WREG8     | 0010          |        |               | WREG8      |        |        |        |       |       |       |       |       | 0000  |       |       |       |       |               |

| WREG9     | 0012          |        |               | WREG9      |        |        |        |       |       |       |       |       | 0000  |       |       |       |       |               |

| WREG10    | 0014          |        |               | WREG10     |        |        |        |       |       |       |       |       | 0000  |       |       |       |       |               |

| WREG11    | 0016          |        |               |            |        |        |        |       | WR    | EG11  |       |       |       |       |       |       |       | 0000          |

| WREG12    | 0018          |        |               |            |        |        |        |       | WR    | EG12  |       |       |       |       |       |       |       | 0000          |

| WREG13    | 001A          |        |               |            |        |        |        |       | WR    | EG13  |       |       |       |       |       |       |       | 0000          |

| WREG14    | 001C          |        |               |            |        |        |        |       | WR    | EG14  |       |       |       |       |       |       |       | 0000          |

| WREG15    | 001E          |        |               |            |        |        |        |       | WR    | EG15  |       |       |       |       |       |       |       | 0000          |

| SPLIM     | 0020          |        |               |            |        |        |        |       | SF    | PLIM  |       |       |       |       |       |       |       | XXXX          |

| PCL       | 002E          |        |               |            |        |        |        |       | F     | PCL   |       |       |       |       |       |       |       | 0000          |

| PCH       | 0030          | _      | _             | _          | _      | _      | _      | _     | _     | _     |       |       |       | PCH   |       |       |       | 0000          |

| TBLPAG    | 0032          |        | _             |            | —      | —      |        | —     | —     |       |       |       | TBI   | _PAG  |       |       |       | 0000          |

| PSVPAG    | 0034          |        |               | - <u> </u> |        |        |        |       |       |       |       | 0000  |       |       |       |       |       |               |

| RCOUNT    | 0036          |        |               |            |        |        |        |       | RC    | DUNT  |       |       |       |       |       |       |       | XXXXX         |

| SR        | 0042          | _      | _             |            | -      | -      |        | _     | DC    | IPL2  | IPL1  | IPL0  | RA    | Ν     | OV    | Z     | С     | 0000          |

| CORCON    | 0044          |        | _             | -          | _      | _      |        | _     | —     | —     | _     | _     | -     | IPL3  | PSV   | —     | _     | 0000          |

| DISICNT   | 0052          |        | – – DISICNT 2 |            |        |        |        |       |       |       |       | XXXX  |       |       |       |       |       |               |

|           |               |        |               |            |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

DS39995D-page 39

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-21: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14       | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------------|--------|---------|---------|---------|---------|---------|--------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1      | 0640 | CRCEN  | —            | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0  | CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | —     | —     | —     | 0000          |

| CRCCON2      | 0642 | _      | _            | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0 | _      | _      | —       | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL      | 0644 | X15    | X14          | X13    | X12     | X11     | X10     | X9      | X8      | X7     | X6     | X5      | X4    | X3      | X2    | X1    | _     | 0000          |

| CRCXORH      | 0646 | X31    | X30          | X29    | X28     | X27     | X26     | X25     | X24     | X23    | X22    | X21     | X20   | X19     | X18   | X17   | X16   | 0000          |

| CRCDATL      | 0648 |        |              |        |         |         |         |         | CRCDA   | TL     |        |         |       |         |       |       |       | XXXX          |

| CRCDATH      | 064A |        | CRCDATH      |        |         |         |         |         |         |        | XXXX   |         |       |         |       |       |       |               |

| CRCWDATL     | 064C |        | CRCWDATL xxx |        |         |         |         |         |         |        | XXXX   |         |       |         |       |       |       |               |

| CRCWDATH     | 064E |        | CRCWDATH     |        |         |         |         |         |         |        |        | XXXX    |       |         |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: CLOCK CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | RETEN  | —      | DPSLP  | CM     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 3140          |

| OSCTUN    | 0748 | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   | _      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | _      | HLSIDL | _      | _      | _      | _      | -      | VDIR    | BGVST | IRVST  | —     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses and by type of Reset.

### TABLE 4-23: DEEP SLEEP REGISTER MAP

| File Name             | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1 | Bit 0   | All<br>Resets |

|-----------------------|------|--------|--------|--------|--------|--------|--------|-------|----------|-------|-------|-------|-------|--------|---------|-------|---------|---------------|

| DSCON                 | 0758 | DSEN   | _      | —      | —      | _      | _      | _     | RTCCWDIS | _     | —     | —     |       | —      | ULPWDIS | DSBOR | RELEASE | 0000          |

| DSWAKE                | 075A | _      | _      | _      | _      | -      | -      | _     | DSINT0   | DSFLT | _     | _     | DSWDT | DSRTCC | DSMCLR  | _     | DSPOR   | 0000          |

| DSGPR0 <sup>(1)</sup> | 075C |        | DSGPR0 |        |        |        |        |       |          |       |       | 0000  |       |        |         |       |         |               |

| DSGPR1 <sup>(1)</sup> | 075E |        | DSGPR1 |        |        |        |        |       |          |       |       | 0000  |       |        |         |       |         |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Deep Sleep registers, DSGPR0 and DSGPR1, are only reset on a VDD POR event.

#### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE Reset - GOTO Instruction 000000h Reset - GOTO Address 000002h Reserved 000004h Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000014h Interrupt Vector 1 \_ Interrupt Vector 52 00007Ch Interrupt Vector Table (IVT)<sup>(1)</sup> Decreasing Natural Order Priority Interrupt Vector 53 00007Eh Interrupt Vector 54 000080h \_ Interrupt Vector 116 0000FCh Interrupt Vector 117 0000FEh Reserved 000100h Reserved 000102h Reserved Oscillator Fail Trap Vector Address Error Trap Vector Stack Error Trap Vector Math Error Trap Vector Reserved Reserved Reserved Interrupt Vector 0 000114h Interrupt Vector 1 Alternate Interrupt Vector Table (AIVT)<sup>(1)</sup> 00017Ch Interrupt Vector 52 00017Eh Interrupt Vector 53 Interrupt Vector 54 000180h \_\_\_\_\_ Interrupt Vector 116 Interrupt Vector 117 0001FEh Start of Code 000200h

Note 1: See Table 8-2 for the interrupt vector list.

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O Ports, refer to the "PIC24F Family Reference Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24FV32KA304 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

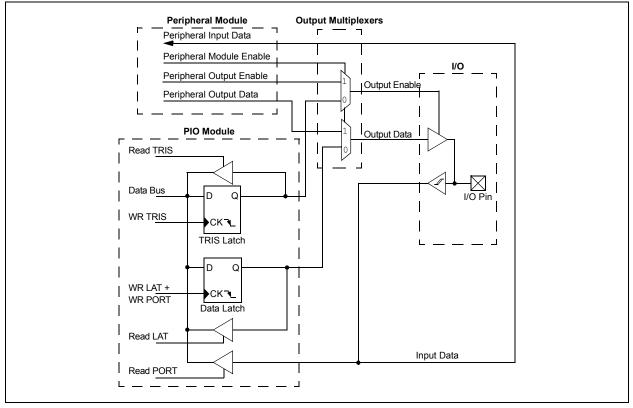

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LAT), read the latch. Writes to the latch, write the latch. Reads from the port (PORT), read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: This feature is is only available for the 16x BRG mode (BRGH = 0).

- 2: The bit availability depends on the pin availability.

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |

|----------|--------|----------|-----|-----------|-------|----------|----------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |

| bit 15   |        |          |     |           |       |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |

|----------|----------|-------|----------|----------|----------|-----------|----------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |

| bit 7    |          |       |          |          |          |           | bit 0    |

| Legend:                    | HC = Hardware Clearable bit |                             |                    |

|----------------------------|-----------------------------|-----------------------------|--------------------|

| HS = Hardware Settable bit | C = Clearable bit           | HSC = Hardware Settable/Cle | earable bit        |

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR          | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

| bit 14  | UTXINV: IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit                                                                                                                                                                                                                                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <u>If IREN = 1:</u>                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                         |

|         | 0 = UxTX  Idle  0'                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                                                                                                                                                                                                     |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                                                                                                                                                                                                      |

| bit 10  | UTXEN: UARTx Transmit Enable bit                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>1 = Transmit is enabled; UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled; any pending transmission is aborted and the buffer is reset. UxTX pin is controlled by the PORT register.</li> </ul>                                                                                                                                                                                 |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                  |

|         | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                               |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                                                               |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                                                                       |

|         | 1 = Transmit Shift Register is empty and the transmit buffer is empty (the last transmission has completed)                                                                                                                                                                                                                                                                                               |

|         | 0 = Transmit Shift Register is not empty; a transmission is in progress or queued                                                                                                                                                                                                                                                                                                                         |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>11 = Interrupt is set on a RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on a RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters.</li> </ul> |

|         |                                                                                                                                                                                                                                                                                                                                                                                                           |

#### 19.2.5 RTCVAL REGISTER MAPPINGS

### REGISTER 19-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | —      | —      | —      | —      | —      | —      |

| bit 15 |        |        | •      | •      |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-x  |

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

### Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

#### REGISTER 19-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 12    | <b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'. |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits                                   |

|           | Contains a value from 0 to 9.                                                                        |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits                                     |

|           | Contains a value from 0 to 3.                                                                        |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits                                     |

|           | Contains a value from 0 to 9.                                                                        |

|           |                                                                                                      |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

NOTES:

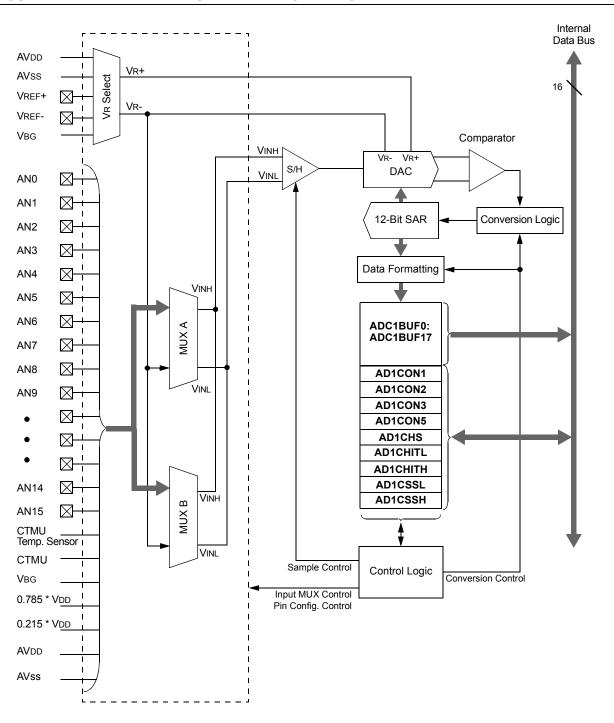

### FIGURE 22-1: 12-BIT A/D CONVERTER BLOCK DIAGRAM

#### **CMxCON: COMPARATOR x CONTROL REGISTERS REGISTER 23-1:** R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R-0 CON COE CPOL CLPWR CEVT COUT bit 15 bit 8 R/W-0 R/W-0 U-0 R/W-0 U-0 U-0 R/W-0 R/W-0 EVPOL1 **EVPOL0** CREF CCH1 CCH0 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 CON: Comparator x Enable bit 1 = Comparator is enabled 0 = Comparator is disabled bit 14 COE: Comparator x Output Enable bit 1 = Comparator output is present on the CxOUT pin 0 = Comparator output is internal only bit 13 CPOL: Comparator x Output Polarity Select bit 1 = Comparator output is inverted 0 = Comparator output is not inverted bit 12 CLPWR: Comparator x Low-Power Mode Select bit 1 = Comparator operates in Low-Power mode 0 = Comparator does not operate in Low-Power mode bit 11-10 Unimplemented: Read as '0' bit 9 **CEVT:** Comparator x Event bit 1 = Comparator event defined by EVPOL<1:0> has occurred; subsequent triggers and interrupts are disabled until the bit is cleared 0 = Comparator event has not occurred bit 8 COUT: Comparator x Output bit When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN -When CPOL = 1: 1 = VIN + < VIN -0 = VIN + > VIN bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits 11 = Trigger/event/interrupt is generated on any change of the comparator output (while CEVT = 0) 10 = Trigger/event/interrupt is generated on the transition of the comparator output: If CPOL = 0 (non-inverted polarity): High-to-low transition only. If CPOL = 1 (inverted polarity): Low-to-high transition only. 01 = Trigger/event/interrupt is generated on the transition of the comparator output If CPOL = <u>0</u> (non-inverted polarity): Low-to-high transition only. If CPOL = $\underline{1}$ (inverted polarity): High-to-low transition only. 00 = Trigger/event/interrupt generation is disabled

bit 5 Unimplemented: Read as '0'

| R/W-0        |                                                              |                                                                  |                 |                                                    |                  |                 |       |

|--------------|--------------------------------------------------------------|------------------------------------------------------------------|-----------------|----------------------------------------------------|------------------|-----------------|-------|

|              | R/W-0                                                        | R/W-0                                                            | R/W-0           | R/W-0                                              | R/W-0            | R/W-0           | R/W-0 |

| ITRIM5       | ITRIM4                                                       | ITRIM3                                                           | ITRIM2          | ITRIM1                                             | ITRIM0           | IRNG1           | IRNG0 |

| bit 15       |                                                              |                                                                  |                 |                                                    |                  |                 | bit   |

| U-0          | U-0                                                          | U-0                                                              | U-0             | U-0                                                | U-0              | U-0             | U-0   |

| _            | _                                                            | _                                                                | _               | _                                                  | _                | _               | _     |

| bit 7        |                                                              |                                                                  |                 |                                                    |                  |                 | bit   |

|              |                                                              |                                                                  |                 |                                                    |                  |                 |       |

| Legend:      |                                                              |                                                                  |                 |                                                    |                  |                 |       |

| R = Readab   | le bit                                                       | W = Writable I                                                   | oit             | U = Unimplem                                       | nented bit, read | d as '0'        |       |

| -n = Value a | t POR                                                        | '1' = Bit is set                                                 |                 | '0' = Bit is clea                                  | ared             | x = Bit is unkn | iown  |

|              | 000000 <b>= No</b>                                           | minal current o                                                  | utput specified | nominal current<br>by IRNG<1:0><br>nominal current |                  |                 |       |

|              | •                                                            |                                                                  |                 |                                                    |                  |                 |       |

|              | •<br>•<br>100010<br>100001 = Ma                              | iximum negativo                                                  | e change from   | nominal currer                                     | ıt               |                 |       |

| bit 9-8      | 100001 = Ma<br>IRNG<1:0>: (<br>11 = 100 × Ba<br>10 = 10 × Ba | Current Source<br>ase Current<br>se Current<br>urrent Level (0.5 | Range Select    |                                                    | ıt               |                 |       |

### REGISTER 25-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

NOTES:

### 29.1 DC Characteristics

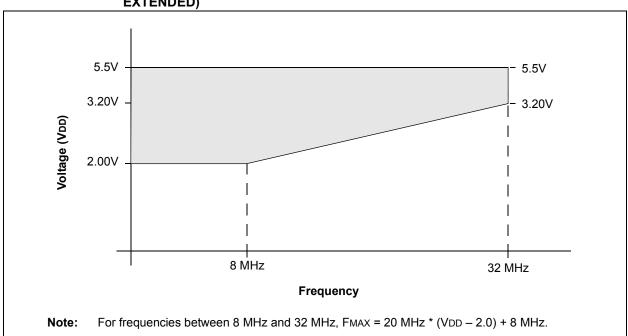

### FIGURE 29-1: PIC24FV32KA304 VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL AND EXTENDED)

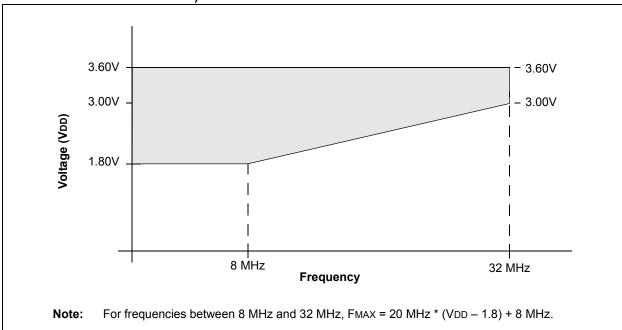

### FIGURE 29-2: PIC24F32KA304 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL AND EXTENDED)

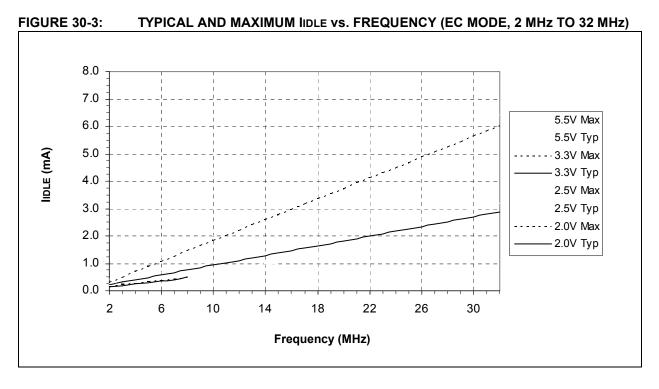

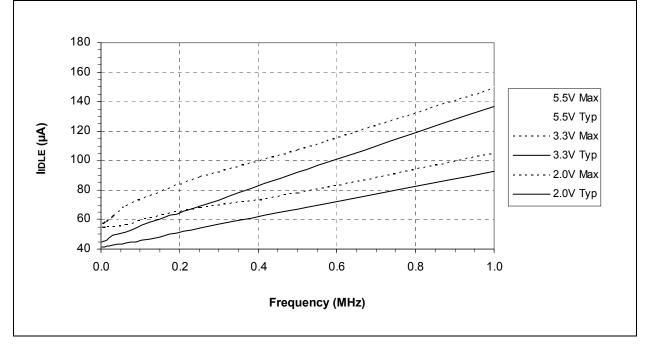

FIGURE 30-4: TYPICAL AND MAXIMUM lidle vs. FREQUENCY (EC MODE, 1.95 kHz TO 1 MHz)

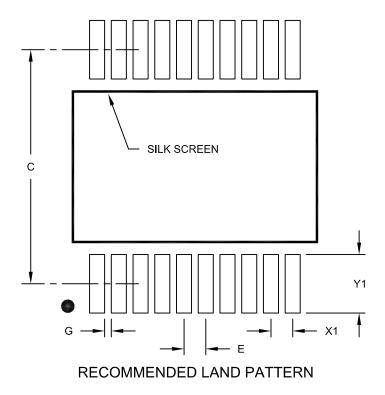

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension                | MIN         | NOM  | MAX      |      |

| Contact Pitch            | E           |      | 0.65 BSC |      |

| Contact Pad Spacing      | С           |      | 7.20     |      |

| Contact Pad Width (X20)  | X1          |      |          | 0.45 |

| Contact Pad Length (X20) | Y1          |      |          | 1.75 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

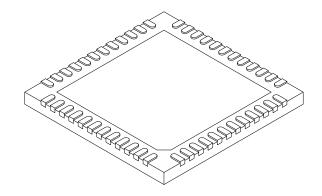

### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | N    | <b>ILLIMETER</b> | S    |  |

|------------------------|--------|------|------------------|------|--|

| Dimension              | Limits | MIN  | NOM              | MAX  |  |

| Number of Pins         | N      |      | 48               |      |  |

| Pitch                  | е      |      | 0.40 BSC         |      |  |

| Overall Height         | Α      | 0.45 | 0.50             | 0.55 |  |

| Standoff               | A1     | 0.00 | 0.02             | 0.05 |  |

| Contact Thickness      | A3     |      | 0.127 REF        |      |  |

| Overall Width          | E      |      | 6.00 BSC         |      |  |

| Exposed Pad Width      | E2     | 4.45 | 4.60             | 4.75 |  |

| Overall Length         | D      |      | 6.00 BSC         |      |  |

| Exposed Pad Length     | D2     | 4.45 | 4.60             | 4.75 |  |

| Contact Width          | b      | 0.15 | 0.20             | 0.25 |  |

| Contact Length         | L      | 0.30 | 0.40             | 0.50 |  |

| Contact-to-Exposed Pad | K      | 0.20 | -                | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Product Group<br>Pin Count<br>Tape and Reel Fl |                                                                                                                                                                                          | <ul> <li>Examples:</li> <li>a) PIC24FV32KA304-I/ML: Wide voltage range,<br/>General Purpose, 32-Kbyte program memory,<br/>44-pin, Industrial temp., QFN package</li> <li>b) PIC24F16KA302-I/SS: Standard voltage range,<br/>General Purpose, 16-Kbyte program memory,<br/>28-pin, Industrial temp., SSOP package</li> </ul> |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                                   | 24 = 16-bit modified Harvard without DSP                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                             |

| Flash Memory Family                            | <ul><li>F = Standard voltage range Flash program memory</li><li>FV = Wide voltage range Flash program memory</li></ul>                                                                   |                                                                                                                                                                                                                                                                                                                             |

| Product Group                                  | KA3 = General purpose microcontrollers                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                             |

| Pin Count                                      | 01 = 20-pin<br>02 = 28-pin<br>04 = 44-pin                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |

| Temperature Range                              | $I = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Industrial)}$<br>$E = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (Industrial)}$                                                    |                                                                                                                                                                                                                                                                                                                             |

| Package                                        | SP         = SPDIP           SO         = SOIC           SS         = SSOP           ML         = QFN           P         = PDIP           PT         = TQFP           MV         = UQFN |                                                                                                                                                                                                                                                                                                                             |

| Pattern                                        | Three-digit QTP, SQTP, Code or Special Requirements<br>(blank otherwise)<br>ES = Engineering Sample                                                                                      |                                                                                                                                                                                                                                                                                                                             |