#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka304-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address, as shown in Figure 4-2.

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h, with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables, located from 000004h to 0000FFh and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the Interrupt Vector Tables (IVT) is provided in Section 8.1 "Interrupt Vector Table (IVT)".

#### 4.1.3 DATA EEPROM

In the PIC24FV32KA304 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFF.

The data EEPROM is organized as 16-bit wide memory and 256 words deep. This memory is accessed using table read and write operations similar to the user code memory.

#### 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24FV32KA304 family. Their location in the memory map is shown in Figure 4-1.

For more information on device Configuration Words, see **Section 26.0 "Special Features"**.

# TABLE 4-1:DEVICE CONFIGURATION<br/>WORDS FOR PIC24FV32KA304<br/>FAMILY DEVICES

| Configuration Words | Configuration Word<br>Addresses |

|---------------------|---------------------------------|

| FBS                 | F80000                          |

| FGS                 | F80004                          |

| FOSCSEL             | F80006                          |

| FOSC                | F80008                          |

| FWDT                | F8000A                          |

| FPOR                | F8000C                          |

| FICD                | F8000E                          |

| FDS                 | F80010                          |

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| msw<br>Address | most significant wor                              | rd lea     | ast significant word | PC Address<br>(Isw Address) |

|----------------|---------------------------------------------------|------------|----------------------|-----------------------------|

|                | 23                                                | 16         | 8                    | 0                           |

| 000001h        | 0000000                                           |            |                      | 000000h                     |

| 000003h        | 0000000                                           |            |                      | 000002h                     |

| 000005h        | 0000000                                           |            |                      | 000004h                     |

| 000007h        | 0000000                                           |            |                      | 000006h                     |

|                |                                                   | ~          |                      |                             |

|                | Program Memory<br>'Phantom' Byte<br>(read as '0') | Instructio | on Width             |                             |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| IADLL        | <del>4</del> -J. |        |         |         |         |        | JULK     |          |          |       |          |          |          |         |          |          |          |               |

|--------------|------------------|--------|---------|---------|---------|--------|----------|----------|----------|-------|----------|----------|----------|---------|----------|----------|----------|---------------|

| File<br>Name | Addr             | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10   | Bit 9    | Bit 8    | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| INTCON1      | 0080             | NSTDIS | _       | —       | —       | _      | _        | —        | —        | —     | —        | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082             | ALTIVT | DISI    | -       | _       | _      |          | _        | _        | _     | _        |          | _        | _       | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084             | NVMIF  | _       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF   | SPF1IF   | T3IF     | T2IF  | OC2IF    | IC2IF    | —        | T1IF    | OC1IF    | IC1IF    | INT0IF   | 0000          |

| IFS1         | 0086             | U2TXIF | U2RXIF  | INT2IF  | T5IF    | T4IF   | _        | OC3IF    | _        | _     | _        | _        | INT1IF   | CNIF    | CMIF     | MI2C1IF  | SI2C1IF  | 0000          |

| IFS2         | 8800             | _      | _       | _       | _       | _      | _        | _        | _        | -     | _        | IC3IF    | _        | _       | _        | SPI2IF   | SPF2IF   | 0000          |

| IFS3         | 008A             | _      | RTCIF   | _       | _       | _      | _        | _        | _        | -     | _        | _        | _        | _       | MI2C2IF  | SI2C2IF  | _        | 0000          |

| IFS4         | 008C             | -      | _       | CTMUIF  | —       | —      |          | —        | HLVDIF   |       | —        | _        | _        | CRCIF   | U2ERIF   | U1ERIF   |          | 0000          |

| IFS5         | 008E             |        | —       |         | _       | _      |          | —        | —        |       | —        |          | _        | —       |          | —        | ULPWUIF  | 0000          |

| IEC0         | 0094             | NVMIE  | _       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE   | SPF1IE   | T3IE     | T2IE  | OC2IE    | IC2IE    | _        | T1IE    | OC1IE    | IC1IE    | INT0IE   | 0000          |

| IEC1         | 0096             | U2TXIE | U2RXIE  | INT2IE  | T5IE    | T4IE   | _        | OC3IE    | _        | -     | _        | _        | INT1IE   | CNIE    | CMIE     | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098             | _      | _       | _       | _       | _      | _        | _        | _        | -     | _        | IC3IE    | _        | _       | _        | SPI2IE   | SPF2IE   | 0000          |

| IEC3         | 009A             | _      | RTCIE   | _       | _       | _      | _        | _        | _        | -     | _        | _        | _        | _       | MI2C2IE  | SI2C2IE  | _        | 0000          |

| IEC4         | 009C             |        | —       | CTMUIE  | _       | _      |          | —        | HLVDIE   |       | —        |          | _        | CRCIE   | U2ERIE   | U1ERIE   |          | 0000          |

| IEC5         | 009E             | _      | _       | _       | _       | _      | _        | _        | _        | -     | _        | _        | _        | _       | _        | _        | ULPWUIE  | 0000          |

| IPC0         | 00A4             |        | T1IP2   | T1IP1   | T1IP0   | _      | OC1IP2   | OC1IP1   | OC1IP0   |       | IC1IP2   | IC1IP1   | IC1IP0   | —       | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1         | 00A6             |        | T2IP2   | T2IP1   | T2IP0   | _      | OC2IP2   | OC2IP1   | OC2IP0   |       | IC2IP2   | IC2IP1   | IC2IP0   | —       |          | —        |          | 4444          |

| IPC2         | 00A8             |        | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2  | SPI1IP1  | SPI1IP0  |       | SPF1IP2  | SPF1IP1  | SPF1IP0  | —       | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA             |        | NVMIP2  | NVMIP1  | NVMIP0  | _      |          | —        | —        |       | AD1IP2   | AD1IP1   | AD1IP0   | —       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 4044          |

| IPC4         | 00AC             |        | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2    | CMIP1    | CMIP0    |       | MI2C1P2  | MI2C1P1  | MI2C1P0  | —       | SI2C1P2  | SI2C1P1  | SI2C1P0  | 4444          |

| IPC5         | 00AE             |        | _       |         | _       | _      |          | —        | —        |       | —        |          | _        | —       | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC6         | 00B0             |        | T4IP2   | T4IP1   | T4IP0   | _      |          | —        | —        |       | OC3IP2   | OC3IP1   | OC3IP0   | —       |          | —        |          | 4040          |

| IPC7         | 00B2             |        | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2  | U2RXIP1  | U2RXIP0  |       | INT2IP2  | INT2IP1  | INT2IP0  | —       | T5IP2    | T5IP1    | T5IP0    | 4440          |

| IPC8         | 00B4             |        | _       |         | _       | _      |          | —        | —        |       | SPI2IP2  | SPI2IP1  | SPI2IP0  | —       | SPF2IP2  | SPF2IP1  | SPF2IP0  | 0044          |

| IPC9         | 00B6             |        | _       |         | _       | _      |          | —        | —        |       | IC3IP2   | IC3IP1   | IC3IP0   | —       |          | —        |          | 0040          |

| IPC12        | 00BC             | -      | _       |         | —       | —      | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 |       | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | —       |          | —        |          | 0440          |

| IPC15        | 00C2             | _      | _       | _       | _       | _      | RTCIP2   | RTCIP1   | RTCIP0   | -     | _        | _        | _        | _       | _        | _        | _        | 0400          |

| IPC16        | 00C4             | _      | CRCIP2  | CRCIP1  | CRCIP0  | _      | U2ERIP2  | U2ERIP1  | U2ERIP0  | -     | U1ERIP2  | U1ERIP1  | U1ERIP0  | _       | _        | _        | _        | 4440          |

| IPC18        | 00C8             | -      |         |         | —       | —      |          | _        | _        | _     | —        |          | _        | _       | HLVDIP2  | HLVDIP1  | HLVDIP0  | 0004          |

| IPC19        | 00CA             | -      |         |         | —       | —      |          | _        | _        | _     | CTMUIP2  | CTMUIP1  | CTMUIP0  | _       | _        | _        | _        | 0040          |

| IPC20        | 00CC             | _      | _       |         | _       |        |          | _        |          | —     |          |          |          |         | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 | 0000          |

| INTTREG      | 00E0             | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2     | ILR1     | ILR0     | _     | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

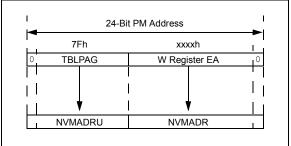

#### 6.3 NVM Address Register

As with Flash program memory, the NVM Address registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space. Instead, they directly capture the EA<23:0> of the last table write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", are unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

#### 6.4 Data EEPROM Operations

The EEPROM block is accessed using table read and write operations similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

Note 1: Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.

2: The C30 C compiler includes library procedures to automatically perform the table read and table write operations, manage the Table Pointer and write buffers, and unlock and initiate memory write sequences. This eliminates the need to create assembler macros or time critical routines in C for each application.

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

#### **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 5 | SWDTEN: Software Enable/Disable of WDT bit <sup>(2)</sup>                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = WDT is enabled</li><li>0 = WDT is disabled</li></ul>                                                                                       |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-up Reset has occurred<br>0 = A Power-up Reset has not occurred                                      |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTENx Configuration bit is '1' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV32KA3XX parts only; not used on PIC24F32KA3XX devices.

#### TABLE 7-1:RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                       | Clearing Event          |

|-------------------|-----------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                                 | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access   | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                        | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                          | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                   | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                        | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                           | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                            | POR                     |

| BOR (RCON<1>)     | POR, BOR                                            | —                       |

| POR (RCON<0>)     | POR                                                 | —                       |

| DPSLP (RCON<10>)  | PWRSAV #SLEEP Instruction with DSEN (DSCON<15>) Set | POR                     |

Note: All Reset flag bits may be set or cleared by the user software.

#### REGISTER 8-11: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

#### bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

NOTES:

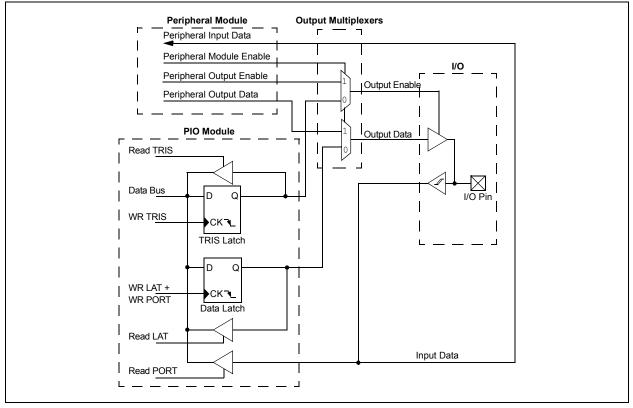

#### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O Ports, refer to the "PIC24F Family Reference Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24FV32KA304 family devices do not support Peripheral Pin Select features.

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LAT), read the latch. Writes to the latch, write the latch. Reads from the port (PORT), read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

#### REGISTER 11-2: ANSB: ANALOG SELECTION (PORTB)

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|--------|-----|-----|-----|-------|

| ANSB15 | ANSB14 | ANSB13 | ANSB12 | —   | —   | —   | —     |

| bit 15 |        |        |        |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1                | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|----------------------|-------|-------|-------|

| —     | —   | —   | ANSB4 | ANSB3 <sup>(1)</sup> | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |     |     |       |                      |       |       | bit 0 |

#### Legend:

bit 7

| Legena:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-12 ANSB<15:12>: Analog Select Control bits

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- bit 11-5 Unimplemented: Read as '0'

- bit 4-0 ANSB<4:0>: Analog Select Control bits<sup>(1)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

- Note 1: The ANSB3 bit is not available on 20-pin devices.

#### REGISTER 11-3: ANSC ANALOG SELECTION (PORTC)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0                  | U-0                  | U-0                  |

|--------|-----|-----|-----|-----|----------------------|----------------------|----------------------|

| —      | —   | —   | —   | —   | —                    | —                    | —                    |

| bit 15 |     |     |     |     |                      |                      | bit 8                |

|        |     |     |     |     |                      |                      |                      |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                | R/W-1                | R/W-1                |

| —      | —   | —   | —   | _   | ANSC2 <sup>(1)</sup> | ANSC1 <sup>(1)</sup> | ANSC0 <sup>(1)</sup> |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 ANSC<2:0>: Analog Select Control bits<sup>(1)</sup>

- 1 = Digital input buffer is not active (use for analog input)

- 0 = Digital input buffer is active

Note 1: These bits are not available on 20-pin or 28-pin devices.

bit 0

#### 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even numbered module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bit (ICxCON2<8>) for both modules.

#### 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. If Synchronous mode is to be used, disable the Sync source before proceeding.

- 2. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 3. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired Sync/trigger source.

- Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source. If the desired clock source is running, set the ICTSELx bits before the input capture module is enabled, for proper synchronization with the desired clock source.

- 5. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- 6. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 7. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 8. Enable the selected Sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same Sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bit settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the Sync source as the last step. Both input capture modules are held in Reset until the Sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the Sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

#### 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0 and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

#### 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 18.2 "Transmitting in 8-Bit Data Mode"**).

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

#### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

#### 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

#### 18.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

### 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

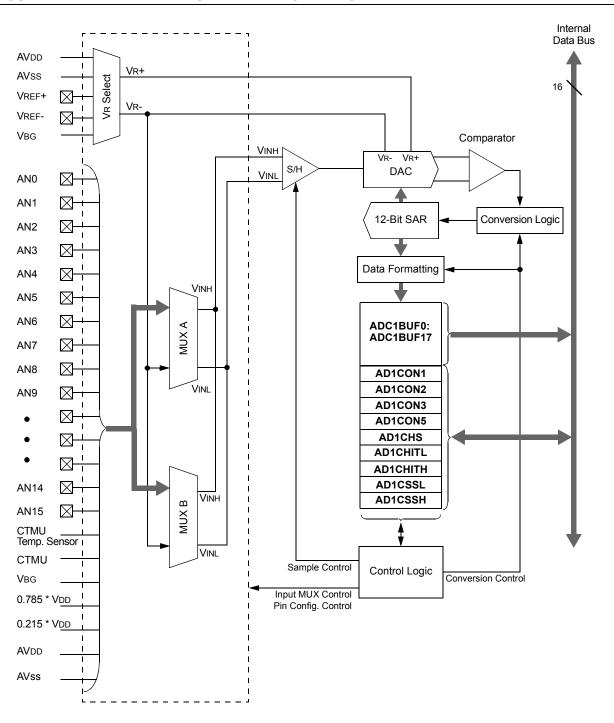

#### FIGURE 22-1: 12-BIT A/D CONVERTER BLOCK DIAGRAM

#### REGISTER 22-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   | U-0   |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   | —   | —   | —   | _   |       | —     |

| bit 15 |     |     |     |     |     |       | bit 8 |

|        |     |     |     |     |     |       |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|        |     | —   | —   | —   |     | CHH17 | CHH16 |

| bit 7  |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'.

bit 1-0 CHH<17:16>: A/D Compare Hit bits

If CM<1:0> = 11:

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For All Other Values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

#### REGISTER 22-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| CHH15  | CHH14 | CHH13 | CHH12 | CHH11 | CHH10 | CHH9  | CHH8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CHH7   | CHH6  | CHH5  | CHH4  | CHH3  | CHH2  | CHH1  | CHH0  |

| bit 7  | •     | •     | •     |       | •     | •     | bit 0 |

|        |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CHH<15:0>: A/D Compare Hit bits

<u>If CM<1:0> = 11:</u>

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For all other values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

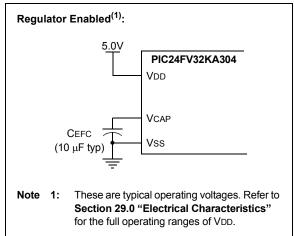

#### 26.2 On-Chip Voltage Regulator

All of the PIC24FV32KA304 family devices power their core digital logic at a nominal 3.0V. This may create an issue for designs that are required to operate at a higher typical voltage, as high as 5.0V. To simplify system design, all devices in the "FV" family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator is always enabled and provides power to the core from the other VDD pins. A low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 26-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is discussed in Section 2.4 "Voltage Regulator Pin (VCAP)", and in Section 29.1 "DC Characteristics".

For "F" devices, the regulator is disabled. Instead, core logic is powered directly from VDD. This allows the devices to operate at an overall lower allowable voltage range (1.8V-3.6V).

#### 26.2.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

For all PIC24FV32KA304 devices, the on-chip regulator provides a constant voltage of 3.2V nominal to the digital core logic. The regulator can provide this level from a VDD of about 3.2V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 3.2V. In order to prevent "brown-out" conditions when the voltage drops too low for the regulator, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD with a typical voltage drop of 150 mV.

When the device enters Tracking mode, it is no longer possible to operate at full speed. To provide information about when the device enters Tracking mode, the on-chip regulator includes a simple, High/Low-Voltage Detect (HLVD) circuit. When VDD drops below full-speed operating voltage, the circuit sets the High/Low-Voltage Detect Interrupt Flag, HLVDIF (IFS4<8>). This can be used to generate an interrupt and put the application into a low-power operational mode or trigger an orderly shutdown. Maximum device speeds as a function of VDD are shown in **Section 29.1 "DC Characteristics"**, in Figure 29-1 and Figure 29-1.

#### 26.2.2 ON-CHIP REGULATOR AND POR

For PIC24FV32KA304 devices, it takes a brief time, designated as TPM, for the Voltage Regulator to generate a stable output. During this time, code execution is disabled. TPM (DC Specification SY71) is applied every time the device resumes operation after any power-down, including Sleep mode.

### FIGURE 26-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

#### 26.3 Watchdog Timer (WDT)

For the PIC24FV32KA304 family of devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranging from 1 ms to 131 seconds, can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

#### 28.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |  |  |  |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |  |  |  |  |  |  |

|       | reference source.                          |  |  |  |  |  |  |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could either be the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| DC CHARACTERISTICS |     |                     | Operating temperature -40°C |                    |     |       | pns: 1.8V to 3.6V PIC24F32KA3XX<br>2.0V to 5.5V PIC24FV32KA3XX<br>$C \le TA \le +85^{\circ}C$ for Industrial<br>$C \le TA \le +125^{\circ}C$ for Extended |            |  |  |

|--------------------|-----|---------------------|-----------------------------|--------------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Param<br>No.       | Sym | Characteristic      | Min                         | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                                                                                                |            |  |  |

|                    | Vol | Output Low Voltage  |                             |                    |     |       |                                                                                                                                                           |            |  |  |

| DO10               |     | All I/O Pins        | —                           | —                  | 0.4 | V     | IOL = 8.0 mA                                                                                                                                              | VDD = 4.5V |  |  |

|                    |     |                     | —                           | —                  | 0.4 | V     | IOL = 4.0 mA                                                                                                                                              | VDD = 3.6V |  |  |

|                    |     |                     | —                           | —                  | 0.4 | V     | IOL = 3.5 mA                                                                                                                                              | VDD = 2.0V |  |  |

| DO16               |     | OSC2/CLKO           | _                           | _                  | 0.4 | V     | IOL = 2.0 mA                                                                                                                                              | VDD = 4.5V |  |  |

|                    |     |                     | —                           | —                  | 0.4 | V     | IOL = 1.2 mA                                                                                                                                              | VDD = 3.6V |  |  |

|                    |     |                     | —                           | —                  | 0.4 | V     | IOL = 0.4 mA                                                                                                                                              | VDD = 2.0V |  |  |

|                    | Vон | Output High Voltage |                             |                    |     |       |                                                                                                                                                           |            |  |  |

| DO20               |     | All I/O Pins        | 3.8                         | —                  | —   | V     | IOH = -3.5 mA                                                                                                                                             | VDD = 4.5V |  |  |

|                    |     |                     | 3                           | —                  | —   | V     | IOH = -3.0 mA                                                                                                                                             | VDD = 3.6V |  |  |

|                    |     |                     | 1.6                         | _                  | —   | V     | IOH = -1.0 mA                                                                                                                                             | VDD = 2.0V |  |  |

| DO26               |     | OSC2/CLKO           | 3.8                         | _                  | —   | V     | Іон = -2.0 mA                                                                                                                                             | VDD = 4.5V |  |  |

|                    |     |                     | 3                           | _                  | —   | V     | IOH = -1.0 mA                                                                                                                                             | VDD = 3.6V |  |  |

|                    |     |                     | 1.6                         | _                  | _   | V     | Іон = -0.5 mA                                                                                                                                             | VDD = 2.0V |  |  |

#### TABLE 29-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS              |       |                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                               |  |  |

|---------------------------------|-------|--------------------------------------|------------------------------------------------------|--------------------|-----|-------|-----------------------------------------------|--|--|

| Param<br>No. Sym Characteristic |       |                                      | Min                                                  | Typ <sup>(1)</sup> | Max | Units | Conditions                                    |  |  |

|                                 |       | Program Flash Memory                 |                                                      |                    |     |       |                                               |  |  |

| D130                            | Eр    | Cell Endurance                       | 10,000 <sup>(2)</sup>                                | —                  | —   | E/W   |                                               |  |  |

| D131                            | Vpr   | VDD for Read                         | VMIN                                                 | _                  | 3.6 | V     | VMIN = Minimum operating voltage              |  |  |

| D133A                           | Tiw   | Self-Timed Write Cycle<br>Time       | _                                                    | 2                  | —   | ms    |                                               |  |  |

| D134                            | TRETD | Characteristic Retention             | 40                                                   | _                  | —   | Year  | Provided no other specifications are violated |  |  |

| D135                            | IDDP  | Supply Current During<br>Programming |                                                      | 10                 | —   | mA    |                                               |  |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Self-write and block erase.

| A 0 0''            |               |                                                                         | Standard Operating Conditions: 1.8V to 3.6V PIC24F32KA3XX<br>2.0V to 5.5V PIC24FV32KA3XX |                                                                                           |                    |                          |                                   |  |  |  |

|--------------------|---------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|--------------------------|-----------------------------------|--|--|--|

| AC CHARACTERISTICS |               |                                                                         | Operating terr                                                                           | -40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |                    |                          |                                   |  |  |  |

| Param<br>No.       | Sym           | Characteristic                                                          | Min                                                                                      | Conditions                                                                                |                    |                          |                                   |  |  |  |

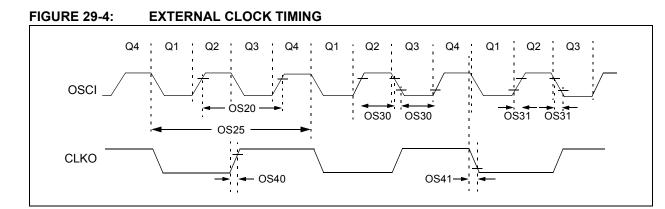

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) | DC<br>4                                                                                  |                                                                                           | 32<br>8            | MHz<br>MHz               | EC<br>ECPLL                       |  |  |  |

| OS15               |               | Oscillator Frequency                                                    | 0.2<br>4<br>4<br>31                                                                      | <br> <br>                                                                                 | 4<br>25<br>8<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT<br>HS<br>XTPLL<br>SOSC         |  |  |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                           | —                                                                                        | —                                                                                         | _                  | _                        | See Parameter OS10 for Fosc value |  |  |  |

| OS25               | TCY           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                                                                                     | —                                                                                         | DC                 | ns                       |                                   |  |  |  |

| OS30               | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                            | 0.45 x Tosc                                                                              | —                                                                                         | _                  | ns                       | EC                                |  |  |  |

| OS31               | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                           | _                                                                                        | —                                                                                         | 20                 | ns                       | EC                                |  |  |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | —                                                                                        | 6                                                                                         | 10                 | ns                       |                                   |  |  |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | _                                                                                        | 6                                                                                         | 10                 | ns                       |                                   |  |  |  |

#### TABLE 29-19: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

**3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TCY) and high for the Q3-Q4 period (1/2 TCY).

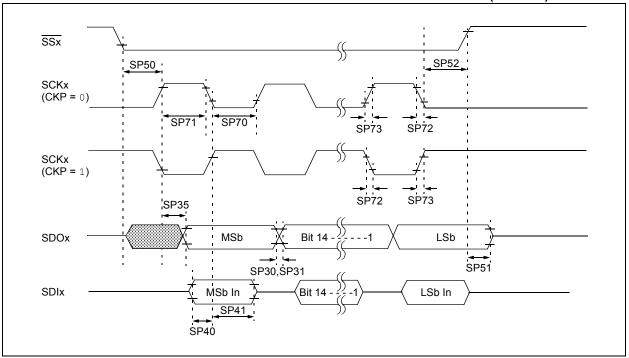

#### FIGURE 29-20: SPIX MODULE SLAVE MODE TIMING CHARACTERISTICS (CKE = 0)

#### TABLE 29-38: SPIX MODULE SLAVE MODE TIMING REQUIREMENTS (CKE = 0)

| AC CHARACTERISTICS |                       |                                                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: } 2.0V \ to \ 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \ for \ Industrial \\ -40^\circ C \leq TA \leq +125^\circ C \ for \ Extended \\ \end{array}$ |                    |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic                                                                  | Min                                                                                                                                                                                                                                                                               | Typ <sup>(1)</sup> | Max | Units | Conditions |  |

| SP70               | TscL                  | SCKx Input Low Time                                                             | 30                                                                                                                                                                                                                                                                                |                    | _   | ns    |            |  |

| SP71               | TscH                  | SCKx Input High Time                                                            | 30                                                                                                                                                                                                                                                                                | _                  | _   | ns    |            |  |

| SP72               | TscF                  | SCKx Input Fall Time <sup>(2)</sup>                                             |                                                                                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |

| SP73               | TscR                  | SCKx Input Rise Time <sup>(2)</sup>                                             |                                                                                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(2)</sup>                                       |                                                                                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(2)</sup>                                       |                                                                                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                       | —                                                                                                                                                                                                                                                                                 | —                  | 30  | ns    |            |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input<br>to SCKx Edge                                   | 20                                                                                                                                                                                                                                                                                | —                  | _   | ns    |            |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                                    | 20                                                                                                                                                                                                                                                                                | _                  | _   | ns    |            |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx to SCKx ↑ or SCKx Input                                                     | 120                                                                                                                                                                                                                                                                               | —                  | _   | ns    |            |  |

| SP51               | TssH2doZ              | $\overline{\text{SSx}}$ $\uparrow$ to SDOx Output High-Impedance <sup>(3)</sup> | 10                                                                                                                                                                                                                                                                                | —                  | 50  | ns    |            |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                             | 1.5 Tcy + 40                                                                                                                                                                                                                                                                      | —                  | —   | ns    |            |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The minimum clock period for SCKx is 100 ns; therefore, the clock generated in Master mode must not violate this specification.

3: This assumes a 50 pF load on all SPIx pins.

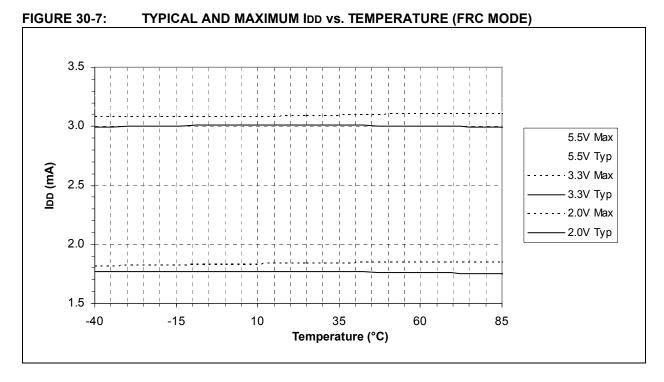

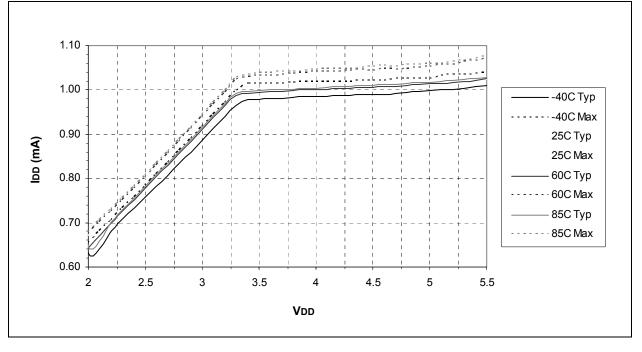

FIGURE 30-8: TYPICAL AND MAXIMUM lidle vs. Vdd (FRC MODE)

NOTES:

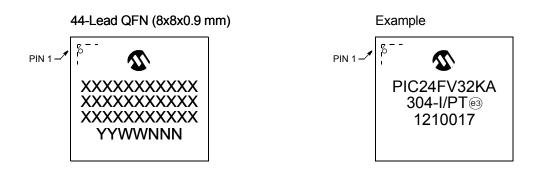

44-Lead TQFP (10x10x1 mm)

Example

48-Lead UQFN (6x6x0.5 mm)

Example